#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k40t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 4-5: OSCFRQ: HFINTOSC FREQUENCY SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-q/q    | R/W-q/q | R/W-q/q | R/W-q/q |

|-------|-----|-----|-----|------------|---------|---------|---------|

| —     | —   | —   | —   | HFFRQ<3:0> |         |         |         |

| bit 7 |     |     |     |            |         |         | bit 0   |

# Legend:

| Logonal              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Reset value is determined by hardware             |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 HFFRQ<3:0>: HFINTOSC Frequency Selection bits

| HFFRQ<3:0>          | Nominal Freq (MHz) |  |  |  |  |

|---------------------|--------------------|--|--|--|--|

| 1001                |                    |  |  |  |  |

| 1010                | Reserved           |  |  |  |  |

| 1111                |                    |  |  |  |  |

| 1110                |                    |  |  |  |  |

| 1101                |                    |  |  |  |  |

| 1100                | ]                  |  |  |  |  |

| 1011                |                    |  |  |  |  |

| 1000 <sup>(3)</sup> | 64                 |  |  |  |  |

| 0111                | 48                 |  |  |  |  |

| 0110                | 32                 |  |  |  |  |

| 0101 <sup>(4)</sup> | 16                 |  |  |  |  |

| 0100                | 12                 |  |  |  |  |

| 0011                | 8                  |  |  |  |  |

| 0010 <b>(1,2)</b>   | 4                  |  |  |  |  |

| 0001                | 2                  |  |  |  |  |

| 0000                | 1                  |  |  |  |  |

**Note 1:** Refer to Table 4-1 for more information.

# 6.4 Register Definitions: Voltage Regulator Control

# **REGISTER 6-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0                                     | U-0 | U-0               | U-0  | U-0                                                   | U-0              | R/W-0/0 | R/W-1/1  |

|-----------------------------------------|-----|-------------------|------|-------------------------------------------------------|------------------|---------|----------|

| _                                       | —   | —                 | —    | —                                                     | _                | VREGPM  | Reserved |

| bit 7                                   |     |                   |      |                                                       |                  |         | bit 0    |

|                                         |     |                   |      |                                                       |                  |         |          |

| Legend:                                 |     |                   |      |                                                       |                  |         |          |

| R = Readable b                          | oit | W = Writable      | bit  | U = Unimpler                                          | mented bit, read | as '0'  |          |

| u = Bit is unchanged x = Bit is unknown |     |                   | nown | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |          |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared |                                                       |                  |         |          |

bit 7-2 Unimplemented: Read as '0'

VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

- Draws lowest current in Sleep, slower wake-up

- 0 =Normal Power mode enabled in Sleep<sup>(2)</sup>

- Draws higher current in Sleep, faster wake-up

bit 0 **Reserved:** Read as '1'. Maintain this bit set.

Note 1: PIC18F2x/4xK40 only.

bit 1

2: See Section 37.0 "Electrical Specifications".

# PIC18(L)F26/45/46K40

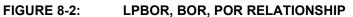

# 8.1 Register Definitions: BOR Control

# REGISTER 8-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN  | —   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |     |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit                  |

|---------|--------------------------------------------------------------|

|         | If BOREN ≠ 01:                                               |

|         | SBOREN is read/write, but has no effect on the BOR.          |

|         | If BOREN = 01:                                               |

|         | 1 = BOR Enabled                                              |

|         | 0 = BOR Disabled                                             |

| bit 6-1 | Unimplemented: Read as '0'                                   |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit             |

|         | 1 = The Brown-out Reset Circuit is active and armed          |

|         | 0 = The Brown-out Reset Circuit is disabled or is warming up |

|         | 5 · · · · · · · · 5 · P                                      |

© 2015-2017 Microchip Technology Inc.

# 8.2 Register Definitions: Power Control

#### R/W/HC-1/q R/W/HC-1/q R/W/HC-1/q R/W/HC-1/q R/W/HC-0/u R/W/HS-0/q R/W/HS-0/q R/W/HC-q/u RI STKOVF STKUNF WDTWV RWDT RMCLR POR BOR bit 7 bit 0 Legend: HC = Bit is cleared by hardware HS = Bit is set by hardware R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit u = Bit is unchanged x = Bit is unknown -m/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared q = Value depends on condition bit 7 STKOVF: Stack Overflow Flag bit 1 = A Stack Overflow occurred (more CALLs than fit on the stack) 0 = A Stack Overflow has not occurred or set to '0' by firmware bit 6 STKUNF: Stack Underflow Flag bit A Stack Underflow occurred (more RETURNS than CALLS) 1 = 0 = A Stack Underflow has not occurred or set to '0' by firmware bit 5 WDTWV: Watchdog Window Violation bit 1 = A WDT window violation has not occurred or set to '1' by firmware 0 = A CLRWDT instruction was issued when the WDT Reset window was closed (set to '0' in hardware when a WDT window violation Reset occurs) bit 4 RWDT: WDT Reset Flag bit 1 = A WDT overflow/time-out Reset has not occurred or set to '1' by firmware 0 = A WDT overflow/time-out Reset has occurred (set to '0' in hardware when a WDT Reset occurs) bit 3 RMCLR: MCLR Reset Flag bit $1 = A \overline{MCLR}$ Reset has not occurred or set to '1' by firmware 0 = A MCLR Reset has occurred (set to '0' in hardware when a MCLR Reset occurs) bit 2 RI: RESET Instruction Flag bit 1 = A RESET instruction has not been executed or set to '1' by firmware 0 = A RESET instruction has been executed (set to '0' in hardware upon executing a RESET instruction) bit 1 POR: Power-on Reset Status bit 1 = No Power-on Reset occurred or set to '1' by firmware 0 = A Power-on Reset occurred (set to '0' in hardware when a Power-on Reset occurs) bit 0 BOR: Brown-out Reset Status bit 1 = No Brown-out Reset occurred or set to '1' by firmware 0 = A Brown-out Reset occurred (set to '0' in hardware when a Brown-out Reset occurs)

### REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

#### REGISTER 9-3: WDTPSL: WWDT PRESCALE SELECT LOW BYTE REGISTER (READ-ONLY)

|                  |       |                      |       |                |                  | •              | ,            |

|------------------|-------|----------------------|-------|----------------|------------------|----------------|--------------|

| R-0/0            | R-0/0 | R-0/0                | R-0/0 | R-0/0          | R-0/0            | R-0/0          | R-0/0        |

|                  |       |                      | PSC   | NT<7:0>        |                  |                |              |

| bit 7            |       |                      |       |                |                  |                | bit 0        |

|                  |       |                      |       |                |                  |                |              |

| Legend:          |       |                      |       |                |                  |                |              |

| R = Readable b   | oit   | W = Writable bit     |       | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | anged | x = Bit is unknow    | n     | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |       | '0' = Bit is cleared | ł     |                |                  |                |              |

#### bit 7-0 **PSCNT<7:0>:** Prescale Select Low Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-4: WDTPSH: WWDT PRESCALE SELECT HIGH BYTE REGISTER (READ-ONLY)

|             |       |       |       |       |       | · ·   |       |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 |  |

| PSCNT<15:8> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       |       |  |

|             |       |       |       |       |       |       |       |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

# bit 7-0 **PSCNT<15:8>:** Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

| U-0             | U-0                         | R/W-0/0               | R/W-0/0                   | U-0              | R/W-0/0               | R/W-0/0               | R/W-0/0               |  |

|-----------------|-----------------------------|-----------------------|---------------------------|------------------|-----------------------|-----------------------|-----------------------|--|

| _               | _                           | TMR0IE <sup>(1)</sup> | IOCIE <sup>(1)</sup>      |                  | INT2IE <sup>(1)</sup> | INT1IE <sup>(1)</sup> | INT0IE <sup>(1)</sup> |  |

| bit 7           | •                           |                       |                           |                  |                       |                       | bit 0                 |  |

|                 |                             |                       |                           |                  |                       |                       |                       |  |

| Legend: IE      |                             |                       |                           |                  |                       |                       |                       |  |

| R = Readable    | bit                         | W = Writable          | bit                       | U = Unimpler     | mented bit, read      | l as '0'              |                       |  |

| -n = Value at F | POR                         | '1' = Bit is set      |                           | '0' = Bit is cle | ared                  | x = Bit is unkr       | nown                  |  |

|                 |                             |                       |                           |                  |                       |                       |                       |  |

| bit 7-6         | Unimplemen                  | ted: Read as '        | )'                        |                  |                       |                       |                       |  |

| bit 5           | TMR0IE: Time                | er0 Interrupt Er      | nable bit <sup>(1)</sup>  |                  |                       |                       |                       |  |

| 1 = Enabled     |                             |                       |                           |                  |                       |                       |                       |  |

|                 | 0 = Disabled                |                       |                           |                  |                       |                       |                       |  |

| bit 4           |                             | pt-on-Change          | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |  |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |  |

| bit 3           |                             | ted: Read as '        | ı'                        |                  |                       |                       |                       |  |

|                 | -                           |                       |                           |                  |                       |                       |                       |  |

| bit 2           |                             | nal Interrupt 2       | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |  |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |  |

| h:+ 1           |                             | nol Interrupt 1       | Enable hit(1)             |                  |                       |                       |                       |  |

| bit 1           |                             | nal Interrupt 1       | Enable bitter             |                  |                       |                       |                       |  |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |  |

| bit 0           |                             | nal Interrupt 0       | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |  |

|                 | 1 = Enabled                 |                       |                           |                  |                       |                       |                       |  |

|                 | 0 = Disabled                |                       |                           |                  |                       |                       |                       |  |

| Note 1: PI      | R0 interrupts ar            | e not disabled        | by the PEIE I             | hit in the INTC  | ON register are       | not disabled b        | v the PEIE bit        |  |

# REGISTER 14-10: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

**Note 1:** PIR0 interrupts are not disabled by the PEIE bit in the INTCON register. are not disabled by the PEIE bit in the INTCON register.

| U-0           | U-0                                                                                  | U-0              | U-0 | U-0                                     | U-0              | R/W-1/1 | R/W-1/1 |

|---------------|--------------------------------------------------------------------------------------|------------------|-----|-----------------------------------------|------------------|---------|---------|

| —             | —                                                                                    | —                | _   | —                                       | —                | CCP2IP  | CCP1IP  |

| bit 7         |                                                                                      |                  |     |                                         |                  |         | bit 0   |

|               |                                                                                      |                  |     |                                         |                  |         |         |

| Legend:       |                                                                                      |                  |     |                                         |                  |         |         |

| R = Readable  | e bit                                                                                | W = Writable     | bit | U = Unimpler                            | mented bit, read | as '0'  |         |

| -n = Value at | POR                                                                                  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                  |         | nown    |

|               |                                                                                      |                  |     |                                         |                  |         |         |

| bit 7-2       | Unimplemen                                                                           | ted: Read as '   | 0'  |                                         |                  |         |         |

| bit 1         | <b>CCP2IP:</b> ECCP2 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |                  |     |                                         |                  |         |         |

| bit 0         |                                                                                      |                  |     |                                         |                  |         |         |

# REGISTER 14-24: IPR6: PERIPHERAL INTERRUPT PRIORITY REGISTER 6

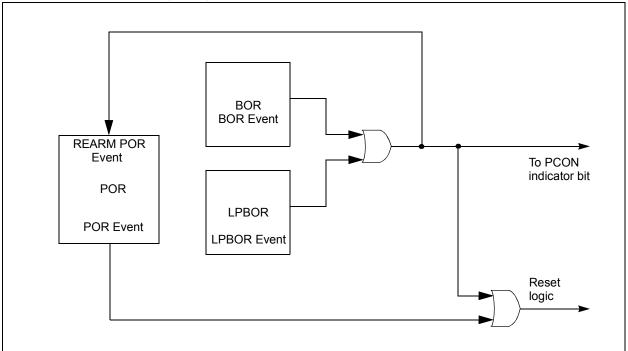

# 15.0 I/O PORTS

#### TABLE 15-1: PORT AVAILABILITY PER DEVICE

| Device            | PORTA | PORTB | PORTC | PORTD | PORTE |

|-------------------|-------|-------|-------|-------|-------|

| PIC18(L)F26K40    | ٠     | ٠     | ٠     |       | ٠     |

| PIC18(L)F45/46K40 | •     | ٠     | ٠     | •     | •     |

Each port has eight registers to control the operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- · TRISx registers (data direction)

- · ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate control)

- · ODCONx registers (open-drain control)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSELx bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 15-1.

# FIGURE 15-1: GENERIC I/O PORT

# **15.4 Register Definitions: Port Control**

| R/W-x/u                 | R/W-x/u | R/W-x/u                           | R/W-x/u | R/W-x/u                         | R/W-x/u          | R/W-x/u  | R/W-x/u |

|-------------------------|---------|-----------------------------------|---------|---------------------------------|------------------|----------|---------|

| Rx7                     | Rx6     | Rx5                               | Rx4     | Rx3                             | Rx2              | Rx1      | Rx0     |

| bit 7                   |         |                                   |         |                                 |                  | •        | bit (   |

|                         |         |                                   |         |                                 |                  |          |         |

| I a su a su al s        |         |                                   |         |                                 |                  |          |         |

| •                       |         |                                   | L 11    |                                 |                  | 1        |         |

| Legend:<br>R = Readable | bit     | W = Writable                      | bit     | U = Unimplen                    | nented bit, read | d as '0' |         |

| •                       |         | W = Writable<br>'0' = Bit is clea |         | U = Unimplen<br>x = Bit is unkr | ,                | d as '0' |         |

REGISTER 15-1: PORTX: PORTX REGISTER<sup>(1)</sup>

bit 7-0 **Rx<7:0>:** Rx7:Rx0 Port I/O Value bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

|       | Device     |               |                    |                    |       |       |                    |       |       |       |

|-------|------------|---------------|--------------------|--------------------|-------|-------|--------------------|-------|-------|-------|

| Name  | 28<br>Pins | 40/44<br>Pins | Bit 7              | Bit 6              | Bit 5 | Bit 4 | Bit 3              | Bit 2 | Bit 1 | Bit 0 |

| PORTA | Х          | Х             | RA7                | RA6                | RA5   | RA4   | RA3                | RA2   | RA1   | RA0   |

| PORTB | Х          | Х             | RB7 <sup>(1)</sup> | RB6 <sup>(1)</sup> | RB5   | RB4   | RB3                | RB2   | RB1   | RB0   |

| PORTC | Х          | Х             | RC7                | RC6                | RC5   | RC4   | RC3                | RC2   | RC1   | RC0   |

| PORTD | Х          |               | _                  | _                  | _     | _     | —                  | _     | _     | —     |

|       |            | Х             | RD7                | RD6                | RD5   | RD4   | RD3                | RD2   | RD1   | RD0   |

| PORTE | Х          |               | _                  | _                  | _     |       | RE3 <sup>(2)</sup> | _     | _     | _     |

|       |            | Х             | _                  | —                  | _     | _     | RE3 <sup>(2)</sup> | RE2   | RE1   | RE0   |

TABLE 15-2: PORT REGISTERS

Note 1: Bits RB6 and RB7 read '1' while in Debug mode.

2: Bit PORTE3 is read-only, and will read '1' when MCLRE = 1 (Master Clear enabled).

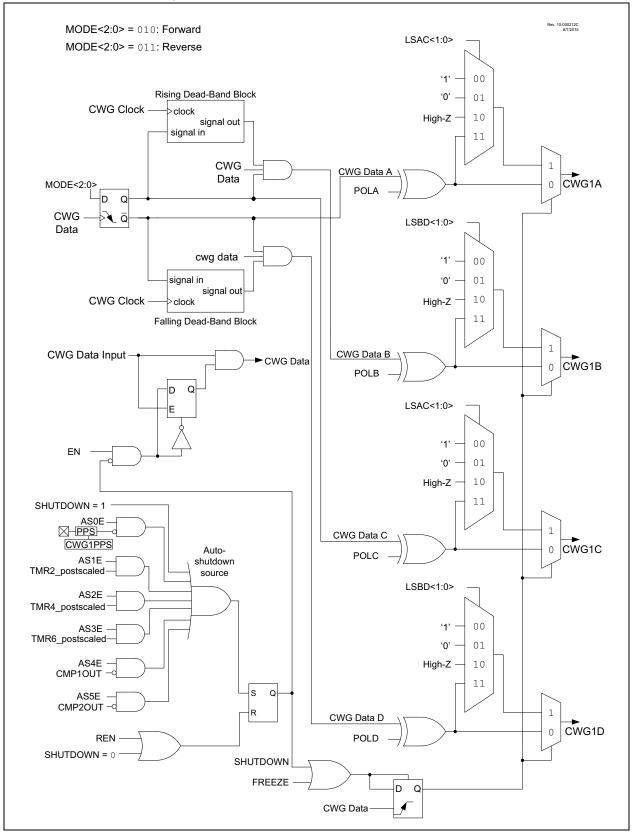

# FIGURE 24-6: SIMPLIFIED CWG BLOCK DIAGRAM (FORWARD AND REVERSE FULL-BRIDGE MODES)

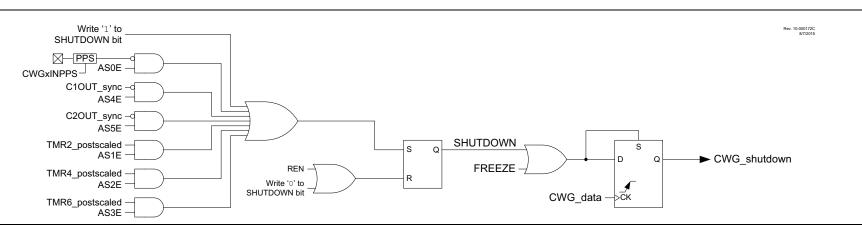

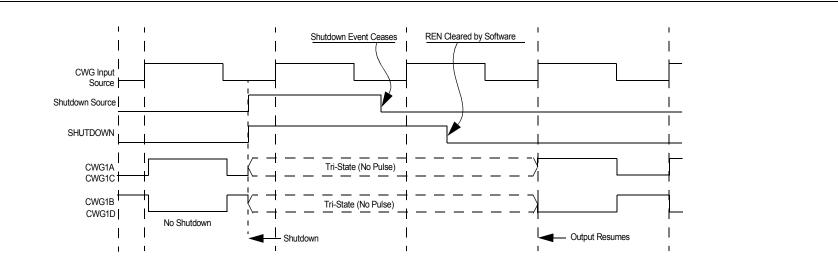

# FIGURE 24-15: SHUTDOWN FUNCTIONALITY, AUTO-RESTART DISABLED (REN = 0, LSAC = 01, LSBD = 01)

| R/W-0        | R/W/HC-0                         | R/W-0                | R/W-0                | R/W-0                       | R/W-0              | R/W-0               | R/W-0              |

|--------------|----------------------------------|----------------------|----------------------|-----------------------------|--------------------|---------------------|--------------------|

| GCEN         | ACKSTAT                          | ACKDT <sup>(1)</sup> | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>         | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7        |                                  |                      | I                    |                             | 1                  |                     | bit (              |

|              |                                  |                      |                      |                             |                    |                     |                    |

| Legend:      | 1.1.1                            |                      |                      |                             |                    |                     |                    |

| R = Readab   |                                  | W = Writable         | DIT                  | HC = Bit is cle             | -                  |                     |                    |

| -n = Value a | at POR                           | '1' = Bit is set     |                      | '0' = Bit is clea           | ared               | x = Bit is unkn     | own                |

| bit 7        | GCEN: Gene                       | eral Call Enable     | bit                  |                             |                    |                     |                    |

|              | Unused in Ma                     | aster mode.          |                      |                             |                    |                     |                    |

| bit 6        | ACKSTAT: A                       | cknowledge Sta       | atus bit (Master     | r Transmit mod              | e only)            |                     |                    |

|              |                                  | edge was not re      |                      | ave                         |                    |                     |                    |

|              |                                  | edge was receiv      |                      |                             |                    |                     |                    |

| bit 5        |                                  | nowledge Data        | bit (Master Re       | ceive mode onl              | y) <sup>(1)</sup>  |                     |                    |

|              | 1 = Not Ackn                     |                      |                      |                             |                    |                     |                    |

|              | 0 = Acknowle                     | •                    |                      | (2)                         |                    |                     |                    |

| bit 4        |                                  | nowledge Sequ        |                      |                             | ning and trans     | mits ACKDT dat      | ha hiti            |

|              |                                  | ically cleared by    |                      |                             | pins and trans     |                     | la Dil,            |

|              |                                  | edge sequence        |                      |                             |                    |                     |                    |

| bit 3        | RCEN: Rece                       | ive Enable bit (     | Master Receive       | e mode only) <sup>(2)</sup> |                    |                     |                    |

|              | 1 = Enables                      | Receive mode f       | or I <sup>2</sup> C  |                             |                    |                     |                    |

|              | 0 = Receive                      |                      |                      |                             |                    |                     |                    |

| bit 2        | PEN: Stop C                      | ondition Enable      | bit <sup>(2)</sup>   |                             |                    |                     |                    |

|              | 1 = Initiates S<br>0 = Stop con  | •                    | n SDAx and S         | CLx pins; autor             | natically cleare   | ed by hardware      |                    |

| bit 1        | RSEN: Repe                       | ated Start Conc      | lition Enable bi     | (2)                         |                    |                     |                    |

|              |                                  | Repeated Start       |                      | DAx and SCLx                | pins; automat      | ically cleared by   | / hardware         |

| bit 0        | SEN: Start C                     | ondition Enable      | bit <sup>(2)</sup>   |                             |                    |                     |                    |

|              | 1 = Initiates S<br>0 = Start con |                      | n SDAx and S         | CLx pins; autor             | natically clear    | ed by hardware      |                    |

|              | The value that wi<br>eceive.     | ill be transmitted   | d when the use       | er initiates an A           | cknowledge se      | equence at the e    | end of a           |

| 2.           | f the $l^2$ C module             | is active these      | bits may not h       | ne set (no snoo             | ling) and the S    | SPvBLIE may n       | ot ho writton      |

# 2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

# 26.8.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 26.9 I<sup>2</sup>C Slave Mode Operation

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of the SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

# 26.9.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 26-5) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register affects the address matching process. See **Section 26.9.9** "**SSP Mask Register**" for more information.

# 26.9.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

# 26.9.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

# 26.9.2 SLAVE RECEPTION

When the R/W bit of a matching received address byte is clear, the R/W bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 26-3.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 26.9.6.2 "10-bit Addressing Mode"** for more detail.

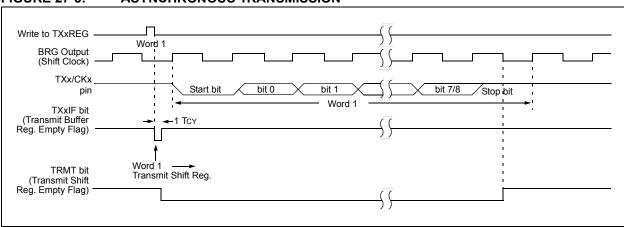

# 27.2.1.5 TSR Status

The TRMT bit of the TXxSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXxREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

# 27.2.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 27.2.2.7 "Address Detection"** for more information on the Address mode.

# 27.2.1.7 Asynchronous Transmission Setup:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXxIF interrupt bit to be set.

- If interrupts are desired, set the TXxIE interrupt enable bit of the PIE3 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXxREG register. This will start the transmission.

#### FIGURE 27-3: ASYNCHRONOUS TRANSMISSION

# 27.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RXx pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. After the ABDOVF bit has been set, the counter continues to count until the fifth rising edge is detected on the RXx pin. Upon detecting the fifth RX edge, the hardware will set the RCxIF interrupt flag and clear the ABDEN bit of the BAUDxCON register. The RCxIF flag can be subsequently cleared by reading the RCxREG register. The ABDOVF flag of the BAUDxCON register can be cleared by software directly.

To terminate the auto-baud process before the RCxIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDxCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

# 27.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDxCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 27-7), and asynchronously if the device is in Sleep mode (Figure 27-8). The interrupt condition is cleared by reading the RCxREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 27.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCxREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

| Name                | Bit 7    | Bit 6        | Bit 5     | Bit 4  | Bit 3   | Bit 2              | Bit 1     | Bit 0           | Register<br>on Page |

|---------------------|----------|--------------|-----------|--------|---------|--------------------|-----------|-----------------|---------------------|

| INTCON              | GIE/GIEH | PEIE/GIEL    | IPEN      | _      | _       | INT2EDG            | INT1EDG   | INT0EDG         | 170                 |

| PIE1                | OSCFIE   | CSWIE        | _         | _      | _       | _                  | ADTIE     | ADIE            | 180                 |

| PIR1                | OSCFIF   | CSWIF        |           | _      | _       | _                  | ADTIF     | ADIF            | 172                 |

| ADCON0              | ADON     | ADCON        | _         | ADCS   | -       | ADFM               | —         | ADGO            | 448                 |

| ADCON1              | ADPPOL   | ADIPEN       | ADGPOL    | _      | _       | _                  | _         | ADDSEN          | 449                 |

| ADCON2              | ADPSIS   | A            | DCRS<2:0  | >      | ADACLR  |                    | ADMD<2:0> | >               | 450                 |

| ADCON3              | -        | A            | DCALC<2:0 | )>     | ADSOI   | A                  | DTMD<2:0  | >               | 451                 |

| ADACT               | _        | _            | —         | —      |         | ADAC               | T<4:0>    |                 | 450                 |

| ADRESH              |          |              |           | ADRES  | SH<7:0> |                    |           |                 | 458, 458            |

| ADRESL              |          |              |           | ADRES  | SL<7:0> |                    |           |                 | 458, 459            |

| ADPREVH             |          |              |           | ADPRE  | V<15:8> |                    |           |                 | 459                 |

| ADPREVL             |          |              |           | ADPRE  | EV<7:0> |                    |           |                 | 460                 |

| ADACCH              |          |              |           | ADACO  | C<15:8> |                    |           |                 | 460                 |

| ADACCL              |          |              |           | ADAC   | C<7:0>  |                    |           |                 | 460                 |

| ADSTPTH             |          | ADSTPT<15:8> |           |        |         |                    |           |                 |                     |

| ADSTPT              |          | ADSTPT<7:0>  |           |        |         |                    |           |                 |                     |

| ADERRL              |          | ADERR<7:0>   |           |        |         |                    |           |                 |                     |

| ADLTHH              |          |              |           | ADLTH  | l<15:8> |                    |           |                 | 462                 |

| ADLTHL              |          |              |           | ADLT   | H<7:0>  |                    |           |                 | 462                 |

| ADUTHH              |          |              |           | ADUTH  | H<15:8> |                    |           |                 | 463                 |

| ADUTHL              |          |              |           | ADUT   | H<7:0>  |                    |           |                 | 463                 |

| ADSTAT              | ADAOV    | ADUTHR       | ADLTHR    | ADMATH |         | ADSTA              | T<3:0>    |                 | 452                 |

| ADCLK               | _        | _            |           |        | ADCS    | 6<5:0>             |           |                 | 453                 |

| ADREF               | _        | _            | _         | ADNREF |         | _                  | ADPRE     | EF<1:0>         | 453                 |

| ADPCH               | —        | _            |           |        | ADPC    | H<5:0>             |           |                 | 454                 |

| ADPRE               |          |              |           | ADPR   | E<7:0>  |                    |           |                 | 455                 |

| ADACQ               |          |              |           | ADAC   | Q<7:0>  |                    |           |                 | 455                 |

| ADCAP               | —        |              | _         |        | ŀ       | ADCAP<4:0          | >         |                 | 456                 |

| ADRPT               |          |              |           |        | T<7:0>  |                    |           |                 | 456                 |

| ADCNT               |          |              |           |        | T<7:0>  |                    |           |                 | 457                 |

| ADFLTRH             |          |              |           |        | R<15:8> |                    |           |                 | 457                 |

| ADFLTRL             | D.(22)   |              | TOTI      |        | R<7:0>  | (5.4.6             |           | <b>D</b> . 1 0: | 457                 |

| FVRCON              | FVREN    | FVRRDY       | TSEN      | TSRNG  | -       | /R<1:0>            |           | R<1:0>          | 423                 |

| DAC1CON1<br>OSCSTAT | EXTOR    | —<br>HFOR    | —<br>MFOR | LFOR   | SOR     | DAC1R<4:0><br>ADOR | ,<br>     | PLLR            | 429<br>39           |

| Legend:             |          |              |           |        |         | -                  |           | FLLK            | 29                  |

| TABLE 31-5: | SUMMARY OF REGISTERS ASSOCIATED WITH ADC |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

Legend: - = unimplemented read as '0'. Shaded cells are not used for the ADC module.

# 32.3 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 32-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 32-2) contains Control bits for the following:

- Interrupt on positive/negative edge enables

- · Positive input channel selection

- Negative input channel selection

# 32.3.1 COMPARATOR ENABLE

Setting the EN bit of the CMxCON0 register enables the comparator for operation. Clearing the CxEN bit disables the comparator resulting in minimum current consumption.

# 32.3.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 17-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

# 32.3.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 32-2 shows the output state versus input conditions, including polarity control.

#### TABLE 32-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### TABLE 37-6: THERMAL CHARACTERISTICS

| Param<br>No. | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |

|--------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                        | 80   | °C/W  | 28-pin SOIC package                                      |

|              |           |                                        | 90   | °C/W  | 28-pin SSOP package                                      |

|              |           |                                        | 27.5 | °C/W  | 28-pin UQFN 4x4 mm package                               |

|              |           |                                        | 27.5 | °C/W  | 28-pin QFN 6x6mm package                                 |

|              |           |                                        | 47.2 | °C/W  | 40-pin PDIP package                                      |

|              |           |                                        | 46   | °C/W  | 44-pin TQFP package                                      |

|              |           |                                        | 24.4 | °C/W  | 44-pin QFN 8x8mm package                                 |

| TH02         | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                        | 24   | °C/W  | 28-pin SOIC package                                      |

|              |           |                                        | 24   | °C/W  | 28-pin SSOP package                                      |

|              |           |                                        | 24   | °C/W  | 28-pin UQFN 4x4mm package                                |

|              |           |                                        | 24   | °C/W  | 28-pin QFN 6x6mm package                                 |

|              |           |                                        | 24.7 | °C/W  | 40-pin PDIP package                                      |

|              |           |                                        | 14.5 | °C/W  | 44-pin TQFP package                                      |

|              |           |                                        | 20   | °C/W  | 44-pin QFN 8x8mm package                                 |

| TH03         | Тјмах     | Maximum Junction Temperature           | 150  | °C    |                                                          |

| TH04         | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O <sup>(3)</sup>                     |

| TH05         | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06         | Pi/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | Pder      | Derated Power                          | _    | W     | Pder = PDmax (Τj - Τa)/θja <sup>(2)</sup>                |

# Standard Operating Conditions (unless otherwise stated)

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

**3:** See absolute maximum ratings for total power dissipation.

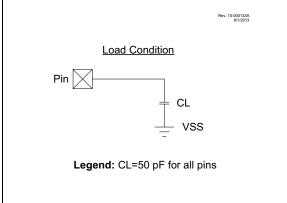

# **37.4** AC Characteristics

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

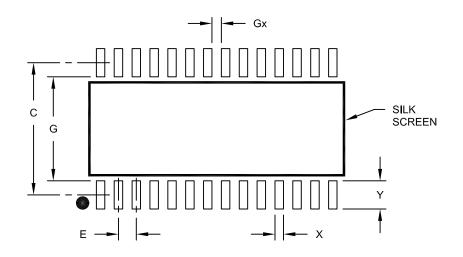

# RECOMMENDED LAND PATTERN

|                          | Units            |      |          |      |  |

|--------------------------|------------------|------|----------|------|--|

| Dimensior                | Dimension Limits |      |          | MAX  |  |

| Contact Pitch            | Contact Pitch E  |      | 1.27 BSC |      |  |

| Contact Pad Spacing      | С                |      | 9.40     |      |  |

| Contact Pad Width (X28)  | Х                |      |          | 0.60 |  |

| Contact Pad Length (X28) | Y                |      |          | 2.00 |  |

| Distance Between Pads    | Gx               | 0.67 |          |      |  |

| Distance Between Pads    | G                | 7.40 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A