Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k40-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection, Device ID and Rev ID.

## 3.1 Configuration Words

There are six Configuration Word bits that allow the user to setup the device with several choices of oscillators, Resets and memory protection options. These are implemented as Configuration Word 1 through Configuration Word 6 at 300000h through 30000Bh.

| Note: | The DEBUG bit in Configuration Words is     |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

## 10.5 Register Definitions: Status

| REGISTER '    | 10-2: STATL                                                          | JS: STATUS                          |                  |                      |                               |                   |           |

|---------------|----------------------------------------------------------------------|-------------------------------------|------------------|----------------------|-------------------------------|-------------------|-----------|

| U-0           | R-1/q                                                                | R-1/q                               | R/W-0/u          | R/W-0/u              | R/W-0/u                       | R/W-0/u           | R/W-0/u   |

| _             | TO                                                                   | PD                                  | Ν                | OV                   | Z                             | DC                | С         |

| oit 7         |                                                                      |                                     |                  |                      |                               |                   | bit       |

|               |                                                                      |                                     |                  |                      |                               |                   |           |

| Legend:       |                                                                      |                                     |                  |                      |                               |                   |           |

| R = Readable  |                                                                      | W = Writable                        |                  | •                    | nented bit, read              |                   |           |

| -n = Value at | POR                                                                  | '1' = Bit is se                     | l                | '0' = Bit is cle     | ared                          | x = Bit is unkr   | nown      |

| bit 7         | Unimplomor                                                           | ited: Read as                       | 0'               |                      |                               |                   |           |

| bit 6         | TO: Time-Ou                                                          |                                     | U                |                      |                               |                   |           |

|               |                                                                      |                                     | execution of CI  | LRWDT <b>OF</b> SLEE | P instruction                 |                   |           |

|               |                                                                      | ime-out occurr                      |                  |                      |                               |                   |           |

| bit 5         | PD: Power-D                                                          | own bit                             |                  |                      |                               |                   |           |

|               |                                                                      |                                     |                  | LRWDT instructi      | on                            |                   |           |

|               | •                                                                    | xecution of the                     |                  |                      |                               |                   |           |

| bit 4         | ALU MSb = 1                                                          |                                     | ned arithmetic   | (2's compleme        | ent); indicates if            | the result is ne  | egative,  |

|               | 1 = The resu                                                         |                                     |                  |                      |                               |                   |           |

|               | 0 = The resu                                                         |                                     |                  |                      |                               |                   |           |

| bit 3         |                                                                      |                                     |                  |                      |                               | an overflow of    | the 7-bit |

|               | -                                                                    |                                     |                  | 7) to change st      |                               |                   |           |

|               | 1 = Overflow 0 = No overflow 1 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = |                                     | urrent signed    | arithmetic oper      | ration                        |                   |           |

| bit 2         | Z: Zero bit                                                          |                                     |                  |                      |                               |                   |           |

|               | 1 = The resu                                                         | It of an arithme                    | etic or logic op | eration is zero      |                               |                   |           |

|               |                                                                      |                                     | •                | eration is not z     |                               |                   |           |

| bit 1         | •                                                                    | •                                   |                  |                      | rF instructions) <sup>(</sup> | 1)                |           |

|               |                                                                      | out from the 4th<br>-out from the 4 |                  | of the result of     | ccurred                       |                   |           |

| bit 0         |                                                                      |                                     |                  | JW, SUBWF instr      | (1,2)                         |                   |           |

|               | •                                                                    | •                                   |                  | bit of the result    | ,                             |                   |           |

|               |                                                                      |                                     |                  | nt bit of the resu   |                               |                   |           |

|               | Borrow, the pola                                                     | arity is reversed                   | d. A subtractio  | n is executed b      | by adding the tw              | vo's complemer    | nt of the |

|               | ond operand.                                                         | <i>.</i>                            |                  |                      |                               |                   | •         |

| 2: For        | Rotate (RRF, RL                                                      | F) Instructions,                    | this bit is load | ded with either      | the high or low-              | -order bit of the | Source    |

## REGISTER 10-2: STATUS: STATUS REGISTER

2: For Rotate (RRF, RLF) instructions, this bit is loaded with either the high or low-order bit of the Source register.

# 14.0 INTERRUPTS

The PIC18(L)F2x/4xK40 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high or low priority level. The high priority interrupt vector is at 0008h and the low priority interrupt vector is at 0018h. A high priority interrupt event will interrupt a low priority interrupt that may be in progress.

The registers for controlling interrupt operation are:

- INTCON

- PIR1, PIR2, PIR3, PIR4, PIR5, PIR6, PIR7

- PIE1, PIE2, PIE3, PIE4, PIE5, PIE6, PIE7

- IPR1, IPR2, IPR3, IPR4, IPR5, IPR6, IPR7

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

## 14.1 Mid-Range Compatibility

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> microcontroller mid-range devices. In Compatibility mode, the interrupt priority bits of the IPRx registers have no effect. The PEIE/GIEL bit of the INTCON register is the global interrupt enable for the peripherals. The PEIE/GIEL bit disables only the peripheral interrupt sources and enables the peripheral interrupt sources when the GIE/GIEH bit is also set. The GIE/GIEH bit of the INTCON register is the global interrupt enable which enables all non-peripheral interrupt sources and disables all interrupt sources, including the peripherals. All interrupts branch to address 0008h in Compatibility mode.

## 14.2 Interrupt Priority

The interrupt priority feature is enabled by setting the IPEN bit of the INTCON register. When interrupt priority is enabled the GIE/GIEH and PEIE/GIEL Global Interrupt Enable bits of Compatibility mode are replaced by the GIEH high priority, and GIEL low priority, global interrupt enables. When the IPEN bit is set, the GEIH bit of the INTCON register enables all interrupts which have their associated bit in the IPRx register set. When the GEIH bit is cleared, then all interrupt sources including those selected as low priority in the IPRx register are disabled.

When both GIEH and GIEL bits are set, all interrupts selected as low priority sources are enabled.

A high priority interrupt will vector immediately to address 00 0008h and a low priority interrupt will vector to address 00 0018h.

## 14.3 Interrupt Response

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. The GIE/GIEH bit is the Global Interrupt Enable when the IPEN bit is cleared. When the IPEN bit is set, enabling interrupt priority levels, the GIEH bit is the high priority Global Interrupt Enable and the GIEL bit is the low priority Global Interrupt Enable. High priority interrupt sources can interrupt a low priority interrupt. Low priority interrupts are not processed while high priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits in the INTCONx and PIRx registers. The interrupt flag bits must be cleared by software before re-enabling interrupts to avoid repeating the same interrupt.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE/GIEH bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the Interrupt-on-change pins, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one-cycle or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bits or the Global Interrupt Enable bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| U-0           | U-0                                                               | U-0                                                                     | U-0         | U-0              | U-0             | R/W-0/0         | R/W-0/0 |  |  |  |  |

|---------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|-------------|------------------|-----------------|-----------------|---------|--|--|--|--|

|               |                                                                   |                                                                         | _           | —                |                 | CCP2IF          | CCP1IF  |  |  |  |  |

| bit 7         |                                                                   |                                                                         |             |                  |                 |                 | bit (   |  |  |  |  |

|               |                                                                   |                                                                         |             |                  |                 |                 |         |  |  |  |  |

| Legend:       |                                                                   |                                                                         |             |                  |                 |                 |         |  |  |  |  |

| R = Readabl   | e bit                                                             | W = Writable I                                                          | bit         |                  | mented bit, rea | id as '0'       |         |  |  |  |  |

| -n = Value at | POR                                                               | '1' = Bit is set                                                        |             | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |

|               |                                                                   |                                                                         |             |                  |                 |                 |         |  |  |  |  |

| bit 7-2       | Unimplemen                                                        | nted: Read as 'o                                                        | )'          |                  |                 |                 |         |  |  |  |  |

| bit 1         | CCP2IF: ECO                                                       | CP2 Interrupt FI                                                        | ag bit      |                  |                 |                 |         |  |  |  |  |

|               | Capture mod                                                       | Capture mode:                                                           |             |                  |                 |                 |         |  |  |  |  |

|               | 1 = A TMR register capture occurred (must be cleared in software) |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               | 0 = No TMR register capture occurred                              |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               | Compare mo                                                        | Compare mode:                                                           |             |                  |                 |                 |         |  |  |  |  |

|               | 1 = A T                                                           | MR register co                                                          | mpare match | occurred (mus    | t be cleared in | i software)     |         |  |  |  |  |

|               | 0 <b>= No</b>                                                     | TMR register c                                                          | ompare matc | h occurred       |                 |                 |         |  |  |  |  |

|               | PWM mode:                                                         |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               | Unused                                                            | d in PWM mode                                                           |             |                  |                 |                 |         |  |  |  |  |

| bit 0         | CCP1IF: ECO                                                       | CP1 Interrupt FI                                                        | ag bit      |                  |                 |                 |         |  |  |  |  |

|               | Capture mode:                                                     |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               | 1 = A TMR register capture occurred (must be cleared in software) |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               | 0 = No TMR register capture occurred                              |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               | Compare mode:                                                     |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               |                                                                   | 1 = A TMR register compare match occurred (must be cleared in software) |             |                  |                 |                 |         |  |  |  |  |

|               | 0 <b>= No</b>                                                     | TMR register c                                                          | ompare matc | h occurred       |                 |                 |         |  |  |  |  |

|               | PWM mode:                                                         |                                                                         |             |                  |                 |                 |         |  |  |  |  |

|               | Unused                                                            | d in PWM mode                                                           |             |                  |                 |                 |         |  |  |  |  |

|               |                                                                   |                                                                         |             |                  |                 |                 |         |  |  |  |  |

## REGISTER 14-8: PIR6: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 6

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |                                                                    |     | -   |                  |         |                 |         |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|------------------|---------|-----------------|---------|--|--|

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-3       Unimplemented: Read as '0'         bit 2       TMR5GIE: TMR5 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 1       TMR3GIE: TMR3 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 0       TMR1GIE: TMR1 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled                                                                                                                                                                                                                                                                 | U-0                                                                          | U-0                                                                | U-0 | U-0 | U-0              | R/W-0/0 | R/W-0/0         | R/W-0/0 |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-3       Unimplemented: Read as '0'         bit 2       TMR5GIE: TMR5 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 1       TMR3GIE: TMR3 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 0       TMR1GIE: TMR1 Gate Interrupt Enable bit         1 = Enabled       1 = Enabled                                                                                                                                                                                                                                                                                | _                                                                            | —                                                                  | —   | _   | _                | TMR5GIE | TMR3GIE         | TMR1GIE |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-3       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 2       TMR5GIE: TMR5 Gate Interrupt Enable bit       1 = Enabled       -         0 = Disabled       0 = Disabled       -       -         bit 1       TMR3GIE: TMR3 Gate Interrupt Enable bit       -       -         1 = Enabled       -       -       -       -         bit 0       TMR1GIE: TMR1 Gate Interrupt Enable bit       -       -       -                                                                                                                                                                                  | bit 7 b                                                                      |                                                                    |     |     |                  |         |                 |         |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-3       Unimplemented: Read as '0'       is cleared       x = Bit is unknown         bit 7-3       Unimplemented: Read as '0'       is cleared       x = Bit is unknown         bit 7-3       Unimplemented: Read as '0'       is cleared       x = Bit is unknown         bit 2       TMR5GIE: TMR5 Gate Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled       is cleared       is cleared         bit 1       TMR3GIE: TMR3 Gate Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled       is cleared       is cleared         bit 0       TMR1GIE: TMR1 Gate Interrupt Enable bit<br>1 = Enabled       is cleared       is cleared | l egend:                                                                     |                                                                    |     |     |                  |         |                 |         |  |  |

| bit 7-3       Unimplemented: Read as '0'         bit 2       TMR5GIE: TMR5 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 1       TMR3GIE: TMR3 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 0       TMR1GIE: TMR1 Gate Interrupt Enable bit         1 = Enabled       1 = Enabled         0 = Disabled       1 = Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |                                                                    |     |     |                  |         |                 |         |  |  |

| bit 2       TMR5GIE: TMR5 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 1       TMR3GIE: TMR3 Gate Interrupt Enable bit         1 = Enabled       0 = Disabled         bit 0       TMR1GIE: TMR1 Gate Interrupt Enable bit         1 = Enabled       1 = Enabled         0 = Disabled       0 = Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -n = Value at POR '1' = Bit is set                                           |                                                                    |     |     | '0' = Bit is cle | ared    | x = Bit is unkr | nown    |  |  |

| bit 0 TMR1GIE: TMR1 Gate Interrupt Enable bit 1 = Enabled i = Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 2 TMR5GIE: TMR5 Gate Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                                                                    |     |     |                  |         |                 |         |  |  |

| 1 = Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 = Enabled                                                                  |                                                                    |     |     |                  |         |                 |         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 0                                                                        | it 0 <b>TMR1GIE:</b> TMR1 Gate Interrupt Enable bit<br>1 = Enabled |     |     |                  |         |                 |         |  |  |

## REGISTER 14-15: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

| R/W-0/u                                                                                                                                                                                                                   | R/W-0/u                                                                                                                                                                                                                                                                                                                   | R/W-0/u                         | R/W-0/u                       | R/W-0/u             | R-x              | U-0             | U-0   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------|---------------------|------------------|-----------------|-------|

| GE                                                                                                                                                                                                                        | GPOL                                                                                                                                                                                                                                                                                                                      | GTM                             | GSPM                          | GGO/DONE            | GVAL             |                 | _     |

| bit 7                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                         |                                 |                               |                     |                  |                 | bit C |

| Legend:                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                           |                                 |                               |                     |                  |                 |       |

| R = Readable                                                                                                                                                                                                              | e bit                                                                                                                                                                                                                                                                                                                     | W = Writable                    | bit                           | U = Unimpleme       | nted bit, read a | ıs '0'          |       |

| -n = Value at                                                                                                                                                                                                             | POR                                                                                                                                                                                                                                                                                                                       | '1' = Bit is se                 | t                             | '0' = Bit is cleare |                  | x = Bit is unkr | nown  |

| bit 7                                                                                                                                                                                                                     | If TMRxON =<br>1 = Timerx<br>0 = Timerx<br>If TMRxON =                                                                                                                                                                                                                                                                    | counting is co<br>is always cou | ontrolled by th               | e Timerx gate fur   | ction            |                 |       |

| bit 6                                                                                                                                                                                                                     | <ul> <li>GPOL: Timerx Gate Polarity bit</li> <li>1 = Timerx gate is active-high (Timerx counts when gate is high)</li> <li>0 = Timerx gate is active-low (Timerx counts when gate is low)</li> </ul>                                                                                                                      |                                 |                               |                     |                  |                 |       |

| bit 5 <b>GTM</b> : Timerx Gate Toggle Mode bit<br>1 = Timerx Gate Toggle mode is enabled<br>0 = Timerx Gate Toggle mode is disabled and Toggle flip-flop is cleared<br>Timerx Gate Flip Flop Toggles on every rising edge |                                                                                                                                                                                                                                                                                                                           |                                 |                               |                     |                  |                 |       |

| bit 4                                                                                                                                                                                                                     | <ul> <li>GSPM: Timerx Gate Single Pulse Mode bit</li> <li>1 = Timerx Gate Single Pulse mode is enabled and is controlling Timerx gate)</li> <li>0 = Timerx Gate Single Pulse mode is disabled</li> </ul>                                                                                                                  |                                 |                               |                     |                  |                 |       |

| bit 3                                                                                                                                                                                                                     | <ul> <li>GGO/DONE: Timerx Gate Single Pulse Acquisition Status bit</li> <li>1 = Timerx Gate Single Pulse Acquisition is ready, waiting for an edge</li> <li>0 = Timerx Gate Single Pulse Acquisition has completed or has not been started.</li> <li>This bit is automatically cleared when TxGSPM is cleared.</li> </ul> |                                 |                               |                     |                  |                 |       |

| bit 2                                                                                                                                                                                                                     | GVAL: Time<br>Indicates the                                                                                                                                                                                                                                                                                               | rx Gate Currer                  | nt State bit<br>of the Timerx | gate that could b   |                  | MRxH:TMRxL      |       |

| bit 1-0                                                                                                                                                                                                                   | Unaffected by Timerx Gate Enable (TMRxGE)<br>Unimplemented: Read as '0'                                                                                                                                                                                                                                                   |                                 |                               |                     |                  |                 |       |

## REGISTER 19-2: TxGCON: TIMERx GATE CONTROL REGISTER

## 19.9 Timer1/3/5 Interrupt

The Timer1/3/5 register pair (TMRxH:TMRxL) increments to FFFFh and rolls over to 0000h. When Timer1/3/5 rolls over, the Timer1/3/5 interrupt flag bit of the PIR4 register is set. To enable the interrupt-on-rollover, you must set these bits:

- TMRxON bit of the TxCON register

- TMRxIE bits of the PIE4 register

- PEIE/GIEL bit of the INTCON register

- · GIE/GIEH bit of the INTCON register

The interrupt is cleared by clearing the TMRxIF bit in the Interrupt Service Routine.

For more information on selecting high or low priority status for the Timer1/3/5 Overflow Interrupt, see **Section 14.0 "Interrupts"**.

Note: The TMRxH:TMRxL register pair and the TMRxIF bit should be cleared before enabling interrupts.

## 19.10 Timer1/3/5 Operation During Sleep

Timer1/3/5 can only operate during Sleep when set up in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMRxON bit of the TxCON register must be set

- TMRxIE bit of the PIE4 register must be set

- PEIE/GIEL bit of the INTCON register must be set

- TxSYNC bit of the TxCON register must be set

- Configure the TMRxCLK register for using secondary oscillator as the clock source

- Enable the SOSCEN bit of the OSCEN register (Register 4-7)

The device will wake-up on an overflow and execute the next instruction. If the GIE/GIEH bit of the INTCON register is set, the device will call the Interrupt Service Routine.

The secondary oscillator will continue to operate in Sleep regardless of the  $\overline{\text{TxSYNC}}$  bit setting.

## 19.11 CCP Capture/Compare Time Base

The CCP modules use the TMRxH:TMRxL register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMRxH:TMRxL register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value in the CCPRxH:CCPRxL register pair matches the value in the TMRxH:TMRxL register pair. This event can be a Special Event Trigger.

For more information, see Section 21.0 "Capture/Compare/PWM Module".

## **19.12 CCP Special Event Trigger**

When any of the CCP's are configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1/3/5 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1/3/5.

Timer1/3/5 should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1/3/5 can cause a Special Event Trigger to be missed.

In the event that a write to TMRxH or TMRxL coincides with a Special Event Trigger from the CCP, the write will take precedence.

# PIC18LF26/45/46K40

| REGISTER 2                                                           | 4-5: CWG1                                                                            | STR <sup>(1)</sup> : CWG                   | STEERING         | CONTROL F           | REGISTER            |                     |                     |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------|------------------|---------------------|---------------------|---------------------|---------------------|--|

| R/W-0/0                                                              | R/W-0/0                                                                              | R/W-0/0                                    | R/W-0/0          | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |  |

| OVRD                                                                 | OVRC                                                                                 | OVRB                                       | OVRA             | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |  |

| bit 7 bit                                                            |                                                                                      |                                            |                  |                     |                     |                     |                     |  |

| Legend:                                                              |                                                                                      |                                            |                  |                     |                     |                     |                     |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                      |                                            |                  |                     |                     |                     |                     |  |

| u = Bit is unch                                                      | anged                                                                                | x = Bit is unkr                            | nown             | •                   | at POR and BO       |                     | ther Resets         |  |

| '1' = Bit is set                                                     | 5.1                                                                                  | '0' = Bit is cle                           | ared             | a = Value der       | pends on condit     | ion                 |                     |  |

|                                                                      |                                                                                      | 0 2010 010                                 |                  | 9 10.00 001         |                     |                     |                     |  |

| bit 7                                                                | OVRD: Steeri                                                                         | ng Data D bit                              |                  |                     |                     |                     |                     |  |

| bit 6                                                                | OVRC: Steeri                                                                         | OVRC: Steering Data C bit                  |                  |                     |                     |                     |                     |  |

| bit 5                                                                | OVRB: Steering Data B bit                                                            |                                            |                  |                     |                     |                     |                     |  |

| bit 4                                                                | OVRA: Steeri                                                                         | OVRA: Steering Data A bit                  |                  |                     |                     |                     |                     |  |

| bit 3                                                                | STRD: Steering                                                                       | STRD: Steering Enable bit D <sup>(2)</sup> |                  |                     |                     |                     |                     |  |

|                                                                      | 1 = CWG1D o                                                                          | output has the                             | CWG data inp     | ut waveform wi      | ith polarity contr  | ol from POLD        | bit                 |  |

|                                                                      | 0 = CWG1D c                                                                          | output is assigr                           | ned to value of  | OVRD bit            |                     |                     |                     |  |

| bit 2                                                                | STRC: Steering                                                                       | ng Enable bit C                            | <sub>)</sub> (2) |                     |                     |                     |                     |  |

|                                                                      | 1 = CWG1C o                                                                          | output has the                             | CWG data inp     | ut waveform wi      | ith polarity contr  | ol from POLC        | bit                 |  |

|                                                                      |                                                                                      | output is assigr                           |                  | OVRC bit            |                     |                     |                     |  |

| bit 1                                                                | STRB: Steering                                                                       | ng Enable bit E                            | 3(2)             |                     |                     |                     |                     |  |

|                                                                      | 1 = CWG1B output has the CWG data input waveform with polarity control from POLB bit |                                            |                  |                     |                     |                     |                     |  |

|                                                                      |                                                                                      | output is assigr                           |                  | OVRB bit            |                     |                     |                     |  |

| bit 0                                                                | STRA: Steering                                                                       | ng Enable bit A                            | (2)              |                     |                     |                     |                     |  |

|                                                                      | 1 = CWG1A c                                                                          | output has the                             | CWG data inp     | ut waveform wi      | th polarity contr   | ol from POLA I      | oit                 |  |

|                                                                      | 0 = CWG1A c                                                                          | output is assigr                           | ed to value of   | OVRA bit            |                     |                     |                     |  |

| Note 1: The                                                          | e bits in this reg                                                                   | ister apply only                           | when MODE        | <2:0> = 00x (F      | Register 24-1, St   | teering modes)      |                     |  |

**2:** This bit is double-buffered when MODE < 2:0 > = 0.01.

4.

## 25.6 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCON1 register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCON1 register.

## 25.7 Programmable Modulator Data

The MDBIT of the MDCON0 register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

## 25.8 Modulated Output Polarity

The modulated output signal provided on the DSM pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON0 register.

## 25.9 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep. Refer to **Section 6.0 "Power-Saving Operation Modes"** for more details.

## 25.10 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

## 25.11 Peripheral Module Disable

The DSM module can be completely disabled using the PMD module to achieve maximum power saving. The DSMMD bit of PMD5 (Register 7-6) when set disables the DSM module completely. When enabled again all the registers of the DSM module default to POR status.

## 26.0 MASTER SYNCHRONOUS SERIAL PORT MODULE

Note: The PIC18(L)F26/45/46K40 devices have two MSSP. Therefore, all information in this section refers to both MSSP1 and MSSP2.

## 26.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The PIC18(L)F26/45/46K40 devices have two MSSP modules that can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

The  $I^2C$  interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- 7-bit and 10-bit addressing

- Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- · Address masking

- Address Hold and Data Hold modes

- Selectable SDA hold times

#### 26.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 26-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### 26.9.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 26.9.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 26.9.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 26.9.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 26-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

**Note 1:** If the master ACKs the clock will be stretched.

ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

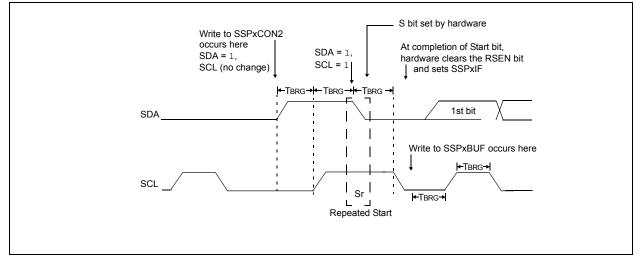

## 26.10.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 26-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## 26.10.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCL low and SDA unchanged (Figure 26-28).

## FIGURE 26-27: REPEATED START CONDITION WAVEFORM

## 27.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RXx pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. After the ABDOVF bit has been set, the counter continues to count until the fifth rising edge is detected on the RXx pin. Upon detecting the fifth RX edge, the hardware will set the RCxIF interrupt flag and clear the ABDEN bit of the BAUDxCON register. The RCxIF flag can be subsequently cleared by reading the RCxREG register. The ABDOVF flag of the BAUDxCON register can be cleared by software directly.

To terminate the auto-baud process before the RCxIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDxCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

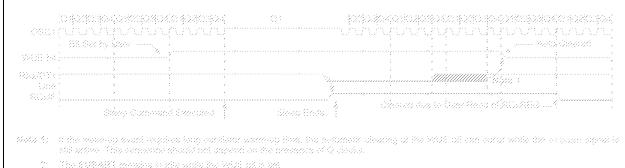

## 27.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDxCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 27-7), and asynchronously if the device is in Sleep mode (Figure 27-8). The interrupt condition is cleared by reading the RCxREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 27.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### <u>WUE Bit</u>

The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCxREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

## FIGURE 27-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

|                                                            | earad   | , Assold                                                      | · · · · · · · · · · · · · · · · · · · | نجب المنة نبة<br>•<br>****** |            |                 | <br>a waqa | j                   |         | wyy.       | fur.        |              | i U U<br>Ritiya                         |                  |

|------------------------------------------------------------|---------|---------------------------------------------------------------|---------------------------------------|------------------------------|------------|-----------------|------------|---------------------|---------|------------|-------------|--------------|-----------------------------------------|------------------|

|                                                            |         |                                                               | <br><br>/                             |                              |            | -<br>-<br>-     |            |                     |         |            | 2.<br>      | ····         |                                         |                  |

| 1                                                          |         | :<br>;<br>*                                                   |                                       |                              |            |                 |            | \$///2;::<br>:<br>: |         | :          | 3<br>5<br>3 |              |                                         |                  |

| Rom 1. The BURARY vertices to bits while the WEB As is set | <i></i> | 1038802 <sub>.</sub><br>[[]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]] | -6 Ç<br>111111.                       | an teorit.<br>IIIIIIIIIIIII  | 308303<br> | iposodi<br>MMMM |            | ///////             |         |            |             |              | /////////////////////////////////////// |                  |

|                                                            |         |                                                               |                                       |                              |            |                 |            |                     | 88.6 se | s (>s V/C) | ide whi     | eensees in i | 98A80                                   | ose (t. 1198-33) |

© 2015-2017 Microchip Technology Inc.

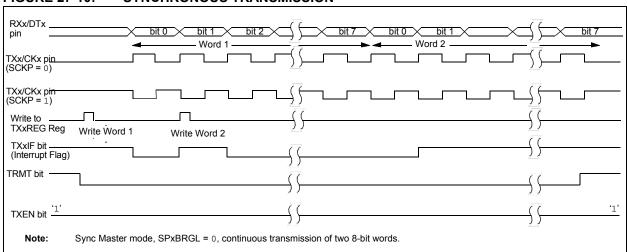

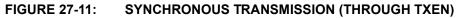

## FIGURE 27-10: SYNCHRONOUS TRANSMISSION

# PIC18(L)F26/45/46K40

## 31.4.1 CVD OPERATION

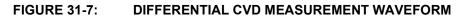

A CVD operation begins with the ADC's internal and hold capacitor sample (С<sub>НОГ</sub>) being disconnected from the path which connects it to the external capacitive sensor node. While disconnected, CHOLD is precharged to VDD or Vss, while the path to the sensor node is also discharged to VDD or VSS. Typically, this node is discharged to the level opposite that of CHOLD. When the precharge phase is complete, the VDD/VSS bias paths for the two nodes are shut off and CHOLD and the path to the external sensor node are re-connected, at which time the acquisition phase of the CVD operation begins. During acquisition, a capacitive voltage divider is formed between the precharged CHOLD and sensor nodes, which results in a final voltage level setting on CHOLD which is determined by the capacitances and precharge levels of the two nodes. After acquisition, the ADC converts the voltage level on CHOLD. This process is then repeated with the selected precharge levels for both the CHOLD and the inverted sensor nodes. Figure 31-7 shows the waveform for two inverted CVD measurements, which is known as differential CVD measurement.

## 33.10 Register Definitions: HLVD Control

Long bit name prefixes for the HLVD peripheral is shown in Table 33-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

## TABLE 33-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| HLVD       | HLVD            |

#### REGISTER 33-1: HLVDCON1: LOW-VOLTAGE DETECT CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | -   |         | SEL<    | <3:0>   |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:           |                  |                       |                      |

|-------------------|------------------|-----------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | u = Bit is unchanged |

#### bit 7-4 Unimplemented: Read as '0'

## bit 3-0 SEL<3:0>: High/Low Voltage Detection Limit Selection bits

| SEL<3:0> | Typical Voltage |

|----------|-----------------|

| 1111     | Reserved        |

| 1110     | 4.63V           |

| 1101     | 4.32V           |

| 1100     | 4.12V           |

| 1011     | 3.91V           |

| 1010     | 3.71V           |

| 1001     | 3.60V           |

| 1000     | 3.4V            |

| 0111     | 3.09V           |

| 0110     | 2.88V           |

| 0101     | 2.78V           |

| 0100     | 2.57V           |

| 0011     | 2.47V           |

| 0010     | 2.26V           |

| 0001     | 2.06V           |

| 0000     | 1.85V           |

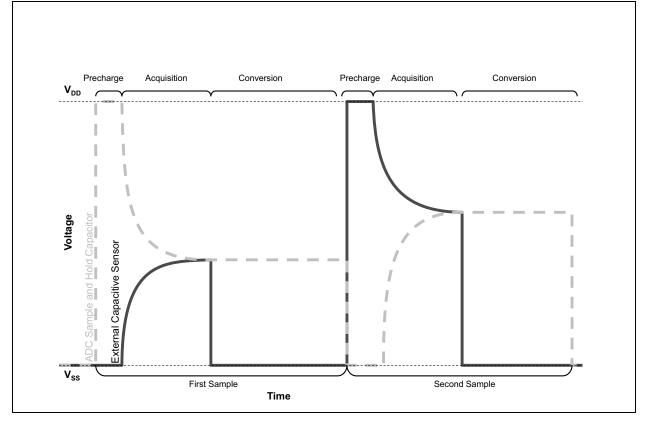

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |      |      |  |

|--------------------------|----|-------------|------|------|--|

| Dimension Limits         |    | MIN         | NOM  | MAX  |  |

| Contact Pitch            | Е  | 1.27 BSC    |      |      |  |

| Contact Pad Spacing      | С  |             | 9.40 |      |  |

| Contact Pad Width (X28)  | Х  |             |      | 0.60 |  |

| Contact Pad Length (X28) | Y  |             |      | 2.00 |  |

| Distance Between Pads    | Gx | 0.67        |      |      |  |

| Distance Between Pads    | G  | 7.40        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

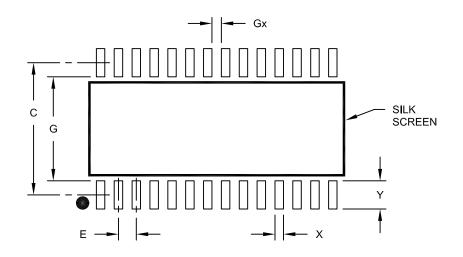

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |  |

|----------------------------|----|-------------|------|------|--|

| Dimension Limits           |    | MIN         | NOM  | MAX  |  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |  |

| Optional Center Pad Width  | W2 |             |      | 4.25 |  |

| Optional Center Pad Length | T2 |             |      | 4.25 |  |

| Contact Pad Spacing        | C1 |             | 5.70 |      |  |

| Contact Pad Spacing        | C2 |             | 5.70 |      |  |

| Contact Pad Width (X28)    | X1 |             |      | 0.37 |  |

| Contact Pad Length (X28)   | Y1 |             |      | 1.00 |  |

| Distance Between Pads      | G  | 0.20        |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A