Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

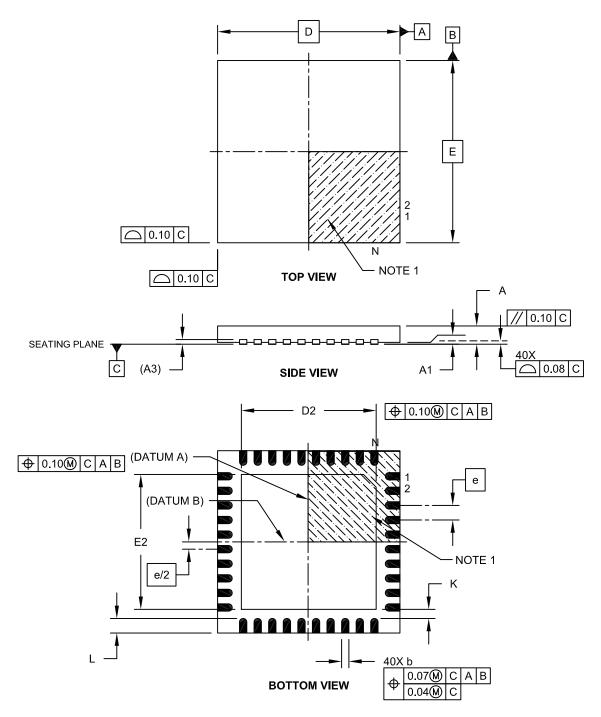

| Mounting Type              | Surface Mount                                                              |

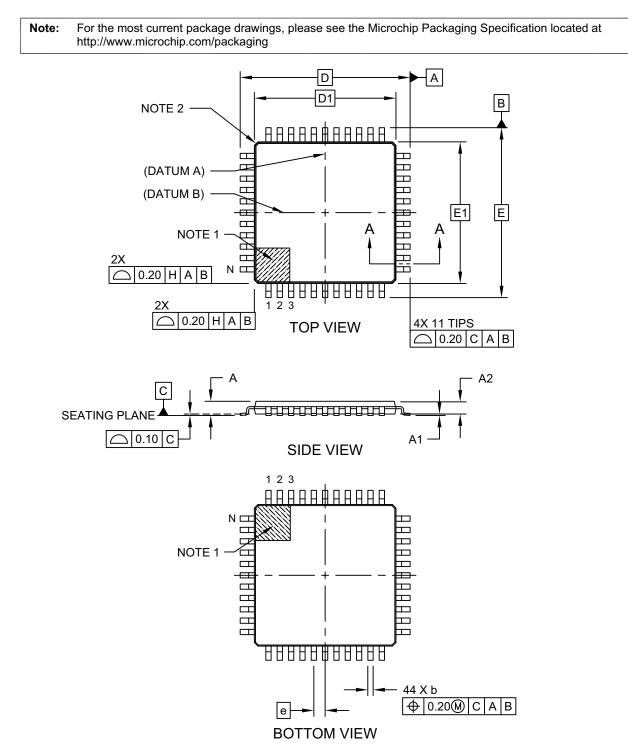

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k40-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|               | • • ••g                                                                |                  |                |                    |                  |                |          |  |

|---------------|------------------------------------------------------------------------|------------------|----------------|--------------------|------------------|----------------|----------|--|

| U-1           | U-1                                                                    | R/W-1            | U-1            | R/W-1              | U-1              | U-1            | R/W-1    |  |

| _             | _                                                                      | FCMEN            | _              | CSWEN              |                  | _              | CLKOUTEN |  |

| bit 7         | ·                                                                      |                  |                |                    | •                |                | bit 0    |  |

|               |                                                                        |                  |                |                    |                  |                |          |  |

| Legend:       |                                                                        |                  |                |                    |                  |                |          |  |

| R = Readabl   | le bit                                                                 | W = Writable     | bit            | U = Unimple        | mented bit, read | d as '1'       |          |  |

| -n = Value fo | or blank device                                                        | '1' = Bit is set |                | '0' = Bit is cle   | eared            | x = Bit is unk | nown     |  |

|               |                                                                        |                  |                |                    |                  |                |          |  |

| bit 7-6       | Unimplemen                                                             | ted: Read as '1  | 3              |                    |                  |                |          |  |

| bit 5         |                                                                        | Safe Clock Mor   | nitor Enable b | it                 |                  |                |          |  |

|               | 1 = FSCM tin<br>0 = FSCM tin                                           |                  |                |                    |                  |                |          |  |

| bit 4         | Unimplemen                                                             | ted: Read as '1  | ,              |                    |                  |                |          |  |

| bit 3         | CSWEN: Cloo                                                            | ck Switch Enabl  | e bit          |                    |                  |                |          |  |

|               |                                                                        | NOSC and ND      |                |                    |                  |                |          |  |

| <b>h</b> #0.4 |                                                                        | C and NDIV bit   |                | nanged by use      | er soπware       |                |          |  |

| bit 2-1       | Unimplemented: Read as '1'                                             |                  |                |                    |                  |                |          |  |

| bit 0         | CLKOUTEN: Clock Out Enable bit                                         |                  |                |                    |                  |                |          |  |

|               | <u>If FEXTOSC = HS, XT, LP, then this bit is ignored</u><br>Otherwise: |                  |                |                    |                  |                |          |  |

|               |                                                                        | function is disa | bled; I/O or o | scillator function | on on OSC2       |                |          |  |

|               | 0 = CLKOUT                                                             | function is enal | bled; FOSC/4   | clock appears      | s at OSC2        |                |          |  |

|               |                                                                        |                  |                |                    |                  |                |          |  |

#### REGISTER 3-2: Configuration Word 1H (30 0001h): Oscillators

| Register 0-7. | Connige |       | 1 4E (00 000) |       |       | cuon  |       |

|---------------|---------|-------|---------------|-------|-------|-------|-------|

| R/W-1         | R/W-1   | R/W-1 | R/W-1         | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| WRT7          | WRT6    | WRT5  | WRT4          | WRT3  | WRT2  | WRT1  | WRT0  |

| bit 7         |         |       |               |       | •     |       | bit 0 |

|               |         |       |               |       |       |       |       |

# Register 3-7: Configuration Word 4L (30 0006h): Memory Write Protection

| Legend:                     |                  |                       |                    |

|-----------------------------|------------------|-----------------------|--------------------|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit | , read as '1'      |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0

WRT<7:0>: User NVM Self-Write Protection bits<sup>(1)</sup>

1 = Corresponding Memory Block NOT write-protected

0 = Corresponding Memory Block write-protected

Note 1: Refer to Table 10-2 for details on implementation of the individual WRT bits.

#### Register 3-8: Configuration Word 4H (30 0007h): Memory Write Protection

| U-1   | U-1 | R/W-1 | R/W-1 | U-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-----|-------|-------|-------|

|       | _   | LVP   | SCANE | —   | WRTD  | WRTB  | WRTC  |

| bit 7 |     |       |       |     |       |       | bit 0 |

| Legend:                     |                  |                            |                    |

|-----------------------------|------------------|----------------------------|--------------------|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | d as '1'           |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

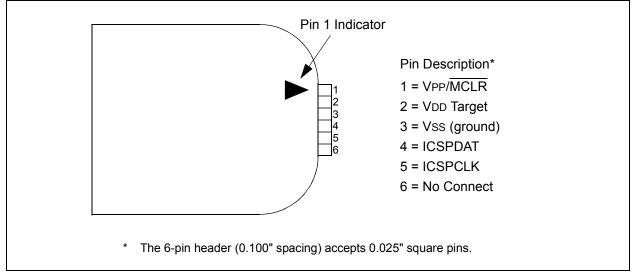

| bit 7-6 | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <ul> <li>LVP: Low-Voltage Programming Enable bit</li> <li>1 = Low-voltage programming enabled. MCLR/VPP pin function is MCLR. MCLRE Configuration bit is ignored.<br/>The LVP bit cannot be written (to zero) while operating from the LVP programming interface. The purpose of this rule is to prevent the user from dropping out of LVP mode while programming from LVP mode, or accidentally eliminating LVP mode from the Configuration state.</li> <li>0 = HV on MCLR/VPP must be used for programming</li> </ul> |

| bit 4   | <ul> <li>SCANE: Scanner Enable bit</li> <li>1 = Scanner module is available for use, SCANMD bit enables the module</li> <li>0 = Scanner module is NOT available for use, SCANMD bit is ignored</li> </ul>                                                                                                                                                                                                                                                                                                               |

| bit 3   | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 2   | <ul> <li>WRTD: Data EEPROM Write Protection bit</li> <li>1 = Data EEPROM NOT write-protected</li> <li>0 = Data EEPROM write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

| bit 1   | WRTB: Boot Block Write Protection bit<br>1 = Boot Block NOT write-protected<br>0 = Boot Block write-protected                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 0   | <ul> <li>WRTC: Configuration Register Write Protection bit</li> <li>1 = Configuration Register NOT write-protected</li> <li>0 = Configuration Register write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

## 8.3 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

# 8.4 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 8-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV<1:0> bits in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Table 37-11 for more information.

#### 8.4.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 8.4.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

# 8.4.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 8.4.4 BOR AND BULK ERASE

BOR is forced ON during PFM Bulk Erase operations to make sure that the system code protection cannot be compromised by reducing VDD.

During Bulk Erase, the BOR is enabled at 2.45V for F and LF devices, even if it is configured to some other value. If VDD falls, the erase cycle will be aborted, but the device will not be reset.

# 8.14 Power Control (PCON0) Register

The Power Control (PCON0) register contains flag bits to differentiate between a:

- Brown-out Reset (BOR)

- Power-on Reset (POR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Window Violation (WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON0 register bits are shown in Register 8-2.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-3).

Software should reset the bit to the inactive state after restart (hardware will not reset the bit).

Software may also set any PCON0 bit to the active state, so that user code may be tested, but no Reset action will be generated.

| Name    | Bit 7  | Bit 6  | Bit 5                  | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|---------|--------|--------|------------------------|------------|-------|-------|-------|--------|---------------------|

| BORCON  | SBOREN |        |                        |            |       |       |       | BORRDY | 75                  |

| PCON0   | STKOVF | STKUNF | WDTWV                  | RWDT       | RMCLR | RI    | POR   | BOR    | 76                  |

| STATUS  | _      | TO     | PD                     | Ν          | OV    | Z     | DC    | С      | 118                 |

| WDTCON0 | _      | _      |                        | WDTPS<4:0> |       |       | SEN   | 85     |                     |

| WDTCON1 |        | W      | DTCS<2:0> — WINDOW<2:0 |            |       |       | )>    | 86     |                     |

TABLE 8-4: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

#### **REGISTER 11-5: NVMDAT: DATA EEPROM MEMORY DATA**

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|------------------|---------|-------------------|---------|------------------|------------------|----------|---------|

|                  |         |                   | NVMD    | AT<7:0>          |                  |          |         |

| bit 7            |         |                   |         |                  |                  |          | bit 0   |

|                  |         |                   |         |                  |                  |          |         |

| Legend:          |         |                   |         |                  |                  |          |         |

| R = Readable     | bit     | W = Writable I    | oit     | U = Unimpler     | nented bit, read | d as '0' |         |

| x = Bit is unkne | own     | '0' = Bit is clea | ared    | '1' = Bit is set |                  |          |         |

| -n = Value at F  | POR     |                   |         |                  |                  |          |         |

bit 7-0 **NVMDAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

#### TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

| Name                   | Bit 7          | Bit 6                                        | Bit 5     | Bit 4        | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Register<br>on Page |

|------------------------|----------------|----------------------------------------------|-----------|--------------|---------------|-------------|---------|---------|---------------------|

| NVMCON1                | NVMRE          | G<1:0>                                       | _         | FREE         | WRERR         | WREN        | WR      | RD      | 145                 |

| NVMCON2                | Unlock Pattern |                                              |           |              |               |             |         |         |                     |

| NVMADRL                |                |                                              |           | NVMA         | .DR<7:0>      |             |         |         | 146                 |

| NVMADRH <sup>(1)</sup> | _              | —                                            | —         | —            | _             | —           | NVMA    | DR<9:8> | 146                 |

| NVMDAT                 |                |                                              |           | NVME         | OAT<7:0>      |             |         |         | 147                 |

| TBLPTRU                | _              | Program Memory Table Pointer (TBLPTR<21:16>) |           |              |               |             |         |         | 127*                |

| TBLPTRH                |                |                                              | Program N | lemory Table | e Pointer (TB | LPTR<15:8>) |         |         | 127*                |

| TBLPTRL                |                |                                              | Program I | Memory Table | e Pointer (TB | LPTR<7:0>)  |         |         | 127*                |

| TABLAT                 |                |                                              |           | TA           | BLAT          |             |         |         | 126*                |

| INTCON                 | GIE/GIEH       | PEIE/GIEL                                    | IPEN      | —            | _             | INT2EDG     | INT1EDG | INT0EDG | 170                 |

| PIE7                   | SCANIE         | CRCIE                                        | NVMIE     | —            | —             | —           | —       | CWG1IE  | 186                 |

| PIR7                   | SCANIF         | CRCIF                                        | NVMIF     | _            | _             | _           | _       | CWG1IF  | 178                 |

| IPR7                   | SCANIP         | CRCIP                                        | NVMIP     | —            | —             | _           | —       | CWG1IP  | 194                 |

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

\*Page provides register information.

Note 1: The NVMADRH register is not implemented on PIC18(L)F26/45/46K40.

|                                                                                                                                                |                                                  |                  |          | =                |                  |                 |         |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|----------|------------------|------------------|-----------------|---------|

| R/W-0/0                                                                                                                                        | R/W-0/0                                          | R/W-0/0          | U-0      | U-0              | U-0              | U-0             | R/W-0/0 |

| SCANIE                                                                                                                                         | CRCIE                                            | NVMIE            | _        | —                | —                | _               | CWG1IE  |

| bit 7                                                                                                                                          |                                                  |                  |          |                  |                  |                 | bit 0   |

|                                                                                                                                                |                                                  |                  |          |                  |                  |                 |         |

| Legend:                                                                                                                                        |                                                  |                  |          |                  |                  |                 |         |

| R = Readable                                                                                                                                   | bit                                              | W = Writable     | bit      | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at                                                                                                                                  | POR                                              | '1' = Bit is set |          | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7 SCANIE: SCAN Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled<br>bit 6 CRCIE: CRC Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                                                  |                  |          |                  |                  |                 |         |

| bit 5 NVMIE: NVM Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled                                                                           |                                                  |                  |          |                  |                  |                 |         |

| bit 4-1                                                                                                                                        | it 4-1 Unimplemented: Read as '0'                |                  |          |                  |                  |                 |         |

| bit 0                                                                                                                                          | <b>CWG1IE:</b> CW<br>1 = Enabled<br>0 = Disabled | /G Interrupt En  | able bit |                  |                  |                 |         |

# REGISTER 14-17: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

# 19.2 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1/3/5 is enabled by configuring the ON and GE bits in the TxCON and TxGCON registers, respectively. Table 19-2 displays the Timer1/3/5 enable selections.

# TABLE 19-2:TIMER1/3/5 ENABLESELECTIONS

| ON | GE | Timer1/3/5<br>Operation |

|----|----|-------------------------|

| 1  | 1  | Count Enabled           |

| 1  | 0  | Always On               |

| 0  | 1  | Off                     |

| 0  | 0  | Off                     |

# 19.3 Clock Source Selection

The CS<3:0> bits of the TMRxCLK register (Register 19-3) are used to select the clock source for Timer1/3/5. The four TMRxCLK bits allow the selection of several possible synchronous and asynchronous clock sources. Register 19-3 displays the clock source selections.

#### 19.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used at the Timer1/3/5 gate:

- · Asynchronous event on the TxGPPS pin

- TMR0OUT

- TMR1/3/5OUT (excluding the TMR for which it is being used)

- TMR 2/4/6OUT (post-scaled)

- CCP1/2OUT

- PWM3/4OUT

- CMP1/2OUT

- ZCDOUT

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge after any one or    |

|       | more of the following conditions:            |

- Timer1/3/5 enabled after POR

- Write to TMRxH or TMRxL

- Timer1/3/5 is disabled

- Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON = 1) when TxCKI is low.

# 19.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input of the TxCKIPPS pin. This external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated secondary internal oscillator circuit.

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |  |  |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|--|--|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |  |  |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |  |  |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |  |  |

#### TABLE 21-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

#### TABLE 21-4:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 21.5.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 21.5.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 21.5.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# PIC18LF26/45/46K40

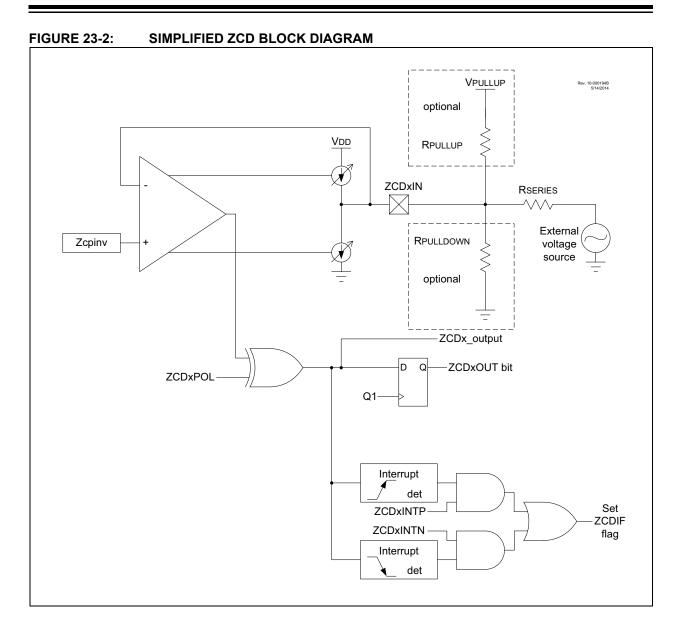

#### EQUATION 23-2: R-C CALCULATIONS

- VPEAK = External voltage source peak voltage

- f = External voltage source frequency

- C = Series capacitor

- R = Series resistor

- $V_{\rm C}$  = Peak capacitor voltage

- $\Phi$  = Capacitor induced zero crossing phase advance in radians

- $T_\Phi\,$  = Time ZC event occurs before actual zero crossing

$$Z = \frac{VPEAK}{3 \times 10^{-4}}$$

$$XC = \frac{1}{2\pi fC}$$

$$R = \sqrt{Z^2 - Xc^2}$$

$$VC = XC(3 \times 10^{-4})$$

$$\Phi = Tan^{-1}\left(\frac{XC}{R}\right)$$

$$T\Phi = \frac{\Phi}{2\pi f}$$

# EXAMPLE 23-1: R-C CALCULATIONS

VRMS = 120

VPEAK = VRMS \*

$$\sqrt{2}$$

= 169.7

f = 60 Hz

C = 0.1 µF

$$Z = \frac{VPEAK}{3 \times 10^{-4}} = \frac{169.7}{3 \times 10^{-4}} = 565.7 k\Omega$$

XC =  $\frac{1}{2\pi fC} = \frac{1}{(2\pi \times 60 \times 1 \times 10^{-7})} = 26.53 k\Omega$

R =  $\sqrt{(Z^2 \times Xc^2)} = 565.1 k\Omega$  (computed)

R = 560k $\Omega$  (used)

ZR =  $\sqrt{R^2 + Xc^2} = 560.6 k\Omega$  (using actual resistor)

IPEAK =  $\frac{VPEAK}{ZR} = 302.7 \times 10^{-6}$

VC = XC × Ipeak = 8.0V

$\Phi = Tan^{-1}(\frac{XC}{R}) = 0.047$  radians

T $\Phi = \frac{\Phi}{2\pi f} = 125.6 \mu s$

# 23.5.2 CORRECTION BY OFFSET CURRENT

When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 23-3.

# EQUATION 23-3: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to VSS. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 23-4.

# EQUATION 23-4: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{PULLUP} = \frac{R_{SERIES}(V_{PULLUP} - V_{CPINV})}{V_{CPINV}}$$

When External Signal is relative to VDD:

$$R_{PULLDOWN} = \frac{R_{SERIES}(VCPINV)}{(VDD - VCPINV)}$$

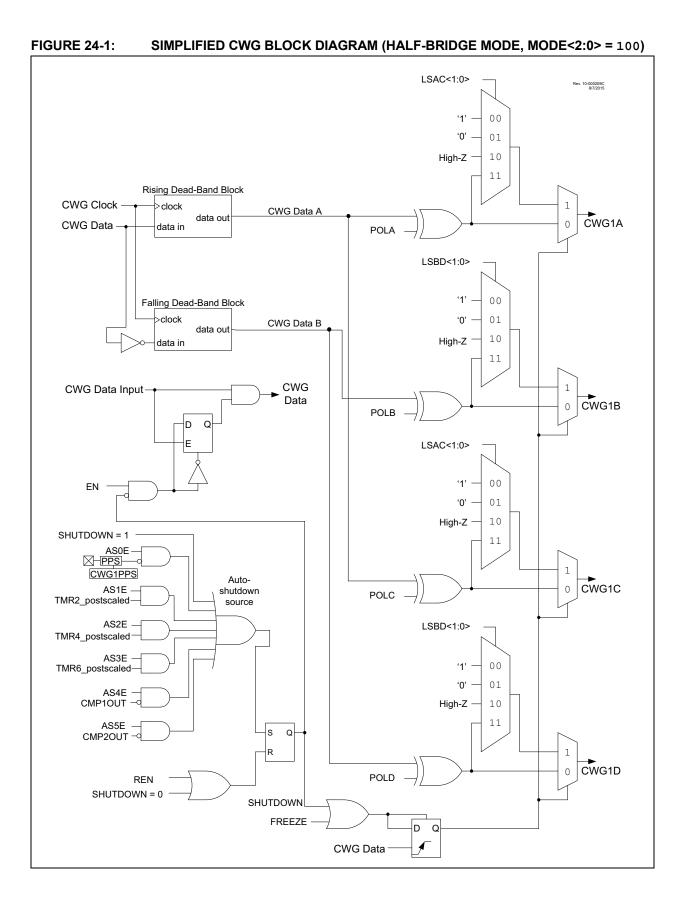

| Name       | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2      | Bit 1     | Bit 0  | Register<br>on Page |

|------------|----------|---------|---------|---------|-------|------------|-----------|--------|---------------------|

| CWG1CON0   | EN       | LD      | -       | _       | _     |            | MODE<2:0> | •      | 315                 |

| CWG1CON1   | _        | _       | IN      | _       | POLD  | POLC       | POLB      | POLA   | 316                 |

| CWG1CLKCON | _        | _       | _       | _       | _     | _          | —         | CS     | 317                 |

| CWG1ISM    | —        | —       | _       | —       |       | ISM<2:0>   |           |        | 317                 |

| CWG1STR    | OVRD     | OVRC    | OVRB    | OVRA    | STRD  | STRC       | STRB      | STRA   | 318                 |

| CWG1AS0    | SHUTDOWN | REN     | LSBD    | <1:0>   | LSAC  | C<1:0> — — |           |        | 319                 |

| CWG1AS1    | —        | —       | AS5E    | AS4E    | AS3E  | AS2E       | AS1E      | AS0E   | 320                 |

| CWG1DBR    | _        | _       |         |         | DBR<  | :5:0>      |           |        | 321                 |

| CWG1DBF    | _        | _       |         |         | DBF<  | :5:0>      |           |        | 321                 |

| PIE7       | SCANIE   | CRCIE   | NVMIE   | _       | _     | —          | _         | CWG1IE | 186                 |

| PIR7       | SCANIF   | CRCIF   | NVMIF   | _       | _     | _          | —         | CWG1IF | 178                 |

| IPR7       | SCANIP   | CRCIP   | NVMIP   | _       | _     | —          | —         | CWG1IP | 194                 |

| PMD4       | UART2MD  | UART1MD | MSSP2MD | MSSP1MD |       | _          | —         | CWG1MD | 72                  |

#### TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

Legend: -= unimplemented locations read as '0'. Shaded cells are not used by CWG.

|                    |      | Bit Clear Conditions                                  | Value after Trigger completion                                                           |                                                             | Threshold Operations                                                                                                                                                                   |                        |                        | Value at ADTIF interrupt |                          |       |

|--------------------|------|-------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|--------------------------|-------|

| Mode               | ADMD | ADACC and ADCNT                                       | ADACC                                                                                    | ADCNT                                                       | Retrigger                                                                                                                                                                              | Threshold<br>Test      | Interrupt              | ADAOV                    | ADFLTR                   | ADCNT |

| Basic              | 0    | ADACLR = 1                                            | Unchanged                                                                                | Unchanged                                                   | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | N/A                      | N/A                      | count |

| Accumulate         | 1    | ADACLR = 1                                            | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Average            | 2    | ADACLR = 1 or<br>ADCNT>=ADRPT at ADGO<br>or retrigger | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Burst<br>Average   | 3    | ADACLR = 1 or ADGO set or<br>retrigger                | Each repetition: same as<br>Average<br>End with sum of all<br>samples                    | Each repetition: same as<br>Average<br>End with ADCNT=ADRPT | Repeat while<br>ADCNT <adrpt< td=""><td>lf<br/>ADCNT&gt;=<br/>ADRPT</td><td>If thresh-<br/>old=true</td><td>ADACC Overflow</td><td>ADACC/2<sup>ADCRS</sup></td><td>ADRPT</td></adrpt<> | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | ADRPT |

| Low-pass<br>Filter | 4    | ADACLR = 1                                            | S+ADACC-ADACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ADACC-ADACC/<br>2 <sup>ADCRS</sup> | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | Filtered Value           | count |

Note: S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = ADREV and S2 = ADRES.

#### **REGISTER 31-19:** ADRESL: ADC RESULT REGISTER LOW, ADFM = 1

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u        | R/W-x/u       | R/W-x/u          | R/W-x/u      | R/W-x/u |

|-----------------------------------------|---------|-------------------|----------------|---------------|------------------|--------------|---------|

|                                         |         |                   | ADRE           | S<7:0>        |                  |              |         |

| bit 7                                   |         |                   |                |               |                  |              | bit 0   |

|                                         |         |                   |                |               |                  |              |         |

| Legend:                                 |         |                   |                |               |                  |              |         |

| R = Readable bit W = Writable bit       |         |                   | bit            | U = Unimpler  | nented bit, read | d as '0'     |         |

| u = Bit is unchanged x = Bit is unknown |         | iown              | -n/n = Value a | at POR and BC | R/Value at all   | other Resets |         |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared           |               |                  |              |         |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits. Lower eight bits of 10-bit conversion result.

#### REGISTER 31-20: ADPREVH: ADC PREVIOUS RESULT REGISTER

| R-x          | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |  |  |

|--------------|-----|-----|-----|-----|-----|-----|-------|--|--|

| ADPREV<15:8> |     |     |     |     |     |     |       |  |  |

| bit 7        |     |     |     |     |     |     | bit 0 |  |  |

|              |     |     |     |     |     |     |       |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADPREV<15:8>: Previous ADC Results bits If ADPSIS = 1: Upper byte of ADFLTR at the start of current ADC conversion If ADPSIS = 0: Upper bits of ADRES at the start of current ADC conversion<sup>(1)</sup>

**Note 1:** If ADPSIS = 0, ADPREVH and ADPREVL are formatted the same way as ADRES is, depending on the ADFM bit.

## 35.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                             | ADD liter                         | al to W         |      |          |  |  |  |

|-------------------------------------------------------------------|-----------------------------------|-----------------|------|----------|--|--|--|

| Syntax:                                                           | ADDLW                             | k               |      |          |  |  |  |

| Operands:                                                         | $0 \le k \le 255$                 |                 |      |          |  |  |  |

| Operation:                                                        | (W) + k $\rightarrow$             | W               |      |          |  |  |  |

| Status Affected:                                                  | N, OV, C, E                       | DC, Z           |      |          |  |  |  |

| Encoding:                                                         | 0000                              | 1111            | kkkk | kkkk     |  |  |  |

| Description:                                                      | The conten<br>8-bit literal<br>W. |                 |      |          |  |  |  |

| Words:                                                            | 1                                 | 1               |      |          |  |  |  |

| Cycles:                                                           | 1                                 | 1               |      |          |  |  |  |

| Q Cycle Activity                                                  | :                                 |                 |      |          |  |  |  |

| Q1                                                                | Q2                                | Q3              |      | Q4       |  |  |  |

| Decode                                                            | Read<br>literal 'k'               | Process<br>Data | s Wr | ite to W |  |  |  |

| Example:ADDLW15hBefore InstructionW=W=10hAfter InstructionW=W=25h |                                   |                 |      |          |  |  |  |

| ADDWF            | ADD W to f                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | ADDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Status Affected: | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Encoding:        | 0010 01da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Description:     | 001001daffffffffAdd W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).If 'a' is '0', the Access Bank is selected.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select the<br>GPR bank.If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br> |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| QC          | ycle Activity:               |        |                      |      |            |                      |

|-------------|------------------------------|--------|----------------------|------|------------|----------------------|

|             | Q1                           |        | Q2                   |      | 23         | Q4                   |

|             | Decode                       | -      | Read<br>register 'f' |      | ess<br>ita | Write to destination |

| <u>Exan</u> | Example:                     |        | DDWF                 | REG, | 0, 0       |                      |

|             | Before Instruc               | tion   |                      |      |            |                      |

|             | W<br>REG<br>After Instructio | =<br>= | 17h<br>0C2h          |      |            |                      |

|             |                              |        |                      |      |            |                      |

|             | W<br>REG                     | =      | 0D9h<br>0C2h         |      |            |                      |

| Note: | All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in       |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s). |

# PIC18(L)F26/45/46K40

| CPFSGT                     |                        | Compare                                                                                                                                                                                                                                                                                               | Compare f with W, skip if f > W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |  |  |  |

|----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| Synta                      | ax:                    | CPFSGT                                                                                                                                                                                                                                                                                                | CPFSGT f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |  |  |  |

| Opera                      | ands:                  | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                              | 0 ≤ f ≤ 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |  |  |

| Operation:                 |                        | • • • •                                                                                                                                                                                                                                                                                               | (f) - (W),<br>skip if $(f) > (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |  |  |  |

| Status Affected:           |                        | (unsigned o<br>None                                                                                                                                                                                                                                                                                   | (unsigned comparison)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |  |  |

| Enco                       |                        |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |  |  |  |

|                            | ription:               | Compares t<br>location 'f t<br>performing<br>If the content<br>contents of<br>instruction i<br>executed in<br>2-cycle inst<br>If 'a' is '0', tt<br>If 'a' is '0', tt<br>If 'a' is '0', tt<br>GPR bank.<br>If 'a' is '0' at<br>set is enabl<br>in Indexed I<br>mode when<br>tion 35.2.3<br>Oriented In | $\begin{tabular}{ c c c c } \hline 0110 & 010a & ffff & ffff \\ \hline Compares the contents of data memory location 'f' to the contents of the W by performing an unsigned subtraction. If the contents of 'f' are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a 2-cycle instruction. If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank. If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f \leq 95 (5Fh). See Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Addressing is in Indexed Literal Offset Addressing in Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Addressing is in Indexed Literal Offset Addressing in Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Addressing in Indexed Literal Offset Addressing is in Indexed Literal Offset Addressing in Indexed Literal Offset Addressing in Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Addressing in Indexed Literal Instructions in Indexed Literal Offset Addressing in Indexed Literal Instructions in Indexed Literal Instructions in Indexed Literal Instructions in Indexed Literal Instruction Indexed Literal$ |                 |  |  |  |

| Word                       | e.                     | eral Offset                                                                                                                                                                                                                                                                                           | Mode" for det                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ails.           |  |  |  |

| Cycles:                    |                        | 1(2)<br>Note: 3 cy                                                                                                                                                                                                                                                                                    | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |

| QC                         | ycle Activity:         |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |  |  |  |