Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k40-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 8.13 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON0 registers are updated to indicate the cause of the Reset. Table 8-3 shows the Reset conditions of these registers.

|  | TABLE 8-3: | <b>RESET CONDITION FOR SPECIAL REGISTERS</b> |

|--|------------|----------------------------------------------|

|--|------------|----------------------------------------------|

| Condition                          | Program<br>Counter    | STATUS<br>Register <sup>(2,3)</sup> | PCON0<br>Register |

|------------------------------------|-----------------------|-------------------------------------|-------------------|

| Power-on Reset                     | 0                     | -110 0000                           | 0011 110x         |

| Brown-out Reset                    | 0                     | -110 0000                           | 0011 11u0         |

| MCLR Reset during normal operation | 0                     | -uuu uuuu                           | uuuu Ouuu         |

| MCLR Reset during Sleep            | 0                     | -10u uuuu                           | uuuu Ouuu         |

| WDT Time-out Reset                 | 0                     | -0uu uuuu                           | սսս0 սսսս         |

| WDT Wake-up from Sleep             | PC + 2                | -00u uuuu                           | uuuu uuuu         |

| WWDT Window Violation Reset        | 0                     | -uuu uuuu                           | uu0u uuuu         |

| Interrupt Wake-up from Sleep       | PC + 2 <sup>(1)</sup> | -10u 0uuu                           | uuuu uuuu         |

| RESET Instruction Executed         | 0                     | -uuu uuuu                           | uuuu u0uu         |

| Stack Overflow Reset (STVREN = 1)  | 0                     | -uuu uuuu                           | luuu uuuu         |

| Stack Underflow Reset (STVREN = 1) | 0                     | -uuu uuuu                           | uluu uuuu         |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit (GIE) is set the return address is pushed on the stack and PC is loaded with the corresponding interrupt vector (depending on source, high or low priority) after execution of PC + 2.

2: If a Status bit is not implemented, that bit will be read as '0'.

3: Status bits Z, C, DC are reset by POR/BOR (Register 10-2).

## 8.14 Power Control (PCON0) Register

The Power Control (PCON0) register contains flag bits to differentiate between a:

- Brown-out Reset (BOR)

- Power-on Reset (POR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Window Violation (WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON0 register bits are shown in Register 8-2.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-3).

Software should reset the bit to the inactive state after restart (hardware will not reset the bit).

Software may also set any PCON0 bit to the active state, so that user code may be tested, but no Reset action will be generated.

| Name    | Bit 7  | Bit 6  | Bit 5                   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|---------|--------|--------|-------------------------|-------|-------|-------|-------|--------|---------------------|

| BORCON  | SBOREN |        |                         |       |       |       |       | BORRDY | 75                  |

| PCON0   | STKOVF | STKUNF | WDTWV                   | RWDT  | RMCLR | RI    | POR   | BOR    | 76                  |

| STATUS  | _      | TO     | PD                      | Ν     | OV    | Z     | DC    | С      | 118                 |

| WDTCON0 | _      | _      | - WDTPS<4:0>            |       |       |       |       | SEN    | 85                  |

| WDTCON1 |        | W      | WDTCS<2:0> — WINDOW<2:0 |       |       |       | )>    | 86     |                     |

TABLE 8-4: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

#### TABLE 10-4: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/45/46K40 DEVICES

| IABLE   | 10-4. SPLV |         |                        |         |                        |         | 20/43/401.40 | DEVICE  | 5               |

|---------|------------|---------|------------------------|---------|------------------------|---------|--------------|---------|-----------------|

| Address | Name       | Address | Name                   | Address | Name                   | Address | Name         | Address | Name            |

| F5Fh    | ADPCH      | F31h    | FVRCON                 | F03h    | RD4PPS <sup>(1)</sup>  | ED5h    | WDTPSH       | EA7h    | T3CKIPPS        |

| F5Eh    | ADPRE      | F30h    | HLVDCON1               | F02h    | RD3PPS <sup>(1)</sup>  | ED4h    | WDTPSL       | EA6h    | T1GPPS          |

| F5Dh    | ADCAP      | F2Fh    | HLVDCON0               | F01h    | RD2PPS <sup>(1)</sup>  | ED3h    | WDTCON1      | EA5h    | T1CKIPPS        |

| F5Ch    | ADACQ      | F2Eh    | ANSELE <sup>(2)</sup>  | F00h    | RD1PPS <sup>(2)</sup>  | ED2h    | WDTCON0      | EA4h    | <b>T0CKIPPS</b> |

| F5Bh    | ADCON3     | F2Dh    | WPUE                   | EFFh    | RD0PPS <sup>(2)</sup>  | ED1h    | PIR7         | EA3h    | INT2PPS         |

| F5Ah    | ADCON2     | F2Ch    | ODCONE <sup>(2)</sup>  | EFEh    | RC7PPS                 | ED0h    | PIR6         | EA2h    | INT1PPS         |

| F59h    | ADCON1     | F2Bh    | SLRCONE <sup>(2)</sup> | EFDh    | RC6PPS                 | ECFh    | PIR5         | EA1h    | INT0PPS         |

| F58h    | ADREF      | F2Ah    | INLVLE                 | EFCh    | RC5PPS                 | ECEh    | PIR4         | EA0h    | PPSLOCK         |

| F57h    | ADCLK      | F29h    | IOCEP                  | EFBh    | RC4PPS                 | ECDh    | PIR3         | E9Fh    | BAUD2CON        |

| F56h    | ADACT      | F28h    | IOCEN                  | EFAh    | RC3PPS                 | ECCh    | PIR2         | E9Eh    | TX2STA          |

| F55h    | MDCARH     | F27h    | IOCEF                  | EF9h    | RC2PPS                 | ECBh    | PIR1         | E9Dh    | RC2STA          |

| F54h    | MDCARL     | F26h    | ANSELD <sup>(2)</sup>  | EF8h    | RC1PPS                 | ECAh    | PIR0         | E9Ch    | SP2BRGH         |

| F53h    | MDSRC      | F25h    | WPUD <sup>(2)</sup>    | EF7h    | RC0PPS                 | EC9h    | PIE7         | E9Bh    | SP2BRGL         |

| F52h    | MDCON1     | F24h    | ODCOND <sup>(2)</sup>  | EF6h    | RB7PPS                 | EC8h    | PIE6         | E9Ah    | TX2REG          |

| F51h    | MDCON0     | F23h    | SLRCOND <sup>(2)</sup> | EF5h    | RB6PPS                 | EC7h    | PIE5         | E99h    | RC2REG          |

| F50h    | SCANDTRIG  | F22h    | INLVLD <sup>(2)</sup>  | EF4h    | RB5PPS                 | EC6h    | PIE4         | E98h    | SSP2CON3        |

| F4Fh    | SCANCON0   | F21h    | ANSELC                 | EF3h    | RB4PPS                 | EC5h    | PIE3         | E97h    | SSP2CON2        |

| F4Eh    | SCANHADRU  | F20h    | WPUC                   | EF2h    | RB3PPS                 | EC4h    | PIE2         | E96h    | SSP2CON1        |

| F4Dh    | SCANHADRH  | F1Fh    | ODCONC                 | EF1h    | RB2PPS                 | EC3h    | PIE1         | E95h    | SSP2STAT        |

| F4Ch    | SCANHADRL  | F1Eh    | SLRCONC                | EF0h    | RB1PPS                 | EC2h    | PIE0         | E94h    | SSP2MSK         |

| F4Bh    | SCANLADRU  | F1Dh    | INLVLC                 | EEFh    | RB0PPS                 | EC1h    | IPR7         | E93h    | SSP2ADD         |

| F4Ah    | SCANLADRH  | F1Ch    | IOCCP                  | EEEh    | RA7PPS                 | EC0h    | IPR6         | E92h    | SSP2BUF         |

| F49h    | SCANLADRL  | F1Bh    | IOCCN                  | EEDh    | RA6PPS                 | EBFh    | IPR5         | E91h    | SSP2SSPPS       |

| F48h    | CWG1STR    | F1Ah    | IOCCF                  | EECh    | RA5PPS                 | EBEh    | IPR4         | E90h    | SSP2DATPPS      |

| F47h    | CWG1AS1    | F19h    | ANSELB                 | EEBh    | RA4PPS                 | EBDh    | IPR3         | E8Fh    | SSP2CLKPPS      |

| F46h    | CWG1AS0    | F18h    | WPUB                   | EEAh    | RA3PPS                 | EBCh    | IPR2         | E8Eh    | TX2PPS          |

| F45h    | CWG1CON1   | F17h    | ODCONB                 | EE9h    | RA2PPS                 | EBBh    | IPR1         | E8Dh    | RX2PPS          |

| F44h    | CWG1CON0   | F16h    | SLRCONB                | EE8h    | RA1PPS                 | EBAh    | IPR0         |         |                 |

| F43h    | CWG1DBF    | F15h    | INLVLB                 | EE7h    | RA0PPS                 | EB9h    | SSP1SSPPS    |         |                 |

| F42h    | CWG1DBR    | F14h    | IOCBP                  | EE6h    | PMD5                   | EB8h    | SSP1DATPPS   |         |                 |

| F41h    | CWG1ISM    | F13h    | IOCBN                  | EE5h    | PMD4                   | EB7h    | SSP1CLKPPS   |         |                 |

| F40h    | CWG1CLKCON | F12h    | IOCBF                  | EE4h    | PMD3                   | EB6h    | TX1PPS       |         |                 |

| F3Fh    | CLKRCLK    | F11h    | ANSELA                 | EE3h    | PMD2                   | EB5h    | RX1PPS       |         |                 |

| F3Eh    | CLKRCON    | F10h    | WPUA                   | EE2h    | PMD1                   | EB4h    | MDSRCPPS     |         |                 |

| F3Dh    | CMOUT      | F0Fh    | ODCONA                 | EE1h    | PMD0                   | EB3h    | MDCARHPPS    |         |                 |

| F3Ch    | CM1PCH     | F0Eh    | SLRCONA                | EE0h    | BORCON                 | EB2h    | MDCARLPPS    |         |                 |

| F3Bh    | CM1NCH     | F0Dh    | INLVLA                 | EDFh    | VREGCON <sup>(1)</sup> | EB1h    | CWGINPPS     |         |                 |

| F3Ah    | CM1CON1    | F0Ch    | IOCAP                  | EDEh    | OSCFRQ                 | EB0h    | CCP2PPS      |         |                 |

| F39h    | CM1CON0    | F0Bh    | IOCAN                  | EDDh    | OSCTUNE                | EAFh    | CCP1PPS      |         |                 |

| F38h    | CM2PCH     | F0Ah    | IOCAF                  | EDCh    | OSCEN                  | EAEh    | ADACTPPS     |         |                 |

| F37h    | CM2NCH     | F09h    | RE2PPS <sup>(2)</sup>  | EDBh    | OSCSTAT                | EADh    | T6INPPS      |         |                 |

| F36h    | CM2CON1    | F08h    | RE1PPS <sup>(2)</sup>  | EDAh    | OSCCON3                | EACh    | T4INPPS      |         |                 |

| F35h    | CM2CON0    | F07h    | RE0PPS <sup>(2)</sup>  | ED9h    | OSCCON2                | EABh    | T2INPPS      |         |                 |

| F34h    | DAC1CON1   | F06h    | RD7PPS <sup>(2)</sup>  | ED8h    | OSCCON1                | EAAh    | T5GPPS       |         |                 |

| F33h    | DAC1CON0   | F05h    | RD6PPS <sup>(2)</sup>  | ED7h    | CPUDOZE                | EA9h    | T5CKIPPS     |         |                 |

| F32h    | ZCDCON     | F04h    | RD5PPS <sup>(2)</sup>  | ED6h    | WDTTMR                 | EA8h    | T3GPPS       | J       |                 |

**Note 1:** Not available on LF parts

2: Not available on PIC18(L)F26K40 (28-pin variants).

## 11.1 Program Flash Memory

The Program Flash Memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory or program memory erase is executed on blocks of n bytes at a time. Refer to Table 11-3 for write and erase block sizes. A Bulk Erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

It is important to understand the PFM memory structure for erase and programming operations. Program memory word size is 16 bits wide. PFM is arranged in rows. A row is the minimum size that can be erased by user software. Refer to Table 11-3 for the row sizes for the these devices.

After a row has been erased, all or a portion of this row can be programmed. Data to be written into the program memory row is written to 6-bit wide data write latches. These latches are not directly accessible, but may be loaded via sequential writes to the TABLAT register.

**Note:** To modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, the new data and retained data can be written into the write latches to reprogram the row of PFM. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations

| <b>TABLE 11-2</b> : | FLASH MEMORY ORGANIZATION BY DEVICE |

|---------------------|-------------------------------------|

|                     |                                     |

| Device         | Row Erase Size<br>(Words) | Write Latches<br>(Bytes) | Program Flash<br>Memory (Words) | Data Memory (Bytes) |  |

|----------------|---------------------------|--------------------------|---------------------------------|---------------------|--|

| PIC18(L)F45K40 |                           |                          | 16384                           | 256                 |  |

| PIC18(L)F26K40 | 32                        | 64                       | 22769                           |                     |  |

| PIC18(L)F46K40 |                           |                          | 32768                           | 1024                |  |

| PIC18(L)F27K40 | 64                        | 100                      | 65526                           | 1024                |  |

| PIC18(L)F47K40 | 04                        | 128                      | 65536                           |                     |  |

## 18.3 **Programmable Prescaler**

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the T0CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register or the T0CON0, T0CON1 registers or by any Reset.

## 18.4 **Programmable Postscaler**

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the TOOUTPS<3:0> bits of the TOCON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register or the T0CON0, T0CON1 registers or by any Reset.

## 18.5 Operation During Sleep

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

## 18.6 Timer0 Interrupts

The Timer0 interrupt flag bit (TMR0IF) is set when either of the following conditions occur:

- 8-bit TMR0L matches the TMR0H value

- 16-bit TMR0 rolls over from 'FFFFh'

When the postscaler bits (TOOUTPS<3:0>) are set to 1:1 operation (no division), the TOIF flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF flag bit will be set every TOOUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE0 register = '1'), the CPU will be interrupted and the device may wake from Sleep (see Section 18.2 "Clock Source Selection" for more details).

## 18.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see **Section 17.0 "Peripheral Pin Select (PPS) Module**" for additional information). The Timer0 output can also be used by other peripherals, such as the auto-conversion trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 output bit (TOOUT) of the TOCON0 register (Register 18-1).

TMR0\_out will be a pulse of one postscaled clock period when a match occurs between TMR0L and PR0 (Period register for TMR0) in 8-bit mode, or when TMR0 rolls over in 16-bit mode. The Timer0 output is a 50% duty cycle that toggles on each TMR0\_out rising clock edge.

### REGISTER 21-3: CCPxCAP: CAPTURE INPUT SELECTION MULTIPLEXER REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/x | R/W-0/x |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | _   | _   |     | CTS<    | <1:0>   |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 7-2 Unimplemented: Read as '0'

bit 1-0 CTS<1:0>: Capture Trigger Input Selection bits

| CTS<1:0> |                         | Connection              |  |  |

|----------|-------------------------|-------------------------|--|--|

| 013<1.02 | CCP1                    | CCP2                    |  |  |

| 11       | IOC_Interrupt           |                         |  |  |

| 10       | CMP2_output             |                         |  |  |

| 01       | CMP1_output             |                         |  |  |

| 00       | Pin selected by CCP1PPS | Pin selected by CCP2PPS |  |  |

### REGISTER 21-4: CCPRxL: CCPx REGISTER LOW BYTE

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| CCPRx<7:0>  |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-0 | MODE = Capture Mode:                           |

|---------|------------------------------------------------|

|         | CCPRxL<7:0>: LSB of captured TMR1 value        |

|         | MODE = Compare Mode:                           |

|         | CCPRxL<7:0>: LSB compared to TMR1 value        |

|         | MODE = PWM Mode && FMT = 0:                    |

|         | CCPRxL<7:0>: CCPW<7:0> - Pulse-Width LS 8 bits |

|         | MODE = PWM Mode && FMT = 1:                    |

|         | CCPRxL<7:6>: CCPW<1:0> - Pulse-Width LS 2 bits |

|         | CCPRxL<5:0>: Not used                          |

© 2015-2017 Microchip Technology Inc.

## 23.0 ZERO-CROSS DETECTION (ZCD) MODULE

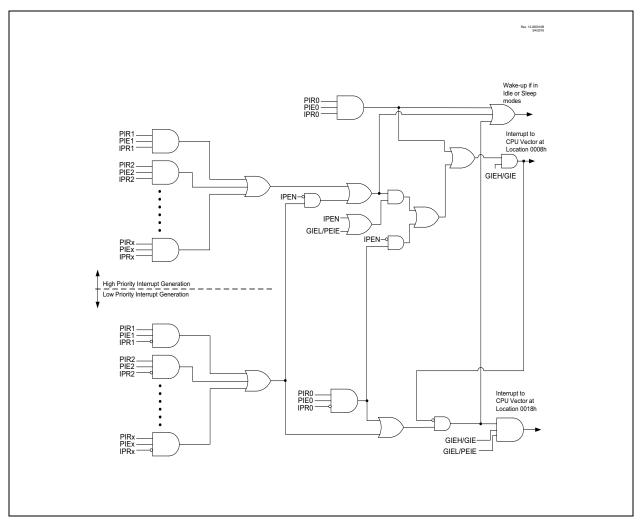

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 23-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- Low EMI cycle switching

## 23.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 23-1 and Figure 23-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

## EQUATION 23-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 23-1: EXTERNAL VOLTAGE

| REGISTER 26-11: | SSPxADD: MSSP ADDRESS REGISTER (I <sup>2</sup> C MASTER MODE) |  |

|-----------------|---------------------------------------------------------------|--|

|-----------------|---------------------------------------------------------------|--|

|                   |       |                     |       | •              |                  | ,              |              |

|-------------------|-------|---------------------|-------|----------------|------------------|----------------|--------------|

| R/W-0             | R/W-0 | R/W-0               | R/W-0 | R/W-0          | R/W-0            | R/W-0          | R/W-0        |

|                   |       |                     | ADD   | )<7:0>         |                  |                |              |

| bit 7             |       |                     |       |                |                  |                | bit 0        |

|                   |       |                     |       |                |                  |                |              |

| Legend:           |       |                     |       |                |                  |                |              |

| R = Readable bi   | t     | W = Writable bit    |       | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unchan | nged  | x = Bit is unknow   | vn    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set  |       | '0' = Bit is cleare | d     |                |                  |                |              |

## Master mode: I<sup>2</sup>C mode

| bit 7-0 | Baud Rate Clock Divider bits <sup>(1)</sup>             |

|---------|---------------------------------------------------------|

|         | SCK/SCL pin clock period = ((SSPxADD<7:0> + 1) *4)/Fosc |

#### 10-Bit Slave mode – Most Significant Address Byte:

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a don't care. Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to, '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<9:8>: Two Most Significant bits of 10-bit Address

- bit 0 Not used: Unused in this mode. Bit state is a don't care.

#### 10-Bit Slave mode – Least Significant Address Byte:

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit Address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a don't care.

**Note 1:** Values of 0x00, 0x01 and 0x02 are not valid for SSPxADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### REGISTER 26-12: SSPxMSK: MSSPx ADDRESS MASK REGISTER

| R/W-1   | R/W-1 | R/W-1 | R/W-1    | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-------|-------|----------|-------|-------|-------|-------|

|         |       |       | MSK<7:1> |       |       |       | MSK0  |

| bit 7   |       |       |          |       |       |       | bit 0 |

|         |       |       |          |       |       |       |       |

| Logond: |       |       |          |       |       |       |       |

| as '0'                      |

|-----------------------------|

| as 0                        |

| R/Value at all other Resets |

|                             |

|                             |

| bit 7-1 | MSK<7:1>: Mask bits                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The received address bit n is compared to SSPxADDn to detect I<sup>2</sup>C address match</li> <li>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</li> </ul>                                                                                                                                                                                                  |

| bit 0   | <b>MSK0:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):<br>1 = The received address bit 0 is compared to SSPxADD0 to detect I <sup>2</sup> C address match<br>0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match<br>I <sup>2</sup> C Slave mode, 7-bit address, the bit is ignored. |

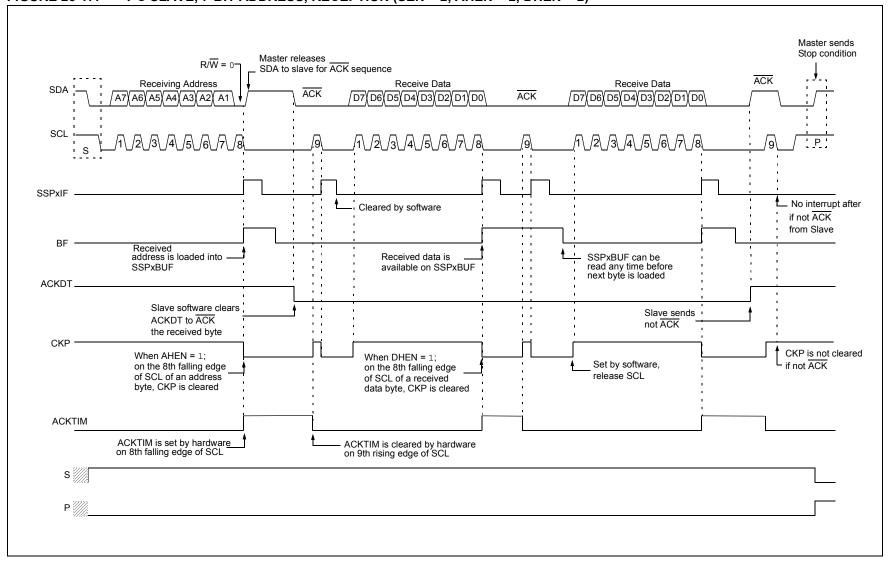

## FIGURE 26-17: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 1, DHEN = 1)

PIC18(L)F26/45/46K40

| R/W-0/0              | R/W-0/0 | R/W-0/0                                                  | R/W-0/0 | R/W-0/0                                               | R/W-0/0     | R/W-0/0 | R/W-0/0 |  |

|----------------------|---------|----------------------------------------------------------|---------|-------------------------------------------------------|-------------|---------|---------|--|

|                      |         |                                                          | ADPF    | RE<7:0>                                               |             |         |         |  |

| bit 7                |         |                                                          |         |                                                       |             |         | bit 0   |  |

|                      |         |                                                          |         |                                                       |             |         |         |  |

| Legend:              |         |                                                          |         |                                                       |             |         |         |  |

| R = Readable bit     |         | W = Writable bit                                         |         | U = Unimplemented bit, read as '0'                    |             |         |         |  |

| u = Bit is unchanged |         | x = Bit is unknown                                       |         | -n/n = Value at POR and BOR/Value at all other Resets |             |         |         |  |

| '1' = Bit is set     |         | '0' = Bit is clea                                        | ared    |                                                       |             |         |         |  |

| bit 7-0              |         | <ul> <li>Precharge Ti</li> <li>Precharge time</li> </ul> |         |                                                       | I ADC clock |         |         |  |

|                      |         | = Precharge time                                         |         |                                                       |             |         |         |  |

|                      | •       |                                                          |         |                                                       |             |         |         |  |

### REGISTER 31-9: ADPRE: ADC PRECHARGE TIME CONTROL REGISTER

00000001 = Precharge time is 1 clock of the selected ADC clock 00000000 = Precharge time is not included in the data conversion cycle

#### REGISTER 31-10: ADACQ: ADC ACQUISITION TIME CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADACO   | Q<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | <b>ADACQ&lt;7:0&gt;</b> : Acquisition (charge share time) Select bits<br>11111111 = Acquisition time is 255 clocks of the selected ADC clock<br>11111110 = Acquisition time is 254 clocks of the selected ADC clock |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                   |

|         | • 00000001 = Acquisition time is 1 clock of the selected ADC clock 00000000 = Acquisition time is not included in the data conversion cycle                                                                         |

| Notor   | If ADREE is not equal to (a), then ADACO = $b'(00000000)$ means Acquisition time is 256 closed                                                                                                                      |

**Note:** If ADPRE is not equal to '0', then ADACQ = b'00000000 means Acquisition time is 256 clocks of the selected ADC clock.

-n/n = Value at POR and BOR/Value at all other Resets

### REGISTER 31-27: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

x = Bit is unknown

| R-x              | R-x | R-x              | R-x  | R-x          | R-x              | R-x      | R-x   |

|------------------|-----|------------------|------|--------------|------------------|----------|-------|

|                  |     |                  | ADER | R<7:0>       |                  |          |       |

| bit 7            |     |                  |      |              |                  |          | bit 0 |

|                  |     |                  |      |              |                  |          |       |

| Legend:          |     |                  |      |              |                  |          |       |

| R = Readable bit |     | W = Writable bit |      | U = Unimplen | nented bit, read | d as '0' |       |

| '1' = Bit is set | '0' = Bit is cleared                                                                           |

|------------------|------------------------------------------------------------------------------------------------|

|                  |                                                                                                |

| bit 7-0          | ADERR<7:0>: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined |

## REGISTER 31-28 ADI THH: ADC I OWER THRESHOLD HIGH BYTE REGISTER

by ADCALC bits of ADCON3, see Register 23-1 for more details.

| ILE OIOTEILO | LO. ADEN |         |         |         | DITEREOR |         |         |

|--------------|----------|---------|---------|---------|----------|---------|---------|

| R/W-x/x      | R/W-x/x  | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x  | R/W-x/x | R/W-x/x |

|              |          |         | ADLTH   | <15:8>  |          |         |         |

| bit 7        |          |         |         |         |          |         | bit 0   |

|              |          |         |         |         |          |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADLTH<15:8>: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 31-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADLTH   | l<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADLTH<7:0>: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2015-2017 Microchip Technology Inc.

u = Bit is unchanged

| Name                | Bit 7      | Bit 6     | Bit 5     | Bit 4  | Bit 3   | Bit 2              | Bit 1     | Bit 0           | Register<br>on Page |

|---------------------|------------|-----------|-----------|--------|---------|--------------------|-----------|-----------------|---------------------|

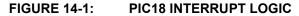

| INTCON              | GIE/GIEH   | PEIE/GIEL | IPEN      | _      | _       | INT2EDG            | INT1EDG   | INT0EDG         | 170                 |

| PIE1                | OSCFIE     | CSWIE     | _         | _      | _       | _                  | ADTIE     | ADIE            | 180                 |

| PIR1                | OSCFIF     | CSWIF     |           | _      | _       | _                  | ADTIF     | ADIF            | 172                 |

| ADCON0              | ADON       | ADCON     | _         | ADCS   | -       | ADFM               | —         | ADGO            | 448                 |

| ADCON1              | ADPPOL     | ADIPEN    | ADGPOL    | _      | _       | _                  | _         | ADDSEN          | 449                 |

| ADCON2              | ADPSIS     | A         | DCRS<2:0  | >      | ADACLR  |                    | ADMD<2:0> | >               | 450                 |

| ADCON3              | -          | A         | DCALC<2:0 | )>     | ADSOI   | A                  | DTMD<2:0  | >               | 451                 |

| ADACT               | _          | _         | —         | —      |         | ADAC               | T<4:0>    |                 | 450                 |

| ADRESH              |            |           |           | ADRES  | SH<7:0> |                    |           |                 | 458, 458            |

| ADRESL              |            |           |           | ADRES  | SL<7:0> |                    |           |                 | 458, 459            |

| ADPREVH             |            |           |           | ADPRE  | V<15:8> |                    |           |                 | 459                 |

| ADPREVL             |            |           |           | ADPRE  | EV<7:0> |                    |           |                 | 460                 |

| ADACCH              |            |           |           | ADACO  | C<15:8> |                    |           |                 | 460                 |

| ADACCL              |            |           |           | ADAC   | C<7:0>  |                    |           |                 | 460                 |

| ADSTPTH             |            |           |           | ADSTP  | T<15:8> |                    |           |                 | 461                 |

| ADSTPT              |            |           |           | ADSTR  | PT<7:0> |                    |           |                 | 461                 |

| ADERRL              |            |           |           | ADER   | R<7:0>  |                    |           |                 | 462                 |

| ADLTHH              |            |           |           | ADLTH  | l<15:8> |                    |           |                 | 462                 |

| ADLTHL              |            |           |           | ADLTI  | H<7:0>  |                    |           |                 | 462                 |

| ADUTHH              |            |           |           | ADUTH  | H<15:8> |                    |           |                 | 463                 |

| ADUTHL              |            |           |           | ADUT   | H<7:0>  |                    |           |                 | 463                 |

| ADSTAT              | ADAOV      | ADUTHR    | ADLTHR    | ADMATH |         | ADSTA              | T<3:0>    |                 | 452                 |

| ADCLK               | _          | _         |           |        | ADCS    | 6<5:0>             |           |                 | 453                 |

| ADREF               | —          | —         |           | ADNREF | —       | _                  | ADPRE     | EF<1:0>         | 453                 |

| ADPCH               | —          | _         |           |        | ADPC    | H<5:0>             |           |                 | 454                 |

| ADPRE               |            |           |           | ADPR   | E<7:0>  |                    |           |                 | 455                 |

| ADACQ               |            |           |           | ADAC   | Q<7:0>  |                    |           |                 | 455                 |

| ADCAP               | —          |           | _         |        | ŀ       | ADCAP<4:0          | >         |                 | 456                 |

| ADRPT               |            |           |           |        | T<7:0>  |                    |           |                 | 456                 |

| ADCNT               |            |           |           |        | T<7:0>  |                    |           |                 | 457                 |

| ADFLTRH             |            |           |           |        | R<15:8> |                    |           |                 | 457                 |

| ADFLTRL             | D.(22)     |           | TOTI      |        | R<7:0>  | (D ( . )           |           | <b>D</b> . 1 0: | 457                 |

| FVRCON              | FVREN      | FVRRDY    | TSEN      | TSRNG  | -       | /R<1:0>            |           | R<1:0>          | 423                 |

| DAC1CON1<br>OSCSTAT | –<br>EXTOR | —<br>HFOR | —<br>MFOR | LFOR   | SOR     | DAC1R<4:0><br>ADOR | ,<br>     | PLLR            | 429<br>39           |

| Legend:             |            |           |           |        |         | -                  |           | FLLK            | 29                  |

| TABLE 31-5: | SUMMARY OF REGISTERS ASSOCIATED WITH ADC |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

Legend: - = unimplemented read as '0'. Shaded cells are not used for the ADC module.

## 32.0 COMPARATOR MODULE

**Note:** The PIC18(L)F26/45/46K40 devices have two comparators. Therefore, all information in this section refers to both C1 and C2.

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution.

The analog comparator module includes the following features:

- Programmable input selection

- Programmable output polarity

- Rising/falling output edge interrupts

- Wake-up from Sleep

- CWG Auto-shutdown source

- Selectable voltage reference

- ADC Auto-trigger

- TMR1/3/5 Gate

- TMR2/4/6 Reset

- CCP Capture Mode Input

- DSM Modulator Source

- Input and Window signal to Signal Measurement

Timer

## 32.1 Comparator Overview

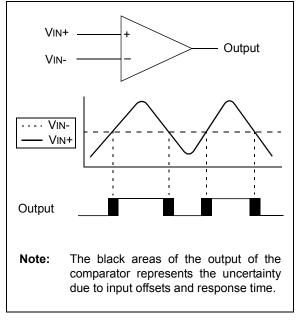

A single comparator is shown in Figure 32-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

TABLE 35-2: INSTRUCTION SET

| Mnemo    | onic,                           | Description                              | Civalaa    | 16-  | Bit Instr | uction W | /ord | Status          | Notoo      |

|----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| Opera    | nds                             | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-ORI | ENTED (                         | OPERATIONS                               |            |      |           |          |      |                 |            |

| ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC   | f, d, a                         | Add WREG and CARRY bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF    | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF     | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF     | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ   | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT   | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT   | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF     | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF     | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF     | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff | None            |            |

|          | 3/ U                            | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                 |            |

| MOVWF    | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF    | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2       |

| NEGF     | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N | ,          |

| RLCF     | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF    | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N            | •, =       |

| RRCF     | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N         |            |

| RRNCF    | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N            |            |

| SETF     | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            | 1, 2       |

| SUBFWB   | f, d, a                         | Subtract f from WREG with<br>borrow      | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N | ,          |

| SUBWF    | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB   | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff     | ffff | C, DC, Z, OV, N | ,          |

|          |                                 | borrow                                   |            |      |           |          |      |                 |            |

| SWAPF    | f, d, a                         | Swap nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ   | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF    | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001 | 10da      | ffff     | ffff | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| RLNCF                                                         | Rotate Le                                                                                                                                                                                | eft f (No Car                                                                                                    | ry)                                                                                                                                                                                                     |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                       | RLNCF                                                                                                                                                                                    | f {,d {,a}}                                                                                                      |                                                                                                                                                                                                         |

| Operands:                                                     | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                      |                                                                                                                  |                                                                                                                                                                                                         |

| Operation:                                                    | $(f \le n >) \rightarrow d$<br>$(f \le 7 >) \rightarrow d$                                                                                                                               | est <n +="" 1="">,<br/>est&lt;0&gt;</n>                                                                          |                                                                                                                                                                                                         |

| Status Affected:                                              | N, Z                                                                                                                                                                                     |                                                                                                                  |                                                                                                                                                                                                         |

| Encoding:                                                     | 0100                                                                                                                                                                                     | 01da ff:                                                                                                         | ff ffff                                                                                                                                                                                                 |

| Description:                                                  | one bit to t<br>is placed ir<br>stored bac<br>If 'a' is '0', 1<br>If 'a' is '1', 1<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>tion 35.2.3<br>Oriented I | and the extend<br>led, this instruc-<br>Literal Offset $\lambda$<br>never f $\leq$ 95 (5<br>5 <b>"Byte-Orien</b> | '0', the result<br>, the result is<br>(default).<br>nk is selected.<br>d to select the<br>led instruction<br>ction operates<br>Addressing<br>Fh). See Sec-<br>ted and Bit-<br>n Indexed Lit-<br>etails. |

| Words:                                                        | 1                                                                                                                                                                                        |                                                                                                                  |                                                                                                                                                                                                         |

| Cycles:                                                       | 1                                                                                                                                                                                        |                                                                                                                  |                                                                                                                                                                                                         |

| ,                                                             | I                                                                                                                                                                                        |                                                                                                                  |                                                                                                                                                                                                         |

| Q Cycle Activity:<br>Q1                                       | Q2                                                                                                                                                                                       | Q3                                                                                                               | Q4                                                                                                                                                                                                      |

| Decode                                                        | Read<br>register 'f'                                                                                                                                                                     | Process<br>Data                                                                                                  | Write to<br>destination                                                                                                                                                                                 |

| Example:<br>Before Instruct<br>REG<br>After Instructio<br>REG | RLNCF<br>ion<br>= 1010 1                                                                                                                                                                 |                                                                                                                  | 0                                                                                                                                                                                                       |

| RRCF                                                                                                         | Rotate Ri                                                                                                                                                                  | -                                                                                                                                                                                 |                                                                                             |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Syntax:                                                                                                      | RRCF f{,                                                                                                                                                                   | d {,a}}                                                                                                                                                                           |                                                                                             |

| Operands:                                                                                                    | $0 \leq f \leq 255$                                                                                                                                                        |                                                                                                                                                                                   |                                                                                             |

|                                                                                                              | d ∈ [0,1]                                                                                                                                                                  |                                                                                                                                                                                   |                                                                                             |

| o "                                                                                                          | a ∈ [0,1]                                                                                                                                                                  |                                                                                                                                                                                   |                                                                                             |

| Operation:                                                                                                   | $(f < n >) \rightarrow de$<br>$(f < 0 >) \rightarrow C$<br>$(C) \rightarrow dest$                                                                                          | ,                                                                                                                                                                                 |                                                                                             |

| Status Affected:                                                                                             | C, N, Z                                                                                                                                                                    |                                                                                                                                                                                   |                                                                                             |

| Encoding:                                                                                                    | 0011                                                                                                                                                                       | 00da ff:                                                                                                                                                                          | ff ffff                                                                                     |

| Description:                                                                                                 | one bit to th<br>flag. If 'd' is<br>If 'd' is '1', t<br>register 'f' (<br>If 'a' is '0', t                                                                                 | ts of register 'f<br>he right throug<br>'0', the result i<br>he result is pla<br>default).<br>he Access Bai<br>he BSR is use                                                      | h the CARRY<br>is placed in W<br>aced back in<br>nk is selected                             |

|                                                                                                              | set is enabl<br>in Indexed<br>mode when<br>tion 35.2.3<br>Oriented Ir                                                                                                      | nd the extende<br>ed, this instruct<br>Literal Offset A<br>lever f ≤ 95 (5)<br>"Byte-Orient<br>hstructions in<br>Mode" for de<br>registe                                          | ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lite<br>tails.       |

| Words:                                                                                                       | set is enabl<br>in Indexed<br>mode when<br>tion 35.2.3<br>Oriented In<br>eral Offset                                                                                       | ed, this instruct<br>Literal Offset A<br>lever $f \le 95$ (50<br>"Byte-Orient<br>instructions in<br>Mode" for de                                                                  | ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lite<br>tails.       |

| Words:<br>Cycles:                                                                                            | set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset                                                                                       | ed, this instruct<br>Literal Offset A<br>lever $f \le 95$ (50<br>"Byte-Orient<br>instructions in<br>Mode" for de                                                                  | ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lite<br>tails.       |

| Cycles:                                                                                                      | set is enablin Indexed<br>mode when<br>tion 35.2.3<br>Oriented In<br>eral Offset                                                                                           | ed, this instruct<br>Literal Offset A<br>lever $f \le 95$ (50<br>"Byte-Orient<br>instructions in<br>Mode" for de                                                                  | ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lite<br>tails.       |

|                                                                                                              | set is enablin Indexed<br>mode when<br>tion 35.2.3<br>Oriented In<br>eral Offset                                                                                           | ed, this instruct<br>Literal Offset A<br>lever $f \le 95$ (50<br>"Byte-Orient<br>instructions in<br>Mode" for de                                                                  | ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lite<br>tails.       |

| Cycles:<br>Q Cycle Activity:                                                                                 | set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>1                                                                                  | ed, this instru<br>Literal Offset A<br>lever f ≤ 95 (51<br>"Byte-Orient<br>instructions in<br>Mode" for de<br>registe                                                             | ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lit-<br>tails.       |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                                           | set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>1<br>1<br>2                                                                        | ed, this instru<br>Literal Offset A<br>ever f ≤ 95 (51<br>"Byte-Orient<br>instructions in<br>Mode" for de<br>registe                                                              | Ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lit-<br>tails.<br>rf |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                                                 | set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>1<br>1<br>1<br>2<br>Q2<br>Read<br>register 'f'                                     | ed, this instruu<br>Literal Offset A<br>leever f ≤ 95 (5)<br><b>"Byte-Orient</b><br><b>instructions in</b><br><b>Mode</b> " for de<br>registe<br>Q3<br>Process<br>Data            | Q4<br>Q4<br>Write to<br>destination                                                         |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                                                 | set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>C<br>1<br>1<br>2<br>2<br>Read                                                      | ed, this instru<br>Literal Offset A<br>ever f ≤ 95 (51<br>"Byte-Orient<br>instructions in<br>Mode" for de<br>registe<br>Q3<br>Process                                             | Q4<br>Q4<br>Write to<br>destination                                                         |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct                                  | set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>I<br>1<br>1<br>2<br>Q2<br>Read<br>register 'f'<br>RRCF<br>tion                     | ed, this instruc<br>Literal Offset A<br>ever f ≤ 95 (51<br>"Byte-Orient<br>astructions in<br>Mode" for de<br>registe<br>Q3<br>Process<br>Data<br>REG, 0, 1                        | Q4<br>Q4<br>Write to<br>destination                                                         |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruc<br>REG                            | set is enablin Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>I<br>1<br>1<br>2<br>Read<br>register 'f'<br>RRCF<br>tion<br>= 1110 0                   | ed, this instruc<br>Literal Offset A<br>ever f ≤ 95 (51<br>"Byte-Orient<br>astructions in<br>Mode" for de<br>registe<br>Q3<br>Process<br>Data<br>REG, 0, 1                        | Q4<br>Q4<br>Write to<br>destination                                                         |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct                                  | set is enablin Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>T<br>1<br>1<br>1<br>2<br>Q2<br>Read<br>register 'f'<br>RRCF<br>tion<br>= 1110 C<br>= 0 | ed, this instruc<br>Literal Offset A<br>ever f ≤ 95 (51<br>"Byte-Orient<br>astructions in<br>Mode" for de<br>registe<br>Q3<br>Process<br>Data<br>REG, 0, 1                        | Q4<br>Q4<br>Write to<br>destination                                                         |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>REG<br>C                      | set is enablin Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>T<br>1<br>1<br>1<br>2<br>Q2<br>Read<br>register 'f'<br>RRCF<br>tion<br>= 1110 C<br>= 0 | ed, this instruc<br>Literal Offset A<br>lever f ≤ 95 (5)<br><b>"Byte-Orient</b><br><b>istructions in</b><br><b>Mode</b> " for de<br>registe<br>Q3<br>Process<br>Data<br>REG, 0, 0 | Q4<br>Q4<br>Write to<br>destination                                                         |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>REG<br>C<br>After Instruction | set is enablin Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir<br>eral Offset<br>I<br>1<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>RRCF<br>tion<br>= 1110 C<br>= 0      | ed, this instruc<br>Literal Offset A<br>lever f ≤ 95 (5)<br><b>"Byte-Orient</b><br><b>istructions in</b><br><b>Mode</b> " for de<br>registe<br>Q3<br>Process<br>Data<br>REG, 0, 0 | Q4<br>Q4<br>Write to<br>destination                                                         |

| SLEEP                                                                                                                                                                        | Enter Sle                                               | ep mode                                                                                                                                                                                                           |                |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|--|

| Syntax:                                                                                                                                                                      | SLEEP                                                   |                                                                                                                                                                                                                   |                |  |  |  |  |  |  |

| Operands:                                                                                                                                                                    | None                                                    |                                                                                                                                                                                                                   |                |  |  |  |  |  |  |

| Operation:                                                                                                                                                                   |                                                         |                                                                                                                                                                                                                   |                |  |  |  |  |  |  |

| Status Affected:                                                                                                                                                             | TO, PD                                                  | TO, PD                                                                                                                                                                                                            |                |  |  |  |  |  |  |