Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k40-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

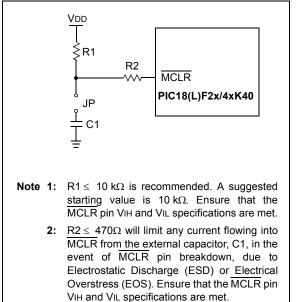

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 2.4 ICSP™ Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 36.0 "Development Support"**.

| ILEGIO I EILO O | . comg |     | 010011011 |     |     |       |       |

|-----------------|--------|-----|-----------|-----|-----|-------|-------|

| U-1             | U-1    | U-1 | U-1       | U-1 | U-1 | R/W-1 | R/W-1 |

| —               | _      | _   | _         | _   | —   | CPD   | CP    |

| bit 7           |        |     |           |     |     |       | bit 0 |

|                 |        |     |           |     |     |       |       |

| l egend.        |        |     |           |     |     |       |       |

### **REGISTER 3-9:** Configuration Word 5L (30 0008h): Code Protection

| Legend:                     |                  |                            |                    |  |

|-----------------------------|------------------|----------------------------|--------------------|--|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | id as '1'          |  |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |  |

| bit 7-2 | Unimplemented: Read as '1'                            |

|---------|-------------------------------------------------------|

| bit 1   | CPD: Data NVM Memory Code Protection bit              |

|         | 1 = Data NVM code protection disabled                 |

|         | 0 = Data NVM code protection enabled                  |

| bit 0   | CP: User NVM Program Memory Code Protection bit       |

|         | <ol> <li>User NVM code protection disabled</li> </ol> |

|         | 0 = User NVM code protection enabled                  |

### **REGISTER 3-10:** Configuration Word 6L (30 000Ah): Memory Read Protection

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EBTR7 | EBTR6 | EBTR5 | EBTR4 | EBTR3 | EBTR2 | EBTR1 | EBTR0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:                     |                  |                            |                    |

|-----------------------------|------------------|----------------------------|--------------------|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | d as '1'           |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0

EBTR<7:0>: Table Read Protection bits<sup>(1)</sup>

1 = Corresponding Memory Block NOT protected from table reads executed in other blocks

0 = Corresponding Memory Block protected from table reads executed in other blocks

Note 1: Refer to Table 10-2 for details on implementation of the individual EBTR bits.

### REGISTER 3-11: Configuration Word 6H (30 000Bh): Memory Read Protection

| U-1   | U-1 | U-1 | U-1 | U-1 | U-1 | R/W-1 | U-1   |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | _   | _   | _   | _   | EBTRB | _     |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                     |                  |                        |                    |

|-----------------------------|------------------|------------------------|--------------------|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, | , read as '1'      |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 7-2 Unimplemented: Read as '1'

# bit 1 **EBTRB:** Table Read Protection bit

- 1 = Memory Boot Block NOT protected from table reads executed in other blocks

- 0 = Memory Boot Block protected from table reads executed in other blocks

- bit 0 Unimplemented: Read as '1'

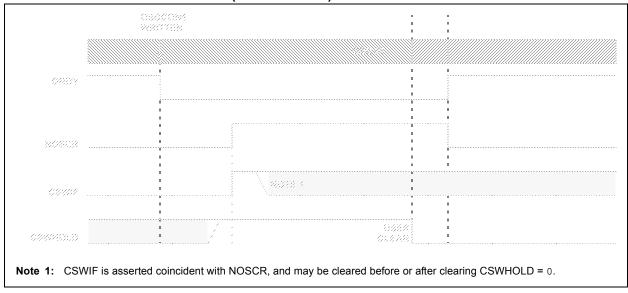

# 4.4.2 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

# FIGURE 4-7: CLOCK SWITCH (CSWHOLD = 1)

# 7.5 Register Definitions: Peripheral Module Disable

| R/W-0/0                 | R/W-0/0                         | R/W-0/0                                                                            | R/W-0/0                        | R/W-0/0                                       | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-------------------------|---------------------------------|------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------|------------------|------------------|--------------|

| SYSCMD                  | FVRMD                           | HLVDMD                                                                             | CRCMD                          | SCANMD                                        | NVMMD            | CLKRMD           | IOCMD        |

| 7                       | •                               | •                                                                                  | •                              | •                                             |                  | •                |              |

|                         |                                 |                                                                                    |                                |                                               |                  |                  |              |

| Legend:<br>R = Readable | , hit                           | W = Writable                                                                       | hit                            | II – Unimplor                                 | nented bit, read |                  |              |

| u = Bit is uncl         |                                 | x = Bit is unkn                                                                    |                                | •                                             |                  | R/Value at all o | thar Pasata  |

| '1' = Bit is set        | •                               | 0' = Bit is clear                                                                  |                                |                                               |                  |                  |              |

|                         |                                 |                                                                                    | areu                           | q – value dep                                 | ends on condi    |                  |              |

| bit 7                   | See descript<br>1 = System      | isable Periphera<br>ion in <b>Section 7</b><br>clock network di<br>clock network e | .4 "System Cl<br>sabled (Fosc) | k Network bit <sup>(1)</sup><br>ock Disable". |                  |                  |              |

| bit 6                   | 1 = FVR mo                      | able Fixed Volta<br>dule disabled<br>dule enabled                                  | ge Reference                   | bit                                           |                  |                  |              |

| bit 5                   | 1 = HLVD m                      | isable Low-Volta<br>nodule disabled<br>nodule enabled                              | ige Detect bit                 |                                               |                  |                  |              |

| bit 4                   | 1 = CRC mc                      | able CRC Engir<br>odule disabled<br>odule enabled                                  | ne bit                         |                                               |                  |                  |              |

| bit 3                   | 1 = NVM M                       | isable NVM Me<br>emory Scan mo<br>emory Scan mo                                    | dule disabled                  | bit <sup>(2)</sup>                            |                  |                  |              |

| bit 2                   | 1 = All Mem                     | M Module Disal<br>ory reading and<br>odule enabled                                 |                                | bled; NVMCON                                  | registers canr   | not be written   |              |

| bit 1                   | 1 = CLKR m                      | isable Clock Re<br>odule disabled<br>odule enabled                                 | ference bit                    |                                               |                  |                  |              |

| bit 0                   | 1 = IOC mod                     | able Interrupt-on<br>dule(s) disabled<br>dule(s) enabled                           | -Change bit, A                 | ll Ports                                      |                  |                  |              |

|                         | earing the SYS<br>Fosc/4 are no | SCMD bit disable of affected.                                                      | es the system                  | clock (Fosc) to                               | peripherals, h   | owever periphe   | rals clocked |

# REGISTER 7-1: PMD0: PMD CONTROL REGISTER 0

- 2: Subject to SCANE bit in CONFIG4H.

- **3:** When enabling NVM, a delay of up to 1 µs may be required before accessing data.

# 8.14 Power Control (PCON0) Register

The Power Control (PCON0) register contains flag bits to differentiate between a:

- Brown-out Reset (BOR)

- Power-on Reset (POR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Window Violation (WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON0 register bits are shown in Register 8-2.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-3).

Software should reset the bit to the inactive state after restart (hardware will not reset the bit).

Software may also set any PCON0 bit to the active state, so that user code may be tested, but no Reset action will be generated.

| Name    | Bit 7  | Bit 6  | Bit 5      | Bit 4                  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|---------|--------|--------|------------|------------------------|-------|-------|-------|--------|---------------------|

| BORCON  | SBOREN |        |            |                        |       |       |       | BORRDY | 75                  |

| PCON0   | STKOVF | STKUNF | WDTWV      | RWDT                   | RMCLR | RI    | POR   | BOR    | 76                  |

| STATUS  | _      | TO     | PD         | Ν                      | OV    | Z     | DC    | С      | 118                 |

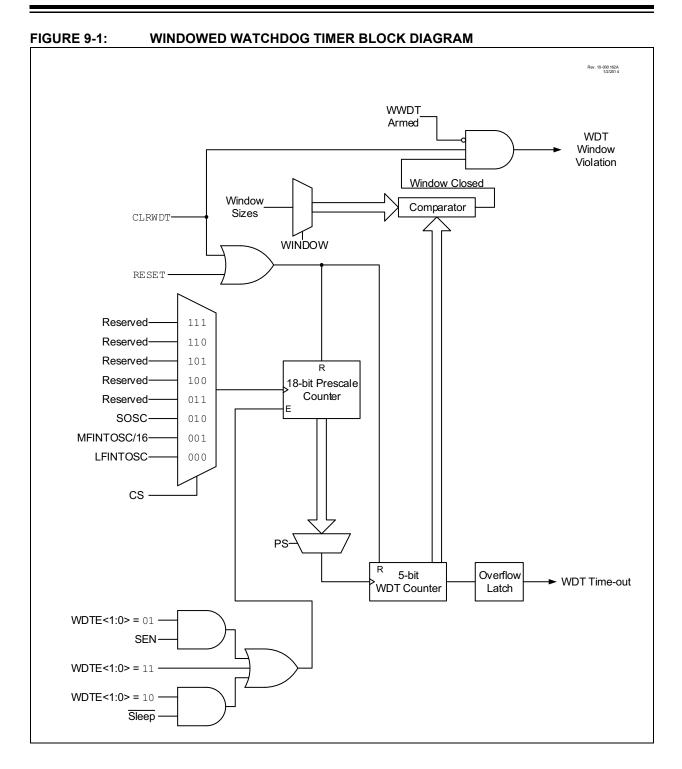

| WDTCON0 | _      | _      |            | WDTPS<4:0>             |       |       |       |        | 85                  |

| WDTCON1 |        | W      | /DTCS<2:0> | DTCS<2:0> — WINDOW<2:0 |       |       |       | )>     | 86                  |

TABLE 8-4: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| Address | Name     | Bit 7                           | Bit 6                                | Bit 5         | Bit 4            | Bit 3          | Bit 2           | Bit 1           | Bit 0            | <u>Value on</u><br>POR, BOR |

|---------|----------|---------------------------------|--------------------------------------|---------------|------------------|----------------|-----------------|-----------------|------------------|-----------------------------|

| FFFh    | TOSU     |                                 | Top of Stack Upper byte (TOS<20:16>) |               |                  |                |                 |                 |                  |                             |

| FFEh    | TOSH     |                                 | I                                    | Тс            | op of Stack High | byte (TOS<15   | :8>)            |                 |                  | xxxxxxxx                    |

| FFDh    | TOSL     |                                 |                                      | Т             | op of Stack Low  | v byte (TOS<7: | 0>)             |                 |                  | xxxxxxxx                    |

| FFCh    | STKPTR   | _                               | —                                    | —             |                  |                | STKPTR<4:0>     |                 |                  | 000000                      |

| FFBh    | PCLATU   | _                               | —                                    | _             |                  | Holding        | Register for PC | <20:16>         |                  | 00000                       |

| FFAh    | PCLATH   |                                 |                                      |               | Holding Regist   | er for PC<15:8 | >               |                 |                  | 00000000                    |

| FF9h    | PCL      |                                 |                                      |               | PC Low byt       | e (PC<7:0>)    |                 |                 |                  | 00000000                    |

| FF8h    | TBLPTRU  | _                               | —                                    |               | Program I        | Memory Table   | Pointer (TBLP1  | R<21:16>)       |                  | 000000                      |

| FF7h    | TBLPTRH  |                                 |                                      | Program       | Memory Table     | Pointer (TBLP  | TR<15:8>)       |                 |                  | 00000000                    |

| FF6h    | TBLPTRL  |                                 |                                      | Program       | n Memory Table   | Pointer (TBLF  | PTR<7:0>)       |                 |                  | 00000000                    |

| FF5h    | TABLAT   |                                 |                                      |               | TAE              | BLAT           |                 |                 |                  | 00000000                    |

| FF4h    | PRODH    |                                 |                                      |               | Product Regi     | ster High byte |                 |                 |                  | xxxxxxxx                    |

| FF3h    | PRODL    |                                 |                                      |               | Product Reg      | ister Low byte |                 |                 |                  | xxxxxxxx                    |

| FF2h    | INTCON   | GIE/GIEH                        | PEIE/GIEL                            | IPEN          | —                | —              | INT2EDG         | INT1EDG         | INT0EDG          | 000111                      |

| FF1h    | -        |                                 |                                      |               | Unimple          | emented        |                 |                 |                  | —                           |

| FF0h    | -        |                                 |                                      |               | Unimple          | emented        |                 |                 |                  | —                           |

| FEFh    | INDF0    | Uses contents                   | of FSR0 to ad                        | dress data me | emory – value of | f FSR0 not cha | inged (not a ph | ysical register | )                |                             |

| FEEh    | POSTINC0 | Uses contents                   | of FSR0 to ad                        | dress data me | emory – value of | f FSR0 post-in | cremented (not  | a physical reg  | jister)          |                             |

| FEDh    | POSTDEC0 | Uses contents                   | of FSR0 to ad                        | dress data me | emory – value of | f FSR0 post-de | cremented (no   | t a physical re | gister)          |                             |

| FECh    | PREINC0  | Uses contents                   | of FSR0 to ad                        | dress data me | emory – value of | f FSR0 pre-inc | remented (not a | a physical regi | ster)            |                             |

| FEBh    | PLUSW0   | Uses contents<br>FSR0 offset by |                                      | dress data me | emory – value of | f FSR0 pre-inc | remented (not a | a physical regi | ster) – value of |                             |

| FEAh    | FSR0H    | -                               | —                                    | —             | —                | Indirect       | t Data Memory   | Address Point   | er 0 High        | xxxx                        |

| FE9h    | FSR0L    |                                 |                                      | Indired       | t Data Memory    | Address Point  | er 0 Low        |                 |                  | xxxxxxx                     |

| FE8h    | WREG     |                                 |                                      |               | Working          | Register       |                 |                 |                  | xxxxxxxx                    |

| FE7h    | INDF1    | Uses c                          | ontents of FSF                       | R0 to address | data memory –    | value of FSR1  | not changed (r  | not a physical  | register)        |                             |

| FE6h    | POSTINC1 | Uses contents                   | of FSR0 to ad                        | dress data me | emory – value of | f FSR1 post-in | cremented (not  | a physical reg  | jister)          |                             |

| FE5h    | POSTDEC1 | Uses contents                   | of FSR0 to ad                        | dress data me | emory – value of | f FSR1 post-de | cremented (no   | t a physical re | gister)          |                             |

| FE4h    | PREINC1  | Uses contents                   | of FSR0 to ad                        | dress data me | emory – value of | f FSR1 pre-inc | remented (not a | a physical regi | ster)            |                             |

| FE3h    | PLUSW1   | Uses contents<br>FSR0 offset by |                                      | dress data me | emory – value of | FSR1 pre-inc   | remented (not a | a physical regi | ster) – value of |                             |

#### REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES **TABLE 10-5**:

Legend:  ${\rm x}$  = unknown,  ${\rm u}$  = unchanged, — = unimplemented,  ${\rm q}$  = value depends on condition

Not available on LF devices. Note 1:

Not available on PIC18(L)F26K40 (28-pin variants).

Not available on PIC18(L)F45K40 devices.

| <b>NEGISTER</b> | 14-II. FILI.I |                     |                | TENADLE          | REGISTER I       |                 |         |  |  |  |

|-----------------|---------------|---------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|

| R/W-0/0         | R/W-0/0       | U-0                 | U-0            | U-0              | U-0              | R/W-0/0         | R/W-0/0 |  |  |  |

| OSCFIE          | CSWIE         | —                   | _              | _                | —                | ADTIE           | ADIE    |  |  |  |

| bit 7           |               |                     |                | ·                |                  |                 | bit 0   |  |  |  |

|                 |               |                     |                |                  |                  |                 |         |  |  |  |

| Legend:         |               |                     |                |                  |                  |                 |         |  |  |  |

| R = Readable    | e bit         | W = Writable        | bit            | U = Unimpler     | mented bit, read | as '0'          |         |  |  |  |

| -n = Value at   | POR           | '1' = Bit is set    |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |

|                 |               |                     |                |                  |                  |                 |         |  |  |  |

| bit 7           | OSCFIE: Osc   | cillator Fail Inter | rupt Enable b  | it               |                  |                 |         |  |  |  |

|                 | 1 = Enabled   |                     |                |                  |                  |                 |         |  |  |  |

|                 | 0 = Disabled  |                     |                |                  |                  |                 |         |  |  |  |

| bit 6           | CSWIE: Cloc   | k-Switch Interru    | upt Enable bit |                  |                  |                 |         |  |  |  |

|                 | 1 = Enabled   |                     |                |                  |                  |                 |         |  |  |  |

|                 | 0 = Disabled  |                     |                |                  |                  |                 |         |  |  |  |

| bit 5-2         | Unimplemen    | ted: Read as '      | כ'             |                  |                  |                 |         |  |  |  |

| bit 1           | ADTIE: ADC    | Threshold Inte      | rrupt Enable b | oit              |                  |                 |         |  |  |  |

|                 | 1 = Enabled   | 1 = Enabled         |                |                  |                  |                 |         |  |  |  |

|                 | 0 = Disabled  |                     |                |                  |                  |                 |         |  |  |  |

| bit 0           | ADIE: ADC Ir  | nterrupt Enable     | bit            |                  |                  |                 |         |  |  |  |

|                 | 1 = Enabled   |                     |                |                  |                  |                 |         |  |  |  |

|                 | 0 = Disabled  |                     |                |                  |                  |                 |         |  |  |  |

|                 |               |                     |                |                  |                  |                 |         |  |  |  |

# REGISTER 14-11: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| Mada              | MODE              | <4:0>                             | Output                                | On creation                                               | Timer Control              |                           |                                   |  |

|-------------------|-------------------|-----------------------------------|---------------------------------------|-----------------------------------------------------------|----------------------------|---------------------------|-----------------------------------|--|

| Mode              | <4:3>             | <2:0>                             | Operation                             | Operation                                                 | Start                      | Reset                     | Stop                              |  |

|                   |                   | 000                               |                                       | Software gate (Figure 20-4)                               | <b>ON =</b> 1              | _                         | ON = 0                            |  |

|                   |                   | 001                               | Period<br>Pulse                       | Hardware gate, active-high<br>(Figure 20-5)               | ON = 1 and<br>TMRx_ers = 1 | _                         | ON = 0 or<br>TMRx_ers = 0         |  |

|                   |                   | 010                               | Fuise                                 | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _                         | ON = 0 or<br>TMRx_ers = 1         |  |

| Free              | 0.0               | 011                               |                                       | Rising or falling edge Reset                              |                            | TMRx_ers                  |                                   |  |

| Running<br>Period | 00                | 100                               | Period                                | Rising edge Reset (Figure 20-6)                           |                            | TMRx_ers ↑                | <b>ON =</b> 0                     |  |

|                   |                   | 101                               | Pulse                                 | Falling edge Reset                                        |                            | TMRx_ers ↓                |                                   |  |

|                   |                   | 110                               | with<br>Hardware                      | Low level Reset                                           | ON = 1                     | TMRx_ers = 0              | ON = 0 or<br>TMRx_ers = 0         |  |

|                   |                   | 111                               | Reset                                 | High level Reset (Figure 20-7)                            |                            | TMRx_ers = 1              | ON = 0 or<br>TMRx_ers = 1         |  |

|                   |                   | 000                               | One-shot                              | Software start (Figure 20-8)                              | <b>ON =</b> 1              | _                         |                                   |  |

|                   |                   | 001                               | Edge                                  | Rising edge start (Figure 20-9)                           | ON = 1 and<br>TMRx_ers ↑   | _                         |                                   |  |

|                   |                   | 010                               | triggered<br>start                    | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                         |                                   |  |

|                   |                   | 011                               | (Note 1)                              | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                         | ON = 0<br>or                      |  |

| One-shot          | 01                | 100                               | Edge                                  | Rising edge start and<br>Rising edge Reset (Figure 20-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑                | Next clock<br>after<br>TMRx = PRx |  |

|                   |                   | 101                               | triggered<br>start                    | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers ↓                | (Note 2)                          |  |

|                   |                   | 110                               | and<br>hardware<br>Reset              | Rising edge start and<br>Low level Reset (Figure 20-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0              |                                   |  |

|                   |                   | 111                               | (Note 1)                              | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1              |                                   |  |

|                   |                   | 000                               |                                       | Rese                                                      | rved                       |                           |                                   |  |

|                   |                   | 001                               | Edge                                  | Rising edge start<br>(Figure 20-12)                       | ON = 1 and<br>TMRx_ers ↑   | —                         | ON = 0<br>or                      |  |

| Mono-stable       |                   | 010                               | triggered<br>start                    | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                         | Next clock<br>after               |  |

|                   |                   | 011                               | (Note 1)                              | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                         | TMRx = PRx<br>( <b>Note 3</b> )   |  |

| Reserved          | 10                | 100                               |                                       | Rese                                                      | rved                       |                           | •                                 |  |

| Reserved          |                   | 101                               |                                       | Rese                                                      | rved                       |                           |                                   |  |

| One-shot          |                   | 110                               | Level<br>triggered                    | High level start and<br>Low level Reset (Figure 20-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0              | ON = 0 or                         |  |

|                   | <sup>111</sup> ha | start<br>and<br>hardware<br>Reset | Low level start &<br>High level Reset | ON = 1 and<br>TMRx_ers = 0                                | TMRx_ers = 1               | Held in Reset<br>(Note 2) |                                   |  |

| Reserved          | 11                | xxx                               |                                       | Rese                                                      | rved                       |                           |                                   |  |

# TABLE 20-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

# REGISTER 21-3: CCPxCAP: CAPTURE INPUT SELECTION MULTIPLEXER REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/x | R/W-0/x |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | _   | _   |     | CTS<    | <1:0>   |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

### bit 7-2 Unimplemented: Read as '0'

bit 1-0 CTS<1:0>: Capture Trigger Input Selection bits

| CTS<1:0> | Connection              |                         |  |  |  |

|----------|-------------------------|-------------------------|--|--|--|

| 013<1.02 | CCP1                    | CCP2                    |  |  |  |

| 11       | IOC_Interrupt           |                         |  |  |  |

| 10       |                         | CMP2_output             |  |  |  |

| 01       | CMP1_output             |                         |  |  |  |

| 00       | Pin selected by CCP1PPS | Pin selected by CCP2PPS |  |  |  |

# REGISTER 21-4: CCPRxL: CCPx REGISTER LOW BYTE

| R/W-x/x     | R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |  |  |  |

|-------------|------------|---------|---------|---------|---------|---------|---------|--|--|--|

|             | CCPRx<7:0> |         |         |         |         |         |         |  |  |  |

| bit 7 bit 0 |            |         |         |         |         |         |         |  |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-0 | MODE = Capture Mode:                           |

|---------|------------------------------------------------|

|         | CCPRxL<7:0>: LSB of captured TMR1 value        |

|         | MODE = Compare Mode:                           |

|         | CCPRxL<7:0>: LSB compared to TMR1 value        |

|         | MODE = PWM Mode && FMT = 0:                    |

|         | CCPRxL<7:0>: CCPW<7:0> - Pulse-Width LS 8 bits |

|         | MODE = PWM Mode && FMT = 1:                    |

|         | CCPRxL<7:6>: CCPW<1:0> - Pulse-Width LS 2 bits |

|         | CCPRxL<5:0>: Not used                          |

© 2015-2017 Microchip Technology Inc.

# PIC18LF26/45/46K40

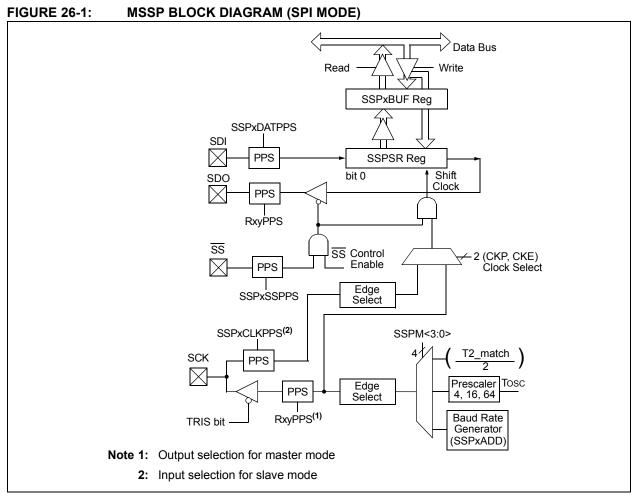

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 26-2 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

| R/W-0         | R/W/HC-0                                                                                                                 | R/W-0                                                                                                               | R/W-0                                                                          | R/W-0                                                 | R/W-0                  | R/W-0                | R/W-0                |

|---------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------|------------------------|----------------------|----------------------|

| WCOL          | SSPOV                                                                                                                    | SSPEN <sup>(1)</sup>                                                                                                | CKP                                                                            | SSPM3 <sup>(2)</sup>                                  | SSPM2 <sup>(2)</sup>   | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7         |                                                                                                                          |                                                                                                                     |                                                                                |                                                       |                        |                      | bit 0                |

|               |                                                                                                                          |                                                                                                                     |                                                                                |                                                       |                        |                      |                      |

| Legend:       |                                                                                                                          |                                                                                                                     |                                                                                |                                                       |                        |                      |                      |

| R = Reada     |                                                                                                                          | W = Writable b                                                                                                      | oit                                                                            |                                                       | eared by hardw         | /are                 |                      |

| -n = Value    | at POR                                                                                                                   | '1' = Bit is set                                                                                                    |                                                                                | '0' = Bit is clea                                     | ared                   | x = Bit is unkr      | nown                 |

| bit 7         | In Master Tra<br>1 = A write t<br>transmis<br>0 = No collis<br>In Slave Tran<br>1 = The SSF<br>software<br>0 = No collis | to the SSPxBUF<br>sion to be starte<br>ion<br><u>smit mode:</u><br>PxBUF register is<br>)                           | <sup>=</sup> register wa<br>d (must be cl<br>s written while                   | eared in softwar                                      | re)                    |                      |                      |

| bit 6         | This is a "don<br>SSPOV: Rec<br>In Receive m<br>1 = A byte is<br>software<br>0 = No overf<br>In Transmit m               | i't care" bit.<br>eive Overflow In<br><u>ode:</u><br>received while t<br>)<br>low                                   | dicator bit<br>he SSPxBUF                                                      | register is still h                                   | holding the prev       | vious byte (mus      | st be cleared in     |

| bit 5         |                                                                                                                          | ter Synchronous                                                                                                     |                                                                                |                                                       |                        |                      |                      |

| bit o         | 1 = Enables t                                                                                                            | he serial port ar serial port and c                                                                                 | nd configures                                                                  | the SDAx and S                                        |                        | ne serial port pi    | ns                   |

| bit 4         | CKP: SCKx F                                                                                                              | Release Control                                                                                                     | bit                                                                            |                                                       |                        |                      |                      |

|               | <u>In Slave mod</u><br>1 = Releases<br>0 = Holds clo<br><u>In Master mo</u><br>Unused in thi                             | clock<br>ck low (clock str<br><u>de:</u>                                                                            | etch), used to                                                                 | o ensure data se                                      | etup time              |                      |                      |

| bit 3-0       | SSPM<3:0>:                                                                                                               | Master Synchro                                                                                                      | nous Serial I                                                                  | Port Mode Selec                                       | ct bits <sup>(2)</sup> |                      |                      |

|               | $1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C M$<br>$0111 = I^{2}C S$                                         | lave mode: 10-bi<br>lave mode: 7-bit<br>irmware Control<br>laster mode: Clo<br>lave mode: 10-bi<br>lave mode: 7-bit | t address with<br>led Master m<br>ock = Fosc/(4<br>bit address <sup>(3,4</sup> | n Start and Stop<br>ode (slave Idle)<br>+* (SSPxADD + | bit interrupts e       |                      |                      |

| Note 1:<br>2: | When enabled, the Bit combinations                                                                                       |                                                                                                                     | -                                                                              | -                                                     | -                      | ed in SPI mode       | e only.              |

# **REGISTER 26-7:** SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C MASTER MODE)

© 2015-2017 Microchip Technology Inc.

| Name     | Bit 7                                  | Bit 6     | Bit 5 | Bit 4      | Bit 3        | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------------------------------------|-----------|-------|------------|--------------|------------|---------|---------|---------------------|

| BAUDxCON | ABDOVF                                 | RCIDL     |       | SCKP       | BRG16        | —          | WUE     | ABDEN   | 395                 |

| INTCON   | GIE/GIEH                               | PEIE/GIEL | IPEN  | -          | —            | INT2EDG    | INT1EDG | INT0EDG | 170                 |

| PIE3     | RC2IE                                  | TX2IE     | RC1IE | TX1IE      | BCL2IE       | SSP2IE     | BCL1IE  | SSP1IE  | 182                 |

| PIR3     | RC2IF                                  | TX2IF     | RC1IF | TX1IF      | BCL2IF       | SSP2IF     | BCL1IF  | SSP1IF  | 174                 |

| IPR3     | RC2IP                                  | TX2IP     | RC1IP | TX1IP      | BCL2IP       | SSP2IP     | BCL1IP  | SSP1IP  | 190                 |

| RCxREG   |                                        |           | EL    | JSARTx Rec | eive Registe | r          |         |         | 399*                |

| RCxSTA   | SPEN                                   | RX9       | SREN  | CREN       | ADDEN        | FERR       | OERR    | RX9D    | 394                 |

| RxyPPS   | _                                      | _         | _     |            |              | RxyPPS<4:0 | >       |         | 218                 |

| RXxPPS   | _                                      | _         | _     |            |              | RXPPS<4:0> | >       |         | 216                 |

| SPxBRGH  | EUSARTx Baud Rate Generator, High Byte |           |       |            |              |            | 404*    |         |                     |

| SPxBRGL  | EUSARTx Baud Rate Generator, Low Byte  |           |       |            |              | 404*       |         |         |                     |

| TXxSTA   | CSRC                                   | TX9       | TXEN  | SYNC       | SENDB        | BRGH       | TRMT    | TX9D    | 393                 |

# TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception. \* Page provides register information.

#### ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES<sup>(1,4)</sup> TABLE 31-1:

| ADC C               | lock Period (TAD)   | Device Frequency (Fosc) |                         |                       |                       |                        |                        |                         |

|---------------------|---------------------|-------------------------|-------------------------|-----------------------|-----------------------|------------------------|------------------------|-------------------------|

| ADC<br>Clock Source | ADCS<5:0>           | 64 MHz                  | 32 MHz                  | 20 MHz                | 16 MHz                | 8 MHz                  | 4 MHz                  | 1 MHz                   |

| Fosc/2              | 000000              | 31.25 ns <sup>(2)</sup> | 62.5 ns <sup>(2)</sup>  | 100 ns <sup>(2)</sup> | 125 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>  | 500 ns <sup>(2)</sup>  | 2.0 μs                  |

| Fosc/4              | 000001              | 62.5 ns <sup>(2)</sup>  | 125 ns <sup>(2)</sup>   | 200 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup>  | 1.0 μs                 | 4.0 μs                  |

| Fosc/6              | 000010              | 125 ns <sup>(2)</sup>   | 187.5 ns <sup>(2)</sup> | 300 ns <sup>(2)</sup> | 375 ns <sup>(2)</sup> | 750 ns <sup>(2)</sup>  | 1.5 μs                 | 6.0 μs                  |

| Fosc/8              | 000011              | 187.5 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>   | 400 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup> | 1.0 μs                 | 2.0 μs                 | 8.0 μs <sup>(3)</sup>   |

|                     |                     |                         |                         |                       |                       |                        |                        |                         |

| Fosc/16             | 000100              | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 800 ns <sup>(2)</sup> | 1.0 μs                | 2.0 μs                 | 4.0 μs                 | 16.0 μs <sup>(3)</sup>  |

|                     |                     |                         |                         |                       |                       |                        |                        |                         |

| Fosc/128            | 111111              | 2.0 μs                  | 4.0 μs                  | 6.4 μs                | 8.0 μs                | 16.0 μs <sup>(3)</sup> | 32.0 μs <sup>(2)</sup> | 128.0 μs <sup>(2)</sup> |

| FRC                 | ADCS(ADCON0<4>) = 1 | 1.0-6.0 μs              | 1.0-6.0 μs              | 1.0-6.0 μs            | 1.0-6.0 μs            | 1.0-6.0 μs             | 1.0-6.0 μs             | 1.0-6.0 μs              |

Legend: Shaded cells are outside of recommended range. Note

1: See TAD parameter for FRC source typical TAD value.

These values violate the required TAD time. 2:

- 3: Outside the recommended TAD time.

- 4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock Fosc. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

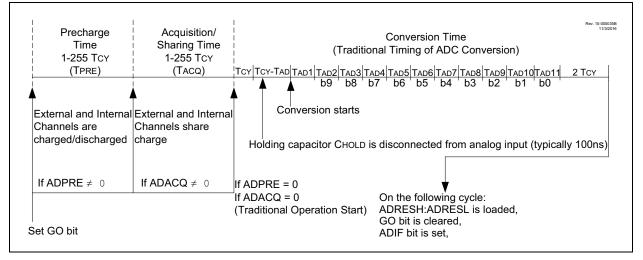

#### **FIGURE 31-2:** ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

# 31.4.2 PRECHARGE CONTROL

The Precharge stage is an optional period of time that brings the external channel and internal sample and hold capacitor to known voltage levels. Precharge is enabled by writing a non-zero value to the ADPRE register. This stage is initiated when an ADC conversion begins, either from setting the ADGO bit, a special event trigger, or a conversion restart from the computation functionality. If the ADPRE register is cleared when an ADC conversion begins, this stage is skipped.

During the precharge time, CHOLD is disconnected from the outer portion of the sample path that leads to the external capacitive sensor and is connected to either VDD or VSS, depending on the value of the ADPPOL bit of ADCON1. At the same time, the port pin logic of the selected analog channel is overridden to drive a digital high or low out, in order to precharge the outer portion of the ADC's sample path, which includes the external sensor. The output polarity of this override is also determined by the ADPPOL bit of ADCON1. The amount of time that this charging needs is controlled by the ADPRE register.

| Note: | The external charging overrides the TRIS       |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|

|       | setting of the respective I/O pin. If there is |  |  |  |  |  |  |

|       | a device attached to this pin, Precharge       |  |  |  |  |  |  |

|       | should not be used.                            |  |  |  |  |  |  |

# 31.4.3 ACQUISITION CONTROL

The Acquisition stage is an optional time for the voltage on the internal sample and hold capacitor to charge or discharge from the selected analog channel. This acquisition time is controlled by the ADACQ register. If ADPRE = 0, acquisition starts at the beginning of conversion. When ADPRE = 1, the acquisition stage begins when precharge ends.

At the start of the acquisition stage, the port pin logic of the selected analog channel is overridden to turn off the digital high/low output drivers so they do not affect the final result of the charge averaging. Also, the selected ADC channel is connected to CHOLD. This allows charge averaging to proceed between the precharged channel and the CHOLD capacitor.

Note: When ADPRE! = 0, acquisition time cannot be '0'. In this case, setting ADACQ to '0' will set a maximum acquisition time (256 ADC clock cycles). When precharge is disabled, setting ADACQ to '0' will disable hardware acquisition time control.

# 31.4.4 GUARD RING OUTPUTS

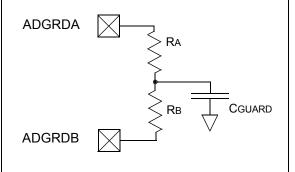

Figure 31-8 shows a typical guard ring circuit. CGUARD represents the capacitance of the guard ring trace placed on the PCB board. The user selects values for RA and RB that will create a voltage profile on CGUARD, which will match the selected acquisition channel.

The purpose of the guard ring is to generate a signal in phase with the CVD sensing signal to minimize the effects of the parasitic capacitance on sensing electrodes. It also can be used as a mutual drive for mutual capacitive sensing. For more information about active guard and mutual drive, see Application Note AN1478, "*mTouch<sup>TM</sup> Sensing Solution Acquisition Methods Capacitive Voltage Divider*" (DS01478).

The ADC has two guard ring drive outputs, ADGRDA and ADGRDB. These outputs can be routed through PPS controls to I/O pins (see **Section 17.0 "Peripheral Pin Select (PPS) Module"** for details) and the polarity of these outputs are controlled by the ADGPOL and ADIPEN bits of ADCON1.

At the start of the first precharge stage, both outputs are set to match the ADGPOL bit of ADCON1. Once the acquisition stage begins, ADGRDA changes polarity, while ADGRDB remains unchanged. When performing a double sample conversion, setting the ADIPEN bit of ADCON1 causes both guard ring outputs to transition to the opposite polarity of ADGPOL at the start of the second precharge stage, and ADGRDA toggles again for the second acquisition. For more information on the timing of the guard ring output, refer to Figure 31-8 and Figure 31-9.

# PIC18(L)F26/45/46K40

| CPF      | SGT                   | Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Compare f with W, skip if f > W    |                 |  |  |  |  |

|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|--|--|--|--|

| Synta    | ax:                   | CPFSGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | f {,a}                             |                 |  |  |  |  |

| Opera    | ands:                 | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                    |                 |  |  |  |  |

| Opera    | ation:                | (f) – (W),<br>skip if (f) > (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . ,                                |                 |  |  |  |  |

| Statu    | s Affected:           | (unsigned o<br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | comparison)                        |                 |  |  |  |  |

| Enco     |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 010a fff                           | f ffff          |  |  |  |  |

|          | ription:              | 0110010affffffffCompares the contents of data memory<br>location 'f' to the contents of the W by<br>performing an unsigned subtraction.If the contents of 'f' are greater than the<br>contents of WREG, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select the<br>GPR bank.If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br> |                                    |                 |  |  |  |  |

| Word     | e.                    | eral Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mode" for det                      | ails.           |  |  |  |  |

| Cycle    |                       | 1(2)<br>Note: 3 cy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | cles if skip and<br>2-word instrue |                 |  |  |  |  |

| QC       | ycle Activity:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |                 |  |  |  |  |

|          | Q1                    | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3                                 | Q4              |  |  |  |  |

|          | Decode                | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Process                            | No              |  |  |  |  |

| lf sk    | ip:                   | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data                               | operation       |  |  |  |  |

|          | Q1                    | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3                                 | Q4              |  |  |  |  |

|          | No                    | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                                 | No              |  |  |  |  |

|          | operation             | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | operation                          | operation       |  |  |  |  |

| lf sk    |                       | d by 2-word in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |                 |  |  |  |  |

|          | Q1                    | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3                                 | Q4              |  |  |  |  |

|          | No                    | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                                 | No              |  |  |  |  |

|          | operation<br>No       | operation<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | operation<br>No                    | operation<br>No |  |  |  |  |

|          | operation             | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | operation                          | operation       |  |  |  |  |

| Example: |                       | HERE<br>NGREATER<br>GREATER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CPFSGT RE<br>:<br>:                | G, 0            |  |  |  |  |

|          | Before Instruc        | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                 |  |  |  |  |

| PC       |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dress (HERE)                       | )               |  |  |  |  |

|          | W<br>After Instructio | = ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |                 |  |  |  |  |

|          | If REG                | > W;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                 |  |  |  |  |

|          | PC                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dress (GREAT                       | TER)            |  |  |  |  |

|          | If REG                | ≤ W;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                 |  |  |  |  |

|          | PC                    | = Ad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | dress (NGREA                       | ATER)           |  |  |  |  |

| CPFSLT             |                             | Compare                                                                                                                       | Compare f with W, skip if f < W                                                                                                                                                                                                                                                                                                                                                                       |       |                |  |  |  |