#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k40t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

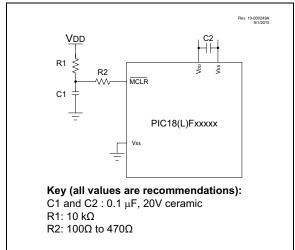

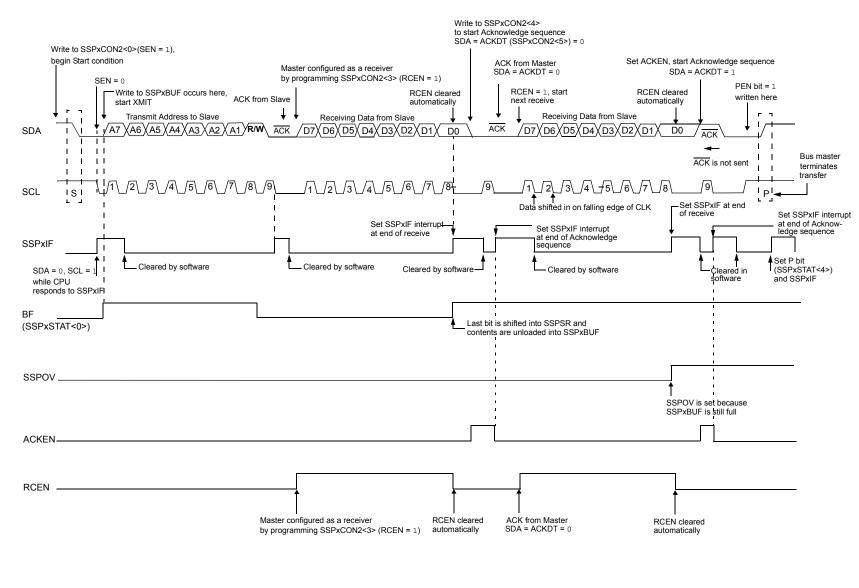

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18(L)F26/45/46K40 MICROCONTROLLERS

## 2.1 Basic Connection Requirements

Getting started with the PIC18(L)F26/45/46K40 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

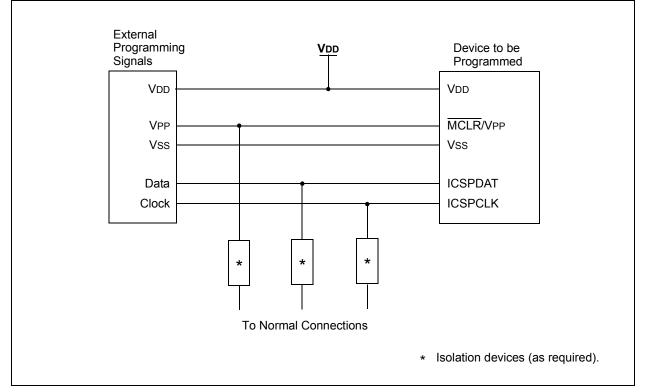

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP<sup>™</sup> Pins"**)

- OSCI and OSCO pins when an external oscillator source is used (see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

The minimum mandatory connections are shown in Figure 2-1.

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

## 2.2 Power Supply Pins

## 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins (VDD and VSS) is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

## 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

| U-1            | U-1            | R/W-1                                | R/W-1                     | R/W-1               | R/W-1                    | R/W-1                | R/W-1                        |  |  |  |

|----------------|----------------|--------------------------------------|---------------------------|---------------------|--------------------------|----------------------|------------------------------|--|--|--|

| _              | _              | WDTCCS<2:0>                          |                           |                     | WDTCWS<2:0               | )>                   |                              |  |  |  |

| bit 7          |                |                                      |                           |                     |                          |                      | bit                          |  |  |  |

|                |                |                                      |                           |                     |                          |                      |                              |  |  |  |

| Legend:        |                |                                      |                           |                     |                          |                      |                              |  |  |  |

| R = Readable   | e bit          | W = Writab                           | e bit                     | U = Unimple         | mented bit, r            | ead as '1'           |                              |  |  |  |

| -n = Value for | blank device   | '1' = Bit is s                       | et                        | '0' = Bit is cl     | eared                    | x = Bit is ur        | nknown                       |  |  |  |

|                |                |                                      |                           |                     |                          |                      |                              |  |  |  |

| bit 7-6        | Unimplement    | ed: Read as                          | '1'                       |                     |                          |                      |                              |  |  |  |

| bit 5-3        | WDTCCS<2:0     | >: WDT Inpu                          | t Clock Selecto           | or bits             |                          |                      |                              |  |  |  |

|                | If WDTE<1:0>   |                                      | 00                        |                     |                          |                      |                              |  |  |  |

|                |                | This bit is ignored.                 |                           |                     |                          |                      |                              |  |  |  |

|                |                | Otherwise:                           |                           |                     |                          |                      |                              |  |  |  |

|                |                | 111 = Software Control               |                           |                     |                          |                      |                              |  |  |  |

|                | 110 <b>- K</b> | 110 = Reserved (Default to LFINTOSC) |                           |                     |                          |                      |                              |  |  |  |

|                | •              |                                      |                           |                     |                          |                      |                              |  |  |  |

|                |                |                                      |                           |                     |                          |                      |                              |  |  |  |

|                | 010 = Re       | eserved (Def                         | ault to LFINTO            | SC)                 |                          |                      |                              |  |  |  |

|                |                |                                      | e clock is the 3          |                     | ITOSC                    |                      |                              |  |  |  |

|                | 000 = W        | DT reference                         | e clock is the 3          | 1.0 kHz LFINT       | OSC (defaul              | t value)             |                              |  |  |  |

| bit 2-0        | WDTCWS<2:0     | )>: WDT Win                          | dow Select bit            | S                   |                          |                      |                              |  |  |  |

|                |                |                                      | WINDOV                    | OOW at POR Software |                          |                      |                              |  |  |  |

|                | WDTCWS         | Value                                | Window de<br>Percent of t |                     | w opening<br>ent of time | control of<br>WINDOW | Keyed<br>access<br>required? |  |  |  |

|                | 111            | 111                                  | n/a                       |                     | 100                      | Yes                  | No                           |  |  |  |

|                | 110            | 111                                  | n/a                       |                     | 100                      |                      |                              |  |  |  |

|                | 101            | 101                                  | 25                        |                     | 75                       |                      |                              |  |  |  |

|                | 100            | 100                                  | 37.5                      |                     | 62.5                     |                      |                              |  |  |  |

|                | 011            | 011                                  | 50                        |                     | 50                       | No                   | Yes                          |  |  |  |

|                |                |                                      | 1                         |                     |                          |                      |                              |  |  |  |

62.5

75

87.5

37.5

25

12.5

## REGISTER 3-6: CONFIGURATION WORD 3H (30 0005h): WINDOWED WATCHDOG TIMER

010

001

000

010

001

000

## 6.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-On-Interrupt bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 6-1, the interrupt occurs during the 2<sup>nd</sup> instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-On-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

#### EXAMPLE 6-1: DOZE SOFTWARE EXAMPLE

```

//Mainline operation

bool somethingToDo = FALSE:

void main()

initializeSystem();

// DOZE = 64:1 (for example)

// ROI = 1;

GIE = 1; // enable interrupts

while (1)

{

// If ADC completed, process data

if (somethingToDo)

{

doSomething();

DOZEN = 1; // resume low-power

}

}

// Data interrupt handler

void interrupt()

// DOZEN = 0 because ROI = 1

if (ADIF)

{

somethingToDo = TRUE;

DOE = 0; // make main() go fast

ADIF = 0;

// else check other interrupts...

if (TMROIF)

{

timerTick++;

DOE = 1; // make main() go slow

TMROIF = 0;

}

```

## 6.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0).

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The PD bit of the STATUS register is cleared (Register 10-2)

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set (Register 10-2)

- 4. The CPU clock is disabled

- 5. LFINTOSC, SOSC, HFINTOSC and ADCRC are unaffected and peripherals using them may continue operation in Sleep.

- I/O ports maintain the status they had before Sleep was executed (driving high, low, or highimpedance)

- 7. Resets other than WDT are not affected by Sleep mode

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module" and Section 28.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

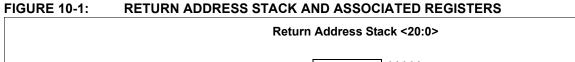

## 10.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 10-1) contains the Stack Pointer value. The STKOVF (Stack Overflow) Status bit and the STKUNF (Stack Underflow) Status bit can be accessed using the PCON0 register. The value of the Stack Pointer can be 0 through 31. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for stack maintenance. After the PC is pushed onto the stack 32 times (without popping any values off the stack), the STKOVF bit is set. The STKOVF bit is cleared by software or by a POR. The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to Section 3.1 "Configuration Words" for a description of the device Configuration bits.)

If STVREN is set (default), a Reset will be generated and a Stack Overflow will be indicated by the STKOVF bit when the 32nd push is initiated. This includes CALL and CALLW instructions, as well as stacking the return address during an interrupt response. The STKOVF bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKOVF bit will be set on the 32nd push and the Stack Pointer will remain at 31 but no Reset will occur. Any additional pushes will overwrite the 31<sup>st</sup> push but the STKPTR will remain at 31.

Setting STKOVF = 1 in software will change the bit, but will not generate a Reset.

The STKUNF bit is set when a stack pop returns a value of zero. The STKUNF bit is cleared by software or by POR. The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 3.1 "Configuration Words"** for a description of the device Configuration bits.)

If STVREN is set (default) and the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC, it will set the STKUNF bit and a Reset will be generated. This condition can be generated by the RETURN, RETLW and RETFIE instructions. If STVREN is cleared, the STKUNF bit will be set, but no Reset will occur.

When STVREN = 0, STKUNF will be set but no Reset will occur.

**Note:** Returning a value of zero to the PC on an underflow has the effect of vectoring the program to the Reset vector, where the stack conditions can be verified and appropriate actions can be taken. This is not the same as a Reset, as the contents of the SFRs are not affected.

#### 10.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

# PIC18LF26/45/46K40

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | ACC     | <7:0>          |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0

**ACC<7:0>:** CRC Accumulator Register bits Writing to this register writes to the CRC accumulator register through the CRC write bus. Reading from this register reads the CRC accumulator.

#### REGISTER 13-7: CRCSHIFTH: CRC SHIFT HIGH BYTE REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|--------|-----|-----|-------|

|       |     |     | SHIFT | <15:8> |     |     |       |

| bit 7 |     |     |       |        |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<15:8>: CRC Shifter Register bits Reading from this register reads the CRC Shifter.

#### REGISTER 13-8: CRCSHIFTL: CRC SHIFT LOW BYTE REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0   | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|-------|-----|-----|-------|

|       |     |     | SHIFT | <7:0> |     |     |       |

| bit 7 |     |     |       |       |     |     | bit 0 |

|       |     |     |       |       |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<7:0>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

<sup>© 2015-2017</sup> Microchip Technology Inc.

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                            | R/W-0/0       | R/W-0/0          | R/W-0/0     |

|------------------|---------|--------------------|---------|------------------------------------|---------------|------------------|-------------|

|                  |         |                    | HADR<   | :15:8> <sup>(1, 2)</sup>           |               |                  |             |

| bit 7            |         |                    |         |                                    |               |                  | bit 0       |

|                  |         |                    |         |                                    |               |                  |             |

| Legend:          |         |                    |         |                                    |               |                  |             |

| R = Readable     | bit     | W = Writable bit   |         | U = Unimplemented bit, read as '0' |               |                  |             |

| u = Bit is unch  | anged   | x = Bit is unknown |         | -n/n = Value a                     | at POR and BO | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                                    |               |                  |             |

#### **REGISTER 13-16: SCANHADRH: SCAN HIGH ADDRESS HIGH BYTE REGISTER**

bit 7-0 HADR<15:8>: Scan End Address bits<sup>(1, 2)</sup>

Most Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 13-17: SCANHADRL: SCAN HIGH ADDRESS LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                 | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|--------------------|---------|-------------------------|------------------|------------------|--------------|

|                  |         |                    | HADR<   | :7:0> <sup>(1, 2)</sup> |                  |                  |              |

| bit 7            |         |                    |         |                         |                  |                  | bit 0        |

|                  |         |                    |         |                         |                  |                  |              |

| Legend:          |         |                    |         |                         |                  |                  |              |

| R = Readable     | bit     | W = Writable bit   |         | U = Unimpler            | mented bit, read | l as '0'         |              |

| u = Bit is uncha | anged   | x = Bit is unknown |         | -n/n = Value            | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                         |                  |                  |              |

bit 7-0 HADR<7:0>: Scan End Address bits<sup>(1, 2)</sup>

Least Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

## 14.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable and priority bits.

## 14.5 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Request Flag registers (PIR0, PIR1, PIR2, PIR3, PIR4, PIR5, PIR6 and PIR7).

## 14.6 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Enable registers (PIE0, PIE1, PIE2, PIE3, PIE4, PIE5, PIE6 and PIE7). When IPEN = 0, the PEIE/GIEL bit must be set to enable any of these peripheral interrupts.

## 14.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Priority registers (IPR0, IPR1, IPR2, IPR3, IPR4 and IPR5, IPR6 and IPR7). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

| U-0           | U-0                                                               | U-0                                                                     | U-0           | U-0              | U-0             | R/W-0/0         | R/W-0/0 |  |  |  |  |

|---------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|---------|--|--|--|--|

|               | —                                                                 | —                                                                       | _             | —                |                 | CCP2IF          | CCP1IF  |  |  |  |  |

| bit 7         |                                                                   |                                                                         |               |                  |                 |                 | bit (   |  |  |  |  |

|               |                                                                   |                                                                         |               |                  |                 |                 |         |  |  |  |  |

| Legend:       |                                                                   |                                                                         |               |                  |                 |                 |         |  |  |  |  |

| R = Readabl   | e bit                                                             | W = Writable I                                                          | bit           |                  | mented bit, rea | id as '0'       |         |  |  |  |  |

| -n = Value at | POR                                                               | '1' = Bit is set                                                        |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |

|               |                                                                   |                                                                         |               |                  |                 |                 |         |  |  |  |  |

| bit 7-2       | Unimplemen                                                        | nted: Read as 'o                                                        | )'            |                  |                 |                 |         |  |  |  |  |

| bit 1         | CCP2IF: ECO                                                       | CP2 Interrupt FI                                                        | ag bit        |                  |                 |                 |         |  |  |  |  |

|               | Capture mod                                                       | <u>e:</u>                                                               |               |                  |                 |                 |         |  |  |  |  |

|               | 1 = A T                                                           | MR register ca                                                          | pture occurre | d (must be clea  | ared in softwar | e)              |         |  |  |  |  |

|               | 0 <b>= No</b>                                                     | TMR register c                                                          | apture occurr | ed               |                 |                 |         |  |  |  |  |

|               | Compare mo                                                        | de:                                                                     |               |                  |                 |                 |         |  |  |  |  |

|               | 1 = A T                                                           | MR register co                                                          | mpare match   | occurred (mus    | t be cleared in | i software)     |         |  |  |  |  |

|               | 0 <b>= No</b>                                                     | TMR register c                                                          | ompare matc   | h occurred       |                 |                 |         |  |  |  |  |

|               | PWM mode:                                                         |                                                                         |               |                  |                 |                 |         |  |  |  |  |

|               | Unused                                                            | d in PWM mode                                                           |               |                  |                 |                 |         |  |  |  |  |

| bit 0         | CCP1IF: ECO                                                       | CP1 Interrupt FI                                                        | ag bit        |                  |                 |                 |         |  |  |  |  |

|               | Capture mode:                                                     |                                                                         |               |                  |                 |                 |         |  |  |  |  |

|               | 1 = A TMR register capture occurred (must be cleared in software) |                                                                         |               |                  |                 |                 |         |  |  |  |  |

|               | 0 <b>= No</b>                                                     | 0 = No TMR register capture occurred                                    |               |                  |                 |                 |         |  |  |  |  |

|               | Compare mo                                                        | Compare mode:                                                           |               |                  |                 |                 |         |  |  |  |  |

|               |                                                                   | 1 = A TMR register compare match occurred (must be cleared in software) |               |                  |                 |                 |         |  |  |  |  |

|               | 0 <b>= No</b>                                                     | TMR register c                                                          | ompare matc   | h occurred       |                 |                 |         |  |  |  |  |

|               | PWM mode:                                                         |                                                                         |               |                  |                 |                 |         |  |  |  |  |

|               | Unused                                                            | d in PWM mode                                                           |               |                  |                 |                 |         |  |  |  |  |

|               |                                                                   |                                                                         |               |                  |                 |                 |         |  |  |  |  |

## REGISTER 14-8: PIR6: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 6

#### 15.2.5 SLEW RATE CONTROL

The SLRCONx register (Register 15-7) controls the slew rate option for each port pin. Slew rate for each port pin can be controlled independently. When an SLRCONx bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONx bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 15.2.6 INPUT THRESHOLD CONTROL

The INLVLx register (Register 15-8) controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-8 for more information on threshold levels.

| Note: | Changing the input threshold selection      |

|-------|---------------------------------------------|

|       | should be performed while all peripheral    |

|       | modules are disabled. Changing the          |

|       | threshold level during the time a module is |

|       | active may inadvertently generate a         |

|       | transition associated with an input pin,    |

|       | regardless of the actual voltage level on   |

|       | that pin.                                   |

#### 15.2.7 WEAK PULL-UP CONTROL

The WPUx register (Register 15-5) controls the individual weak pull-ups for each port pin.

#### 15.2.8 EDGE SELECTABLE INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal at the port pin that has either a rising edge or a falling edge. Any individual pin can be configured to generate an interrupt. The interrupt-on-change module is present on all the pins that are common between 28-pin and 40/44-pin devices. For further details about the IOC module refer to **Section 16.0 "Interrupt-on-Change**".

## 15.3 PORTE Registers

Depending on the device selected, PORTE is implemented in two different ways.

#### 15.3.1 PORTE ON 40/44-PIN DEVICES

For PIC18(L)F4xK40 devices, PORTE is a 4-bit wide port. Three pins (RE0, RE1 and RE2) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

TRISE controls the direction of the REx pins, even when they are being used as analog pins. The user must make sure to keep the pins configured as inputs when using them as analog inputs. RE<2:0> bits have other registers associated with them (i.e., ANSELE, WPUE, INLVLE, SLRCONE and ODCONE). The functionality is similar to the other ports.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

| Note: | On a Power-on Reset, RE<2:0> are |

|-------|----------------------------------|

|       | configured as analog inputs.     |

The fourth pin of PORTE (MCLR/VPP/RE3) is an inputonly pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input-only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

RE3 in PORTE register is a read-only bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

| Note: | On a Power-on Reset, RE3 is enabled as |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|

|       | a digital input only if Master Clea    |  |  |  |  |  |  |  |  |

|       | functionality is disabled.             |  |  |  |  |  |  |  |  |

#### EXAMPLE 15-2: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by   |

|-------|--------|-------------------------|

|       |        | ; clearing output       |

|       |        | ; data latches          |

| CLRF  | LATE   | ; Alternate method      |

|       |        | ; to clear output       |

|       |        | ; data latches          |

| CLRF  | ANSELE | ; Configure analog pins |

|       |        | ; for digital only      |

| MOVLW | 05h    | ; Value used to         |

|       |        | ; initialize data       |

|       |        | ; direction             |

| MOVWF | TRISE  | ; Set RE<0> as input    |

|       |        | ; RE<1> as output       |

|       |        | ; RE<2> as input        |

|       |        |                         |

## 15.3.2 PORTE ON 28-PIN DEVICES

For PIC18(L)F2xK40 devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In this case, PORTE is a single bit, inputonly port comprised of RE3 only. The pin operates as previously described. RE3 in PORTE register is a readonly bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

© 2015-2017 Microchip Technology Inc.

# 16.0 INTERRUPT-ON-CHANGE

PORTA, PORTB, PORTC and pin RE3 of PORTE can be configured to operate as Interrupt-on-Change (IOC) pins on PIC18(L)F2x/4xK40 family devices. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 16-1 is a block diagram of the IOC module.

## 16.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 16.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 16.3 Interrupt Flags

The IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits located in the IOCAF, IOCBF, IOCCF and IOCEF registers respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIRO register reflects the status of all IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits.

# 16.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 16-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

# 16.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

#### 19.8.2 TIMER1/3/5 GATE SOURCE SELECTION

The gate source for Timer1/3/5 can be selected using the GSS<3:0> bits of the TMRxGATE register (Register 19-4). The polarity selection for the gate source is controlled by the TxGPOL bit of the TxGCON register (Register 19-2).

Any of the above mentioned signals can be used to trigger the gate. The output of the CMPx can be synchronized to the Timer1/3/5 clock or left asynchronous. For more information see **Section 32.5.1 "Comparator Output Synchronization**".

#### 19.8.3 TIMER1/3/5 GATE TOGGLE MODE

When Timer1/3/5 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1/3/5 gate signal, as opposed to the duration of a single level pulse.

The Timer1/3/5 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 19-5 for timing details.

Timer1/3/5 Gate Toggle mode is enabled by setting the GTM bit of the TxGCON register. When the GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 19.8.4 TIMER1/3/5 GATE SINGLE-PULSE MODE

When Timer1/3/5 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1/3/5 Gate Single-Pulse mode is first enabled by setting the GSPM bit in the TxGCON register. Next, the GGO/DONE bit in the TxGCON register must be set. The Timer1/3/5 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1/3/5 until the GGO/DONE bit is once again set in software.

Clearing the TxGSPM bit of the TxGCON register will also clear the GGO/DONE bit. See Figure 19-6 for timing details.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1/3/5 gate source to be measured. See Figure 19-7 for timing details.

#### 19.8.5 TIMER1/3/5 GATE VALUE STATUS

When Timer1/3/5 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the GVAL bit in the TxGCON register. The GVAL bit is valid even when the Timer1/3/5 gate is not enabled (GE bit is cleared).

#### 19.8.6 TIMER1/3/5 GATE EVENT INTERRUPT

When Timer1/3/5 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of GVAL occurs, the TMRxGIF flag bit in the PIR5 register will be set. If the TMRxGIE bit in the PIE5 register is set, then an interrupt will be recognized.

The TMRxGIF flag bit operates even when the Timer1/3/5 gate is not enabled (GE bit is cleared).

For more information on selecting high or low priority status for the Timer1/3/5 Gate Event Interrupt see **Section 14.0 "Interrupts"**.

PIC18(L)F26/45/46K4(

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |                   |                             |                |                    |                             |                |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz                                    |            | Fosc = 20.000 MHz           |                | Fosc = 18.432 MHz |                             |                | Fosc = 11.0592 MHz |                             |                |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 26666                       | 300.0          | 0.00              | 16665                       | 300.0          | 0.00               | 15359                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200                                                 | 0.00       | 6666                        | 1200           | -0.01             | 4166                        | 1200           | 0.00               | 3839                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400                                                 | 0.01       | 3332                        | 2400           | 0.02              | 2082                        | 2400           | 0.00               | 1919                        | 2400           | 0.00       | 1151                        |

| 9600   | 9604                                                 | 0.04       | 832                         | 9597           | -0.03             | 520                         | 9600           | 0.00               | 479                         | 9600           | 0.00       | 287                         |

| 10417  | 10417                                                | 0.00       | 767                         | 10417          | 0.00              | 479                         | 10425          | 0.08               | 441                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.18k                                               | -0.08      | 416                         | 19.23k         | 0.16              | 259                         | 19.20k         | 0.00               | 239                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.55k                                               | -0.08      | 138                         | 57.47k         | -0.22             | 86                          | 57.60k         | 0.00               | 79                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 115.9k                                               | 0.64       | 68                          | 116.3k         | 0.94              | 42                          | 115.2k         | 0.00               | 39                          | 115.2k         | 0.00       | 23                          |

## TABLE 27-5: SAMPLE BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |                   |                             |                |                  |                             |                |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                     |            | Fosc = 4.000 MHz            |                | Fosc = 3.6864 MHz |                             |                | Fosc = 1.000 MHz |                             |                |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0          | 0.01              | 3332                        | 300.0          | 0.00             | 3071                        | 300.1          | 0.04       | 832                         |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200           | 0.04              | 832                         | 1200           | 0.00             | 767                         | 1202           | 0.16       | 207                         |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398           | 0.08              | 416                         | 2400           | 0.00             | 383                         | 2404           | 0.16       | 103                         |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615           | 0.16              | 103                         | 9600           | 0.00             | 95                          | 9615           | 0.16       | 25                          |

| 10417  | 10417                                                | 0          | 191                         | 10417          | 0.00              | 95                          | 10473          | 0.53             | 87                          | 10417          | 0.00       | 23                          |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k         | 0.16              | 51                          | 19.20k         | 0.00             | 47                          | 19.23k         | 0.16       | 12                          |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k         | 2.12              | 16                          | 57.60k         | 0.00             | 15                          | _              | _          | _                           |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k         | -3.55             | 8                           | 115.2k         | 0.00             | 7                           | _              |            | —                           |

#### 31.5.8 CONTINUOUS SAMPLING MODE

Setting the ADCONT bit in the ADCON0 register automatically retriggers a new conversion cycle after updating the ADACC register. That means the ADGO bit is set to generate automatic retriggering, until the device Reset occurs or the A/D Stop-on-interrupt bit (ADSOI in the ADCON3 register) is set (correct logic).

#### 31.5.9 DOUBLE SAMPLE CONVERSION

Double sampling is enabled by setting the ADDSEN bit of the ADCON1 register. When this bit is set, two conversions are required before the module will calculate threshold error (each conversion must still be triggered separately). The first conversion will set the ADMATH bit of the ADSTAT register and update ADACC, but will not calculate ADERR or trigger ADTIF. When the second conversion completes, the first value is transferred to ADPREV (depending on the setting of ADPSIS) and the value of the second conversion is placed into ADRES. Only upon the completion of the second conversion is ADERR calculated and ADTIF triggered (depending on the value of ADCALC).

## 31.6 Register Definitions: ADC Control

| R/W-0/0          | R/W-0/0                                                                                                                               | U-0                                                                                                                                               | R/W-0/0         | U-0                             | R/W-0/0          | U-0           | R/W/HC-0         |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|------------------|---------------|------------------|--|--|--|--|

| ADON             | ADCONT                                                                                                                                | -                                                                                                                                                 | ADCS            | -                               | ADFM             | -             | ADGO             |  |  |  |  |

| bit 7            |                                                                                                                                       |                                                                                                                                                   |                 |                                 |                  |               | bit 0            |  |  |  |  |

|                  |                                                                                                                                       |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

| Legend:          |                                                                                                                                       |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

| R = Readable     | e bit                                                                                                                                 | W = Writable                                                                                                                                      | bit             | U = Unimpler                    | nented bit, read | as '0'        |                  |  |  |  |  |

| u = Bit is unc   | hanged                                                                                                                                | x = Bit is unk                                                                                                                                    | nown            | -n/n = Value a                  | at POR and BOP   | R/Value at al | l other Resets   |  |  |  |  |

| '1' = Bit is set | t                                                                                                                                     | '0' = Bit is cle                                                                                                                                  | ared            | HC = Bit is cle                 | eared by hardwa  | are           |                  |  |  |  |  |

|                  |                                                                                                                                       |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

| bit 7            | ADON: ADC                                                                                                                             |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

|                  |                                                                                                                                       | 1 = ADC is enabled<br>0 = ADC is disabled                                                                                                         |                 |                                 |                  |               |                  |  |  |  |  |

| bit 6            |                                                                                                                                       |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

|                  |                                                                                                                                       | ADCONT: ADC Continuous Operation Enable bit<br>1 = ADGO is retriggered upon completion of each conversion trigger until ADTIF is set (if ADSOI is |                 |                                 |                  |               |                  |  |  |  |  |

|                  |                                                                                                                                       | set) or until ADGO is cleared (regardless of the value of ADSOI)                                                                                  |                 |                                 |                  |               |                  |  |  |  |  |

|                  | 0 = ADC is c                                                                                                                          | cleared upon c                                                                                                                                    | ompletion of ea | ach conversion                  | trigger          |               |                  |  |  |  |  |

| bit 5            | Unimplemer                                                                                                                            | nted: Read as                                                                                                                                     | '0'             |                                 |                  |               |                  |  |  |  |  |

| bit 4            |                                                                                                                                       | Clock Selectio                                                                                                                                    |                 |                                 |                  |               |                  |  |  |  |  |

|                  | <ol> <li>Clock supplied from FRC dedicated oscillator</li> <li>Clock supplied by Fosc, divided according to ADCLK register</li> </ol> |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

| bit 3            |                                                                                                                                       | ited: Read as                                                                                                                                     |                 |                                 | (Tegistei        |               |                  |  |  |  |  |

| bit 2            | -                                                                                                                                     |                                                                                                                                                   |                 | ection                          |                  |               |                  |  |  |  |  |

|                  | <b>ADFM:</b> ADC results Format/alignment Selection<br>1 = ADRES and ADPREV data are right-justified                                  |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

|                  |                                                                                                                                       |                                                                                                                                                   |                 | stified, zero-fille             | ed               |               |                  |  |  |  |  |

| bit 1            | Unimplemer                                                                                                                            | nted: Read as                                                                                                                                     | '0'             |                                 |                  |               |                  |  |  |  |  |

|                  | ADGO: ADC                                                                                                                             | Conversion St                                                                                                                                     | atus bit        |                                 |                  |               |                  |  |  |  |  |

| bit 0            | 1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle. The bit is                                     |                                                                                                                                                   |                 |                                 |                  |               |                  |  |  |  |  |

| bit 0            |                                                                                                                                       | •                                                                                                                                                 |                 | Setting this bit s y the ADCONT |                  | conversion c  | ycle. The bit is |  |  |  |  |

#### REGISTER 31-1: ADCON0: ADC CONTROL REGISTER 0

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                         |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| 15 12 11 9 8 7 0                                                                                                                                                                                                                                      |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| b = 3-bit position of bit in file register (f)<br>a = 0 to force Access Bank<br>a = 1 for BSR to select bank<br>f = 8-bit file register address                                                                                                       |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                      |

|                                                                                                                                                                                                                                                       |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

| CALL, GOTO and Branch operations 15 8 7 0                                                                                                                                                                                                             |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

|                                                                                                                                                                                                                                                       | BRA MYFUNC           |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | ERA MILONC           |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | BC MYFUNC            |

© 2015-2017 Microchip Technology Inc.

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2

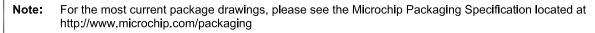

## 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |                |          |      |

|------------------------|-------------|----------------|----------|------|

| Dimensior              | MIN         | NOM            | MAX      |      |

| Number of Pins         | N           |                | 40       |      |

| Pitch                  | е           |                | 0.40 BSC |      |

| Overall Height         | A           | 0.45           | 0.50     | 0.55 |

| Standoff               | A1          | 0.00           | 0.02     | 0.05 |

| Contact Thickness      | A3          | 0.127 REF      |          |      |

| Overall Width          | E           | 5.00 BSC       |          |      |

| Exposed Pad Width      | E2          | 3.60 3.70 3.80 |          |      |

| Overall Length         | D           | 5.00 BSC       |          |      |

| Exposed Pad Length     | D2          | 3.60           | 3.70     | 3.80 |

| Contact Width          | b           | 0.15 0.20 0.25 |          |      |

| Contact Length         | L           | 0.30 0.40 0.50 |          |      |

| Contact-to-Exposed Pad | ĸ           | 0.20           | -        | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.