Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2011.10                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

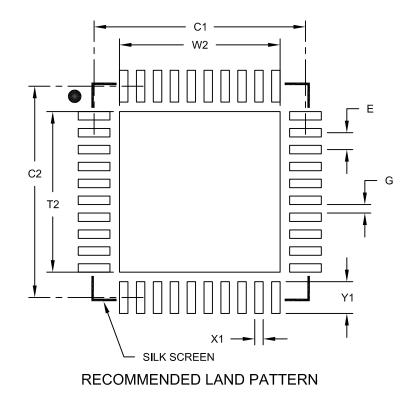

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k40-e-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

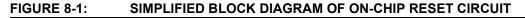

## 8.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 8-1.

|                  | ••••••••••••••••••••••••••••••••••••••• |                   |       |              | ••••••           |                  |              |

|------------------|-----------------------------------------|-------------------|-------|--------------|------------------|------------------|--------------|

| R-0/0            | R-0/0                                   | R-0/0             | R-0/0 | R-0/0        | R-0/0            | R-0/0            | R-0/0        |

|                  | ١                                       | VDTTMR<4:0>       |       |              | STATE            | PSCNT            | <17:16>      |

| bit 7            |                                         |                   |       |              |                  |                  | bit 0        |

|                  |                                         |                   |       |              |                  |                  |              |

| Legend:          |                                         |                   |       |              |                  |                  |              |

| R = Readable b   | R = Readable bit W = Writable bit       |                   |       | U = Unimpler | mented bit, read | l as '0'         |              |

| u = Bit is uncha | anged                                   | x = Bit is unkr   | nown  | -n/n = Value | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared  |              |                  |                  |              |

#### REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ-ONLY)

bit 7-3 WDTTMR<4:0>: Watchdog Window Value bits

| WINDOW | WDT Win     | Open Bereant |              |

|--------|-------------|--------------|--------------|

| WINDOW | Closed      | Open         | Open Percent |

| 111    | N/A         | 00000-11111  | 100          |

| 110    | 00000-00011 | 00100-11111  | 87.5         |

| 101    | 00000-00111 | 01000-11111  | 75           |

| 100    | 00000-01011 | 01100-11111  | 62.5         |

| 011    | 00000-01111 | 10000-11111  | 50           |

| 010    | 00000-10011 | 10100-11111  | 37.5         |

| 001    | 00000-10111 | 11000-11111  | 25           |

| 000    | 00000-11011 | 11100-11111  | 12.5         |

bit 2 STATE: WDT Armed Status bit

1 = WDT is armed

0 = WDT is not armed

## bit 1-0 **PSCNT<17:16>:** Prescale Select Upper Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                  | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|--------------------------|------------------|------------------|-------------|

|                  |         |                   | HADR<   | :15:8> <sup>(1, 2)</sup> |                  |                  |             |

| bit 7            |         |                   |         |                          |                  |                  | bit 0       |

|                  |         |                   |         |                          |                  |                  |             |

| Legend:          |         |                   |         |                          |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler             | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a           | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                          |                  |                  |             |

#### **REGISTER 13-16: SCANHADRH: SCAN HIGH ADDRESS HIGH BYTE REGISTER**

bit 7-0 HADR<15:8>: Scan End Address bits<sup>(1, 2)</sup>

Most Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 13-17: SCANHADRL: SCAN HIGH ADDRESS LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                 | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|--------------------|---------|-------------------------|------------------|------------------|--------------|

|                  |         |                    | HADR<   | :7:0> <sup>(1, 2)</sup> |                  |                  |              |

| bit 7            |         |                    |         |                         |                  |                  | bit 0        |

|                  |         |                    |         |                         |                  |                  |              |

| Legend:          |         |                    |         |                         |                  |                  |              |

| R = Readable     | bit     | W = Writable       | bit     | U = Unimpler            | mented bit, read | l as '0'         |              |

| u = Bit is uncha | anged   | x = Bit is unknown |         | -n/n = Value            | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                         |                  |                  |              |

bit 7-0 HADR<7:0>: Scan End Address bits<sup>(1, 2)</sup>

Least Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

## 14.8 Register Definitions: Interrupt Control

| REGISTER 14-1: | <b>INTCON: INTERRUPT</b> | CONTROL REGISTER |

|----------------|--------------------------|------------------|

|                |                          |                  |

| R/W-0/0               | R/W-0/0                                                                                                                                                                | R/W-0/0                                                                       | U-0                                              | U-0             | R/W-1/1          | R/W-1/1            | R/W-1/1        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------|-----------------|------------------|--------------------|----------------|

| GIE/GIEH              | PEIE/GIEL                                                                                                                                                              | IPEN                                                                          | —                                                | -               | INT2EDG          | INT1EDG            | INT0EDG        |

| bit 7                 |                                                                                                                                                                        | •                                                                             |                                                  |                 |                  | •                  | bit (          |

|                       |                                                                                                                                                                        |                                                                               |                                                  |                 |                  |                    |                |

| Legend:               |                                                                                                                                                                        |                                                                               |                                                  |                 |                  |                    |                |

| R = Readabl           | e bit                                                                                                                                                                  | W = Writable                                                                  | bit                                              | U = Unimple     | emented bit, rea | d as '0'           |                |

| -n = Value at         | POR                                                                                                                                                                    | '1' = Bit is set                                                              |                                                  | '0' = Bit is c  | leared           | x = Bit is unk     | nown           |

| bit 7                 | <b>GIE/GIEH:</b> G<br>If IPEN = 1:                                                                                                                                     | lobal Interrupt I                                                             | Enable bit                                       |                 |                  |                    |                |

|                       |                                                                                                                                                                        | ables all unma<br>sables all interr                                           |                                                  | pts and cleared | by hardware for  | r high-priority ir | nterrupts only |

|                       | 1 = En                                                                                                                                                                 | ables all unmas<br>sables all interru                                         |                                                  | ots and cleared | by hardware for  | all interrupts     |                |

| bit 6                 |                                                                                                                                                                        | Peripheral Inter                                                              | rupt Enable                                      | bit             |                  |                    |                |

|                       | 0 = Dis                                                                                                                                                                | ables all low-pr<br>sables all low-p                                          |                                                  |                 | d by hardware fo | r low-priority in  | terrupts only  |

|                       |                                                                                                                                                                        | ables all unma<br>sables all peripl                                           |                                                  | -               |                  |                    |                |

| bit 5                 | 1 = Enable                                                                                                                                                             | pt Priority Enab<br>priority levels o<br>priority levels o                    | n interrupts                                     | i               |                  |                    |                |

| bit 4-3               | Unimplemen                                                                                                                                                             | ited: Read as 'd                                                              | )'                                               |                 |                  |                    |                |

| bit 2                 | INT2EDG: External Interrupt 2 Edge Select bit<br>1 = Interrupt on rising edge of INT2 pin<br>0 = Interrupt on falling edge of INT2 pin                                 |                                                                               |                                                  |                 |                  |                    |                |

| bit 1                 | <ul> <li>INTIEDG: External Interrupt 1 Edge Select bit</li> <li>1 = Interrupt on rising edge of INT1 pin</li> <li>0 = Interrupt on falling edge of INT1 pin</li> </ul> |                                                                               |                                                  |                 |                  |                    |                |

| bit 0                 | 1 = Interrup                                                                                                                                                           | xternal Interrupt<br>at on rising edge<br>at on falling edge                  | e of INT0 pir                                    | ı               |                  |                    |                |

| co<br>its<br>er<br>th | iterrupt flag bits a<br>ondition occurs, r<br>s corresponding<br>nable bit. User s<br>le appropriate inf                                                               | egardless of the<br>enable bit or the<br>software should<br>terrupt flag bits | e state of<br>ne global<br>d ensure<br>are clear |                 |                  |                    |                |

prior to enabling an interrupt. This feature

allows for software polling.

| U-0                                                                     | U-0        | U-0              | U-0 | U-0                                     | U-0 | R/W-0/0 | R/W-0/0 |

|-------------------------------------------------------------------------|------------|------------------|-----|-----------------------------------------|-----|---------|---------|

| _                                                                       | —          | —                |     | _                                       | —   | CCP2IE  | CCP1IE  |

| bit 7                                                                   |            |                  |     |                                         |     |         | bit 0   |

|                                                                         |            |                  |     |                                         |     |         |         |

| Legend:                                                                 |            |                  |     |                                         |     |         |         |

| R = Readab                                                              | le bit     | W = Writable I   | bit | U = Unimplemented bit, read as '0'      |     |         |         |

| -n = Value a                                                            | t POR      | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |         | nown    |

|                                                                         |            |                  |     |                                         |     |         |         |

| bit 7-2                                                                 | Unimplemen | ted: Read as 'd  | )'  |                                         |     |         |         |

| bit 1 CCP2IE: ECCP2 Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |            |                  |     |                                         |     |         |         |

| bit 0 CCP1IE: ECCP1 Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |            |                  |     |                                         |     |         |         |

#### REGISTER 14-16: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

|                                                                                                                               |            |                  | -   | -                |                  |                 |         |

|-------------------------------------------------------------------------------------------------------------------------------|------------|------------------|-----|------------------|------------------|-----------------|---------|

| R/W-1/1                                                                                                                       | R/W-1/1    | R/W-1/1          | U-0 | U-0              | U-0              | U-0             | R/W-1/1 |

| SCANIP                                                                                                                        | CRCIP      | NVMIP            | _   | —                | —                | —               | CWG1IP  |

| bit 7                                                                                                                         | ·          |                  |     |                  |                  | •               | bit 0   |

|                                                                                                                               |            |                  |     |                  |                  |                 |         |

| Legend:                                                                                                                       |            |                  |     |                  |                  |                 |         |

| R = Readable                                                                                                                  | bit        | W = Writable     | bit | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at                                                                                                                 | POR        | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7 SCANIP: SCAN Interrupt Priority bit<br>1 = High priority<br>0 = Low priority<br>bit 6 CRCIP: CRC Interrupt Priority bit |            |                  |     |                  |                  |                 |         |

| bit 6 CRCIP: CRC Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                                              |            |                  |     |                  |                  |                 |         |

| bit 5 NVMIP: NVM Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                                              |            |                  |     |                  |                  |                 |         |

| bit 4-1                                                                                                                       | Unimplemen | ted: Read as '   | כ'  |                  |                  |                 |         |

| bit 0                                                                                                                         | -          |                  |     |                  |                  |                 |         |

## REGISTER 14-25: IPR7: PERIPHERAL INTERRUPT PRIORITY REGISTER 7

### 18.3 **Programmable Prescaler**

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the T0CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register or the T0CON0, T0CON1 registers or by any Reset.

## 18.4 **Programmable Postscaler**

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the TOOUTPS<3:0> bits of the TOCON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register or the T0CON0, T0CON1 registers or by any Reset.

## 18.5 Operation During Sleep

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

## 18.6 Timer0 Interrupts

The Timer0 interrupt flag bit (TMR0IF) is set when either of the following conditions occur:

- 8-bit TMR0L matches the TMR0H value

- 16-bit TMR0 rolls over from 'FFFFh'

When the postscaler bits (TOOUTPS<3:0>) are set to 1:1 operation (no division), the TOIF flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF flag bit will be set every TOOUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE0 register = '1'), the CPU will be interrupted and the device may wake from Sleep (see Section 18.2 "Clock Source Selection" for more details).

## 18.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see **Section 17.0 "Peripheral Pin Select (PPS) Module**" for additional information). The Timer0 output can also be used by other peripherals, such as the auto-conversion trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 output bit (TOOUT) of the TOCON0 register (Register 18-1).

TMR0\_out will be a pulse of one postscaled clock period when a match occurs between TMR0L and PR0 (Period register for TMR0) in 8-bit mode, or when TMR0 rolls over in 16-bit mode. The Timer0 output is a 50% duty cycle that toggles on each TMR0\_out rising clock edge.

| FIGURE 19-7:           | TIMER1/3/5 GATE SINC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GLE-PULSE AND TOGGLE COMBINED MODE                  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGPOL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGSPM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGTM                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGG <u>O/</u><br>DONE | <ul> <li>Set by software</li> <li>Counting enabled of the set of the</li></ul> | Cleared by hardware on falling edge of TxGVAL       |

| TxG_IN                 | rising edge of TxC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| ТхСКІ                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGVAL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TIMER1/3/5             | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>N + 1</u> <u>N + 2</u> <u>N + 3</u> <u>N + 4</u> |

| TMRxGIF                | <ul> <li>Cleared by software</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Set by hardware on<br>falling edge of TxGVAL —      |

## 19.13 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD1 register. See Section **7.0 "Peripheral Module Disable (PMD)"** for more information.

## 20.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the TxCON register are cleared).

- The diagrams illustrate any clock except Fosc/4 and show clock-sync delays of at least two full cycles for both ON and Timer2\_ers. When using Fosc/4, the clock-sync delay is at least one instruction period for Timer2\_ers; ON applies in the next instruction period.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in Section

21.0 "Capture/Compare/PWM Module".

The signals are not a part of the Timer2 module.

#### 20.5.1 SOFTWARE GATE MODE

This mode corresponds to legacy Timer2 operation. The timer increments with each clock input when ON = 1 and does not increment when ON = 0. When the TMRx count equals the PRx period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 20-4. With PRx = 5, the counter advances until TMRx = 5, and goes to zero with the next clock.

| MODE                          | 0b00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMRx_clk                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Instruction <sup>(1)</sup> —— | BSF BSF BSF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ON                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PRx                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TMRx 0                        | $\begin{array}{c} \begin{array}{c} \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} $ |

| TMRx_postscaled               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PWM Duty                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PWM Output                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

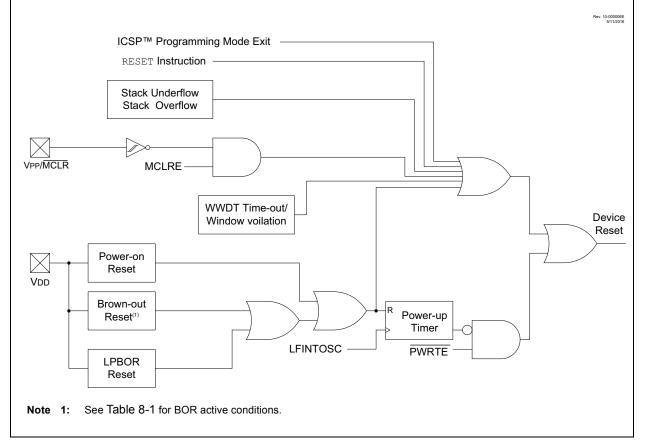

## 20.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 20-7. Selecting MODE<4:0> = 0.0110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 0.0111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

## 21.5.5 PWM DUTY CYCLE

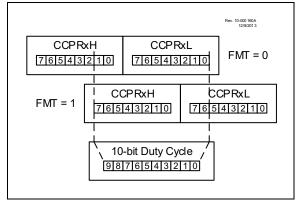

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the FMT bit of the CCPxCON register (see Figure 21-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between PR2 and TMR2.

Equation 21-2 is used to calculate the PWM pulse width.

Equation 21-3 is used to calculate the PWM duty cycle ratio.

FIGURE 21-5: PWM 10-BIT ALIGNMENT

#### EQUATION 21-2: PULSE WIDTH

| Pulse Width = (CCPRx) | H:CCPRxL register pair) • |

|-----------------------|---------------------------|

| Tosc                  | • (TMR2 Prescale Value)   |

## EQUATION 21-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 21-4).

## 21.5.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 21-4.

## EQUATION 21-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | DCH     | <7:0>          |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is unch  | nanged  | x = Bit is unkn   | own     | -n/n = Value a | t POR and BO     | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

#### REGISTER 22-3: PWMxDCH: PWM DUTY CYCLE HIGH BITS

bit 7-0 **DCh<7:0>:** PWM Duty Cycle Most Significant bits These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 22-4: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| DCL<    | :7:6>   | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 DC<8:9>: PWM Duty Cycle Least Significant bits These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register.

bit 5-0 Unimplemented: Read as '0'

## PIC18LF26/45/46K40