Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k40-e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

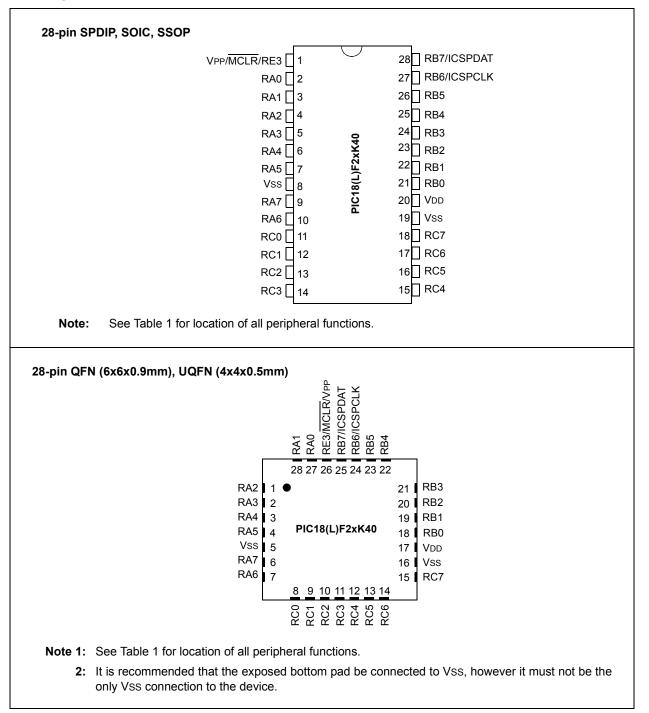

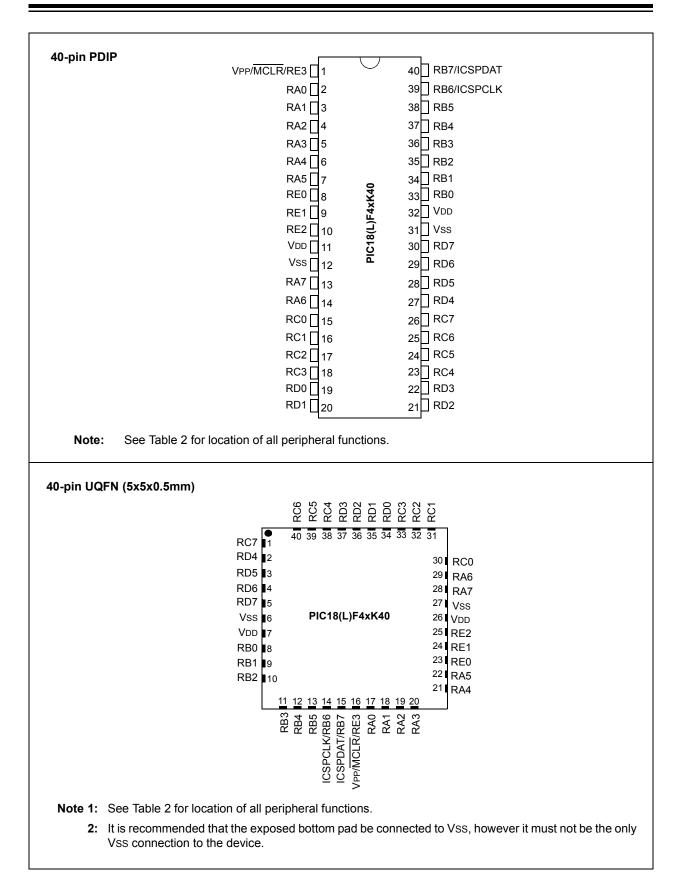

## **Pin Diagrams**

| TABLI              | E 2:        | 40/         | 44-PIN /   | ALLO        | CATION | N TABLE (PI                             | C18(L)F          | -45/46K4                                                           | 40)                 |                     |       |                              |                        |                       |                                              |         |                 |

|--------------------|-------------|-------------|------------|-------------|--------|-----------------------------------------|------------------|--------------------------------------------------------------------|---------------------|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|-----------------|

| I/O <sup>(2)</sup> | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | A/D    | Reference                               | Comparator       | Timers                                                             | ССР                 | CWG                 | ZCD   | Interrupt                    | EUSART                 | WSQ                   | ASSM                                         | Pull-up | Basic           |

| RA0                | 2           | 17          | 19         | 19          | ANA0   | _                                       | C1INO-<br>C2IN0- | _                                                                  | —                   | —                   | _     | IOCA0                        | —                      | _                     | _                                            | Y       | —               |

| RA1                | 3           | 18          | 20         | 20          | ANA1   | —                                       | C1IN1-<br>C2IN1- | -                                                                  | —                   | —                   | _     | IOCA1                        | -                      | —                     | _                                            | Y       | —               |

| RA2                | 4           | 19          | 21         | 21          | ANA2   | DAC1OUT1<br>VREF- (DAC5)<br>VREF- (ADC) | C1IN0+<br>C2IN0+ | -                                                                  | -                   | _                   | _     | IOCA2                        | -                      | —                     | _                                            | Y       | _               |

| RA3                | 5           | 20          | 22         | 22          | ANA3   | VREF+ (DAC5)<br>VREF+ (ADC)             | C1IN1+           | -                                                                  | _                   | _                   |       | IOCA3                        | —                      | MDCIN1 <sup>(1)</sup> | _                                            | Y       | _               |

| RA4                | 6           | 21          | 23         | 23          | ANA4   | _                                       | _                | T0CKI <sup>(1)</sup>                                               | _                   | _                   | _     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Y       | _               |

| RA5                | 7           | 22          | 24         | 24          | ANA5   | _                                       | _                | _                                                                  | _                   | _                   | _     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Y       | _               |

| RA6                | 14          | 29          | 33         | 31          | ANA6   | —                                       | —                | _                                                                  | —                   | —                   | _     | IOCA6                        | _                      | —                     | _                                            | Y       | CLKOUT<br>OSC2  |

| RA7                | 13          | 28          | 32         | 30          | ANA7   | —                                       | _                | -                                                                  | —                   | _                   |       | IOCA7                        | -                      | -                     | _                                            | Y       | OSC1<br>CLKIN   |

| RB0                | 33          | 8           | 9          | 8           | ANB0   | _                                       | C2IN1+           | -                                                                  | _                   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | —                      | _                     | SS2 <sup>(1)</sup>                           | Y       | _               |

| RB1                | 34          | 9           | 10         | 9           | ANB1   | —                                       | C1IN3-<br>C2IN3- | -                                                                  | —                   | —                   |       | IOCB1<br>INT1 <sup>(1)</sup> | -                      | -                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | -               |

| RB2                | 35          | 10          | 11         | 10          | ANB2   | —                                       | -                | -                                                                  | _                   | _                   |       | IOCB2<br>INT2 <sup>(1)</sup> | -                      | -                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | —               |

| RB3                | 36          | 11          | 12         | 11          | ANB3   | —                                       | C1IN2-<br>C2IN2- | -                                                                  | —                   | —                   | -     | IOCB3                        | -                      | —                     | _                                            | Y       | _               |

| RB4                | 37          | 12          | 14         | 14          | ANB4   | —                                       | _                | T5G <sup>(1)</sup>                                                 | _                   | _                   | _     | IOCB4                        | _                      | _                     | _                                            | Y       | _               |

| RB5                | 38          | 13          | 15         | 15          | ANB5   | _                                       | _                | T1G <sup>(1)</sup>                                                 | —                   | _                   | _     | IOCB5                        | _                      | _                     | _                                            | Y       | _               |

| RB6                | 39          | 14          | 16         | 16          | ANB6   | _                                       | _                | —                                                                  | _                   | _                   | _     | IOCB6                        | CK2 <sup>(1)</sup>     | _                     | _                                            | Y       | ICSPCLK         |

| RB7                | 40          | 15          | 17         | 17          | ANB7   | DAC1OUT2                                | _                | T6AIN <sup>(1)</sup>                                               | —                   | _                   | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> | _                     | _                                            | Y       | ICSPDAT         |

| RC0                | 15          | 30          | 34         | 32          | ANC0   | _                                       | -                | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup> | -                   | -                   | Ι     | IOCC0                        | -                      |                       | _                                            | Y       | SOSCO           |

| RC1                | 16          | 31          | 35         | 35          | ANC1   | —                                       | _                | —                                                                  | CCP2 <sup>(1)</sup> | —                   | _     | IOCC1                        | _                      | _                     |                                              | Y       | SOSCIN<br>SOSCI |

## TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC18(L)F45/46K40)

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

**3:** These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I2C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I2C specific or SMBus input buffer thresholds.

|                                                                      | • • ••g                                                                                   |                  |                |               |            |     |          |  |  |  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|----------------|---------------|------------|-----|----------|--|--|--|--|

| U-1                                                                  | U-1                                                                                       | R/W-1            | U-1            | R/W-1         | U-1        | U-1 | R/W-1    |  |  |  |  |

| _                                                                    | _                                                                                         | FCMEN            | _              | CSWEN         |            | _   | CLKOUTEN |  |  |  |  |

| bit 7                                                                | ·                                                                                         |                  |                |               | ·          |     | bit 0    |  |  |  |  |

|                                                                      |                                                                                           |                  |                |               |            |     |          |  |  |  |  |

| Legend:                                                              |                                                                                           |                  |                |               |            |     |          |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '1' |                                                                                           |                  |                |               |            |     |          |  |  |  |  |

| -n = Value fo                                                        | = Value for blank device $(1)^2$ = Bit is set $(0)^2$ = Bit is cleared x = Bit is unknown |                  |                |               |            |     |          |  |  |  |  |

|                                                                      |                                                                                           |                  |                |               |            |     |          |  |  |  |  |

| bit 7-6                                                              | 5 Unimplemented: Read as '1'                                                              |                  |                |               |            |     |          |  |  |  |  |

| bit 5                                                                |                                                                                           | Safe Clock Mor   | nitor Enable b | it            |            |     |          |  |  |  |  |

|                                                                      | 1 = FSCM tin<br>0 = FSCM tin                                                              |                  |                |               |            |     |          |  |  |  |  |

| bit 4                                                                | Unimplemen                                                                                | ted: Read as '1  | ,              |               |            |     |          |  |  |  |  |

| bit 3                                                                | CSWEN: Cloo                                                                               | ck Switch Enabl  | e bit          |               |            |     |          |  |  |  |  |

|                                                                      |                                                                                           | NOSC and ND      |                |               |            |     |          |  |  |  |  |

| <b>h</b> #0.4                                                        |                                                                                           | C and NDIV bit   |                | nanged by use | er soπware |     |          |  |  |  |  |

| bit 2-1                                                              | Unimplemen                                                                                | ted: Read as '1  |                |               |            |     |          |  |  |  |  |

| bit 0                                                                | CLKOUTEN: Clock Out Enable bit<br>If FEXTOSC = HS, XT, LP, then this bit is ignored       |                  |                |               |            |     |          |  |  |  |  |

|                                                                      | <u>Otherwise:</u>                                                                         |                  |                |               |            |     |          |  |  |  |  |

|                                                                      | 1 = CLKOUT function is disabled; I/O or oscillator function on OSC2                       |                  |                |               |            |     |          |  |  |  |  |

|                                                                      | 0 = CLKOUT                                                                                | function is enal | bled; FOSC/4   | clock appears | s at OSC2  |     |          |  |  |  |  |

|                                                                      |                                                                                           |                  |                |               |            |     |          |  |  |  |  |

## REGISTER 3-2: Configuration Word 1H (30 0001h): Oscillators

| Name    | Bit 7  | Bit 6                          | Bit 5     | Bit 4       | Bit 3    | Bit 2 | Bit 1    | Bit 0 | Register<br>on Page |

|---------|--------|--------------------------------|-----------|-------------|----------|-------|----------|-------|---------------------|

| PCON0   | STKOVF | STKUNF                         | WDTWV     | RWDT        | RMCLR    | RI    | POR      | BOR   | 76                  |

| STATUS  | _      | _                              | _         | TO          | PD       | Z     | DC       | С     | 118                 |

| WDTCON0 | _      | _                              |           |             | WDTPS<4: | 0>    |          | SEN   | 85                  |

| WDTCON1 | _      | V                              | /DTCS<2:0 | >           | _        | WI    | NDOW<2:0 | >     | 86                  |

| WDTPSL  |        |                                |           | PSC         | NT<7:0>  |       |          |       | 87                  |

| WDTPSH  |        |                                |           | PSCNT<15:8> |          |       |          |       |                     |

| WDTTMR  |        | WDTTMR<4:0> STATE PSCNT<17:16> |           |             |          |       |          |       |                     |

## TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH WINDOWED WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Windowed Watchdog Timer.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WINDOWED WATCHDOG TIMER

| Name Bits Bit -/7 Bit -/6 Bit 13/5 | Bit 12/4 Bit 11/3 | Bit 10/2 Bit 9/1 |  | egister<br>n Page |

|------------------------------------|-------------------|------------------|--|-------------------|

|------------------------------------|-------------------|------------------|--|-------------------|

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Windowed Watchdog Timer.

| Address | Name                   | Bit 7       | Bit 6          | Bit 5          | Bit 4  | Bit 3    | Bit 2                 | Bit 1                 | Bit 0              | <u>Value on</u><br>POR, BOR |

|---------|------------------------|-------------|----------------|----------------|--------|----------|-----------------------|-----------------------|--------------------|-----------------------------|

| F9Bh    | SP1BRGL                | EUSART1 Ba  | ud Rate Genera | ator, Low Byte | 1      |          |                       |                       |                    | 00000000                    |

| F9Ah    | TX1REG                 | EUSART1 Tra | nsmit Register |                |        |          |                       |                       |                    | 00000000                    |

| F99h    | RC1REG                 | EUSART1 Red | ceive Register |                |        |          |                       |                       |                    | 00000000                    |

| F98h    | SSP1CON3               | ACKTIM      | PCIE           | SCIE           | BOEN   | SDAHT    | SBCDE                 | AHEN                  | DHEN               | 00000000                    |

| F97h    | SSP1CON2               | GCEN        | ACKSTAT        | ACKDT          | ACKEN  | RCEN     | PEN                   | RSEN                  | SEN                | 00000000                    |

| F96h    | SSP1CON1               | WCOL        | SSPOV          | SSPEN          | СКР    |          | SSPN                  | 1<3:0>                |                    | 00000000                    |

| F95h    | SSP1STAT               | SMP         | CKE            | D/Ā            | Р      | S        | R/W                   | UA                    | BF                 | 00000000                    |

| F94h    | SSP1MSK                |             |                | I              | MSł    | <7:0>    |                       |                       |                    | 11111111                    |

| F93h    | SSP1ADD                |             |                |                | ADE    | )<7:0>   |                       |                       |                    | 00000000                    |

| F92h    | SSP1BUF                |             |                |                | BUF    | <7:0>    |                       |                       |                    | xxxxxxx                     |

| F91h    | PORTE                  | _           | _              | —              | —      | RE0      | RE2 <sup>(2)</sup>    | RE1 <sup>(2)</sup>    | RE1 <sup>(2)</sup> | xxxx                        |

| F90h    | PORTD <sup>(2)</sup>   | RD7         | RD6            | RD5            | RD4    | RD3      | RD2                   | RD1                   | RD0                | xxxxxxx                     |

| F8Fh    | PORTC                  | RC7         | RC6            | RC5            | RC4    | RC3      | RC2                   | RC1                   | RC0                | xxxxxxx                     |

| F8Eh    | PORTB                  | RB7         | RB6            | RB5            | RB4    | RB3      | RB2                   | RB1                   | RB0                | xxxxxxx                     |

| F8Dh    | PORTA                  | RA7         | RA6            | RA5            | RA4    | RA3      | RA2                   | RA1                   | RA0                | xxxxxxx                     |

| F8Ch    | TRISE                  | _           | _              | _              | _      | _        | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0             | 111                         |

| F8Bh    | TRISD <sup>(2)</sup>   | TRISD7      | TRISD6         | TRISD5         | TRISD4 | TRISD3   | TRISD2                | TRISD1                | TRISD0             | 11111111                    |

| F8Ah    | TRISC                  | TRISC7      | TRISC6         | TRISC5         | TRISC4 | TRISC3   | TRISC2                | TRISC1                | TRISC0             | 11111111                    |

| F89h    | TRISB                  | TRISB7      | TRISB6         | TRISB5         | TRISB4 | TRISB3   | TRISB2                | TRISB1                | TRISB0             | 11111111                    |

| F88h    | TRISA                  | TRISA7      | TRISA6         | TRISA5         | TRISA4 | TRISA3   | TRISA2                | TRISA1                | TRISA0             | 11111111                    |

| F87h    | LATE                   | _           | _              | _              | _      | _        | LATE2 <sup>(2)</sup>  | LATE1 <sup>(2)</sup>  | LATE0              | xxx                         |

| F86h    | LATD <sup>(2)</sup>    | LATD7       | LATD6          | LATD5          | LATD4  | LATD3    | LATD2                 | LATD1                 | LATD0              | xxxxxxx                     |

| F85h    | LATC                   | LATC7       | LATC6          | LATC5          | LATC4  | LATC3    | LATC2                 | LATC1                 | LATC0              | xxxxxxx                     |

| F84h    | LATB                   | LATB7       | LATB6          | LATB5          | LATB4  | LATB3    | LATB2                 | LATB1                 | LATB0              | xxxxxxx                     |

| F83h    | LATA                   | LATA7       | LATA6          | LATA5          | LATA4  | LATA3    | LATA2                 | LATA1                 | LATA0              | xxxxxxx                     |

| F82h    | NVMCON2                |             |                |                | NVMC   | DN2<7:0> |                       |                       |                    | 00000000                    |

| F81h    | NVMCON1                | NVMRE       | G<1:0>         | _              | FREE   | WRERR    | WREN                  | WR                    | RD                 | 00-0x000                    |

| F80h    | NVMDAT                 |             |                |                | NVMD   | AT<7:0>  |                       |                       |                    | 00000000                    |

| F7Fh    | NVMADRH <sup>(3)</sup> | _           | _              | —              | —      | —        | -                     | NVMA                  | DR<9:8>            | xx                          |

| F7Eh    | NVMADRL                |             |                |                | NVMA   | DR<7:0>  |                       |                       |                    | xxxxxxx                     |

| F7Dh    | CRCCON1                |             | DLEN           | <3:0>          |        |          | PLEN                  | I<3:0>                |                    | 00000000                    |

| F7Ch    | CRCCON0                | EN          | GO             | BUSY           | ACCM   |          | _                     | SHIFTM                | FULL               | 000000                      |

| F7Bh    | CRCXORH                |             |                |                | Х<     | 15:8>    |                       |                       |                    | xxxxxxx                     |

| F7Ah    | CRCXORL                |             |                |                | X<7:1> |          |                       |                       | _                  | xxxxxxx0                    |

| F79h    | CRCSHIFTH              |             |                |                | SHIF   | ۲<15:8>  |                       |                       |                    | 00000000                    |

| F78h    | CRCSHIFTL              |             |                |                | SHIF   | T<7:0>   |                       |                       |                    | 00000000                    |

| F77h    | CRCACCH                |             |                |                | ACC    | <15:8>   |                       |                       |                    | 00000000                    |

| F76h    | CRCACCL                |             |                |                | ACC    | <7:0>    |                       |                       |                    | 00000000                    |

| F75h    | CRCDATH                |             |                |                | DATA   | <15:8>   |                       |                       |                    | xxxxxxx                     |

#### **TABLE 10-5**: REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES (CONTINUED)

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F26K40 (28-pin variants).

3: Not available on PIC18(L)F45K40 devices.

# 10.5 Register Definitions: Status

| REGISTER '    | 10-2: STATL                                                          | JS: STATUS                          |                  |                      |                               |                   |           |

|---------------|----------------------------------------------------------------------|-------------------------------------|------------------|----------------------|-------------------------------|-------------------|-----------|

| U-0           | R-1/q                                                                | R-1/q                               | R/W-0/u          | R/W-0/u              | R/W-0/u                       | R/W-0/u           | R/W-0/u   |

| _             | TO                                                                   | PD                                  | Ν                | OV                   | Z                             | DC                | С         |

| oit 7         |                                                                      |                                     |                  |                      |                               |                   | bit       |

|               |                                                                      |                                     |                  |                      |                               |                   |           |

| Legend:       |                                                                      |                                     |                  |                      |                               |                   |           |

| R = Readable  |                                                                      | W = Writable                        |                  | •                    | nented bit, read              |                   |           |

| -n = Value at | POR                                                                  | '1' = Bit is se                     | l                | '0' = Bit is cle     | ared                          | x = Bit is unkr   | nown      |

| bit 7         | Unimplomor                                                           | ited: Read as                       | 0'               |                      |                               |                   |           |

| bit 6         | TO: Time-Ou                                                          |                                     | U                |                      |                               |                   |           |

|               |                                                                      |                                     | execution of CI  | LRWDT <b>OF</b> SLEE | P instruction                 |                   |           |

|               |                                                                      | ime-out occurr                      |                  |                      |                               |                   |           |

| bit 5         | PD: Power-D                                                          | own bit                             |                  |                      |                               |                   |           |

|               |                                                                      |                                     |                  | LRWDT instructi      | on                            |                   |           |

|               | •                                                                    | xecution of the                     |                  |                      |                               |                   |           |

| bit 4         | ALU MSb = 1                                                          |                                     | ned arithmetic   | (2's compleme        | ent); indicates if            | the result is ne  | egative,  |

|               | 1 = The resu                                                         |                                     |                  |                      |                               |                   |           |

|               | 0 = The resu                                                         |                                     |                  |                      |                               |                   |           |

| bit 3         |                                                                      |                                     |                  |                      |                               | an overflow of    | the 7-bit |

|               | -                                                                    |                                     |                  | 7) to change st      |                               |                   |           |

|               | 1 = Overflow 0 = No overflow 1 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = |                                     | urrent signed    | arithmetic oper      | ration                        |                   |           |

| bit 2         | Z: Zero bit                                                          |                                     |                  |                      |                               |                   |           |

|               | 1 = The resu                                                         | It of an arithme                    | etic or logic op | eration is zero      |                               |                   |           |

|               |                                                                      |                                     | •                | eration is not z     |                               |                   |           |

| bit 1         | •                                                                    | •                                   |                  |                      | rF instructions) <sup>(</sup> | 1)                |           |

|               |                                                                      | out from the 4th<br>-out from the 4 |                  | of the result of     | ccurred                       |                   |           |

| bit 0         | -                                                                    |                                     |                  | JW, SUBWF instr      | (1,2)                         |                   |           |

|               | •                                                                    | •                                   |                  | bit of the result    | ,                             |                   |           |

|               |                                                                      |                                     |                  | nt bit of the resu   |                               |                   |           |

|               | Borrow, the pola                                                     | arity is reversed                   | d. A subtractio  | n is executed b      | by adding the tw              | vo's complemer    | nt of the |

|               | ond operand.                                                         | <i>.</i>                            |                  |                      |                               |                   | •         |

| 2: For        | Rotate (RRF, RL                                                      | F) Instructions,                    | this bit is load | ded with either      | the high or low-              | -order bit of the | Source    |

# REGISTER 10-2: STATUS: STATUS REGISTER

2: For Rotate (RRF, RLF) instructions, this bit is loaded with either the high or low-order bit of the Source register.

| U-0              | U-0   | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0             | R/W-0/0          | R/W-0/0     |

|------------------|-------|-------------------|---------|----------------|---------------------|------------------|-------------|

| —                | —     |                   |         | LADR<2         | 21:16> <b>(1,2)</b> |                  |             |

| bit 7            |       |                   |         |                |                     |                  | bit 0       |

|                  |       |                   |         |                |                     |                  |             |

| Legend:          |       |                   |         |                |                     |                  |             |

| R = Readable b   | oit   | W = Writable      | bit     | U = Unimplen   | nented bit, read    | l as '0'         |             |

| u = Bit is uncha | anged | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BO       | R/Value at all o | ther Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                |                     |                  |             |

#### REGISTER 13-12: SCANLADRU: SCAN LOW ADDRESS UPPER BYTE REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 LADR<21:16>: Scan Start/Current Address bits<sup>(1,2)</sup> Upper bits of the current address to be fetched from, value increments on each fetch of memory.

2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 13-13: SCANLADRH: SCAN LOW ADDRESS HIGH BYTE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|---------|---------|---------|---------|------------------------|---------|---------|---------|--|--|

|         |         |         | LADR<1  | 5:8> <sup>(1, 2)</sup> |         |         |         |  |  |

| bit 7   |         |         |         |                        |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LADR<15:8>: Scan Start/Current Address bits<sup>(1, 2)</sup> Most Significant bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

**Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

## 14.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable and priority bits.

## 14.5 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Request Flag registers (PIR0, PIR1, PIR2, PIR3, PIR4, PIR5, PIR6 and PIR7).

# 14.6 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Enable registers (PIE0, PIE1, PIE2, PIE3, PIE4, PIE5, PIE6 and PIE7). When IPEN = 0, the PEIE/GIEL bit must be set to enable any of these peripheral interrupts.

# 14.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Priority registers (IPR0, IPR1, IPR2, IPR3, IPR4 and IPR5, IPR6 and IPR7). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

| R/W-0/0         | R/W-0/0                     | R/W-0/0              | R-/W0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0         | R/W-0/0 |

|-----------------|-----------------------------|----------------------|-----------------|-------------------|------------------|-----------------|---------|

| RC2IE           | TX2IE                       | RC1IE                | TX1IE           | BCL2IE            | SSP2IE           | BCL1IE          | SSP1IE  |

| bit 7           |                             |                      |                 |                   |                  |                 | bit (   |

| <u> </u>        |                             |                      |                 |                   |                  |                 |         |

| Legend:         |                             |                      |                 |                   |                  |                 |         |

| R = Readable    |                             | W = Writable         |                 | •                 | nented bit, read |                 |         |

| -n = Value at I | POR                         | '1' = Bit is set     |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| h:+ 7           |                             |                      | laters at Each  | le hit            |                  |                 |         |

| bit 7           | 1 = Enabled                 | ART2 Receive         | interrupt Enac  | bie bit           |                  |                 |         |

|                 | 1 = Enabled<br>0 = Disabled | I                    |                 |                   |                  |                 |         |

| bit 6           | TX2IE: EUSA                 | ART2 Transmit        | Interrupt Enat  | ole bit           |                  |                 |         |

|                 | 1 = Enabled                 |                      | -               |                   |                  |                 |         |

|                 | 0 = Disabled                | I                    |                 |                   |                  |                 |         |

| bit 5           | RC1IE: EUS/                 | ART1 Receive         | Interrupt Enab  | ole bit           |                  |                 |         |

|                 | 1 = Enabled                 |                      |                 |                   |                  |                 |         |

|                 | 0 = Disabled                |                      |                 |                   |                  |                 |         |

| bit 4           |                             | ART1 Transmit        | Interrupt Enat  | ble bit           |                  |                 |         |

|                 | 1 = Enabled<br>0 = Disabled | ı                    |                 |                   |                  |                 |         |

| bit 3           |                             | '<br>SP2 Bus Collisi | on Interrunt F  | nable bit         |                  |                 |         |

| bit 0           | 1 = Enabled                 |                      |                 |                   |                  |                 |         |

|                 | 0 = Disabled                | l                    |                 |                   |                  |                 |         |

| bit 2           | SSP2IE: Syn                 | chronous Seria       | I Port 2 Interr | upt Enable bit    |                  |                 |         |

|                 | 1 = Enabled                 |                      |                 |                   |                  |                 |         |

|                 | 0 = Disabled                | l                    |                 |                   |                  |                 |         |

| bit 1           |                             | SP1 Bus Collis       | on Interrupt E  | nable bit         |                  |                 |         |

|                 | 1 = Enabled                 |                      |                 |                   |                  |                 |         |

|                 | 0 = Disabled                |                      |                 |                   |                  |                 |         |

| bit 0           | •                           | chronous Seria       | I Port 1 Interr | upt Enable bit    |                  |                 |         |

|                 | 1 = Enabled<br>0 = Disabled | I                    |                 |                   |                  |                 |         |

|                 |                             | 1                    |                 |                   |                  |                 |         |

# REGISTER 14-13: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

|                        | PPS Input  | Default Pin         | Register Reset  | Inpu  | t Avai | lable f | rom S | elect  | ed PC | RTx |

|------------------------|------------|---------------------|-----------------|-------|--------|---------|-------|--------|-------|-----|

| Peripheral             | Register   | Selection<br>at POR | Value<br>at POR | PIC18 | B(L)F2 | 6K40    | PIC   | 18(L)F | 45/46 | K40 |

| Interrupt 0            | INT0PPS    | RB0                 | 5'b0 1000       | Α     | В      | _       | А     | В      |       | _   |

| Interrupt 1            | INT1PPS    | RB1                 | 5'b0 1001       | А     | В      | _       | А     | В      | _     | _   |

| Interrupt 2            | INT2PPS    | RB2                 | 5'b0 1010       | А     | В      |         | А     | В      | _     | _   |

| Timer0 Clock           | TOCKIPPS   | RA4                 | 5'b0 0100       | А     | В      |         | А     | В      | _     | _   |

| Timer1 Clock           | T1CKIPPS   | RC0                 | 5'bl 0000       | А     | _      | С       | А     | _      | С     | _   |

| Timer1 Gate            | T1GPPS     | RB5                 | 5'b0 1101       | _     | В      | С       | _     | В      | С     | _   |

| Timer3 Clock           | T3CKIPPS   | RC0                 | 5'b1 0000       | _     | В      | С       | _     | В      | С     | _   |

| Timer3 Gate            | T3GPPS     | RC0                 | 5'b1 0000       | А     | _      | С       | А     | _      | С     |     |

| Timer5 Clock           | T5CKIPPS   | RC2                 | 5'b1 0010       | А     | _      | С       | А     | _      | С     |     |

| Timer5 Gate            | T5GPPS     | RB4                 | 5'b0 1100       | _     | В      | С       | _     | В      | _     | D   |

| Timer2 Clock           | T2INPPS    | RC3                 | 5'b1 0011       | А     | _      | С       | А     | _      | С     | _   |

| Timer4 Clock           | T4INPPS    | RC5                 | 5'b1 0101       | _     | В      | С       | _     | В      | С     |     |

| Timer6 Clock           | T6INPPS    | RB7                 | 5'b0 1111       | _     | В      | С       | _     | В      | _     | D   |

| CCP1                   | CCP1PPS    | RC2                 | 5'b1 0010       | _     | В      | С       |       | В      | С     | _   |

| CCP2                   | CCP2PPS    | RC1                 | 5'b1 0001       | _     | В      | С       | _     | В      | С     |     |

| CWG                    | CWG1PPS    | RB0                 | 5'b0 1000       | _     | В      | С       | _     | В      | _     | D   |

| DSM Carrier Low        | MDCARLPPS  | RA3                 | 5'b0 0011       | А     | _      | С       | А     | _      | _     | D   |

| DSM Carrier High       | MDCARHPPS  | RA4                 | 5'b0 0100       | А     | _      | С       | А     | _      | _     | D   |

| DSM Source             | MDSRCPPS   | RA5                 | 5'b0 0101       | А     |        | С       | А     | _      | _     | D   |

| ADC Conversion Trigger | ADACTPPS   | RB4                 | 5'b0 1100       | _     | В      | С       | _     | В      | _     | D   |

| MSSP1 Clock            | SSP1CLKPPS | RC3                 | 5'bl 0011       | _     | В      | С       | _     | В      | С     | _   |

| MSSP1 Data             | SSP1DATPPS | RC4                 | 5'bl 0100       | —     | В      | С       | _     | В      | С     | _   |

| MSSP1 Slave Select     | SSP1SSPPS  | RA5                 | 5'b0 0101       | А     | _      | С       | А     | _      | _     | D   |

| MSSP2 Clock            | SSP2CLKPPS | RB1                 | 5'b0 1001       | _     | В      | С       | _     | В      | _     | D   |

| MSSP2 Data             | SSP2DATPPS | RB2                 | 5'b0 1010       | _     | В      | С       | _     | В      | _     | D   |

| MSSP2 Slave Select     | SSP2SSPPS  | RB0                 | 5'b0 1000       | _     | В      | С       | _     | В      | _     | D   |

| EUSART1 Receive        | RX1PPS     | RC7                 | 5'bl 0111       | _     | В      | С       | _     | В      | С     | _   |

| EUSART1 Transmit       | TX1PPS     | RC6                 | 5'b1 0110       | _     | В      | С       |       | В      | С     | _   |

| EUSART2 Receive        | RX2PPS     | RB7                 | 5'b0 1111       | _     | В      | С       | _     | В      | _     | D   |

| EUSART2 Transmit       | TX2PPS     | RB6                 | 5'b0 1110       | _     | В      | С       | _     | В      | _     | D   |

TABLE 17-1:PPS INPUT REGISTER DETAILS

| REGISTER 20-4: | TxRST: TIMER2 EXTERNAL RESET SIGNAL SELECTION REGISTER |

|----------------|--------------------------------------------------------|

|----------------|--------------------------------------------------------|

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | —   |     | —   |         | RSEL    | <3:0>   |         |

| bit 7 |     |     | •   |         |         |         | bit 0   |

|       |     |     |     |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7-4 Unimplemented: Read as '0'

bit 3-0 RSEL<3:0>: Timer2 External Reset Signal Source Selection bits

| RSEL<3:0> | TMR2                    | TMR4                    | TMR6                    |

|-----------|-------------------------|-------------------------|-------------------------|

| RSEL<3.02 | Reset Source            | Reset Source            | Reset Source            |

| 1011-1111 | Reserved                | Reserved                | Reserved                |

| 1010      | ZCD_OUT                 | ZCD_OUT                 | ZCD_OUT                 |

| 1001      | CMP2OUT                 | CMP2OUT                 | CMP2OUT                 |

| 1000      | CMP1OUT                 | CMP1OUT                 | CMP1OUT                 |

| 0111      | PWM4OUT                 | PWM4OUT                 | PWM4OUT                 |

| 0110      | PWM3OUT                 | PWM3OUT                 | PWM3OUT                 |

| 0101      | CCP2OUT                 | CCP2OUT                 | CCP2OUT                 |

| 0100      | CCP1OUT                 | CCP10UT                 | CCP1OUT                 |

| 0011      | TMR6 post-scaled        | TMR6 post-scaled        | Reserved                |

| 0010      | TMR4 post-scaled        | Reserved                | TMR4 post-scaled        |

| 0001      | Reserved                | TMR2 post-scaled        | TMR2 post-scaled        |

| 0000      | Pin selected by T2INPPS | Pin selected by T4INPPS | Pin selected by T6INPPS |

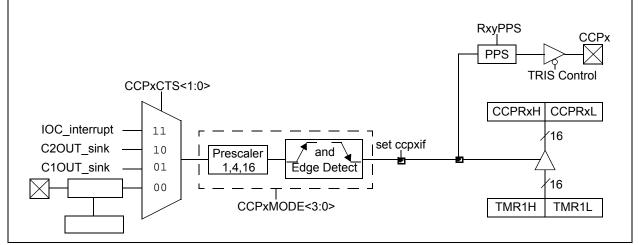

# 21.3 Capture Mode

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the capture source, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMRxH:TMRxL register pair, respectively. An event is defined as one of the following and is configured by the MODE<3:0> bits of the CCPxCON register:

- · Every falling edge of CCPx input

- Every rising edge of CCPx input

- Every 4th rising edge of CCPx input

- · Every 16th rising edge of CCPx input

- Every edge of CCPx input (rising or falling)

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIR6 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH:CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Note: If an event occurs during a 2-byte read, the high and low-byte data will be from different events. It is recommended while reading the CCPRxH:CCPRxL register pair to either disable the module or read the register pair twice for data integrity.

Figure 21-1 shows a simplified diagram of the capture operation.

## 21.3.1 CAPTURE SOURCES

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

The capture source is selected by configuring the CTS<1:0> bits of the CCPxCAP register. The following sources can be selected:

- · Pin selected by CCPxPPS

- C1\_output

- C2\_output

- IOC\_interrupt

## 21.3.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

• See Section 19.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

PIC18(L)F26/45/46K4(

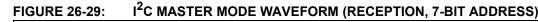

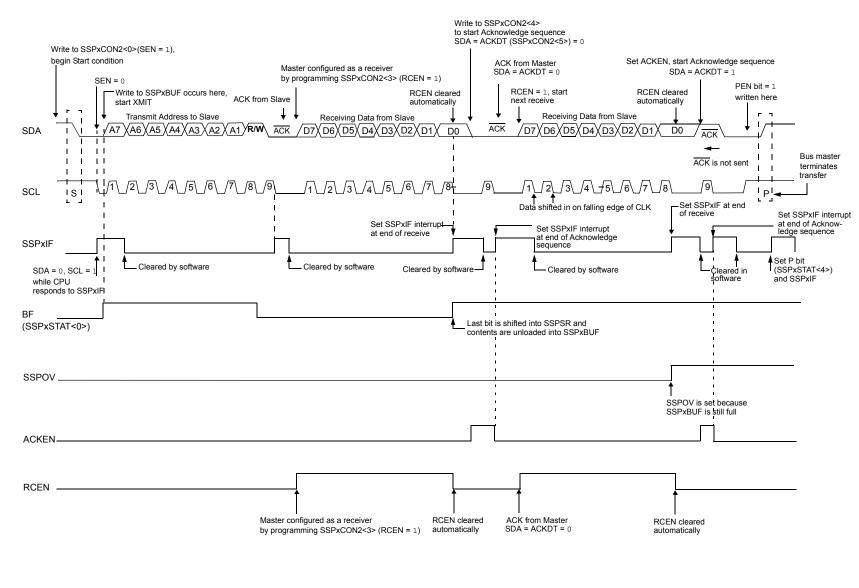

#### 26.10.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 26-30).

## 26.10.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

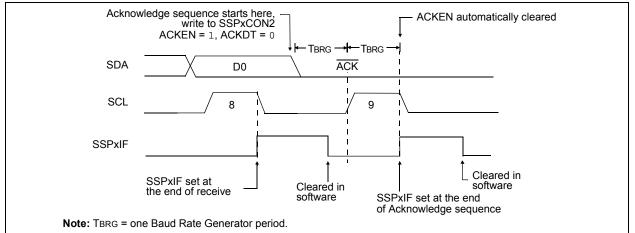

## 26.10.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 26-31).

## 26.10.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## FIGURE 26-30: ACKNOWLEDGE SEQUENCE WAVEFORM

## FIGURE 26-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

## 27.2.2.8 Asynchronous Reception Setup:

- Initialize the SPxBRGH:SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RXx pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCxIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCxIE interrupt enable bit was also set.

- 8. Read the RCxSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

ASYNCHRONOUS RECEPTION

## 27.2.2.9 9-Bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPxBRGH:SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RXx pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCxIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCxIE interrupt enable bit was also set.

- 9. Read the RCxSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RXx/DTx pin                                    | Start bit 0 / bit 1 / 5 / bit 7/8 / Stop bit / bit 0 / 5 / bit 7/8 / Stop bit / bit / bit 0 / 5 / bit 7/8 / Stop bit / 5 / bit 7/8 / Stop bit                 |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg →<br>Rcv Buffer Reg.<br>RCIDL | Word 1 Word 2 Word 2 KCXREG                                                                                                                                   |

| Read Rcv<br>Buffer Reg.<br>RCxREG              |                                                                                                                                                               |

| RCxIF<br>(Interrupt Flag)                      |                                                                                                                                                               |

| OERR bit<br>CREN                               |                                                                                                                                                               |

|                                                | timing diagram shows three words appearing on the RXx input. The RCxREG (receive buffer) is read after the third word, sing the OERR (overrun) bit to be set. |

**FIGURE 27-5:**

|                    |      | Bit Clear Conditions Value after Trigger completion   |                                                                                          | ger completion                                              | Threshold Operations                                                                                                                                                                   |                        |                        | Value at ADTIF interrupt |                          |       |

|--------------------|------|-------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|--------------------------|-------|

| Mode               | ADMD | ADACC and ADCNT                                       | ADACC                                                                                    | ADCNT                                                       | Retrigger                                                                                                                                                                              | Threshold<br>Test      | Interrupt              | ADAOV                    | ADFLTR                   | ADCNT |

| Basic              | 0    | ADACLR = 1                                            | Unchanged                                                                                | Unchanged                                                   | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | N/A                      | N/A                      | count |

| Accumulate         | 1    | ADACLR = 1                                            | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Average            | 2    | ADACLR = 1 or<br>ADCNT>=ADRPT at ADGO<br>or retrigger | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Burst<br>Average   | 3    | ADACLR = 1 or ADGO set or<br>retrigger                | Each repetition: same as<br>Average<br>End with sum of all<br>samples                    | Each repetition: same as<br>Average<br>End with ADCNT=ADRPT | Repeat while<br>ADCNT <adrpt< td=""><td>lf<br/>ADCNT&gt;=<br/>ADRPT</td><td>If thresh-<br/>old=true</td><td>ADACC Overflow</td><td>ADACC/2<sup>ADCRS</sup></td><td>ADRPT</td></adrpt<> | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | ADRPT |

| Low-pass<br>Filter | 4    | ADACLR = 1                                            | S+ADACC-ADACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ADACC-ADACC/<br>2 <sup>ADCRS</sup> | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | Filtered Value           | count |

Note: S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = ADREV and S2 = ADRES.

## REGISTER 31-4: ADCON3: ADC CONTROL REGISTER 3

| U-0     | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W/HC-0 | R/W-0/0 | R/W-0/0    | R/W-0/0 |

|---------|---------|-------------|---------|----------|---------|------------|---------|

| _       |         | ADCALC<2:0> |         | ADSOI    |         | ADTMD<2:0> |         |

| bit 7   |         |             |         |          |         |            | bit 0   |

|         |         |             |         |          |         |            |         |

| Legend. |         |             |         |          |         |            |         |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 ADCALC<2:0>: ADC Error Calculation Mode Select bits

|        | Action During                    | Action During 1st Precharge Stage                   |                                                              |  |  |  |

|--------|----------------------------------|-----------------------------------------------------|--------------------------------------------------------------|--|--|--|

| ADCALC | ADDSEN = 0<br>Single-Sample Mode | ADDSEN = 1 CVD<br>Double-Sample Mode <sup>(1)</sup> | Application                                                  |  |  |  |

| 111    | Reserved                         | Reserved                                            | Reserved                                                     |  |  |  |

| 110    | Reserved                         | Reserved                                            | Reserved                                                     |  |  |  |

| 101    | ADLFTR-ADSTPT                    | ADFLTR-ADSTPT                                       | Average/filtered value vs. setpoint                          |  |  |  |

| 100    | ADPREV-ADFLTR                    | ADPREV-ADFLTR                                       | First derivative of filtered value <sup>(3)</sup> (negative) |  |  |  |

| 011    | Reserved                         | Reserved                                            | Reserved                                                     |  |  |  |

| 010    | ADRES-ADFLTR                     | (ADRES-ADPREV)-ADFLTR                               | Actual result vs.<br>averaged/filtered value                 |  |  |  |

| 001    | ADRES-ADSTPT                     | (ADRES-ADPREV)-ADSTPT                               | Actual result vs.setpoint                                    |  |  |  |

| 000    | ADRES-ADPREV                     | ADRES-ADPREV                                        | First derivative of single measurement <sup>(2)</sup>        |  |  |  |

|        |                                  |                                                     | Actual CVD result in CVD mode <sup>(2)</sup>                 |  |  |  |

bit 3 ADSOI: ADC Stop-on-Interrupt bit

#### If ADCONT = 1:

- 1 = ADGO is cleared when the threshold conditions are met, otherwise the conversion is retriggered

- 0 = ADGO is not cleared by hardware, must be cleared by software to stop retriggers

#### bit 2-0 ADTMD<2:0>: Threshold Interrupt Mode Select bits

- 111 = Interrupt regardless of threshold test results

- 110 = Interrupt if ADERR>ADUTH

- 101 = Interrupt if ADERR≤ADUTH

- 100 = Interrupt if ADERR<ADLTH or ADERR>ADUTH

- 011 = Interrupt if ADERR>ADLTH and ADERR<ADUTH

- 010 = Interrupt if ADERR≥ADLTH

- 001 = Interrupt if ADERR<ADLTH

- 000 = Never interrupt

- Note 1: When ADPSIS = 0, the value of ADRES-ADPREV) is the value of (S2-S1) from Table 31-3.

- 2: When ADPSIS = 0

- 3: When ADPSIS = 1.

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

## TABLE B-1: DEVICE DIFFERENCES

| Features <sup>(1)</sup>              | PIC18(L)F26K40                                                          | PIC18(L)F45K40                                          | PIC18(L)F46K40                                          |

|--------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Program Memory (Bytes)               | 65536                                                                   | 32768                                                   | 65536                                                   |

| SRAM (Bytes)                         | 3720                                                                    | 2048                                                    | 3720                                                    |

| EEPROM (Bytes)                       | 1024                                                                    | 256                                                     | 1024                                                    |

| Interrupt Sources                    | 36                                                                      | 36                                                      | 36                                                      |

| I/O Ports                            | Ports A, B, C, (E)                                                      | Ports A, B, C, D, E                                     | Ports A, B, C, D, E                                     |

| Capture/Compare/PWM Modules<br>(CCP) | 2                                                                       | 2                                                       | 2                                                       |

| 10-bit Analog-to-Digital Module      | 4 internal<br>24 external                                               | 4 internal<br>35 external                               | 4 internal<br>35 external                               |

| Packages                             | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN | 40-pin PDIP<br>40-pin UQFN<br>44-pin TQFP<br>44-pin QFN | 40-pin PDIP<br>40-pin UQFN<br>44-pin TQFP<br>44-pin QFN |

Note 1: PIC18F2x/4xK40: operating voltage, 2.3V-5.5V. PIC18LF2x/4xK40: operating voltage, 1.8V-3.6V.