Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

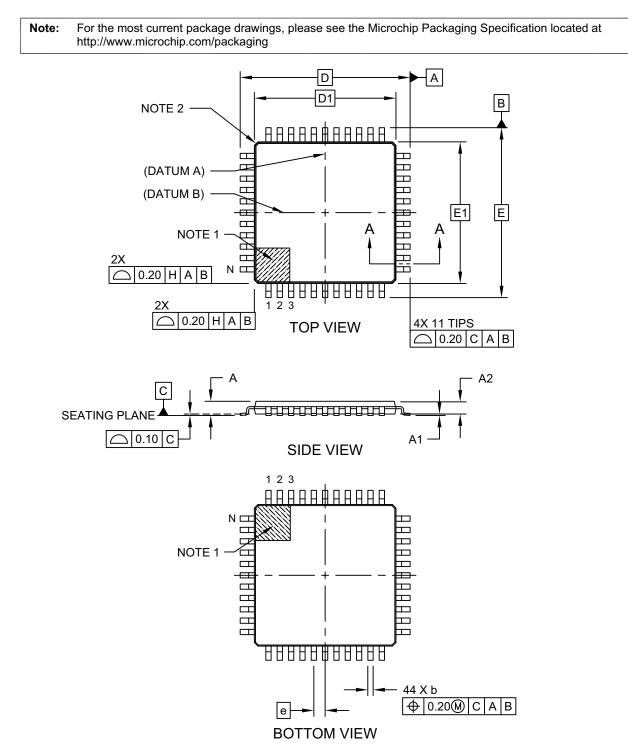

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k40-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2 Register Definitions: Configuration Words

| REGISTER 3-1: Configuration word 1L (30 0000n): Oscillators |                 |                  |                                    |                  |       |                   |       |  |  |

|-------------------------------------------------------------|-----------------|------------------|------------------------------------|------------------|-------|-------------------|-------|--|--|

| U-1                                                         | R/W-1           | R/W-1            | R/W-1                              | U-1              | R/W-1 | R/W-1             | R/W-1 |  |  |

| _                                                           | — RSTOSC<2:0> — |                  |                                    |                  |       | FEXTOSC<2:0>      |       |  |  |

| bit 7 bit 0                                                 |                 |                  |                                    |                  |       |                   |       |  |  |

|                                                             |                 |                  |                                    |                  |       |                   |       |  |  |

| Legend:                                                     |                 |                  |                                    |                  |       |                   |       |  |  |

| R = Readable bit W = Writable bit                           |                 |                  | U = Unimplemented bit, read as '1' |                  |       |                   |       |  |  |

| -n = Value for blank device                                 |                 | '1' = Bit is set |                                    | '0' = Bit is cle | eared | x = Bit is unknow | /n    |  |  |

|                                                             |                 |                  |                                    |                  |       |                   |       |  |  |

#### **REGISTER 3-1:** Configuration Word 1L (30 0000h): Oscillators

bit 7 Unimplemented: Read as '1'

#### RSTOSC<2:0>: Power-up Default Value for COSC bits bit 6-4 This value is the Reset default value for COSC and selects the oscillator first used by user software. Refer to COSC operation. 111 = EXTOSC operating per FEXTOSC bits (device manufacturing default) 110 = HFINTOSC with HFFRQ = 4 MHz (Register 4-5) and CDIV = 4:1 (Register 4-2) 101 = LFINTOSC 100 = SOSC 011 = Reserved 010 = EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits 001 = Reserved 000 = HFINTOSC with HFFRQ = 64 MHz (Register 4-5) and CDIV = 1:1 (Register 4-2). Resets COSC/NOSC to 3'b110. bit 3 Unimplemented: Read as '1' bit 2-0 FEXTOSC<2:0>: FEXTOSC External Oscillator Mode Selection bits 111 = EC (external clock) above 8 MHz; PFM set to high power (device manufacturing default) 110 = EC (external clock) for 500 kHz to 8 MHz; PFM set to medium power 101 = EC (external clock) below 500 kHz; PFM set to low power 100 = Oscillator not enabled 011 = Reserved (do not use) 010 = HS (crystal oscillator) above 8 MHz; PFM set to high power

- 001 = XT (crystal oscillator) above 500 kHz, below 8 MHz; PFM set to medium power

- 000 = LP (crystal oscillator) optimized for 32.768 kHz; PFM set to low power

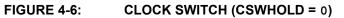

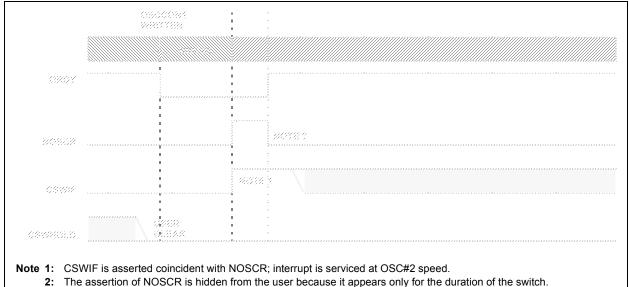

#### 4.4.2 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

## FIGURE 4-7: CLOCK SWITCH (CSWHOLD = 1)

## 4.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, ECL/M/H and Secondary Oscillator).

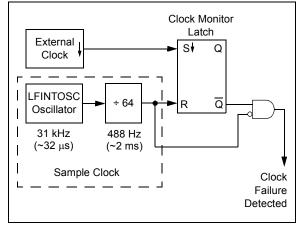

FIGURE 4-9: FSCM BLOCK DIAGRAM

### 4.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 4-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 4.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM overwrites the COSC bits to select HFINTOSC (3'b110). The frequency of HFINTOSC would be determined by the previous state of the HFFRQ bits and the NDIV/CDIV bits. The bit flag OSCFIF of the PIR1 register is set. Setting this flag will generate an interrupt if the OSCFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC and NDIV bits of the OSCCON1 register.

#### 4.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC and NDIV bits of the OSCCON1 register. When switching to the external oscillator or PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSCFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSCFIF flag will again become set by hardware.

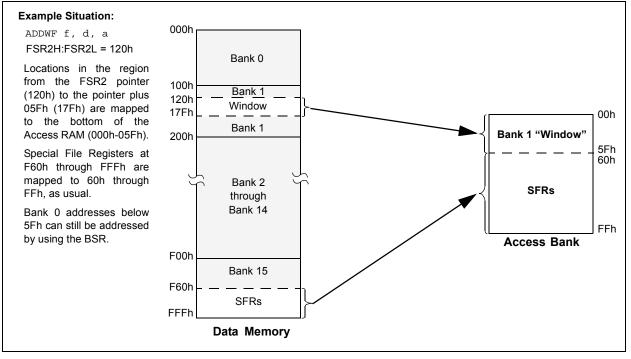

# 10.7.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom section of Bank 0, this mode maps the contents from a user defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 10.4.2 "Access Bank"**). An example of Access Bank remapping in this addressing mode is shown in Figure 10-8.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use direct addressing as before.

# 10.8 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 35.2 "Extended Instruction Set**".

#### FIGURE 10-8: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

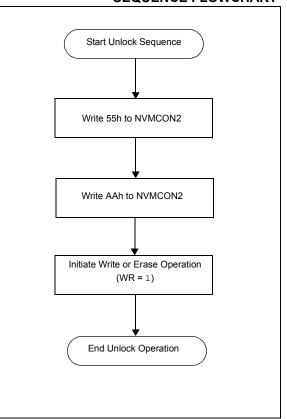

#### 11.1.4 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- Write of PFM write latches to PFM memory

- Write of PFM write latches to User IDs

- Write to Data EEPROM Memory

- Write to Configuration Words

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

| BCF     | INTCON, GIE                       | ; Recommended so sequence is not interrupted                     |

|---------|-----------------------------------|------------------------------------------------------------------|

| BANKSEL | NVMCON1                           |                                                                  |

| BSF     | NVMCON1,WREN                      | ; Enable write/erase                                             |

| MOVLW   | 55h                               | ; Load 55h                                                       |

|         |                                   |                                                                  |

| MOVWF   | NVMCON2                           | ; Step 1: Load 55h into NVMCON2                                  |

| MOVLW   | AAh                               | ; Step 2: Load W with AAh                                        |

| MOVWF   | NVMCON2                           | ; Step 3: Load AAh into NVMCON2                                  |

| BSF     | INTCON1,WR                        | ; Step 4: Set WR bit to begin write/erase                        |

|         |                                   |                                                                  |

| BSF     | INTCON, GIE                       | ; Re-enable interrupts                                           |

|         |                                   |                                                                  |

| Note 1: | Sequence begins when NVMCON       | V2 is written; steps 1-4 must occur in the cycle-accurate order  |

|         | <b>u</b>                          | to 4 is corrupted by an interrupt or a debugger Halt, the action |

|         | will not take place.              | · · · · · · · · · · · · · · · · · · ·                            |

| 2:      | Opcodes shown are illustrative; a | ny instruction that has the indicated effect may be used.        |

|         |                                   |                                                                  |

#### EXAMPLE 11-2: NVM UNLOCK SEQUENCE

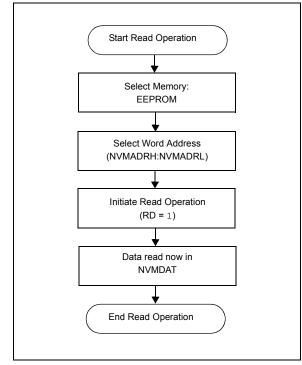

#### 11.3.3 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the NVMADRL and NVMADRH register pair, clear NVMREG<1:0> control bit in NVMCON1 register to access Data EEPROM locations and then set control bit, RD. The data is available on the very next instruction cycle; therefore, the NVMDAT register can be read by the next instruction. NVMDAT will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 11-5.

#### FIGURE 11-11: DATA EEPROM READ FLOWCHART

# 11.3.4 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the address must first be written to the NVMADRL and NVMADRH register pair and the data written to the NVMDAT register. The sequence in Example 11-6 must be followed to initiate the write cycle.

The write will not begin if NVM Unlock sequence, described in **Section 11.1.4 "NVM Unlock Sequence"**, is not exactly followed for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in NVMCON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, NVMCON1, NVMADRL, NVMADRH and NVMDAT cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. A single Data EEPROM word is written and the operation includes an implicit erase cycle for that word (it is not necessary to set FREE). CPU execution continues in parallel and at the completion of the write cycle, the WR bit is cleared in hardware and the NVM Interrupt Flag bit (NVMIF) is set. The user can either enable this interrupt or poll this bit. NVMIF must be cleared by software.

| U-0             | U-0                         | R/W-0/0               | R/W-0/0                   | U-0              | R/W-0/0               | R/W-0/0               | R/W-0/0               |

|-----------------|-----------------------------|-----------------------|---------------------------|------------------|-----------------------|-----------------------|-----------------------|

| _               | _                           | TMR0IE <sup>(1)</sup> | IOCIE <sup>(1)</sup>      | _                | INT2IE <sup>(1)</sup> | INT1IE <sup>(1)</sup> | INT0IE <sup>(1)</sup> |

| bit 7           | •                           |                       |                           |                  |                       |                       | bit 0                 |

|                 |                             |                       |                           |                  |                       |                       |                       |

| Legend: IE      |                             |                       |                           |                  |                       |                       |                       |

| R = Readable    | bit                         | W = Writable          | bit                       | U = Unimpler     | mented bit, read      | l as '0'              |                       |

| -n = Value at F | POR                         | '1' = Bit is set      |                           | '0' = Bit is cle | ared                  | x = Bit is unkr       | nown                  |

|                 |                             |                       |                           |                  |                       |                       |                       |

| bit 7-6         | Unimplemen                  | ted: Read as '        | )'                        |                  |                       |                       |                       |

| bit 5           | TMR0IE: Time                | er0 Interrupt Er      | nable bit <sup>(1)</sup>  |                  |                       |                       |                       |

|                 | 1 = Enabled                 |                       |                           |                  |                       |                       |                       |

|                 | 0 = Disabled                |                       | (4)                       |                  |                       |                       |                       |

| bit 4           |                             | pt-on-Change          | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |

| bit 3           |                             | ted: Read as '        | ı'                        |                  |                       |                       |                       |

|                 | -                           |                       |                           |                  |                       |                       |                       |

| bit 2           |                             | nal Interrupt 2       | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |

| h:+ 1           |                             | nol Interrupt 1       | Enable hit(1)             |                  |                       |                       |                       |

| bit 1           | 1 = Enabled                 | nal Interrupt 1       | Enable bitter             |                  |                       |                       |                       |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |

| bit 0           |                             | nal Interrupt 0       | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |

|                 | 1 = Enabled                 |                       |                           |                  |                       |                       |                       |

|                 | 0 = Disabled                |                       |                           |                  |                       |                       |                       |

| Note 1: PI      | R0 interrupts ar            | e not disabled        | by the PEIE I             | bit in the INTC  | ON register are       | not disabled b        | v the PEIE bit        |

## REGISTER 14-10: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

**Note 1:** PIR0 interrupts are not disabled by the PEIE bit in the INTCON register. are not disabled by the PEIE bit in the INTCON register.

| FIGURE 19-7:           | TIMER1/3/5 GATE SING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GLE-PULSE AND TOGGLE COMBINED MODE                  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| TMRxGE                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGPOL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGSPM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGTM                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGG <u>O/</u><br>DONE | <ul> <li>Set by software</li> <li>Counting enabled of the set of the</li></ul> | Cleared by hardware on falling edge of TxGVAL       |

| TxG_IN                 | rising edge of TxC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| ТхСКІ                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TxGVAL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

| TIMER1/3/5             | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>N + 1</u> <u>N + 2</u> <u>N + 3</u> <u>N + 4</u> |

| TMRxGIF                | <ul> <li>Cleared by software</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Set by hardware on<br>falling edge of TxGVAL —      |

## 19.13 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD1 register. See Section **7.0 "Peripheral Module Disable (PMD)"** for more information.

#### 20.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

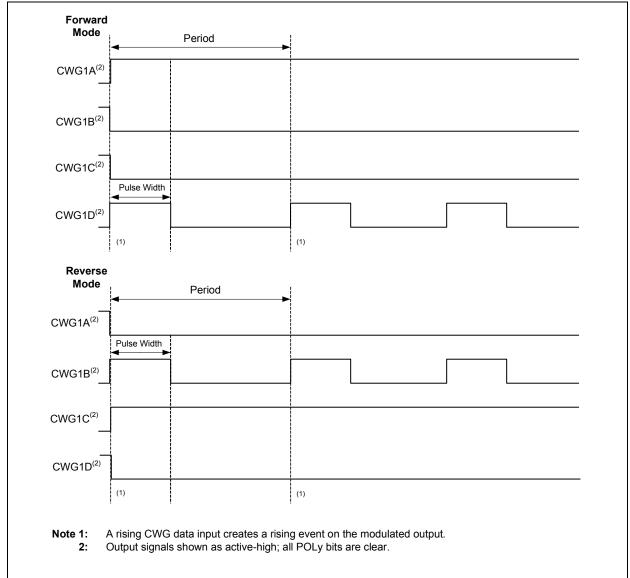

In Forward Full-Bridge mode (MODE<2:0> = 010), CWG1A is driven to its active state, CWG1B and CWG1C are driven to their inactive state, and CWG1D is modulated by the input signal, as shown in Figure 24-7.

In Reverse Full-Bridge mode (MODE<2:0> = 011), CWG1C is driven to its active state, CWG1A and CWG1D are driven to their inactive states, and CWG1B is modulated by the input signal, as shown in Figure 24-7. In Full-Bridge mode, the dead-band period is used when there is a switch from forward to reverse or viceversa. This dead-band control is described in Section 24.6 "Dead-Band Control", with additional details in Section 24.7 "Rising Edge and Reverse Dead Band" and Section 24.8 "Falling Edge and Forward Dead Band". Steering modes are not used with either of the Full-Bridge modes. The mode selection may be toggled between forward and reverse toggling the MODE<0> bit of the CWG1CON0 while keeping MODE<2:1> static, without disabling the CWG module.

FIGURE 24-7: EXAMPLE OF FULL-BRIDGE OUTPUT

| Name       | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1     | Bit 0  | Register<br>on Page |

|------------|----------|---------|---------|---------|-------|-------|-----------|--------|---------------------|

| CWG1CON0   | EN       | LD      | —       | —       | _     |       | MODE<2:0> | •      | 315                 |

| CWG1CON1   | _        | —       | IN      | _       | POLD  | POLC  | POLB      | POLA   | 316                 |

| CWG1CLKCON | _        | —       | _       | _       | _     | —     | —         | CS     | 317                 |

| CWG1ISM    | —        | —       | _       | —       |       |       | ISM<2:0>  |        | 317                 |

| CWG1STR    | OVRD     | OVRC    | OVRB    | OVRA    | STRD  | STRC  | STRB      | STRA   | 318                 |

| CWG1AS0    | SHUTDOWN | REN     | LSBD    | <1:0>   | LSAC  | <1:0> | —         | —      | 319                 |

| CWG1AS1    | _        | —       | AS5E    | AS4E    | AS3E  | AS2E  | AS1E      | AS0E   | 320                 |

| CWG1DBR    | _        | _       |         |         | DBR<  | <5:0> |           |        | 321                 |

| CWG1DBF    | _        | —       |         |         | DBF<  | :5:0> |           |        | 321                 |

| PIE7       | SCANIE   | CRCIE   | NVMIE   | _       | _     | _     | _         | CWG1IE | 186                 |

| PIR7       | SCANIF   | CRCIF   | NVMIF   | _       | _     | _     | —         | CWG1IF | 178                 |

| IPR7       | SCANIP   | CRCIP   | NVMIP   | _       | _     | —     | —         | CWG1IP | 194                 |

| PMD4       | UART2MD  | UART1MD | MSSP2MD | MSSP1MD | _     | —     | —         | CWG1MD | 72                  |

#### TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

Legend: -= unimplemented locations read as '0'. Shaded cells are not used by CWG.

| FIGURE 27-12:                                       | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                    |

|-----------------------------------------------------|------------------------------------------------------------------------------|

| RXx/DTx<br>pin<br>TXx/CKx pin<br>(SCKP = 0)         |                                                                              |

| TXx/CKx pin<br>(SCKP = 1)<br>Write to<br>bit SREN   |                                                                              |

| SREN bit                                            | ·0'                                                                          |

| RCxIF bit<br>(Interrupt) ———<br>Read<br>RCxREG ———— |                                                                              |

| Note: Timing dia                                    | agram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

# TABLE 27-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name     | Bit 7                                  | Bit 6     | Bit 5   | Bit 4       | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------------------------------------|-----------|---------|-------------|---------------|-------------|---------|---------|---------------------|

| ANSELB   | ANSELB7                                | ANSELB6   | ANSELB5 | ANSELB4     | ANSELB3       | ANSELB2     | ANSELB1 | ANSELB0 | 204                 |

| ANSELC   | ANSELC7                                | ANSELC6   | ANSELC5 | ANSELC4     | ANSELC3       | ANSELC2     | ANSELC1 | ANSELC0 | 204                 |

| BAUDxCON | ABDOVF                                 | RCIDL     |         | SCKP        | BRG16         | _           | WUE     | ABDEN   | 395                 |

| INTCON   | GIE/GIEH                               | PEIE/GIEL | IPEN    | -           | -             | INT2EDG     | INT1EDG | INT0EDG | 170                 |

| PIE3     | RC2IE                                  | TX2IE     | RC1IE   | TX1IE       | BCL2IE        | SSP2IE      | BCL1IE  | SSP1IE  | 182                 |

| PIR3     | RC2IF                                  | TX2IF     | RC1IF   | TX1IF       | BCL2IF        | SSP2IF      | BCL1IF  | SSP1IF  | 174                 |

| IPR3     | RC2IP                                  | TX2IP     | RC1IP   | TX1IP       | BCL2IP        | SSP2IP      | BCL1IP  | SSP1IP  | 190                 |

| RCxREG   |                                        |           | EUS     | ARTx Receiv | e Data Regis  | ter         |         |         | 399*                |

| RCxSTA   | SPEN                                   | RX9       | SREN    | CREN        | ADDEN         | FERR        | OERR    | RX9D    | 394                 |

| RxyPPS   | _                                      | _         | _       |             | F             | RxyPPS<4:0> |         |         | 218                 |

| RXxPPS   | _                                      | _         | _       |             |               | RXPPS<4:0>  |         |         | 216                 |

| SPxBRGH  | EUSARTx Baud Rate Generator, High Byte |           |         |             |               |             |         |         | 404*                |

| SPxBRGL  |                                        |           | EUSART  | x Baud Rate | Generator, Lo | ow Byte     |         |         | 404*                |

| TXxSTA   | CSRC                                   | TX9       | TXEN    | SYNC        | SENDB         | BRGH        | TRMT    | TX9D    | 393                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

#### 31.1.3 ADC VOLTAGE REFERENCE

The ADPREF<1:0> bits of the ADREF register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- Vdd

- FVR 1.024V

- FVR 2.048V

- FVR 4.096V

The ADNREF bit of the ADREF register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See Section 28.0 "Fixed Voltage Reference (FVR)" for more details on the Fixed Voltage Reference.

#### 31.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCLK register and the ADCS bits of the ADCON0 register. There are 66 possible clock options:

- Fosc/2

- Fosc/4

- Fosc/6

- Fosc/8

- Fosc/10

- •

- •

- •

- Fosc/128

- FRC (dedicated RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 31-2.

For correct conversion, the appropriate TAD specification must be met. Refer to Table 37-14 for more information. Table 31-1 gives examples of appropriate ADC clock selections.

| Note 1: | Unless using the FRC, any changes in the<br>system clock frequency will change the<br>ADC clock frequency, which may<br>adversely affect the ADC result.                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | The internal control logic of the ADC runs<br>off of the clock selected by the ADCS bit<br>of ADCON0. What this can mean is when<br>the ADCS bit of ADCON0 is set to '1'<br>(ADC runs on FRC), there may be<br>unexpected delays in operation when<br>setting ADC control bits. |

# PIC18(L)F26/45/46K40

| DAW                     |           | Decimal Adjust W Register |                                                                                                                                                                           |              |                 |       | er         |

|-------------------------|-----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|-------|------------|

| Syntax:                 |           | DA                        | ٩W                                                                                                                                                                        |              |                 |       |            |

| Operands:               |           | No                        | one                                                                                                                                                                       |              |                 |       |            |

| Operation:              |           | (V<br>els                 | If [W<3:0> > 9] or [DC = 1] then<br>(W<3:0>) + 6 $\rightarrow$ W<3:0>;<br>else<br>(W<3:0>) $\rightarrow$ W<3:0>;                                                          |              |                 |       |            |

|                         |           | (V<br>els                 | [W<7:4> ·<br>V<7:4>) +<br>se<br>√<7:4>) +                                                                                                                                 | 6 + DC       | $\rightarrow W$ | <7:4> |            |

| Status Affect           | ted:      | С                         |                                                                                                                                                                           |              |                 |       |            |

| Encoding:               |           |                           | 0000                                                                                                                                                                      | 0000         | 000             | 00    | 0111       |

| Description:            |           |                           | DAW adjusts the 8-bit value in W, result-<br>ing from the earlier addition of two vari-<br>ables (each in packed BCD format) and<br>produces a correct packed BCD result. |              |                 |       |            |

| Words:                  |           | 1                         |                                                                                                                                                                           |              |                 |       |            |

| Cycles:                 |           | 1                         |                                                                                                                                                                           |              |                 |       |            |

| Q Cycle Ac              | tivity:   |                           |                                                                                                                                                                           |              |                 |       |            |

| C                       | Q1        |                           | Q2                                                                                                                                                                        | Q3           |                 | Q4    |            |

| Dec                     | code      |                           | Read<br>gister W                                                                                                                                                          | Proce<br>Dat |                 |       | Write<br>W |

| Example1:               |           |                           |                                                                                                                                                                           |              |                 |       |            |

|                         |           | DÆ                        | AM                                                                                                                                                                        |              |                 |       |            |

| Before                  | Instruc   | tion                      |                                                                                                                                                                           |              |                 |       |            |

| W<br>C<br>D             |           | =<br>=<br>=               | A5h<br>0<br>0                                                                                                                                                             |              |                 |       |            |

|                         | nstructio | n                         |                                                                                                                                                                           |              |                 |       |            |

| C =                     |           | =<br>=<br>=               | 05h<br>1<br>0                                                                                                                                                             |              |                 |       |            |

|                         | Instruc   | tion                      |                                                                                                                                                                           |              |                 |       |            |

| W<br>C<br>D<br>After Ir |           | =<br>=<br>=<br>on         | CEh<br>0<br>0                                                                                                                                                             |              |                 |       |            |

| W<br>C<br>D             |           | =<br>=<br>=               | 34h<br>1<br>0                                                                                                                                                             |              |                 |       |            |

| DECF                                                                                            | Decrement f                                                                                                                                                                         |                                                                                             |                      |  |  |  |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Syntax:                                                                                         | DECF f{,c                                                                                                                                                                           | l {,a}}                                                                                     |                      |  |  |  |  |

| Operands:                                                                                       | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                  | d ∈ [0,1]                                                                                   |                      |  |  |  |  |

| Operation:                                                                                      | $(f) - 1 \rightarrow de$                                                                                                                                                            | est                                                                                         |                      |  |  |  |  |

| Status Affected:                                                                                | C, DC, N, C                                                                                                                                                                         | DV, Z                                                                                       |                      |  |  |  |  |

| Encoding:                                                                                       | 0000                                                                                                                                                                                | 01da ff:                                                                                    | ff ffff              |  |  |  |  |

| Description:                                                                                    | result is sto<br>result is sto<br>(default).<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank.<br>If 'a' is '0' al<br>set is enabl<br>in Indexed I<br>mode when<br>tion 35.2.3 | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the |                      |  |  |  |  |

| Words:                                                                                          | 1                                                                                                                                                                                   |                                                                                             |                      |  |  |  |  |

| Cycles:                                                                                         | 1                                                                                                                                                                                   |                                                                                             |                      |  |  |  |  |

| Q Cycle Activity:                                                                               |                                                                                                                                                                                     |                                                                                             |                      |  |  |  |  |

| Q1                                                                                              | Q2                                                                                                                                                                                  | Q3                                                                                          | Q4                   |  |  |  |  |

| Decode                                                                                          | Read<br>register 'f'                                                                                                                                                                | Process<br>Data                                                                             | Write to destination |  |  |  |  |

| Example:DECFCNT,1,0Before Instruction $CNT = 01h$ $Z = 0$ After Instruction $CNT = 00h$ $Z = 1$ |                                                                                                                                                                                     |                                                                                             |                      |  |  |  |  |

# PIC18(L)F26/45/46K40

| RET                                               | RETURN Return from Subroutine |                                                                                                                                                                                                                                                                                                    |                 |                 |     |  |  |  |  |

|---------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----|--|--|--|--|

| Synta                                             | ax:                           | RETURN                                                                                                                                                                                                                                                                                             | RETURN {s}      |                 |     |  |  |  |  |

| Oper                                              | ands:                         | $s \in [0,1]$                                                                                                                                                                                                                                                                                      |                 |                 | Ор  |  |  |  |  |

| Oper                                              | ation:                        | $(TOS) \rightarrow PO$<br>if s = 1<br>$(WS) \rightarrow W$ ,                                                                                                                                                                                                                                       | С,              |                 | Ор  |  |  |  |  |

|                                                   |                               | (STATUSS)<br>$(BSRS) \rightarrow I$                                                                                                                                                                                                                                                                |                 | changed         |     |  |  |  |  |

| Statu                                             | s Affected:                   | None                                                                                                                                                                                                                                                                                               |                 | lenanged        | Sta |  |  |  |  |

| Enco                                              |                               | 0000                                                                                                                                                                                                                                                                                               | 0000 000        | )1 001s         | En  |  |  |  |  |

|                                                   | ription:                      |                                                                                                                                                                                                                                                                                                    | subroutine. T   |                 | De  |  |  |  |  |

|                                                   |                               | popped and the top of the stack (TOS)<br>is loaded into the program counter. If<br>'s'= 1, the contents of the shadow<br>registers, WS, STATUSS and BSRS,<br>are loaded into their corresponding<br>registers, W, Status and BSR. If<br>'s' = 0, no update of these registers<br>occurs (default). |                 |                 |     |  |  |  |  |

| Word                                              | ls:                           | 1                                                                                                                                                                                                                                                                                                  |                 |                 |     |  |  |  |  |

| Cycle                                             | es:                           | 2                                                                                                                                                                                                                                                                                                  |                 |                 |     |  |  |  |  |

| QC                                                | ycle Activity:                |                                                                                                                                                                                                                                                                                                    |                 |                 |     |  |  |  |  |

|                                                   | Q1                            | Q2                                                                                                                                                                                                                                                                                                 | Q3              | Q4              | _   |  |  |  |  |

|                                                   | Decode                        | No                                                                                                                                                                                                                                                                                                 | Process         | POP PC          |     |  |  |  |  |

|                                                   |                               | operation                                                                                                                                                                                                                                                                                          | Data            | from stack      |     |  |  |  |  |

|                                                   | No<br>operation               | No<br>operation                                                                                                                                                                                                                                                                                    | No<br>operation | No<br>operation | Wo  |  |  |  |  |

|                                                   | operation                     | operation                                                                                                                                                                                                                                                                                          | operation       | operation       | Cy  |  |  |  |  |

|                                                   |                               |                                                                                                                                                                                                                                                                                                    |                 |                 | Q   |  |  |  |  |

| Exan                                              | nple:                         | RETURN                                                                                                                                                                                                                                                                                             |                 |                 | Q   |  |  |  |  |

| Example: RETURN<br>After Instruction:<br>PC = TOS |                               |                                                                                                                                                                                                                                                                                                    |                 |                 |     |  |  |  |  |

| RLCF                                                                         | Rotate Left f through Carry                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |  |  |  |  |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|