Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k40-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection, Device ID and Rev ID.

### 3.1 Configuration Words

There are six Configuration Word bits that allow the user to setup the device with several choices of oscillators, Resets and memory protection options. These are implemented as Configuration Word 1 through Configuration Word 6 at 300000h through 30000Bh.

| Note: | The DEBUG bit in Configuration Words is     |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

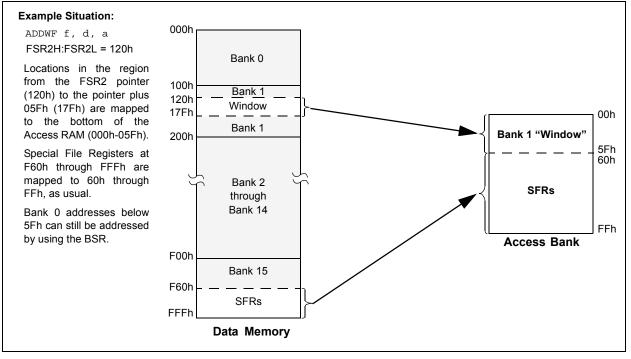

### 10.7.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom section of Bank 0, this mode maps the contents from a user defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 10.4.2 "Access Bank"**). An example of Access Bank remapping in this addressing mode is shown in Figure 10-8.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use direct addressing as before.

## 10.8 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 35.2 "Extended Instruction Set**".

### FIGURE 10-8: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

## PIC18LF26/45/46K40

### 13.6 CRC Check Value

The CRC check value will be located in the CRCACC registers after the CRC calculation has finished. The check value will depend on two mode settings of the CRCCON register: ACCM and SHIFTM.

When the ACCM bit is set, the CRC module augments the data with a number of zeros equal to the length of the polynomial to align the final check value. When the ACCM bit is not set, the CRC will stop at the end of the data. A number of zeros equal to the length of the polynomial can then be entered into CRCDAT to find the same check value as augmented mode. Alternatively, the expected check value can be entered at this point to make the final result equal 0.

When the CRC check value is computed with the SHIFTM bit set, selecting LSb first, and the ACCM bit is set then the final value in the CRCACC registers will be reversed such that the LSb will be in the MSb position and vice versa. This is the expected check value in bit reversed form. If you are creating a check value to be appended to a data stream then a bit reversal must be performed on the final value to achieve the correct checksum. You can use the CRC to do this reversal by the following method:

- Save CRCACC value in user RAM space

- Clear the CRCACC registers

- Clear the CRCXOR registers

- Write the saved CRCACC value to the CRCDAT input

The properly oriented check value will be in the CRCACC registers as the result.

### 13.7 CRC Interrupt

The CRC will generate an interrupt when the BUSY bit transitions from 1 to 0. The CRCIF Interrupt Flag bit of the PIR7 register is set every time the BUSY bit transitions, regardless of whether or not the CRC interrupt is enabled. The CRCIF bit can only be cleared in software. The CRC interrupt enable is the CRCIE bit of the PIE7 register.

### 13.8 Configuring the CRC

The following steps illustrate how to properly configure the CRC.

- Determine if the automatic program memory scan will be used with the scanner or manual calculation through the SFR interface and perform the actions specified in Section 13.5 "CRC Data Sources", depending on which decision was made.

- 2. If desired, seed a starting CRC value into the CRCACCH/L registers.

- 3. Program the CRCXORH/L registers with the desired generator polynomial.

- Program the DLEN<3:0> bits of the CRCCON1 register with the length of the data word - 1 (refer to Example 13-1). This determines how many times the shifter will shift into the accumulator for each data word.

- 5. Program the PLEN<3:0> bits of the CRCCON1 register with the length of the polynomial -2 (refer to Example 13-1).

- Determine whether shifting in trailing zeros is desired and set the ACCM bit of the CRCCON0 register appropriately.

- 7. Likewise, determine whether the MSb or LSb should be shifted first and write the SHIFTM bit of the CRCCON0 register appropriately.

- 8. Write the CRCGO bit of the CRCCON0 register to begin the shifting process.

- 9a. If manual SFR entry is used, monitor the FULL bit of the CRCCON0 register. When FULL = 0, another word of data can be written to the CRCDATH/L registers, keeping in mind that CRCDATH should be written first if the data has more than eight bits, as the shifter will begin upon the CRCDATL register being written.

- 9b. If the scanner is used, the scanner will automatically stuff words into the CRCDATH/L registers as needed, as long as the SCANGO bit is set.

- 10a. If using the Flash memory scanner, monitor the SCANIF (or the SCANGO bit) for the scanner to finish pushing information into the CRCDATA registers. After the scanner is completed, monitor the BUSY bit to determine that the CRC has been completed and the check value can be read from the CRCACC registers. If both the interrupt flags are set (or both BUSY and SCANGO bits are cleared), the completed CRC calculation can be read from the CRCACCH/L registers.

- 10b. If manual entry is used, monitor the BUSY bit to determine when the CRCACC registers will hold the check value.

### 14.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable and priority bits.

### 14.5 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Request Flag registers (PIR0, PIR1, PIR2, PIR3, PIR4, PIR5, PIR6 and PIR7).

### 14.6 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Enable registers (PIE0, PIE1, PIE2, PIE3, PIE4, PIE5, PIE6 and PIE7). When IPEN = 0, the PEIE/GIEL bit must be set to enable any of these peripheral interrupts.

### 14.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Priority registers (IPR0, IPR1, IPR2, IPR3, IPR4 and IPR5, IPR6 and IPR7). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

| U-0          | U-0                                                                                   | R/W-1/1                                                                          | R/W-1/1      | U-0              | R/W-1/1          | R/W-1/1         | R/W-1/1 |

|--------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------|------------------|------------------|-----------------|---------|

| —            | —                                                                                     | TMR0IP                                                                           | IOCIP        | —                | INT2IP           | INT1IP          | INT0IP  |

| bit 7        |                                                                                       |                                                                                  |              |                  |                  |                 | bit C   |

| Legend:      |                                                                                       |                                                                                  |              |                  |                  |                 |         |

| R = Readat   | ole hit                                                                               | W = Writable                                                                     | bit          | U = Unimpler     | mented bit, read | 1 as '0'        |         |

| -n = Value a |                                                                                       | '1' = Bit is set                                                                 |              | '0' = Bit is cle |                  | x = Bit is unkr | nown    |

|              |                                                                                       |                                                                                  |              |                  |                  |                 |         |

| bit 7-6      | Unimplemen                                                                            | ted: Read as '                                                                   | 0'           |                  |                  |                 |         |

| bit 5        | <b>TMR0IP:</b> Timer0 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |                                                                                  |              |                  |                  |                 |         |

| bit 4        | 1 = High prio                                                                         | IOCIP: Interrupt-on-Change Priority bit<br>1 = High priority<br>0 = Low priority |              |                  |                  |                 |         |

| bit 3        | Unimplemen                                                                            | ted: Read as '                                                                   | 0'           |                  |                  |                 |         |

| bit 2        | INT2IP: External Interrupt 2 Priority bit<br>1 = High priority<br>0 = Low priority    |                                                                                  |              |                  |                  |                 |         |

| bit 1        | INT1IP: External Interrupt 1 Priority bit<br>1 = High priority<br>0 = Low priority    |                                                                                  |              |                  |                  |                 |         |

| bit 0        | INTOIP: Exter<br>1 = High prio<br>0 = Low prior                                       |                                                                                  | Priority bit |                  |                  |                 |         |

### REGISTER 14-18: IPR0: PERIPHERAL INTERRUPT PRIORITY REGISTER 0

### REGISTER 20-3: TxCLKCON: TIMERx CLOCK SELECTION REGISTER

| CS<3:0><br>bit 7 | /-0/0 | R/W-0/0 R/W-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------------|-------|---------------|---------|---------|-----|-----|-----|-------|

| bit 7            |       | :0>           | CS      |         | —   | —   | —   | —     |

|                  | bit 0 |               |         |         |     |     |     | bit 7 |

|                  |       |               |         |         |     |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 CS<3:0>: Timerx Clock Selection bits

| CS<3:0>   | TMR2                    | TMR4                    | TMR6                    |

|-----------|-------------------------|-------------------------|-------------------------|

| 03\3.0>   | Clock Source            | Clock Source            | Clock Source            |

| 1111-1001 | Reserved                | Reserved                | Reserved                |

| 1000      | ZCD_OUT                 | ZCD_OUT                 | ZCD_OUT                 |

| 0111      | CLKREF_OUT              | CLKREF_OUT              | CLKREF_OUT              |

| 0110      | SOSC                    | SOSC                    | SOSC                    |

| 0101      | MFINTOSC (31 kHz)       | MFINTOSC (31 kHz)       | MFINTOSC (31 kHz)       |

| 0100      | LFINTOSC                | LFINTOSC                | LFINTOSC                |

| 0011      | HFINTOSC                | HFINTOSC                | HFINTOSC                |

| 0010      | Fosc                    | Fosc                    | Fosc                    |

| 0001      | Fosc/4                  | Fosc/4                  | Fosc/4                  |

| 0000      | Pin selected by T2INPPS | Pin selected by T4INPPS | Pin selected by T6INPPS |

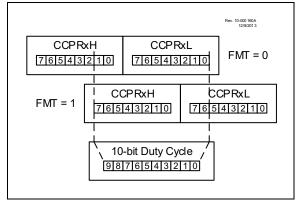

### 21.5.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the FMT bit of the CCPxCON register (see Figure 21-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between PR2 and TMR2.

Equation 21-2 is used to calculate the PWM pulse width.

Equation 21-3 is used to calculate the PWM duty cycle ratio.

FIGURE 21-5: PWM 10-BIT ALIGNMENT

### EQUATION 21-2: PULSE WIDTH

| Pulse Width = (CCPRx) | H:CCPRxL register pair) • |

|-----------------------|---------------------------|

| Tosc                  | • (TMR2 Prescale Value)   |

### EQUATION 21-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 21-4).

### 21.5.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 21-4.

### EQUATION 21-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

## PIC18LF26/45/46K40

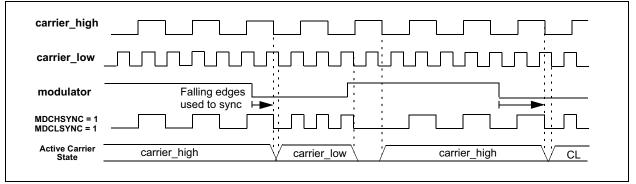

| FIGURE 25-5:                 | Carrier Low Synchronization (MDSHSYNC = 0, MDCLSYNC = 1) |

|------------------------------|----------------------------------------------------------|

| carrier_high                 |                                                          |

| carrier_low                  |                                                          |

| modulator                    |                                                          |

| MDCHSYNC = 0<br>MDCLSYNC = 1 |                                                          |

| Active Carrier<br>State      | carrier_high                                             |

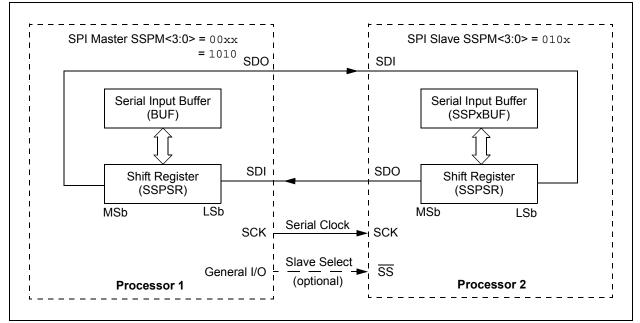

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

### FIGURE 26-3: SPI MASTER/SLAVE CONNECTION

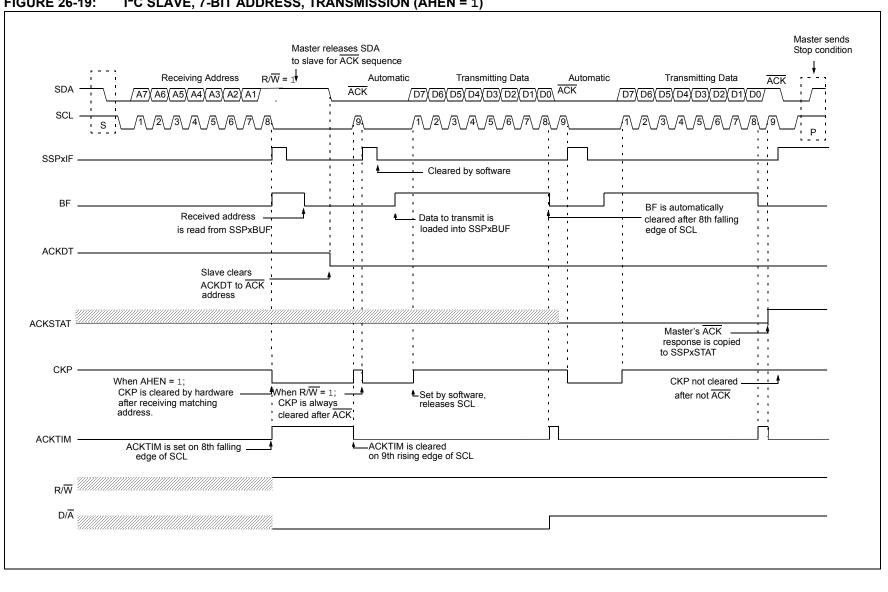

# **FIGURE 26-19:**

PIC18(L)F26/45/46K40

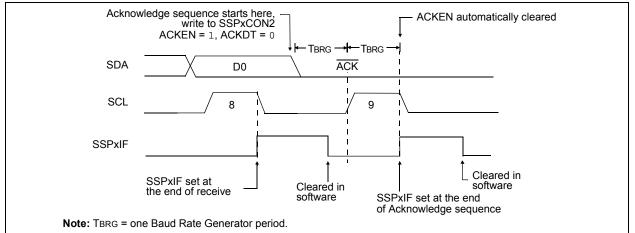

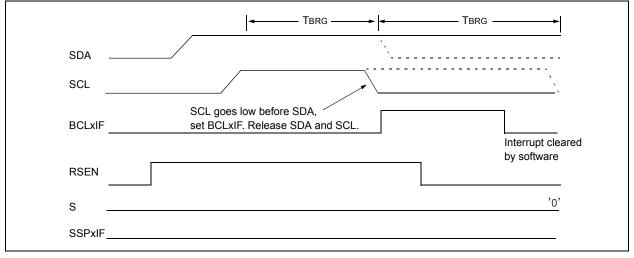

#### 26.10.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 26-30).

### 26.10.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

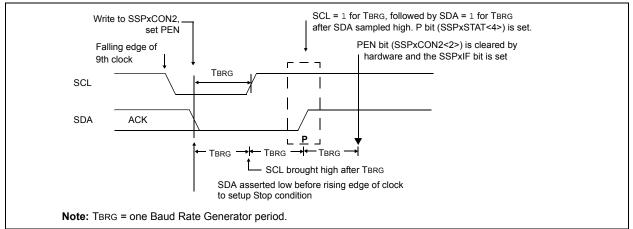

### 26.10.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 26-31).

### 26.10.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 26-30: ACKNOWLEDGE SEQUENCE WAVEFORM

### FIGURE 26-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

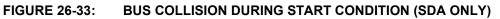

### 26.10.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 26-33).

- b) SCL is sampled low before SDA is asserted low (Figure 26-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- the BCLxIF flag is set and

- the MSSP module is reset to its Idle state (Figure 26-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 26-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

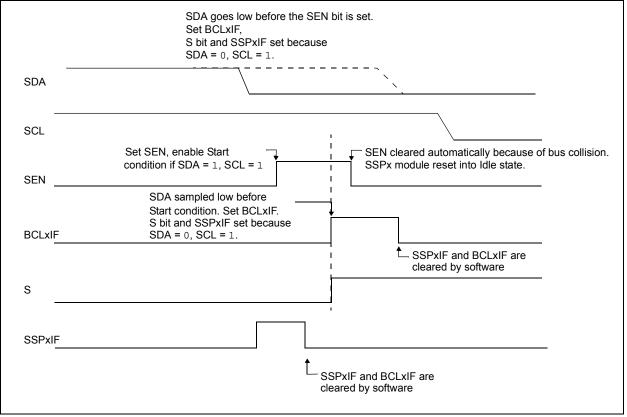

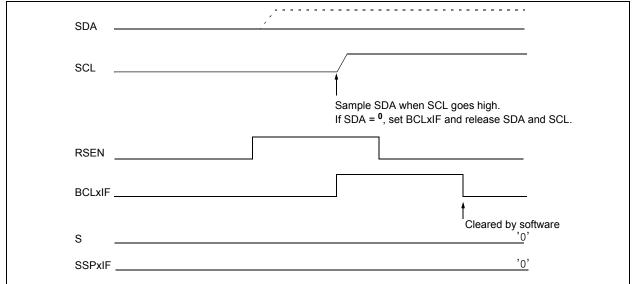

### 26.10.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 26-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 26-37.

If, at the end of the BRG time out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 26-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### 35.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                                                              | ADD liter             | al to W         |      |          |  |

|----------------------------------------------------------------------------------------------------|-----------------------|-----------------|------|----------|--|

| Syntax:                                                                                            | ADDLW                 | k               |      |          |  |

| Operands:                                                                                          | $0 \le k \le 255$     |                 |      |          |  |

| Operation:                                                                                         | (W) + k $\rightarrow$ | W               |      |          |  |

| Status Affected:                                                                                   | N, OV, C, E           | DC, Z           |      |          |  |

| Encoding:                                                                                          | 0000                  | 1111            | kkkk | kkkk     |  |

| Description: The contents of W are added to the<br>8-bit literal 'k' and the result is place<br>W. |                       |                 |      |          |  |

| Words:                                                                                             | 1                     |                 |      |          |  |

| Cycles:                                                                                            | 1                     | 1               |      |          |  |

| Q Cycle Activity                                                                                   | :                     |                 |      |          |  |

| Q1                                                                                                 | Q2                    | Q3              |      | Q4       |  |

| Decode                                                                                             | Read<br>literal 'k'   | Process<br>Data | s Wr | ite to W |  |

| Example:<br>Before Instru<br>W =<br>After Instruc<br>W =                                           | uction<br>= 10h       | .5h             |      |          |  |

| ADDWF            | ADD W to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | ADDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operation:       | (W) + (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Status Affected: | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Encoding:        | 0010 01da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Description:     | Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| QC          | ycle Activity:               |                      |              |                 |      |                      |

|-------------|------------------------------|----------------------|--------------|-----------------|------|----------------------|

|             | Q1                           |                      | Q2           | G               | 23   | Q4                   |

|             | Decode                       | Read<br>register 'f' |              | Process<br>Data |      | Write to destination |

| <u>Exan</u> | <u>nple</u> :                | AI                   | DDWF         | REG,            | 0, 0 |                      |

|             | Before Instruc               | tion                 |              |                 |      |                      |

|             | W<br>REG<br>After Instructio | =<br>=               | 17h<br>0C2h  |                 |      |                      |

|             |                              |                      |              |                 |      |                      |

|             | W<br>REG                     | =                    | 0D9h<br>0C2h |                 |      |                      |

| Note: | All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in       |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s). |

# PIC18(L)F26/45/46K40

| POP                            | Рор Тор                                                                                                                                                                                                                                                                                               | of Return Stack               | PUSH                              | Push Top                                                                                                                                             | of Return S                   | stack                                                 |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------|

| Syntax:                        | POP                                                                                                                                                                                                                                                                                                   |                               | Syntax:                           | PUSH                                                                                                                                                 |                               |                                                       |

| Operands:                      | None                                                                                                                                                                                                                                                                                                  |                               | Operands:                         | None                                                                                                                                                 |                               |                                                       |

| Operation:                     | $(TOS) \rightarrow b$                                                                                                                                                                                                                                                                                 | it bucket                     | Operation:                        | $(PC + 2) \rightarrow$                                                                                                                               | TOS                           |                                                       |

| Status Affected                | d: None                                                                                                                                                                                                                                                                                               |                               | Status Affected                   | : None                                                                                                                                               |                               |                                                       |

| Encoding:                      | 0000                                                                                                                                                                                                                                                                                                  | 0000 0000 0110                | Encoding:                         | 0000                                                                                                                                                 | 0000 00                       | 0101                                                  |

| Description:                   | Scription: The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |                               | Description:<br>Words:            | the return stack. The previ<br>value is pushed down on t<br>This instruction allows imp<br>software stack by modifyir<br>then pushing it onto the re |                               | rious TOS<br>the stack.<br>plementing a<br>ng TOS and |

| Words:                         | 1                                                                                                                                                                                                                                                                                                     |                               | Cycles:                           | 1                                                                                                                                                    |                               |                                                       |

| Cycles:                        | 1                                                                                                                                                                                                                                                                                                     |                               | Q Cycle Activi                    | tv:                                                                                                                                                  |                               |                                                       |

| Q Cycle Activ                  | rity:                                                                                                                                                                                                                                                                                                 |                               | Q1                                | Q2                                                                                                                                                   | Q3                            | Q4                                                    |

| Q1                             | Q2                                                                                                                                                                                                                                                                                                    | Q3 Q4                         | Decod                             | e PUSH                                                                                                                                               | No                            | No                                                    |

| Decod                          | de No<br>operation                                                                                                                                                                                                                                                                                    | POP TOS No<br>value operation |                                   | PC + 2 onto<br>return stack                                                                                                                          | operation                     | operation                                             |

| Example:                       | POP<br>GOTO                                                                                                                                                                                                                                                                                           | NEW                           | Example:                          | PUSH                                                                                                                                                 |                               |                                                       |

| Before In                      |                                                                                                                                                                                                                                                                                                       | INEW                          | Before Ins<br>TOS                 | struction                                                                                                                                            | - 24546                       |                                                       |

| TOS                            |                                                                                                                                                                                                                                                                                                       | = 0031A2h<br>= 014332h        | PC                                |                                                                                                                                                      | = 345Ah<br>= 0124h            |                                                       |

| After Instruction<br>TOS<br>PC |                                                                                                                                                                                                                                                                                                       | = 014332h<br>= NEW            | After Instr<br>PC<br>TOS<br>Stacl | uction<br>< (1 level down)                                                                                                                           | = 0126h<br>= 0126h<br>= 345Ah |                                                       |

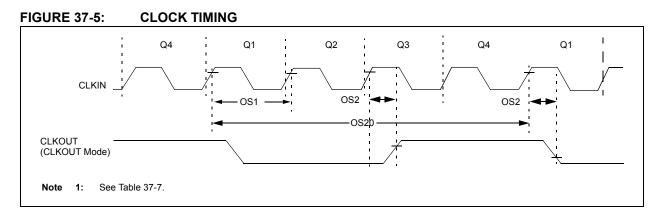

### TABLE 37-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS

| Param a contract a con |                     |                        |      |        |      |       |                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|------|--------|------|-------|------------------|--|--|

| No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Sym.                | Characteristic         | Min. | Тур†   | Max. | Units | Conditions       |  |  |

| ECL Oso                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cillator            |                        | •    |        |      |       | •                |  |  |

| OS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F <sub>ECL</sub>    | Clock Frequency        | _    | —      | 500  | kHz   |                  |  |  |

| OS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T <sub>ECL_DC</sub> | Clock Duty Cycle       | 40   | —      | 60   | %     |                  |  |  |

| ECM Os                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cillator            |                        |      |        |      |       |                  |  |  |

| OS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F <sub>ECM</sub>    | Clock Frequency        | _    | _      | 8    | MHz   |                  |  |  |

| OS4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T <sub>ECM_DC</sub> | Clock Duty Cycle       | 40   | —      | 60   | %     |                  |  |  |

| ECH Os                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cillator            |                        |      |        |      |       |                  |  |  |

| OS5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F <sub>ECH</sub>    | Clock Frequency        | _    | _      | 32   | MHz   |                  |  |  |

| OS6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T <sub>ECH_DC</sub> | Clock Duty Cycle       | 40   | —      | 60   | %     |                  |  |  |

| LP Osci                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | llator              |                        | •    |        |      |       |                  |  |  |

| OS7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F <sub>LP</sub>     | Clock Frequency        | _    | _      | 100  | kHz   | Note 4           |  |  |

| XT Osci                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | llator              |                        |      |        |      |       |                  |  |  |