#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k40t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F26/45/46K40

| U-0                                                                                                                                | U-0    | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|---------|----------------|------------------|----------------|--------------|

| _                                                                                                                                  | _      |                   |         | HFTU           | N<5:0>           |                |              |

| bit 7                                                                                                                              |        |                   |         |                |                  |                | bit 0        |

| Legend:                                                                                                                            |        |                   |         |                |                  |                |              |

| R = Readable                                                                                                                       | e bit  | W = Writable      | bit     | U = Unimplen   | nented bit, read | d as '0'       |              |

| u = Bit is uncl                                                                                                                    | nanged | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set                                                                                                                   |        | '0' = Bit is clea | ared    |                |                  |                |              |

| <pre>bit 7-6 Unimplemented: Read as '0' bit 5-0 HFTUN&lt;5:0&gt;: HFINTOSC Frequency Tuning bits 01 1111 = Maximum frequency</pre> |        |                   |         |                |                  |                |              |

# 5.1 Clock Source

The input to the reference clock output can be selected using the CLKRCLK register.

### 5.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (EN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

## 5.2 Programmable Clock Divider

The module takes the clock input and divides it based on the value of the DIV<2:0> bits of the CLKRCON register (Register 5-1).

The following configurations can be made based on the DIV<2:0> bits:

- · Base Fosc value

- Fosc divided by 2

- Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- · Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the DIV<2:0> bits should only be changed when the module is disabled (EN = 0).

# 5.3 Selectable Duty Cycle

The DC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the DC<1:0> bits should only be changed when the module is disabled (EN = 0).

Note: The DC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

# 5.4 Operation in Sleep Mode

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal. No change should occur in the module from entering or exiting from Sleep.

## 6.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Windowed Watchdog Timer (WWDT)

- External interrupt pin/Interrupt-On-Change pins

- Peripherals that run off external secondary clock source

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

| Note: | The PIC18LF2x/4xK40 devices do not<br>have a configurable Low-Power Sleep<br>mode. PIC18LF2x/4xK40 devices are<br>unregulated and are always in the lowest<br>power state when in Sleep, with no wake-<br>up time penalty. These devices have a<br>lower maximum VDD and I/O voltage than<br>the PIC18F2x/4xK40. See <b>Section</b><br><b>37.0 "Electrical Specifications"</b> for |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | more information.                                                                                                                                                                                                                                                                                                                                                                  |

## 6.2.4 IDLE MODE

When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into Idle mode. In Idle mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to Doze mode, except that in IDLE both the CPU and PFM are shut off.

Note: If CLKOUTEN is enabled (CLKOUTEN = 0, Configuration Word 1H), the output will continue operating while in Idle.

## 6.2.4.1 Idle and Interrupts

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can reenter IDLE by executing the SLEEP instruction.

If Recover-On-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of Idle also restores full-speed CPU execution when doze is also enabled.

## 6.2.4.2 Idle and WWDT

When in Idle, the WWDT Reset is blocked and will instead wake the device. The WWDT wake-up is not an interrupt, therefore ROI does not apply.

Note: The WDT can bring the device out of Idle, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

# 6.3 Peripheral Operation in Power Saving Modes

All selected clock sources and the peripherals running off them are active in both IDLE and DOZE mode. Only in Sleep mode, both the Fosc and Fosc/4 clocks are unavailable. All the other clock sources are active, if enabled manually or through peripheral clock selection before the part enters Sleep.

### **10.4 Data Memory Organization**

| Note: | The operation of some aspects of data    |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | memory are changed when the PIC18        |  |  |  |  |  |  |  |  |

|       | extended instruction set is enabled. See |  |  |  |  |  |  |  |  |

|       | Section 10.7 "Data Memory and the        |  |  |  |  |  |  |  |  |

|       | Extended Instruction Set" for more       |  |  |  |  |  |  |  |  |

|       | information.                             |  |  |  |  |  |  |  |  |

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. Figure 10-4 shows the data memory organization for the PIC18(L)F2x/4xK40 devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this subsection.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to SFRs and the lower portion of GPR Bank 0 without using the Bank Select Register (BSR). **Section 10.4.2 "Access Bank"** provides a detailed description of the Access RAM.

#### 10.4.1 BANK SELECT REGISTER (BSR)

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the four Most Significant bits of a location's address; the instruction itself includes the eight Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory; the eight bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 10-4.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory maps in Figure 10-4 indicate which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

### 10.4.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h<sup>-</sup>5Fh) in Bank 0 and the last 160 bytes of memory (60h<sup>-</sup>FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 10-4).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 10.7.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 10.4.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

#### 10.4.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top portion of Bank 15 (F38h to FFFh). A list of these registers is given in Table 10-3 and Table 10-4.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 10.6.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to either the INDF2 or POSTDEC2 register will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 10.7 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

# 10.7.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

### 10.7.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 10-7.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 35.2.1 "Extended Instruction Syntax"**.

| U-0             | U-0                         | R/W-0/0               | R/W-0/0                   | U-0              | R/W-0/0               | R/W-0/0               | R/W-0/0               |

|-----------------|-----------------------------|-----------------------|---------------------------|------------------|-----------------------|-----------------------|-----------------------|

| _               | _                           | TMR0IE <sup>(1)</sup> | IOCIE <sup>(1)</sup>      |                  | INT2IE <sup>(1)</sup> | INT1IE <sup>(1)</sup> | INT0IE <sup>(1)</sup> |

| bit 7           | •                           |                       |                           |                  |                       |                       | bit 0                 |

|                 |                             |                       |                           |                  |                       |                       |                       |

| Legend: IE      |                             |                       |                           |                  |                       |                       |                       |

| R = Readable    | bit                         | W = Writable          | bit                       | U = Unimpler     | mented bit, read      | l as '0'              |                       |

| -n = Value at F | POR                         | '1' = Bit is set      |                           | '0' = Bit is cle | ared                  | x = Bit is unkr       | nown                  |

|                 |                             |                       |                           |                  |                       |                       |                       |

| bit 7-6         | Unimplemen                  | ted: Read as '        | )'                        |                  |                       |                       |                       |

| bit 5           | TMR0IE: Time                | er0 Interrupt Er      | nable bit <sup>(1)</sup>  |                  |                       |                       |                       |

|                 | 1 = Enabled                 |                       |                           |                  |                       |                       |                       |

|                 | 0 = Disabled                |                       | (4)                       |                  |                       |                       |                       |

| bit 4           |                             | pt-on-Change          | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |

| bit 3           |                             | ted: Read as '        | ı'                        |                  |                       |                       |                       |

|                 | -                           |                       |                           |                  |                       |                       |                       |

| bit 2           |                             | nal Interrupt 2       | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |

| h:+ 1           |                             | nol Interrupt 1       | Enable hit(1)             |                  |                       |                       |                       |

| bit 1           | 1 = Enabled                 | nal Interrupt 1       | Enable bitter             |                  |                       |                       |                       |

|                 | 1 = Enabled<br>0 = Disabled |                       |                           |                  |                       |                       |                       |

| bit 0           |                             | nal Interrupt 0       | Enable bit <sup>(1)</sup> |                  |                       |                       |                       |

|                 | 1 = Enabled                 |                       |                           |                  |                       |                       |                       |

|                 | 0 = Disabled                |                       |                           |                  |                       |                       |                       |

| Note 1: PI      | R0 interrupts ar            | e not disabled        | by the PEIE I             | hit in the INTC  | ON register are       | not disabled b        | v the PEIE bit        |

# REGISTER 14-10: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

**Note 1:** PIR0 interrupts are not disabled by the PEIE bit in the INTCON register. are not disabled by the PEIE bit in the INTCON register.

# 17.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 17-1.

The peripheral input is selected with the peripheral xxxPPS register (Register 17-1), and the peripheral output is selected with the PORT RxyPPS register (Register 17-2). For example, to select PORTC<7> as the EUSART RX input, set RXxPPS to 5'b1 0111, and to select PORTC<6> as the EUSART TX output set RC6PPS to 5'b0 1001.

# 17.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has analog functions associated, the ANSEL bit for that pin must be cleared to enable the digital input buffer.

Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 17-1.

**Note:** The notation "xxx" in the register name is a place holder for the peripheral identifier. For example, INTOPPS.

# 17.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 17-2.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

# 17.8 Register Definitions: PPS Input Selection

REGISTER 17-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

| REGISTER         | 17-1: xxxPP                                                                                        | S: PERIPHE                                                                                                                                      | RAL xxx INF                                                                            | PUT SELECT                                          | ION                    |                        |                        |

|------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------|------------------------|------------------------|

| U-0              | U-0                                                                                                | U-0                                                                                                                                             | R/W-m/u <sup>(1)</sup>                                                                 | R/W-m/u <sup>(1)</sup>                              | R/W-m/u <sup>(1)</sup> | R/W-m/u <sup>(1)</sup> | R/W-m/u <sup>(1)</sup> |

| _                |                                                                                                    |                                                                                                                                                 |                                                                                        |                                                     |                        |                        |                        |

| bit 7            |                                                                                                    |                                                                                                                                                 |                                                                                        |                                                     |                        |                        | bit C                  |

|                  |                                                                                                    |                                                                                                                                                 |                                                                                        |                                                     |                        |                        |                        |

| Legend:          |                                                                                                    |                                                                                                                                                 |                                                                                        |                                                     |                        |                        |                        |

| R = Readabl      | le bit                                                                                             | W = Writable                                                                                                                                    | bit                                                                                    | -n/n = Value a                                      | at POR and BO          | R/Value at all o       | other Resets           |

| u = Bit is und   | changed                                                                                            | x = Bit is unk                                                                                                                                  | nown                                                                                   | q = value dep                                       | ends on periph         | ieral                  |                        |

| '1' = Bit is se  | et                                                                                                 | U = Unimpler                                                                                                                                    | nented bit,                                                                            | m = value de                                        | pends on defau         | It location for t      | nat input              |

| '0' = Bit is cle | eared                                                                                              | read as '                                                                                                                                       | D'                                                                                     |                                                     |                        |                        |                        |

|                  | 11 = PORTD<br>10 = PORTC<br>01 = PORTB<br>00 = PORTA                                               | (PIC18(L)F4xI                                                                                                                                   | (40 only)                                                                              | s and default p                                     |                        |                        |                        |

| bit 2-0          | 111 = Periphe<br>110 = Periphe<br>101 = Periphe<br>100 = Periphe<br>011 = Periphe<br>010 = Periphe | eral input is fro<br>eral input is fro | m PORTx Pin<br>m PORTx Pin<br>m PORTx Pin<br>m PORTx Pin<br>m PORTx Pin<br>m PORTx Pin | 6 (Rx6)<br>5 (Rx5)<br>4 (Rx4)<br>3 (Rx3)<br>2 (Rx2) | n bits                 |                        |                        |

Note 1: The Reset value 'm' of this register is determined by device default locations for that input.

© 2015-2017 Microchip Technology Inc.

# PIC18(L)F26/45/46K40

# 19.0 TIMER1/3/5 MODULE WITH GATE CONTROL

Timer1/3/5 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMRxH:TMRxL)

- Programmable internal or external clock source

- 2-bit prescaler

- Dedicated Secondary 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1/3/5 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- 16-Bit Read/Write Operation

- Time base for the Capture/Compare function with the CCP modules

- Special Event Trigger (with CCP)

- Selectable Gate Source Polarity

- · Gate Toggle mode

- Gate Single-pulse mode

- Gate Value Status

- Gate Event Interrupt

Figure 19-1 is a block diagram of the Timer1/3/5 module.

# 19.1 Register Definitions: Timer1/3/5

Long bit name prefixes for the Timer1/3/5 are shown in Table 20-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

#### TABLE 19-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| Timer1     | T1              |

| Timer3     | Т3              |

| Timer5     | T5              |

#### REGISTER 19-1: TxCON: TIMERx CONTROL REGISTER

| U-0   | U-0 | R/W-0/u R/W-0/u |  | U-0 | R/W-0/u | R/W-0/0 | R/W-0/u |

|-------|-----|-----------------|--|-----|---------|---------|---------|

| —     | —   | CKPS<1:0>       |  | —   | SYNC    | RD16    | ON      |

| bit 7 |     |                 |  |     |         |         | bit 0   |

| Legend:           |                             |                      |               |

|-------------------|-----------------------------|----------------------|---------------|

| R = Readable bit  | U = Unimplemented bit, read | as '0'               |               |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared | u = unchanged |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

#### bit 5-4 CKPS<1:0>: Timerx Input Clock Prescale Select bits

- 11 = 1:8 Prescale value

- 10 = 1:4 Prescale value

- 01 = 1:2 Prescale value

- 00 = 1:1 Prescale value

- bit 3 Unimplemented: Read as '0'

- bit 2 SYNC: Timerx External Clock Input Synchronization Control bit TMRxCLK = Fosc/4 or Fosc:

- This bit is ignored. Timer1 uses the incoming clock as is.

#### Else:

- 1 = Do not synchronize external clock input

- 0 = Synchronize external clock input with system clock

- bit 1 RD16: 16-Bit Read/Write Mode Enable bit

- 1 = Enables register read/write of Timer in one 16-bit operation

- 0 = Enables register read/write of Timer in two 8-bit operations

- bit 0 ON: Timerx On bit

- 1 = Enables Timerx

- 0 = Disables Timerx

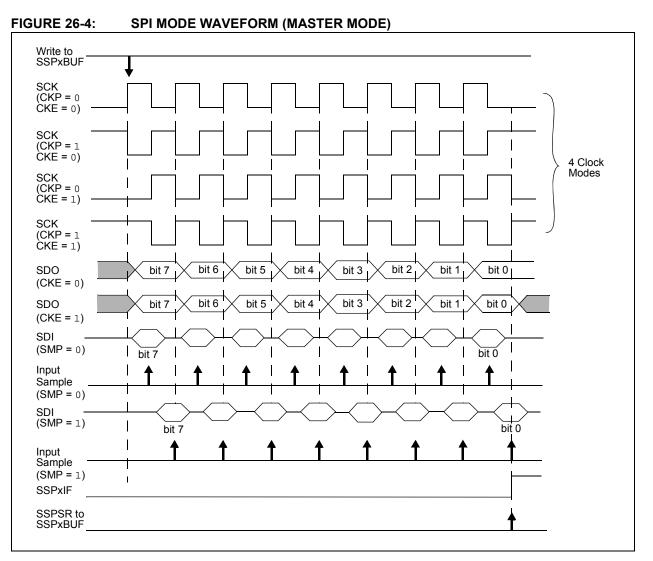

### 26.5.2 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 26.5.3 DAISY-CHAIN CONFIGURATION

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 26-5 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it. After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

## 26.10.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

## 26.10.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

The WCOL bit must be cleared by software before the next transmission.

# 26.10.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

26.10.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| Name       | Bit 7    | Bit 6     | Bit 5 | Bit 4          | Bit 3  | Bit 2      | Bit 1   | Bit 0   | Reset<br>Values<br>on Page |  |

|------------|----------|-----------|-------|----------------|--------|------------|---------|---------|----------------------------|--|

| INTCON     | GIE/GIEH | PEIE/GIEL | IPEN  | _              | _      | INT2EDG    | INT1EDG | INT0EDG | 170                        |  |

| PIE3       | RC2IE    | TX2IE     | RC1IE | TX1IE          | BCL2IE | SSP2IE     | BCL1IE  | SSP1IE  | 182                        |  |

| PIR3       | RC2IF    | TX2IF     | RC1IF | TX1IF          | BCL2IF | SSP2IF     | BCL1IF  | SSP1IF  | 174                        |  |

| IPR3       | RC2IP    | TX2IP     | RC1IP | TX1IP          | BCL2IP | SSP2IP     | BCL1IP  | SSP1IP  | 190                        |  |

| RxyPPS     | _        | —         | _     |                |        | RxyPPS<4:0 | >       |         | 218                        |  |

| SSPxADD    | ADD<7:0> |           |       |                |        |            |         |         |                            |  |

| SSPxBUF    |          |           |       | BUF<           | :7:0>  |            |         |         | 336*                       |  |

| SSPxCLKPPS | _        | —         | _     |                | S      | SPCLKPPS<4 | :0>     |         | 216                        |  |

| SSPxCON1   | WCOL     | SSPOV     | SSPEN | CKP            |        | SSPN       | 1<3:0>  |         | 338                        |  |

| SSPxCON2   | GCEN     | ACKSTAT   | ACKDT | ACKEN          | RCEN   | PEN        | RSEN    | SEN     | 355                        |  |

| SSPxCON3   | ACKTIM   | PCIE      | SCIE  | BOEN           | SDAHT  | SBCDE      | AHEN    | DHEN    | 339                        |  |

| SSPxDATPPS | _        | _         | _     | SSPDATPPS<4:0> |        |            |         |         |                            |  |

| SSPxMSK    |          |           |       | MSK•           | <7:0>  |            |         |         | 357                        |  |

| SSPxSTAT   | SMP      | CKE       | D/A   | Р              | S      | R/W        | UA      | BF      | 337                        |  |

# TABLE 26-4: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in I<sup>2</sup>C mode. \* Page provides register information.

# 27.2 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VOL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 27-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

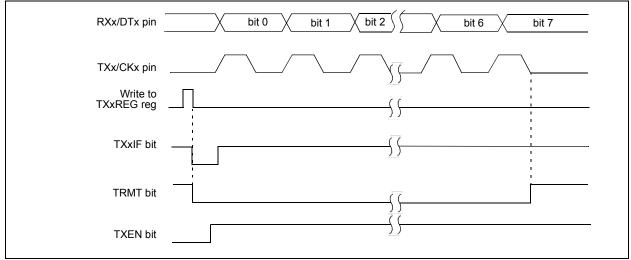

#### 27.2.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 27-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 27.2.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TXx/CKx I/O pin as an output. If the TXx/CKx pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

# 27.2.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

### 27.2.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 27.5.1.2 "Clock Polarity**".

### 27.2.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                  |            |                             |                |            |                             |                  |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos                           | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |            |                             | Foso           | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE A | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                             | _          | —                           | _                |            | _                           | _              | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | —                             | —          | —                           | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | —                | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231                         | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | _                | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | _          | _                           | 57.60k         | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | —                             |            | —                           | —                |            | —                           | 115.2k         | 0.00       | 1                           | _                | —          | —                           |

# TABLE 27-5: SAMPLE BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

| BAUD<br>RATE | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

|              | Fosc = 32.000 MHz             |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

|              | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300          | 300.0                         | 0.00       | 6666                        | 300.0             | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.0              | 0.00       | 2303                        |

| 1200         | 1200                          | -0.02      | 3332                        | 1200              | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200               | 0.00       | 575                         |

| 2400         | 2401                          | -0.04      | 832                         | 2399              | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2400               | 0.00       | 287                         |

| 9600         | 9615                          | 0.16       | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417        | 10417                         | 0.00       | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k        | 19.23k                        | 0.16       | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k        | 57.14k                        | -0.79      | 34                          | 56.818            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k       | 117.6k                        | 2.12       | 16                          | 113.636           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

| BAUD<br>RATE | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

|              | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

|              | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300          | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5            | 0.16       | 207                         |

| 1200         | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400         | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600         | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | _                | _          | _                           |

| 10417        | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k        | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          | _                | _          | _                           |

| 57.6k        | 55556                         | -3.55      | 8                           | —                | —          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k       | —                             | _          | _                           | —                | _          | _                           | 115.2k            | 0.00       | 1                           | —                | _          | _                           |

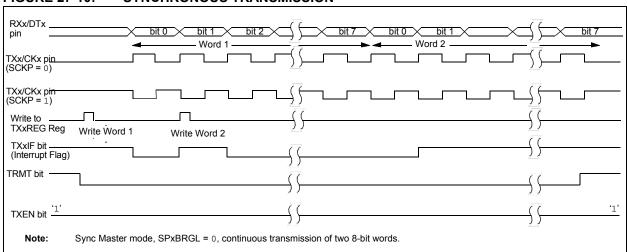

### FIGURE 27-10: SYNCHRONOUS TRANSMISSION

# PIC18(L)F26/45/46K40

| BTG                                               | Bit Toggle f                                                                                                                                                                                                                                                                                                                                                                                                    | BOV                                                                | Branch if Overflow                                                                                                                                                                                                                                                                                    |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                           | BTG f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                   | Syntax:                                                            | BOV n                                                                                                                                                                                                                                                                                                 |  |  |  |

| Operands:                                         | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                               | Operands:                                                          | $-128 \le n \le 127$                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                   | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                          | Operation:                                                         | if OVERFLOW bit is '1' (PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                 |  |  |  |

| Operation:                                        | $(f \le b >) \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                                                                             | Status Affected:                                                   | None                                                                                                                                                                                                                                                                                                  |  |  |  |

| Status Affected:                                  | None                                                                                                                                                                                                                                                                                                                                                                                                            | Encoding:                                                          | 1110 0100 nnnn nnnn                                                                                                                                                                                                                                                                                   |  |  |  |

| Encoding:<br>Description:                         | 0111bbbaffffffffBit 'b' in data memory location 'f' is<br>inverted.If 'a' is '0', the Access Bank is selected.If 'a' is '0', the BSR is used to select the<br>GPR bank.If 'a' is '1', the BSR is used to select the<br>GPR bank.If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br> | Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>If Jump: | If the OVERFLOW bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>1<br>1(2) |  |  |  |

| Words:                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                               | Q1                                                                 | Q2 Q3 Q4                                                                                                                                                                                                                                                                                              |  |  |  |

| Cycles:                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                               | Decode                                                             | Read literal         Process         Write to PC           'n'         Data                                                                                                                                                                                                                           |  |  |  |

| Q Cycle Activity:<br>Q1                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                        | No                                                                 | No No No                                                                                                                                                                                                                                                                                              |  |  |  |

| Decode                                            | Read Process Write<br>register 'f Data register 'f                                                                                                                                                                                                                                                                                                                                                              | operation<br>If No Jump:                                           | operation operation operation                                                                                                                                                                                                                                                                         |  |  |  |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                 | Q1                                                                 | Q2 Q3 Q4                                                                                                                                                                                                                                                                                              |  |  |  |

| Example:                                          | BTG PORTC, 4, 0                                                                                                                                                                                                                                                                                                                                                                                                 | Decode                                                             | Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                                                                                 |  |  |  |

| Before Instru<br>PORTC<br>After Instruct<br>PORTC | = 0111 0101 <b>[75h]</b><br>ion:                                                                                                                                                                                                                                                                                                                                                                                | PC                                                                 | = address (HERE)<br>ion<br>FLOW = 1;<br>= address (Jump)<br>FLOW = 0;                                                                                                                                                                                                                                 |  |  |  |

# PIC18(L)F26/45/46K40

| CLRF                                         | Clear f                                                                            |                          | CLRWDT            | Clear Watchdog Timer                                                                                                                                                   |                         |            |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------|--------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|--|--|--|

| Syntax:                                      | CLRF f {,a}                                                                        |                          | Syntax:           | CLRWDT                                                                                                                                                                 |                         |            |  |  |  |

| Operands:                                    | $0 \leq f \leq 255$                                                                |                          | Operands:         | None                                                                                                                                                                   |                         |            |  |  |  |

| _                                            | a ∈ [0,1]                                                                          |                          | Operation:        |                                                                                                                                                                        | 000h $\rightarrow$ WDT, |            |  |  |  |

| Operation:                                   | $\begin{array}{l} 000h \rightarrow f \\ 1 \rightarrow Z \end{array}$               |                          |                   | $\begin{array}{c} 000h \rightarrow WI \\ 1 \rightarrow TO, \\ 1 \rightarrow PD \end{array}$                                                                            | DT postscaler,          |            |  |  |  |

| Status Affected:                             | Z                                                                                  |                          | Status Affected:  | $T \rightarrow PD$<br>TO, PD                                                                                                                                           |                         |            |  |  |  |

| Encoding:                                    | ding: 0110 101a ffff ffff                                                          |                          |                   | 0000                                                                                                                                                                   | 0000 00                 | 0.0.01.0.0 |  |  |  |

| Description:                                 | Clears the contents of                                                             | the specified            | Encoding:         |                                                                                                                                                                        |                         |            |  |  |  |

|                                              | register.<br>If 'a' is '0', the Access<br>If 'a' is '1', the BSR is u<br>GPR bank. |                          | Description:      | CLRWDT instruction resets the Watchdog Timer. It also resets the post-<br>scaler of the WDT. Status bits, $\overline{\text{TO}}$ and $\overline{\text{PD}}$ , are set. |                         |            |  |  |  |