Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k40-e-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.2 Other Special Features

- **Memory Endurance:** The Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles up to 10K for program memory and 100K for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a boot loader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18(L)F2x/ 4xK40 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced Peripheral Pin Select: The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins.

- Enhanced Addressable EUSART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-bit A/D Converter with Computation:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead. It has a new module called ADC<sup>2</sup> with computation features, which provides a digital filter and threshold interrupt functions.

- Windowed Watchdog Timer (WWDT):

- Timer monitoring of overflow and underflow events

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

# 1.3 Details on Individual Family Members

Devices in the PIC18(L)F2x/4xK40 family are available in 28-pin and 40/44-pin packages. The block diagram for this device is shown in Figure 1-1.

The devices have the following differences:

- 1. Program Flash Memory

- 2. Data Memory SRAM

- 3. Data Memory EEPROM

- 4. A/D channels

- 5. I/O ports

- 6. Enhanced USART

- 7. Input Voltage Range/Power Consumption

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in the pin summary tables (Table 1 and Table 2).

### 4.2 Register Definitions: Oscillator Control

REGISTER 4-1: OSCCON1: OSCILLATOR CONTROL REGISTER1

| U-0            | R/W-f/f | R/W-f/f        | R/W-f/f | R/W-q/q      | R/W-q/q          | R/W-q/q  | R/W-q/q |

|----------------|---------|----------------|---------|--------------|------------------|----------|---------|

| —              |         | NOSC<2:0>      |         |              | NDIV             | <3:0>    |         |

| bit 7          |         |                |         |              |                  |          | bit 0   |

|                |         |                |         |              |                  |          |         |

| Legend:        |         |                |         |              |                  |          |         |

| R = Readable b | oit     | W = Writable b | oit     | U = Unimpler | nented bit, read | d as '0' |         |

|                      |                      | 0 - Onimplemented bit, read as 0                      |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by fuse setting                        |

|                      |                      | q = Reset value is determined by hardware             |

| bit 7   | Unimplemented: Read as '0'                                                  |

|---------|-----------------------------------------------------------------------------|

| bit 6-4 | NOSC<2:0>: New Oscillator Source Request bits <sup>(1,2,3)</sup>            |

|         | The setting requests a source oscillator and PLL combination per Table 4-2. |

|         | POR value = RSTOSC (Register 3-1).                                          |

| bit 3-0 | NDIV<3:0>: New Divider Selection Request bits <sup>(2,3)</sup>              |

The setting determines the new postscaler division ratio per Table 4-2.

- Note1: The default value (f/f) is determined by the RSTOSC Configuration bits. See Table 4-1below.

- 2: If NOSC is written with a reserved value (Table 4-2), the operation is ignored and neither NOSC nor NDIV is written.

- 3: When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

| TABLE 4-1: | DEFAULT OSCILLATOR SETTINGS USING RSTOSC BITS |

|------------|-----------------------------------------------|

|------------|-----------------------------------------------|

| DOTOGO | SF        | SFR Reset Values |         |                        |  |  |

|--------|-----------|------------------|---------|------------------------|--|--|

| RSTOSC | NOSC/COSC | CDIV OSCFRQ      |         | Initial Fosc Frequency |  |  |

| 111    | 111       | 1:1              |         | EXTOSC per FEXTOSC     |  |  |

| 110    | 110       | 4:1              | 4 1411- | Fosc = 1 MHz (4 MHz/4) |  |  |

| 101    | 101       | 1:1              | 4 MHz   | LFINTOSC               |  |  |

| 100    | 100       | 1:1              |         | SOSC                   |  |  |

| 011    |           |                  | Reserve | ed                     |  |  |

| 010    | 010       | 1:1              | 4 MHz   | EXTOSC + 4xPLL (1)     |  |  |

| 001    |           |                  | Reserve | ed                     |  |  |

| 000    | 110       | 1:1              | 64 MHz  | Fosc = 64 MHz          |  |  |

**Note 1:** EXTOSC must meet the PLL specifications (Table 37-9).

# 7.0 PERIPHERAL MODULE DISABLE (PMD)

Sleep, Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume some amount of power. There may be cases where the application needs what these modes do not provide: the ability to allocate limited power resources to the CPU while eliminating power consumption from the peripherals.

The PIC18(L)F2x/4xK40 family addresses this requirement by allowing peripheral modules to be selectively enabled or disabled, placing them into the lowest possible power mode.

For legacy reasons, all modules are ON by default following any Reset.

# 7.1 Disabling a Module

Disabling a module has the following effects:

- All clock and control inputs to the module are suspended; there are no logic transitions, and the module will not function.

- The module is held in Reset.

- Any SFR becomes "unimplemented"

- Writing is disabled

- Reading returns 00h

- I/O functionality is prioritized as per Section 15.1, I/O Priorities

- All associated Input Selection registers are also disabled

### 7.2 Enabling a Module

When the PMD register bit is cleared, the module is re-enabled and will be in its Reset state (Power-on Reset). SFR data will reflect the POR Reset values.

Depending on the module, it may take up to one full instruction cycle for the module to become active. There should be no interaction with the module (e.g., writing to registers) for at least one instruction after it has been re-enabled.

# 7.3 Effects of a Reset

Following any Reset, each control bit is set to '0', enabling all modules.

### 7.4 System Clock Disable

Setting SYSCMD (PMD0, Register 7-1) disables the system clock (Fosc) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit.

|              | PIC18(L)F24K40             | PIC18(L)F25K40<br>PIC18(L)F45K40 | PIC18(L)F26K40<br>PIC18(L)F46K40 | PIC18(L)F27K40<br>PIC18(L)F47K40 |             |

|--------------|----------------------------|----------------------------------|----------------------------------|----------------------------------|-------------|

| Γ            | PC<21:0>                   | PC<21:0>                         | PC<21:0>                         | PC<21:0>                         |             |

|              | Ŧ                          | Ť                                | Ŧ                                | Ŧ                                | _           |

| Note 1       | Stack (31 levels)          | Stack (31 levels)                | Stack (31 levels)                | Stack (31 levels)                | Note        |

|              | ł                          | +                                | . ↓                              | +                                | _           |

| 0000h        | Reset Vector               | Reset Vector                     | Reset Vector                     | Reset Vector                     | 00 000      |

| •••          | • • •                      | •••                              | •••                              | •••                              | •••         |

| 0008h        | Interrupt Vector High      | Interrupt Vector High            | Interrupt Vector High            | Interrupt Vector High            | 00 000      |

| •••          | • • •                      | •••                              | •••                              | •••                              | •••         |

| 0018h        | Interrupt Vector Low       | Interrupt Vector Low             | Interrupt Vector Low             | Interrupt Vector Low             | 00 00       |

| 001Ah        | User Flash Memory          |                                  |                                  |                                  | 00 00       |

| •<br>3FFFh   | (8KW)                      | User Flash Memory                |                                  |                                  | •<br>00 3FI |

| 4000h        |                            | (16KW)                           |                                  |                                  | 00 400      |

| •            |                            |                                  | User Flash Memory                |                                  | •           |

| 7FFFh        |                            |                                  | (32KW)                           | PFM Flash Memory                 | 00 7FF      |

| 8000h        |                            |                                  |                                  | (64KW)                           | 00 800      |

| •            |                            |                                  |                                  |                                  | •           |

| FFFFh        | Not present <sup>(1)</sup> |                                  |                                  |                                  | 00 FF       |

| 0000h        |                            | Not present <sup>(1)</sup>       |                                  |                                  | 01 000      |

| FFFFh        |                            | Not present                      | (4)                              |                                  | 01 FF       |

| 0000h        |                            |                                  | Not present <sup>(1)</sup>       |                                  | 02 000      |

| •            |                            |                                  |                                  | Not present <sup>(1)</sup>       | •           |

| FFFFh        |                            |                                  |                                  |                                  | 1F FF       |

| 0000h        |                            | Lises IDs.                       | (0.) (o. refe.)                  |                                  | 20 000      |

| •••<br>000Fh |                            | User IDs                         | (8 vvoras)                       |                                  | 20 000      |

| 0010h        |                            |                                  |                                  |                                  | 20 00       |

| •••          |                            | Rese                             | rved                             |                                  | •••         |

| FFFFh        |                            |                                  |                                  |                                  | 2F FF       |

| 0000h        |                            |                                  |                                  |                                  | 30 000      |

| •••<br>000Bh |                            | Configuration W                  | fords (6 Words)                  |                                  | 30 000      |

| 000Ch        |                            |                                  |                                  |                                  | 30 000      |

| •••          |                            | Rese                             | rved                             |                                  |             |

| FFFFh        |                            |                                  |                                  |                                  | 30 FF       |

| 0000h        | DataEl                     | EByte0                           | DataEE                           | ERvita                           | 31 000      |

| •••          |                            |                                  | DataLL                           | LDyteo                           | •••         |

| 00FFh        | DataEE                     | Byte255                          | •••                              | •                                |             |

|              | Unimple                    | emented                          |                                  |                                  |             |

| 03FFh        | Chimple                    |                                  | DataEEB                          | syte1023                         | 31 03       |

| 0400h        |                            |                                  |                                  |                                  | 31 040      |

| •••          |                            | Rese                             | rved                             |                                  | •••         |

| FFFBh        |                            |                                  |                                  |                                  | 3F FF       |

| FFFCh        |                            | Revision ID                      | (1 Mord)(2)                      |                                  | 3F FF       |

| FFFDh        |                            | Revision ID                      |                                  |                                  | 3F FF       |

| FFFEh        |                            |                                  |                                  |                                  | 3F FF       |

| •••          |                            | Device ID                        | (1 Word) <sup>(2)</sup>          |                                  | •••         |

| FFFFh        |                            |                                  |                                  |                                  | 3F FF       |

|              |                            | over. The region is read a       |                                  |                                  |             |

#### TABLE 10-1: PROGRAM AND DATA MEMORY MAP

#### 11.3.5 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

#### EXAMPLE 11-5: DATA EEPROM READ

| ; Data Memory Ad | ldress to read     |   |                                         |

|------------------|--------------------|---|-----------------------------------------|

| BC               | F NVMCON1, NVMREG0 | ; | Setup Data EEPROM Access                |

| BC               | F NVMCON1, NVMREG1 | ; | Setup Data EEPROM Access                |

| MO               | VF EE_ADDRL, W     | ; |                                         |

| MO               | VWF NVMADRL        | ; | Setup Address low byte                  |

| MO               | VF EE_ADDRH, W     | ; |                                         |

| MO               | VWF NVMADRH        | ; | Setup Address high byte (if applicable) |

| BS               | F NVMCON1, RD      | ; | Issue EE Read                           |

| MO               | VF NVMDAT, W       | ; | W = EE_DATA                             |

#### EXAMPLE 11-6: DATA EEPROM WRITE

| ; Data Memory Addre | ess to write     |                                           |

|---------------------|------------------|-------------------------------------------|

| BCF                 | NVMCON1, NVMREG0 | ; Setup Data EEPROM access                |

| BCF                 | NVMCON1, NVMREG1 | ; Setup Data EEPROM access                |

| MOVF                | EE_ADDRL, W      | ;                                         |

| MOVWF               | NVMADRL          | ; Setup Address low byte                  |

| MOVF                | EE_ADDRH, W      | ;                                         |

| MOVWF               | NVMADRH          | ; Setup Address high byte (if applicable) |

| ; Data Memory Value | e to write       |                                           |

| MOVF                | EE_DATA, W       | ;                                         |

| MOVWF               | NVMDAT           | ;                                         |

| ; Enable writes     |                  |                                           |

| BSF                 | NVMCON1, WREN    | ;                                         |

| ; Disable interrupt |                  |                                           |

| BCF                 | INTCON, GIE      | ;                                         |

| ; Required unlock s | -                |                                           |

| MOVLW               | 55h              |                                           |

| MOVWF               | NVMCON2<br>AAh   | · .                                       |

| MOVLW<br>MOVWF      | NVMCON2          |                                           |

| ; Set WR bit to bec |                  | 1                                         |

| BSF                 | NVMCON1, WR      | i                                         |

| ; Wait for write to |                  | ,                                         |

| BTFSC               | NVMCON1, WR      |                                           |

| BIFSC               | \$-2             |                                           |

| ; Enable INT        | γ <sup>−</sup> ∠ |                                           |

|                     | THEODY OFF       |                                           |

| BSF                 | INTCON, GIE      | ;                                         |

| ; Disable writes    |                  |                                           |

| BCF                 | NVMCON1, WREN    | ;                                         |

# 14.8 Register Definitions: Interrupt Control

| REGISTER 14-1: | <b>INTCON: INTERRUPT</b> | CONTROL REGISTER |

|----------------|--------------------------|------------------|

|                |                          |                  |

| R/W-0/0               | R/W-0/0                                                                                                  | R/W-0/0                                                                       | U-0                                              | U-0             | R/W-1/1          | R/W-1/1            | R/W-1/1        |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------|-----------------|------------------|--------------------|----------------|

| GIE/GIEH              | PEIE/GIEL                                                                                                | IPEN                                                                          | —                                                | -               | INT2EDG          | INT1EDG            | INT0EDG        |

| bit 7                 |                                                                                                          | •                                                                             |                                                  |                 |                  | •                  | bit (          |

|                       |                                                                                                          |                                                                               |                                                  |                 |                  |                    |                |

| Legend:               |                                                                                                          |                                                                               |                                                  |                 |                  |                    |                |

| R = Readabl           | e bit                                                                                                    | W = Writable                                                                  | bit                                              | U = Unimple     | emented bit, rea | d as '0'           |                |

| -n = Value at         | POR                                                                                                      | '1' = Bit is set                                                              |                                                  | '0' = Bit is c  | leared           | x = Bit is unk     | nown           |

| bit 7                 | <b>GIE/GIEH:</b> G<br>If IPEN = 1:                                                                       | lobal Interrupt I                                                             | Enable bit                                       |                 |                  |                    |                |

|                       |                                                                                                          | ables all unma<br>sables all interr                                           |                                                  | pts and cleared | by hardware for  | r high-priority ir | nterrupts only |

|                       | 1 = En                                                                                                   | ables all unmas<br>sables all interru                                         |                                                  | ots and cleared | by hardware for  | all interrupts     |                |

| bit 6                 |                                                                                                          | Peripheral Inter                                                              | rupt Enable                                      | bit             |                  |                    |                |

|                       | 0 = Dis                                                                                                  | ables all low-pr<br>sables all low-p                                          |                                                  |                 | d by hardware fo | r low-priority in  | terrupts only  |

|                       |                                                                                                          | ables all unma<br>sables all peripl                                           |                                                  | -               |                  |                    |                |

| bit 5                 | 1 = Enable                                                                                               | pt Priority Enab<br>priority levels o<br>priority levels o                    | n interrupts                                     | i               |                  |                    |                |

| bit 4-3               | Unimplemen                                                                                               | ited: Read as 'd                                                              | )'                                               |                 |                  |                    |                |

| bit 2                 | 1 = Interrup                                                                                             | xternal Interrup<br>at on rising edge<br>at on falling edge                   | e of INT2 pir                                    | ı               |                  |                    |                |

| bit 1                 | 1 = Interrup                                                                                             | xternal Interrupt<br>at on rising edge<br>at on falling edge                  | e of INT1 pir                                    | ı               |                  |                    |                |

| bit 0                 | 1 = Interrup                                                                                             | xternal Interrupt<br>at on rising edge<br>at on falling edge                  | e of INT0 pir                                    | ı               |                  |                    |                |

| co<br>its<br>er<br>th | iterrupt flag bits a<br>ondition occurs, r<br>s corresponding<br>nable bit. User s<br>le appropriate inf | egardless of the<br>enable bit or the<br>software should<br>terrupt flag bits | e state of<br>ne global<br>d ensure<br>are clear |                 |                  |                    |                |

prior to enabling an interrupt. This feature

allows for software polling.

#### **REGISTER 17-3: PPSLOCK: PPS LOCK REGISTER**

| <br> | PPSLOCKED |

|------|-----------|

|      |           |

|      | bit 0     |

|      |           |

|      |           |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 0 PPSLOCKED: PPS Locked bit

1 = PPS is locked. PPS selections can not be changed.

0 = PPS is not locked. PPS selections can be changed.

#### TABLE 17-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

| Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3        | Bit 2      | Bit 1   | Bit 0     | Register<br>on page |  |  |

|------------|-------|-------|-------|-------|--------------|------------|---------|-----------|---------------------|--|--|

| PPSLOCK    | —     | _     | _     | —     | —            | —          | —       | PPSLOCKED | 219                 |  |  |

| INTOPPS    | —     | _     | _     |       | INTOPPS<4:0> |            |         |           |                     |  |  |

| INT1PPS    | —     | _     | _     |       |              | INT1PPS<   | 4:0>    |           | 216                 |  |  |

| INT2PPS    | —     | _     | _     |       |              | INT2PPS<   | 4:0>    |           | 216                 |  |  |

| TOCKIPPS   | —     | _     |       |       |              | T0CKIPPS<  | <4:0>   |           | 216                 |  |  |

| T1CKIPPS   | _     | _     | _     |       |              | T1CKIPPS<  | <4:0>   |           | 216                 |  |  |

| T1GPPS     | —     | _     | _     |       |              | T1GPPS<    | 4:0>    |           | 216                 |  |  |

| T3CKIPPS   | —     | _     |       |       |              | T3CKIPPS<  | <4:0>   |           | 216                 |  |  |

| T3GPPS     | _     | _     | _     |       |              | T3GPPS<    | 4:0>    |           | 216                 |  |  |

| T5CKIPPS   | —     | _     | _     |       |              | T5CKIPPS<  | <4:0>   |           | 216                 |  |  |

| T5GPPS     | —     | _     |       |       |              | T5GPPS<    | 4:0>    |           | 216                 |  |  |

| T2INPPS    | _     |       |       |       |              | T2INPPS<   | 4:0>    |           | 216                 |  |  |

| T4INPPS    | —     | _     | _     |       |              | T4INPPS<   | 4:0>    |           | 216                 |  |  |

| T6INPPS    | —     | _     | _     |       |              | T6INPPS<   | 4:0>    |           | 216                 |  |  |

| CCP1PPS    | —     | _     | _     |       |              | CCP1PPS<   | :4:0>   |           | 216                 |  |  |

| CCP2PPS    | —     | _     | _     |       |              | CCP2PPS<   | :4:0>   |           | 216                 |  |  |

| CWG1PPS    | —     | _     | _     |       |              | CWG1PPS    | <4:0>   |           | 216                 |  |  |

| MDCARLPPS  | —     | _     | _     |       | Ν            | /IDCARLPPS | S<4:0>  |           | 216                 |  |  |

| MDCARHPPS  | —     | _     | _     |       | N            | IDCARHPP   | S<4:0>  |           | 216                 |  |  |

| MDSRCPPS   | —     | _     | _     |       |              | MDSRCPPS   | <4:0>   |           | 216                 |  |  |

| ADACTPPS   | —     | _     | _     |       |              | ADACTPPS   | <4:0>   |           | 216                 |  |  |

| SSP1CLKPPS | —     | _     | _     |       | S            | SP1CLKPP   | S<4:0>  |           | 216                 |  |  |

| SSP1DATPPS | —     | _     | _     |       | S            | SP1DATPP   | S<4:0>  |           | 216                 |  |  |

| SSP1SSPPS  | —     | _     | _     |       | S            | SSP1SSPPS  | \$<4:0> |           | 216                 |  |  |

| RX1PPS     | —     | _     | —     |       |              | RX1PPS<    | 4:0>    |           | 218                 |  |  |

| TX1PPS     | —     | _     | _     |       |              | TX1PPS<4   | 4:0>    |           | 216                 |  |  |

| SSP2CLKPPS | —     | _     | _     |       | S            | SP2CLKPP   | S<4:0>  |           | 216                 |  |  |

| SSP2DATPPS | —     | _     | —     |       | S            | SP2DATPP   | S<4:0>  |           | 216                 |  |  |

© 2015-2017 Microchip Technology Inc.

| Mada              | MODE  | <4:0>  | Output                                         | On creation                                               |                            | Timer Control       |                                   |

|-------------------|-------|--------|------------------------------------------------|-----------------------------------------------------------|----------------------------|---------------------|-----------------------------------|

| Mode              | <4:3> | <2:0>  | Operation                                      | Operation                                                 | Start                      | Reset               | Stop                              |

|                   |       | 000    |                                                | Software gate (Figure 20-4)                               | <b>ON =</b> 1              | _                   | ON = 0                            |

|                   |       | 001    | Period<br>Pulse                                | Hardware gate, active-high<br>(Figure 20-5)               | ON = 1 and<br>TMRx_ers = 1 | _                   | ON = 0 or<br>TMRx_ers = 0         |

|                   |       | 010    | Fuise                                          | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _                   | ON = 0 or<br>TMRx_ers = 1         |

| Free              | 0.0   | 011    |                                                | Rising or falling edge Reset                              |                            | TMRx_ers            |                                   |

| Running<br>Period | 00    | 100    | Period                                         | Rising edge Reset (Figure 20-6)                           |                            | TMRx_ers ↑          | <b>ON =</b> 0                     |

|                   |       | 101    | Pulse                                          | Falling edge Reset                                        |                            | TMRx_ers ↓          |                                   |

|                   |       | 110    | with<br>Hardware                               | Low level Reset                                           | ON = 1                     | TMRx_ers = 0        | ON = 0 or<br>TMRx_ers = 0         |

|                   |       | 111    | Reset                                          | High level Reset (Figure 20-7)                            |                            | TMRx_ers = 1        | ON = 0 or<br>TMRx_ers = 1         |

|                   |       | 000    | One-shot                                       | Software start (Figure 20-8)                              | <b>ON =</b> 1              | _                   |                                   |

|                   |       | 001 EG | Edge                                           | Rising edge start (Figure 20-9)                           | ON = 1 and<br>TMRx_ers ↑   | _                   |                                   |

|                   |       | 010    | triggered<br>start                             | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                   |                                   |

|                   |       | 011    | (Note 1)                                       | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                   | ON = 0<br>or                      |

| One-shot          | 01    | 100    | Edge                                           | Rising edge start and<br>Rising edge Reset (Figure 20-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑          | Next clock<br>after<br>TMRx = PRx |

|                   |       | 101    | triggered<br>start<br>and<br>hardware<br>Reset | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers ↓ (Note 2) |                                   |

|                   |       | 110    |                                                | Low lovel Deast (Figure 20.11) TMDy are t                 |                            | TMRx_ers = 0        |                                   |

|                   |       | 111    | (Note 1)                                       | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1        |                                   |

|                   |       | 000    |                                                | Rese                                                      | rved                       |                     |                                   |

|                   |       | 001    | Edge                                           | Rising edge start<br>(Figure 20-12)                       | ON = 1 and<br>TMRx_ers ↑   | —                   | ON = 0<br>or                      |

| Mono-stable       |       | 010    | triggered<br>start                             | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                   | Next clock<br>after               |

|                   |       | 011    | (Note 1)                                       | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                   | TMRx = PRx<br>( <b>Note 3</b> )   |

| Reserved          | 10    | 100    |                                                | Rese                                                      | rved                       |                     | •                                 |

| Reserved          |       | 101    |                                                | Rese                                                      | rved                       |                     |                                   |

|                   |       | 110    | Level<br>triggered                             | High level start and<br>Low level Reset (Figure 20-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0        | ON = 0 or                         |

| One-shot          |       | 111    | start<br>and<br>hardware<br>Reset              | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 | TMRx_ers = 1        | Held in Reset<br>(Note 2)         |

| Reserved          | 11    | xxx    |                                                | Rese                                                      | rved                       |                     |                                   |

#### TABLE 20-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

| Name     | Bit 7    | Bit 6     | Bit 5       | Bit 4  | Bit 3          | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|-------------|--------|----------------|------------|---------|---------|---------------------|

| CCPTMRS  | P4TSE    | L<1:0>    | P3TSE       | L<1:0> | C2TSE          | L<1:0>     | C1TSE   | EL<1:0> | 286                 |

| PWM3CON  | EN       | _         | OUT         | POL    | _              | —          | _       | —       | 285                 |

| PWM3DCH  |          |           |             | DC<7   | :0>            |            |         |         | 287                 |

| PWM3DCL  | DC<      | 9:8>>     | _           | —      | —              | —          | —       | —       | 287                 |

| PWM4CON  | EN       | _         | OUT         | POL    | _              | —          | _       | —       | 285                 |

| PWM4DCH  |          |           |             | DC<7   | :0>            |            |         |         | 287                 |

| PWM4DCL  | DC<      | <9:8>     | _           | _      | —              | —          | _       | —       | 287                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN        | _      | —              | INT2EDG    | INT1EDG | INT0EDG | 170                 |

| PIE4     | _        | _         | TMR6IE      | TMR5IE | TMR4IE         | TMR3IE     | TMR2IE  | TMR1IE  | 183                 |

| PIR4     | _        | _         | TMR6IF      | TMR5IF | TMR4IF         | TMR3IF     | TMR2IF  | TMR1IF  | 175                 |

| IPR4     | _        | _         | TMR6IP      | TMR5IP | TMR4IP         | TMR3IP     | TMR2IP  | TMR1IP  | 191                 |

| RxyPPS   | _        | _         | _           |        | R              | xyPPS<4:0> |         |         | 218                 |

| TMR2     |          |           |             | TMR2<  | 7:0>           |            |         |         | 244*                |

| PR2      |          |           |             | PR2<7  | <b>':0&gt;</b> |            |         |         | 244*                |

| T2CON    | T2ON     |           | T2CKPS<2:0> |        |                | T2OUTF     | PS<3:0> |         | 262                 |

| T2HLT    | T2PSYNC  | T2CPOL    | T2CSYNC     |        | T:             | 2MODE<4:0> | •       |         | 263                 |

| T2CLKCON | _        | _         | _           | _      |                | T2CS       | <3:0>   |         | 264                 |

| T2RST    |          | _         | _           | _      |                | T2RSE      | L<3:0>  |         | 265                 |

| PMD3     | _        | _         | _           | _      | PWM4MD         | PWM3MD     | CCP2MD  | CCP1MD  | 71                  |

#### TABLE 22-4: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM. \* Not a physical location.

#### 24.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWG1A output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWG1B is affected.

The CWG1DBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBR register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 24-1) is set. Refer to Figure 24-12 for an example.

# 24.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWG1B output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWG1D is affected.

The CWG1DBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBF register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 24-1) is set. Refer to Figure 24-13 for an example.

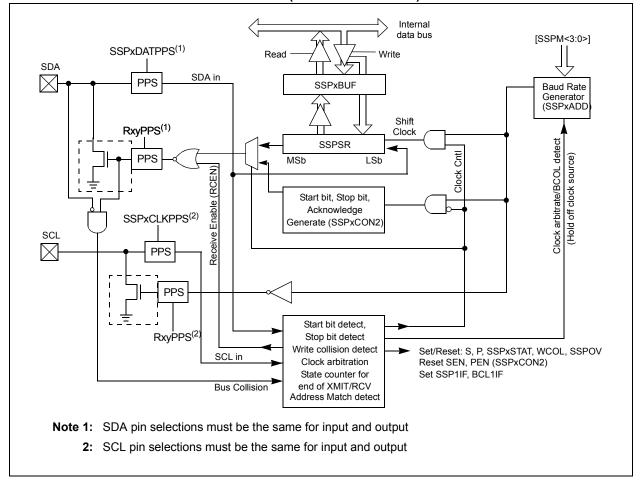

controlled through addressing. Figure 26-9 is a block diagram of the I<sup>2</sup>C interface module in Master mode.

Figure 26-10 is a diagram of the  $I^2C$  interface module

in Slave mode.

# 26.6 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is

FIGURE 26-9: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

#### 26.10.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

#### 26.10.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

The WCOL bit must be cleared by software before the next transmission.

### 26.10.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

26.10.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| ADDWFC                                                                             | ADD W and CARRY bit to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                            | ADDWFC f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Operands:                                                                          | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operation:                                                                         | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected:                                                                   | N,OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Encoding:                                                                          | 0010 00da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                                                                    | Add W, the CARRY flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit- |  |  |  |  |  |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Q Cycle Activity:                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Q1                                                                                 | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Decode                                                                             | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Example:                                                                           | ADDWFC REG, 0, 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Before Instruct<br>CARRY b<br>REG<br>W<br>After Instruction<br>CARRY b<br>REG<br>W | it = 1<br>= 02h<br>= 4Dh<br>n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| AND          | DLW               | AI   | ND lite           | ral with                 | w   |    |                          |

|--------------|-------------------|------|-------------------|--------------------------|-----|----|--------------------------|

| Synta        | ax:               | AN   | NDLW              | k                        |     |    |                          |

| Oper         | ands:             | 0 ≤  | ≤ k ≤ 258         | 5                        |     |    |                          |

| Oper         | ation:            | (W   | /) .AND.          | $k\toW$                  |     |    |                          |

| Statu        | is Affected:      | N,   | Z                 |                          |     |    |                          |

| Enco         | oding:            |      | 0000              | 1011                     | kkk | ck | kkkk                     |

| Description: |                   |      |                   | nts of W a<br>'k'. The r |     |    | d with the<br>aced in W. |

| Word         | ls:               | 1    |                   |                          |     |    |                          |

| Cycle        | es:               | 1    |                   |                          |     |    |                          |

| QC           | ycle Activity:    |      |                   |                          |     |    |                          |

|              | Q1                |      | Q2                | Q3                       | 5   |    | Q4                       |

|              | Decode            | Rea  | ad literal<br>'k' | Proce<br>Dat             |     | Wı | rite to W                |

| Exan         | nple:             | AN   | IDLW              | 05Fh                     |     |    |                          |

|              | Before Instruc    | tion |                   |                          |     |    |                          |

|              | W                 | =    | A3h               |                          |     |    |                          |

|              | After Instruction | on   |                   |                          |     |    |                          |

|              | W                 | =    | 03h               |                          |     |    |                          |

| GOTO                             | Uncondit                    | ional Branc                                        | h                                         | INCF                      | Incremen                                                                                                                                                                                                                 | tf             |                               |                        |

|----------------------------------|-----------------------------|----------------------------------------------------|-------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|------------------------|

| Syntax:                          | GOTO k                      |                                                    |                                           | Syntax:                   | INCF f{,c                                                                                                                                                                                                                | 1 {,a}}        |                               |                        |

| Operands:                        | $0 \le k \le 104$           | 8575                                               |                                           | Operands:                 | $0 \leq f \leq 255$                                                                                                                                                                                                      |                |                               |                        |

| Operation:                       | $k \rightarrow PC<20$       | ):1>                                               |                                           |                           | d ∈ [0,1]                                                                                                                                                                                                                |                |                               |                        |

| Status Affected:                 | None                        |                                                    |                                           | Operation:                | a ∈ [0,1]<br>(f) + 1 → de                                                                                                                                                                                                | oot            |                               |                        |

| Encoding:                        |                             |                                                    |                                           | Status Affected:          | ()                                                                                                                                                                                                                       |                |                               |                        |

| 1st word (k<7:0>)                |                             | 1111 k <sub>7</sub> k                              | 0                                         |                           | C, DC, N,                                                                                                                                                                                                                |                |                               |                        |

| 2nd word(k<19:8><br>Description: | ,                           | k <sub>19</sub> kkk kkl                            | 0                                         | Encoding:<br>Description: | 0010<br>The conten                                                                                                                                                                                                       | 10da           | ffff                          | ffff                   |

|                                  | value <sup>°</sup> 'k' is l | emory range. T<br>loaded into PC<br>ways a 2-cycle | C<20:1>.                                  |                           | incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank is select<br>If 'a' is '1', the BSR is used to select |                | sult is<br>ault).<br>selected |                        |

| Words:                           | 2                           |                                                    |                                           |                           | GPR bank.<br>If 'a' is '0' a                                                                                                                                                                                             |                | ended ir                      | struction              |

| Cycles:                          | 2                           |                                                    |                                           |                           | set is enab                                                                                                                                                                                                              | led, this ins  | struction                     | operates               |

| Q Cycle Activity:                |                             |                                                    |                                           |                           | in Indexed                                                                                                                                                                                                               |                |                               | •                      |

| Q1                               | Q2                          | Q3                                                 | Q4                                        |                           | mode wher<br>tion 35.2.3                                                                                                                                                                                                 |                | • •                           |                        |

| Decode                           | Read literal<br>'k'<7:0>,   | No<br>operation                                    | Read literal<br>'k'<19:8>,<br>Write to PC |                           | Oriented In<br>eral Offset                                                                                                                                                                                               | nstruction     | s in Ind                      | lexed Lit-             |

| No                               | No                          | No                                                 | No                                        | Words:                    | 1                                                                                                                                                                                                                        |                |                               |                        |

| operation                        | operation                   | operation                                          | operation                                 | Cycles:                   | 1                                                                                                                                                                                                                        |                |                               |                        |

|                                  |                             |                                                    |                                           | Q Cycle Activity:         |                                                                                                                                                                                                                          |                |                               |                        |

| Example:                         | GOTO THE                    | RE                                                 |                                           | Q1                        | Q2                                                                                                                                                                                                                       | Q3             |                               | Q4                     |

| After Instruct<br>PC =           | ion<br>Address (TI          | HERE)                                              |                                           | Decode                    | Read<br>register 'f'                                                                                                                                                                                                     | Proces<br>Data | -                             | Write to<br>estination |

|                                  |                             |                                                    |                                           | Example:                  | INCF                                                                                                                                                                                                                     | CNT, 1         | , 0                           |                        |

|                                  |                             |                                                    |                                           | Before Instruc            | tion                                                                                                                                                                                                                     |                |                               |                        |

CNT Z DC

After Instruction

CNT Z C DC FFh 0 ? ?

= = =

= = =

| MOVFF                                                                          | Move f to                                 |                                       |                                 | MOVLB                                                                        | Move lite                | ral to low ni                                                        | bble in BSR                 |  |

|--------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------|---------------------------------|------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------|-----------------------------|--|

| Syntax:                                                                        | MOVFF f <sub>s</sub> ,f <sub>d</sub>      |                                       |                                 | Syntax:                                                                      | MOVLW k                  |                                                                      |                             |  |

| Operands:                                                                      | $0 \le f_s \le 409$                       |                                       |                                 | Operands:                                                                    | $0 \le k \le 255$        |                                                                      |                             |  |

|                                                                                | $0 \le f_d \le 409$                       | 15                                    |                                 | Operation:                                                                   | $k \to BSR$              |                                                                      |                             |  |

| Operation:                                                                     | $(f_s) \rightarrow f_d$                   |                                       |                                 | Status Affected:                                                             | Status Affected: None    |                                                                      |                             |  |

| Status Affected:                                                               | None                                      |                                       |                                 | Encoding:                                                                    | 0000                     | 0001 kk                                                              | kk kkkk                     |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.)<br>Description:           | 1100<br>1111                              | 5                                     |                                 | Description:                                                                 | Bank Selec<br>of BSR<7:4 | eral 'k' is load<br>t Register (BS<br>> always rem<br>of the value o | SR). The value<br>ains '0', |  |

| Description.                                                                   |                                           | estination regis                      |                                 | Words:                                                                       | 1                        |                                                                      |                             |  |

|                                                                                | Location of                               | source 'f_s' can                      | be anywhere                     | Cycles:                                                                      | 1                        |                                                                      |                             |  |