#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

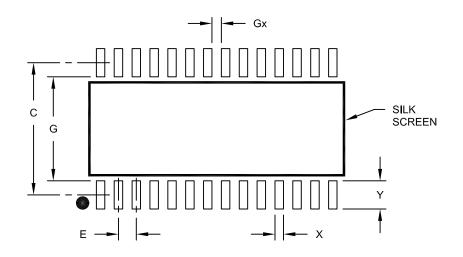

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k40-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. Low-Power Brown-Out Reset (LPBOR), if enabled

- 4. POR Reset

- 5. Windowed Watchdog Timer, if enabled

- 6. All interrupt sources except clock switch interrupt can wake-up the part.

The first five events will cause a device Reset. The last one event is considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 8.13 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 2) is prefetched. For the device to wake-up through an interrupt event, the corresponding Interrupt Enable bit must be enabled, as well as the Peripheral Interrupt Enable bit (PEIE = 1), for every interrupt not in PIRO. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP instruction, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

Upon a wake from a Sleep event, the core will wait for a combination of three conditions before beginning execution. The conditions are:

- PFM Ready

- COSC-Selected Oscillator Ready

- BOR Ready (unless BOR is disabled)

#### 6.2.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source, with the exception of the clock switch interrupt, has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

# 9.1 Register Definitions: Windowed Watchdog Timer Control

| U-0            | U-0                                            | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>                             | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0    |

|----------------|------------------------------------------------|--------------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|------------|

| —              | -                                              |                                                                    |                                        | WDTPS<4:0>                             |                                        |                                        | SEN        |

| oit 7          |                                                |                                                                    |                                        |                                        |                                        |                                        | bit (      |

| _egend:        |                                                |                                                                    |                                        |                                        |                                        |                                        |            |

| R = Readab     | le bit                                         | W = Writable b                                                     | bit                                    | U = Unimplem                           | nented bit, read                       | as '0'                                 |            |

| u = Bit is un  | changed                                        | x = Bit is unkno                                                   | own                                    | -n/n = Value a                         | t POR and BO                           | R/Value at all oth                     | ner Resets |

| 1' = Bit is se | et                                             | '0' = Bit is clea                                                  | red                                    | q = Value dep                          | ends on condit                         | on                                     |            |

| bit 7-6        | Unimpleme                                      | ented: Read as '0                                                  | ,                                      |                                        |                                        |                                        |            |

| oit 5-1        | WDTPS<4:                                       | 0>: Watchdog Tin                                                   | ner Prescale S                         | elect bits <sup>(1)</sup>              |                                        |                                        |            |

|                | Bit Value =                                    | Prescale Rate                                                      |                                        |                                        |                                        |                                        |            |

|                | 11111 <b>= F</b>                               | Reserved. Results                                                  | in minimum in                          | terval (1:32)                          |                                        |                                        |            |

|                | •                                              |                                                                    |                                        |                                        |                                        |                                        |            |

|                | •                                              |                                                                    |                                        |                                        |                                        |                                        |            |

|                | 10011 <b>= F</b>                               | Reserved. Results                                                  | in minimum in                          | terval (1:32)                          |                                        |                                        |            |

|                |                                                |                                                                    |                                        |                                        |                                        |                                        |            |

|                | 10010 = 1                                      | :8388608 (2 <sup>23</sup> ) (li                                    | nterval 256s no                        | ominal)                                |                                        |                                        |            |

|                | 10001 = 1                                      | :4194304 (2 <sup>22</sup> ) (lı<br>:2097152 (2 <sup>21</sup> ) (lı | nterval 128s no                        | ominal)                                |                                        |                                        |            |

|                | 10000 = 1                                      | :1048576 (2 <sup>20</sup> ) (II                                    | nterval 648 noi                        | ninal)<br>minal)                       |                                        |                                        |            |

|                | 01110 = 1                                      | :524288 (2 <sup>19</sup> ) (Int                                    | terval 16s nom                         | inal)                                  |                                        |                                        |            |

|                | 01101 = 1                                      | :262144 (2 <sup>18</sup> ) (Int                                    | terval 8s nomir                        | nal)                                   |                                        |                                        |            |

|                |                                                | :131072 (2 <sup>17</sup> ) (Int                                    |                                        |                                        |                                        |                                        |            |

|                |                                                | :65536 (Interval 2                                                 |                                        | eset value)                            |                                        |                                        |            |

|                |                                                | :32768 (Interval 1                                                 |                                        | D                                      |                                        |                                        |            |

|                |                                                | :16384 (Interval 5<br>:8192 (Interval 25                           |                                        |                                        |                                        |                                        |            |

|                |                                                | :4096 (Interval 12                                                 |                                        |                                        |                                        |                                        |            |

|                |                                                | :2048 (Interval 64                                                 |                                        |                                        |                                        |                                        |            |

|                |                                                | :1024 (Interval 32                                                 | -                                      |                                        |                                        |                                        |            |

|                |                                                | :512 (Interval 16                                                  |                                        |                                        |                                        |                                        |            |

|                |                                                | :256 (Interval 8 m<br>:128 (Interval 4 m                           |                                        |                                        |                                        |                                        |            |

|                |                                                | :64 (Interval 2 ms                                                 |                                        |                                        |                                        |                                        |            |

|                |                                                | :32 (Interval 1 ms                                                 | ,                                      |                                        |                                        |                                        |            |

| oit 0          | SEN: Softw                                     | are Enable/Disab                                                   | le for Watchdo                         | g Timer bit                            |                                        |                                        |            |

|                | If WDTE<1:                                     |                                                                    |                                        |                                        |                                        |                                        |            |

|                | This bit is ig                                 |                                                                    |                                        |                                        |                                        |                                        |            |

|                | $\frac{\text{If WDTE} < 1}{1 - \text{WDT is}}$ |                                                                    |                                        |                                        |                                        |                                        |            |

|                | 1 = WDT is<br>0 = WDT is                       |                                                                    |                                        |                                        |                                        |                                        |            |

|                | If WDTE<1:                                     |                                                                    |                                        |                                        |                                        |                                        |            |

|                | This bit is ig                                 |                                                                    |                                        |                                        |                                        |                                        |            |

#### REGISTER 9-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

- 2: When WDTCPS <4:0> in CONFIG3L = 11111, the Reset value of WDTPS<4:0> is 01011. Otherwise, the Reset value of WDTPS<4:0> is equal to WDTCPS<4:0> in CONFIG3L.

- 3: When WDTCPS <4:0> in CONFIG3L  $\neq$  11111, these bits are read-only.

| TADLE 13-3. | SUMIMART OF REGISTERS ASSOCIATED WITH CRC |           |        |         |        |          | 1       |         |                     |  |

|-------------|-------------------------------------------|-----------|--------|---------|--------|----------|---------|---------|---------------------|--|

| Name        | Bit 7                                     | Bit 6     | Bit 5  | Bit 4   | Bit 3  | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |  |

| CRCACCH     |                                           | ACC<15:8> |        |         |        |          |         |         |                     |  |

| CRCACCL     |                                           |           |        | ACC     | <7:0>  |          |         |         | 153                 |  |

| CRCCON0     | EN                                        | GO        | BUSY   | ACCM    | —      | —        | SHIFTM  | FULL    | 151                 |  |

| CRCCON1     |                                           | DLEN<     | 3:0>   |         |        | PLEI     | N<3:0>  |         | 151                 |  |

| CRCDATH     |                                           |           |        | DATA    | <15:8> |          |         |         | 152                 |  |

| CRCDATL     |                                           |           |        | DATA    | \<7:0> |          |         |         | 152                 |  |

| CRCSHIFTH   |                                           |           |        | SHIFT   | <15:8> |          |         |         | 153                 |  |

| CRCSHIFTL   |                                           |           |        | SHIF    | T<7:0> |          |         |         | 153                 |  |

| CRCXORH     |                                           |           |        | X<1     | 15:8>  |          |         |         | 154                 |  |

| CRCXORL     |                                           |           |        | X<7:1>  |        |          |         | —       | 154                 |  |

| PMD0        | SYSCMD                                    | FVRMD     | HLVDMD | CRCMD   | SCANMD | NVMMD    | CLKRMD  | IOCMD   | 68                  |  |

| SCANCON0    | SCANEN                                    | SCANGO    | BUSY   | INVALID | INTM   | —        | MODE    | =<1:0>  | 155                 |  |

| SCANHADRU   | —                                         | —         |        |         | HADF   | R<21:16> |         |         | 157                 |  |

| SCANHADRH   |                                           |           |        | HADR    | <15:8> |          |         |         | 158                 |  |

| SCANHADRL   |                                           |           |        | HAD     | R<7:0> |          |         |         | 158                 |  |

| SCANLADRU   | —                                         | —         |        |         | LADF   | R<21:16> |         |         | 156                 |  |

| SCANLADRH   | LADR<15:8>                                |           |        |         |        |          | 156     |         |                     |  |

| SCANLADRL   | LADR<7:0>                                 |           |        |         |        |          | 157     |         |                     |  |

| SCANTRIG    | _                                         | _         | _      |         |        | TSEI     | _<3:0>  |         | 159                 |  |

| INTCON      | GIE/GIEH                                  | PEIE/GIEL | IPEN   |         | _      | INT2EDG  | INT1EDG | INT0EDG | 170                 |  |

| PIR7        | SCANIF                                    | CRCIF     | NVMIF  |         | _      | _        | _       | CWG1IF  | 178                 |  |

| PIE7        | SCANIE                                    | CRCIE     | NVMIE  | _       | _      | _        | —       | CWG1IE  | 186                 |  |

| IPR7        | SCANIP                                    | CRCIP     | NVMIP  |         | _      |          | _       | CWG1IP  | 194                 |  |

| TABLE 13-5: | SUMMARY OF REGISTERS ASSOCIATED WITH CRC |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the CRC module.

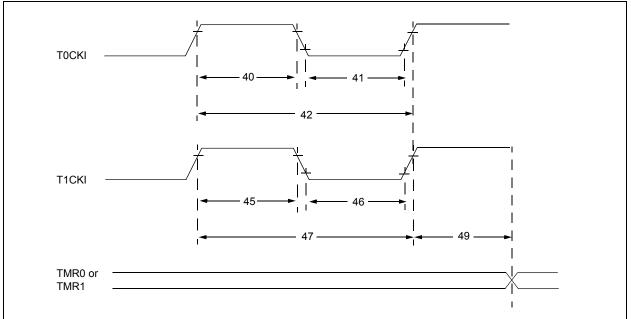

# 18.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

#### 18.1.1 16-BIT MODE

The register pair TMR0H:TMR0L, increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

# 18.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

In 16-bit mode, to avoid rollover between reading high and low registers, the TMR0H register is a buffered copy of the actual high byte of Timer0, which is neither directly readable nor writable (see Figure 18-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### 18.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

In 8-bit mode, the value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or

- Brown-out Reset (BOR)

#### 18.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the T0CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

#### 18.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the T0CKPS bits of the T0CON1 register (Register 18-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

#### 18.1.5 ASYNCHRONOUS MODE

When the TOASYNC bit of the TOCON1 register is set (TOASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

#### 18.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system clock (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

# 18.2 Clock Source Selection

The T0CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 18-2 displays the clock source selections.

#### 18.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, Timer0 operates as a timer and will increment on multiples of the clock source, as determined by the Timer0 prescaler.

#### 18.2.2 EXTERNAL CLOCK SOURCE

When an external clock source is selected, Timer0 can operate as either a timer or a counter. Timer0 will increment on multiples of the rising edge of the external clock source, as determined by the Timer0 prescaler.

#### REGISTER 18-3: TMR0L: TIMER0 COUNT REGISTER

|                  | ••••••• |                    |         |                |                  |                  |              |

|------------------|---------|--------------------|---------|----------------|------------------|------------------|--------------|

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|                  |         |                    | TMR     | 0<7:0>         |                  |                  |              |

| bit 7            |         |                    |         |                |                  |                  | bit 0        |

|                  |         |                    |         |                |                  |                  |              |

| Legend:          |         |                    |         |                |                  |                  |              |

| R = Readable b   | bit     | W = Writable bit   |         | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is uncha | inged   | x = Bit is unknown |         | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                |                  |                  |              |

bit 7-0 TMR0<7:0>:TMR0 Counter bits <7:0>

#### REGISTER 18-4: TMR0H: TIMER0 PERIOD REGISTER

| R/W-1/1    | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|------------|---------|---------|---------|---------|---------|---------|---------|

| TMR0<15:8> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 When T016BIT = 0 PR0<7:0>:TMR0 Period Register Bits <7:0> When T016BIT = 1 TMR0<15:8>: TMR0 Counter bits <15:8>

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name     | Bit 7     | Bit 6     | Bit 5  | Bit 4   | Bit 3               | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|----------|-----------|-----------|--------|---------|---------------------|-----------|---------|---------|---------------------|

| TMR0L    | TMR0<7:0> |           |        |         |                     |           |         |         | 226                 |

| TMR0H    |           |           |        | TMR0    | <15:8>              |           |         |         | 226                 |

| T0CON0   | T0EN      | —         | TOOUT  | T016BIT |                     | TOOUTPS   | <3:0>   |         | 224                 |

| T0CON1   |           | T0CS<2:0> |        | TOASYNC | T0ASYNC T0CKPS<3:0> |           |         |         | 225                 |

| T0CKIPPS | —         | —         | —      |         | TOCK                | IPPS<4:0> |         |         | 216                 |

| TMR0PPS  | _         | —         | _      |         | TMRC                | )PPS<4:0> |         |         | 216                 |

| INTCON   | GIE/GIEH  | PEIE/GIEL | IPEN   | —       | —                   | INT2EDG   | INT1EDG | INT0EDG | 170                 |

| PIR0     | —         | —         | TMR0IF | IOCIF   | —                   | INT2IF    | INT1IF  | INT0IF  | 171                 |

| PIE0     | —         | —         | TMR0IE | IOCIE   | _                   | INT2IE    | INT1IE  | INT0IE  | 179                 |

| IPR0     | —         | —         | TMR0IP | IOCIP   | —                   | INT2IP    | INT1IP  | INT0IP  | 187                 |

| PMD1     | _         | TMR6MD    | TMR5MD | TMR4MD  | TMR3MD              | TMR2MD    | TMR1MD  | TMR0MD  | 69                  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

© 2015-2017 Microchip Technology Inc.

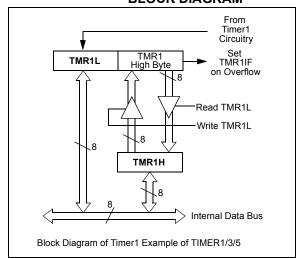

# 19.7 Timer1/3/5 16-Bit Read/Write Mode

Timer1/3/5 can be configured to read and write all 16 bits of data, to and from, the 8-bit TMRxL and TMRxH registers, simultaneously. The 16-bit read and write operations are enabled by setting the RD16 bit of the TxCON register.

To accomplish this function, the TMRxH register value is mapped to a buffer register called the TMRxH buffer register. While in 16-Bit mode, the TMRxH register is not directly readable or writable and all read and write operations take place through the use of this TMRxH buffer register.

When a read from the TMRxL register is requested, the value of the TMRxH register is simultaneously loaded into the TMRxH buffer register. When a read from the TMRxH register is requested, the value is provided from the TMRxH buffer register instead. This provides the user with the ability to accurately read all 16 bits of the Timer1/3/5 value from a single instance in time. Reference the block diagram in Figure 19-2 for more details.

In contrast, when not in 16-Bit mode, the user must read each register separately and determine if the values have become invalid due to a rollover that may have occurred between the read operations.

When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1/3/5 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

#### FIGURE 19-2:

#### TIMER1/3/5 16-BIT READ/WRITE MODE BLOCK DIAGRAM

# 19.8 Timer1/3/5 Gate

Timer1/3/5 can be configured to count freely or the count can be enabled and disabled using Timer1/3/5 gate circuitry. This is also referred to as Timer1/3/5 gate enable.

Timer1/3/5 gate can also be driven by multiple selectable sources.

#### 19.8.1 TIMER1/3/5 GATE ENABLE

The Timer1/3/5 Gate Enable mode is enabled by setting the TMRxGE bit of the TxGCON register. The polarity of the Timer1/3/5 Gate Enable mode is configured using the TxGPOL bit of the TxGCON register.

When Timer1/3/5 Gate Enable mode is enabled, Timer1/3/5 will increment on the rising edge of the Timer1/3/5 clock source. When Timer1/3/5 Gate signal is inactive, the timer will not increment and hold the current count. Enable mode is disabled, no incrementing will occur and Timer1/3/5 will hold the current count. See Figure 19-4 for timing details.

| TABLE 19-3: | TIMER1/3/5 GATE ENABLE |

|-------------|------------------------|

|             | SELECTIONS             |

| TMRxCLK    | TxGPOL | TxG | Timer1/3/5<br>Operation |

|------------|--------|-----|-------------------------|

| $\uparrow$ | 1      | 1   | Counts                  |

| $\uparrow$ | 1      | 0   | Holds Count             |

| 1          | 0      | 1   | Holds Count             |

| $\uparrow$ | 0      | 0   | Counts                  |

# 20.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

| R/W-0/0         | R/W-1/1                                                                      | R/W-0/0                      | R/W-1/1         | R/W-0/0           | R/W-1/1          | R/W-0/0         | R/W-1/1 |  |

|-----------------|------------------------------------------------------------------------------|------------------------------|-----------------|-------------------|------------------|-----------------|---------|--|

| P4TSE           | P4TSEL<1:0>                                                                  |                              | L<1:0>          | C2TSE             | EL<1:0>          | C1TSE           | L<1:0>  |  |

| bit 7           |                                                                              |                              |                 |                   |                  |                 | bit 0   |  |

|                 |                                                                              |                              |                 |                   |                  |                 |         |  |

| Legend:         |                                                                              |                              |                 |                   |                  |                 |         |  |

| R = Readable    | bit                                                                          | W = Writable                 | bit             | U = Unimplen      | nented bit, read | l as '0'        |         |  |

| -n = Value at F | POR                                                                          | '1' = Bit is set             |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |

|                 |                                                                              |                              |                 |                   |                  |                 |         |  |

| bit 7-6         |                                                                              | >: PWM4 Time                 |                 | S                 |                  |                 |         |  |

|                 |                                                                              | based on TMR                 |                 |                   |                  |                 |         |  |

|                 |                                                                              | based on TMR                 |                 |                   |                  |                 |         |  |

|                 | 01 = PWW4<br>00 = Reserv                                                     | based on TMR                 | 2               |                   |                  |                 |         |  |

|                 |                                                                              |                              | r Calastian hit | -                 |                  |                 |         |  |

| bit 5-4         |                                                                              | >: PWM3 Time<br>based on TMR |                 | .5                |                  |                 |         |  |

|                 |                                                                              | based on TMR                 | -               |                   |                  |                 |         |  |

|                 |                                                                              | based on TMR                 | -               |                   |                  |                 |         |  |

|                 | 00 = Reserv                                                                  |                              | -               |                   |                  |                 |         |  |

| bit 3-2         | C2TSEL<1:0                                                                   | >: CCP2 Timer                | Selection bits  | 6                 |                  |                 |         |  |

|                 | 11 = CCP2 is                                                                 | based off Time               | er5 in Capture  | /Compare mod      | le and Timer6 i  | n PWM mode      |         |  |

|                 | 10 = CCP2 is                                                                 | based off Time               | er3 in Capture  | /Compare mod      | le and Timer4 i  | n PWM mode      |         |  |

|                 |                                                                              |                              | er1 in Capture  | e/Compare mod     | le and Timer2 i  | n PWM mode      |         |  |

|                 | 00 = Reserve                                                                 | ed                           |                 |                   |                  |                 |         |  |

| bit 1-0         |                                                                              | >: CCP1 Timer                |                 |                   |                  |                 |         |  |

|                 | 11 = CCP1 is based off Timer5 in Capture/Compare mode and Timer6 in PWM mode |                              |                 |                   |                  |                 |         |  |

|                 |                                                                              |                              |                 | /Compare mod      |                  |                 |         |  |

|                 |                                                                              |                              | er1 in Capture  | e/Compare mod     | le and Timer2 i  | n PWM mode      |         |  |

|                 | 00 = Reserve                                                                 | ed                           |                 |                   |                  |                 |         |  |

#### REGISTER 21-2: CCPTMRS: CCP TIMERS CONTROL REGISTER

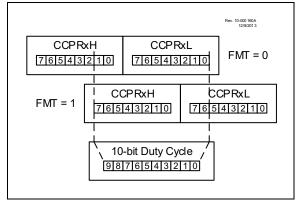

### 21.5.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the FMT bit of the CCPxCON register (see Figure 21-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between PR2 and TMR2.

Equation 21-2 is used to calculate the PWM pulse width.

Equation 21-3 is used to calculate the PWM duty cycle ratio.

FIGURE 21-5: PWM 10-BIT ALIGNMENT

#### EQUATION 21-2: PULSE WIDTH

| Pulse Width = (CCPRx) | H:CCPRxL register pair) • |

|-----------------------|---------------------------|

| Tosc                  | • (TMR2 Prescale Value)   |

# EQUATION 21-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 21-4).

### 21.5.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 21-4.

### EQUATION 21-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| R/W-0        | R/W/HC-0                          | R/W-0                               | R/W-0                | R/W-0                       | R/W-0              | R/W-0               | R/W-0              |

|--------------|-----------------------------------|-------------------------------------|----------------------|-----------------------------|--------------------|---------------------|--------------------|

| GCEN         | ACKSTAT                           | ACKDT <sup>(1)</sup>                | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>         | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7        |                                   |                                     | I                    |                             |                    |                     | bit (              |

|              |                                   |                                     |                      |                             |                    |                     |                    |

| Legend:      | 1.1.1                             |                                     |                      |                             |                    |                     |                    |

| R = Readab   |                                   | W = Writable                        | DIT                  | HC = Bit is cle             | •                  |                     |                    |

| -n = Value a | at POR                            | '1' = Bit is set                    |                      | '0' = Bit is clea           | ared               | x = Bit is unkn     | own                |

| bit 7        | GCEN: Gene                        | eral Call Enable                    | bit                  |                             |                    |                     |                    |

|              | Unused in M                       | aster mode.                         |                      |                             |                    |                     |                    |

| bit 6        | ACKSTAT: A                        | cknowledge Sta                      | atus bit (Master     | r Transmit mod              | e only)            |                     |                    |

|              |                                   | edge was not re                     |                      | ave                         |                    |                     |                    |

|              |                                   | edge was receiv                     |                      |                             |                    |                     |                    |

| bit 5        |                                   | nowledge Data                       | bit (Master Re       | ceive mode onl              | y) <sup>(1)</sup>  |                     |                    |

|              | 1 = Not Ackn                      |                                     |                      |                             |                    |                     |                    |

|              | 0 = Acknowle                      | •                                   |                      | (2)                         |                    |                     |                    |

| bit 4        |                                   | nowledge Sequ                       |                      |                             | ning and trang     | mits ACKDT dat      | ha hiti            |

|              |                                   | ically cleared by                   |                      |                             | pins and trans     |                     | la DIL,            |

|              |                                   | edge sequence                       |                      |                             |                    |                     |                    |

| bit 3        | RCEN: Rece                        | ive Enable bit (                    | Master Receive       | e mode only) <sup>(2)</sup> |                    |                     |                    |

|              | 1 = Enables                       | Receive mode f                      | or I <sup>2</sup> C  |                             |                    |                     |                    |

|              | 0 = Receive                       |                                     |                      |                             |                    |                     |                    |

| bit 2        | PEN: Stop C                       | ondition Enable                     | bit <sup>(2)</sup>   |                             |                    |                     |                    |

|              | 1 = Initiates S<br>0 = Stop con   | •                                   | n SDAx and S         | CLx pins; autor             | natically cleare   | ed by hardware      |                    |

| bit 1        | RSEN: Repe                        | ated Start Conc                     | lition Enable bi     | t <sup>(2)</sup>            |                    |                     |                    |

|              |                                   | Repeated Start<br>d Start condition |                      | DAx and SCLx                | pins; automat      | tically cleared by  | / hardware         |

| bit 0        | SEN: Start C                      | ondition Enable                     | bit <sup>(2)</sup>   |                             |                    |                     |                    |

|              | 1 = Initiates \$<br>0 = Start con |                                     | n SDAx and S         | CLx pins; autor             | matically clear    | ed by hardware      |                    |

|              | The value that w<br>eceive.       | ill be transmitted                  | d when the use       | er initiates an A           | cknowledge se      | equence at the e    | end of a           |

| 2.           | f the $l^2$ C module              | is active these                     | bite may not k       | no oot (no onoo             | ling) and the S    |                     |                    |

# 2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

#### 26.8.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 26.9 I<sup>2</sup>C Slave Mode Operation

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of the SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 26.9.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 26-5) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register affects the address matching process. See **Section 26.9.9** "**SSP Mask Register**" for more information.

### 26.9.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

#### 26.9.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 26.9.2 SLAVE RECEPTION

When the R/W bit of a matching received address byte is clear, the R/W bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 26-3.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 26.9.6.2 "10-bit Addressing Mode"** for more detail.

© 2015-2017 Microchip Technology Inc.

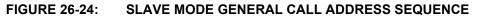

#### 26.9.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 26-24 shows general reception а call sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode. If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### 26.9.9 SSP MASK REGISTER

An SSP Mask (SSPxMSK) register (Register 26-12) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

• 7-bit Address mode: address compare of A<7:1>.

10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |                   |                             |                |                   |                             |                |                    |                             |  |  |  |

|--------|-------------------|-------------------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc           | Fosc = 20.000 MHz |                             |                | Fosc = 18.432 MHz |                             |                | Fosc = 11.0592 MHz |                             |  |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | _                 |                               | _                           | _              |                   | _                           | _              |                   | _                           | _              |                    |                             |  |  |  |

| 1200   | —                 | —                             | —                           | 1221           | 1.73              | 255                         | 1200           | 0.00              | 239                         | 1200           | 0.00               | 143                         |  |  |  |

| 2400   | 2404              | 0.16                          | 207                         | 2404           | 0.16              | 129                         | 2400           | 0.00              | 119                         | 2400           | 0.00               | 71                          |  |  |  |

| 9600   | 9615              | 0.16                          | 51                          | 9470           | -1.36             | 32                          | 9600           | 0.00              | 29                          | 9600           | 0.00               | 17                          |  |  |  |

| 10417  | 10417             | 0.00                          | 47                          | 10417          | 0.00              | 29                          | 10286          | -1.26             | 27                          | 10165          | -2.42              | 16                          |  |  |  |

| 19.2k  | 19.23k            | 0.16                          | 25                          | 19.53k         | 1.73              | 15                          | 19.20k         | 0.00              | 14                          | 19.20k         | 0.00               | 8                           |  |  |  |

| 57.6k  | 55.55k            | -3.55                         | 3                           | —              | _                 | _                           | 57.60k         | 0.00              | 7                           | 57.60k         | 0.00               | 2                           |  |  |  |

| 115.2k | —                 | _                             | _                           | —              | —                 | —                           | —              | —                 | —                           | —              | —                  | —                           |  |  |  |

#### TABLE 27-5: SAMPLE BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                  |            |                             |                |            |                             |                |            |                             |  |  |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |  |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    |                  | _                             | _                           | 300              | 0.16       | 207                         | 300            | 0.00       | 191                         | 300            | 0.16       | 51                          |  |  |  |

| 1200   | 1202             | 0.16                          | 103                         | 1202             | 0.16       | 51                          | 1200           | 0.00       | 47                          | 1202           | 0.16       | 12                          |  |  |  |

| 2400   | 2404             | 0.16                          | 51                          | 2404             | 0.16       | 25                          | 2400           | 0.00       | 23                          | _              | _          | _                           |  |  |  |

| 9600   | 9615             | 0.16                          | 12                          | _                | _          | _                           | 9600           | 0.00       | 5                           | _              | _          | _                           |  |  |  |

| 10417  | 10417            | 0.00                          | 11                          | 10417            | 0.00       | 5                           | _              | _          | _                           | _              | _          | _                           |  |  |  |

| 19.2k  | _                | _                             | _                           | _                | _          | _                           | 19.20k         | 0.00       | 2                           | _              | _          | _                           |  |  |  |

| 57.6k  | —                | —                             | —                           | —                | —          | —                           | 57.60k         | 0.00       | 0                           | —              | _          | —                           |  |  |  |

| 115.2k | —                | _                             | _                           | —                | _          | —                           | —              | _          | —                           | —              | —          | —                           |  |  |  |

|        |                   |            |                             |                | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                |            |                             |                |            |                             |  |

|--------|-------------------|------------|-----------------------------|----------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |            | Fosc = 20.000 MHz           |                |                               | Fosc = 18.432 MHz           |                |            | Fosc = 11.0592 MHz          |                |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    |                   |            | _                           |                |                               | _                           |                | _          | _                           |                | _          | _                           |  |

| 1200   | _                 | _          | —                           | _              | _                             | —                           | —              | _          | —                           | —              | _          | _                           |  |

| 2400   |                   | _          | _                           | _              | _                             | _                           | _              | _          | _                           | _              | _          | _                           |  |

| 9600   | 9615              | 0.16       | 207                         | 9615           | 0.16                          | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          |  |

| 10417  | 10417             | 0.00       | 191                         | 10417          | 0.00                          | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          |  |

| 19.2k  | 19.23k            | 0.16       | 103                         | 19.23k         | 0.16                          | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          |  |

| 57.6k  | 57.14k            | -0.79      | 34                          | 56.82k         | -1.36                         | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          |  |

| 115.2k | 117.64k           | 2.12       | 16                          | 113.64k        | -1.36                         | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           |  |

| FIGURE 27-12:                                       | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                    |

|-----------------------------------------------------|------------------------------------------------------------------------------|

| RXx/DTx<br>pin<br>TXx/CKx pin<br>(SCKP = 0)         |                                                                              |

| TXx/CKx pin<br>(SCKP = 1)<br>Write to<br>bit SREN   |                                                                              |

| SREN bit                                            | ·0'                                                                          |

| RCxIF bit<br>(Interrupt) ———<br>Read<br>RCxREG ———— |                                                                              |

| Note: Timing dia                                    | agram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

# TABLE 27-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name     | Bit 7                                  | Bit 6                                 | Bit 5   | Bit 4       | Bit 3        | Bit 2       | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------------------------------------|---------------------------------------|---------|-------------|--------------|-------------|---------|---------|---------------------|

| ANSELB   | ANSELB7                                | ANSELB6                               | ANSELB5 | ANSELB4     | ANSELB3      | ANSELB2     | ANSELB1 | ANSELB0 | 204                 |

| ANSELC   | ANSELC7                                | ANSELC6                               | ANSELC5 | ANSELC4     | ANSELC3      | ANSELC2     | ANSELC1 | ANSELC0 | 204                 |

| BAUDxCON | ABDOVF                                 | RCIDL                                 |         | SCKP        | BRG16        | _           | WUE     | ABDEN   | 395                 |

| INTCON   | GIE/GIEH                               | PEIE/GIEL                             | IPEN    | -           | -            | INT2EDG     | INT1EDG | INT0EDG | 170                 |

| PIE3     | RC2IE                                  | TX2IE                                 | RC1IE   | TX1IE       | BCL2IE       | SSP2IE      | BCL1IE  | SSP1IE  | 182                 |

| PIR3     | RC2IF                                  | TX2IF                                 | RC1IF   | TX1IF       | BCL2IF       | SSP2IF      | BCL1IF  | SSP1IF  | 174                 |

| IPR3     | RC2IP                                  | TX2IP                                 | RC1IP   | TX1IP       | BCL2IP       | SSP2IP      | BCL1IP  | SSP1IP  | 190                 |

| RCxREG   |                                        |                                       | EUS     | ARTx Receiv | e Data Regis | ter         |         |         | 399*                |

| RCxSTA   | SPEN                                   | RX9                                   | SREN    | CREN        | ADDEN        | FERR        | OERR    | RX9D    | 394                 |

| RxyPPS   | _                                      | _                                     | _       |             | F            | RxyPPS<4:0> |         |         | 218                 |

| RXxPPS   | _                                      | _                                     | _       |             |              | RXPPS<4:0>  |         |         | 216                 |

| SPxBRGH  | EUSARTx Baud Rate Generator, High Byte |                                       |         |             |              |             |         | 404*    |                     |

| SPxBRGL  |                                        | EUSARTx Baud Rate Generator, Low Byte |         |             |              |             |         |         | 404*                |

| TXxSTA   | CSRC                                   | TX9                                   | TXEN    | SYNC        | SENDB        | BRGH        | TRMT    | TX9D    | 393                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

| SUB   | FSR              | Subtrac          | Subtract Literal from FSR                |         |             |  |  |  |  |  |

|-------|------------------|------------------|------------------------------------------|---------|-------------|--|--|--|--|--|

| Synta | ax:              | SUBFSR           | f, k                                     |         |             |  |  |  |  |  |

| Oper  | ands:            | $0 \le k \le 63$ | $0 \le k \le 63$                         |         |             |  |  |  |  |  |

|       |                  | f ∈ [ 0, 1,      | f ∈ [ 0, 1, 2 ]                          |         |             |  |  |  |  |  |

| Oper  | ation:           | FSR(f) – I       | $FSR(f) - k \rightarrow FSRf$            |         |             |  |  |  |  |  |

| Statu | s Affected:      | None             |                                          |         |             |  |  |  |  |  |

| Enco  | ding:            | 1110             | 1001                                     | ffkk    | kkkk        |  |  |  |  |  |

| Desc  | ription:         | The 6-bit        | The 6-bit literal 'k' is subtracted from |         |             |  |  |  |  |  |

|       |                  | the conter       | nts of the                               | FSR spe | ecified by  |  |  |  |  |  |

|       |                  | 'f'.             |                                          |         |             |  |  |  |  |  |

| Word  | s:               | 1                | 1                                        |         |             |  |  |  |  |  |

| Cycle | es:              | 1                |                                          |         |             |  |  |  |  |  |

| QC    | ycle Activity:   |                  |                                          |         |             |  |  |  |  |  |

|       | Q1               | Q2               | Q3                                       |         | Q4          |  |  |  |  |  |

|       | Decode           | Read             | Proce                                    | ess     | Write to    |  |  |  |  |  |

|       |                  | register 'f'     | Data                                     | a c     | destination |  |  |  |  |  |

|       |                  |                  |                                          |         |             |  |  |  |  |  |

| Evan  | nle <sup>.</sup> | CIIDECD          | 2 22h                                    |         |             |  |  |  |  |  |

| Example: | SUBFSR | 2, | 23h |

|----------|--------|----|-----|

|          |        |    |     |

| Before Instru  | ction |       |

|----------------|-------|-------|

| FSR2           | =     | 03FFh |

| After Instruct | ion   |       |

| FSR2           | =     | 03DCh |

| Syntax:                          | SU                                                | BULNK k                                                                                                             |                                          |                                               |                                                     |  |  |  |

|----------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------|-----------------------------------------------------|--|--|--|

| Operands:                        | 0 ≤                                               | k ≤ 63                                                                                                              |                                          |                                               |                                                     |  |  |  |

| Operation:                       | FSI                                               | $R2 - k \rightarrow FS$                                                                                             | R2                                       |                                               |                                                     |  |  |  |

|                                  | (TC                                               | $(TOS) \rightarrow PC$                                                                                              |                                          |                                               |                                                     |  |  |  |

| Status Affected                  | l: Nor                                            | None                                                                                                                |                                          |                                               |                                                     |  |  |  |

| Encoding:                        | 1                                                 | 110 10                                                                                                              | 01                                       | 11kk                                          | kkkk                                                |  |  |  |

| Words:                           | The<br>exe<br>sec<br>This<br>the<br>'11<br>1<br>2 | ecuted by loa<br>e instruction t<br>ecute; a NOP i<br>cond cycle.<br>s may be tho<br>SUBFSR inst<br>'); it operates | akes tw<br>s perfo<br>ught of<br>ruction | vo cycle<br>ormed du<br>as a spe<br>, where t | s to<br>uring the<br>ecial case of<br>f = 3 (binary |  |  |  |

| Cycles:<br>Q Cycle Activ         |                                                   | Q2                                                                                                                  | (                                        | 23                                            | Q4                                                  |  |  |  |

| Q Cycles:<br>Q Cycle Activ<br>Q1 |                                                   | QZ                                                                                                                  |                                          |                                               |                                                     |  |  |  |

| Q Cycle Activ                    | le                                                | Read<br>register 'f'                                                                                                | Pro                                      | ocess<br>ata                                  | Write to destination                                |  |  |  |