#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k40-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Pin Allocation Tables

### TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F26K40)

| I/O <sup>(2)</sup> | 28-Pin SPDIP, SOIC, SSOP | 28-Pin (U)QFN | AD   | Reference                              | Comparator       | Timers               | CCP | CWG                 | ZCD   | Interrupt                    | EUSART                 | WSQ                   | ASSM                                         | Pull-up | Basic          |

|--------------------|--------------------------|---------------|------|----------------------------------------|------------------|----------------------|-----|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|----------------|

| RA0                | 2                        | 27            | ANA0 | _                                      | C1IN0-<br>C2IN0- |                      |     |                     | _     | IOCA0                        | —                      | —                     | _                                            | Y       | —              |

| RA1                | 3                        | 28            | ANA1 | _                                      | C1IN1-<br>C2IN1- | _                    | _   | _                   | _     | IOCA1                        | —                      | —                     | _                                            | Y       | _              |

| RA2                | 4                        | 1             | ANA2 | DAC1OUT1<br>Vref- (DAC)<br>Vref- (ADC) | C1IN0+<br>C2IN0+ | _                    | -   | -                   | Ι     | IOCA2                        | _                      |                       |                                              | Y       | -              |

| RA3                | 5                        | 2             | ANA3 | Vref+ (DAC)<br>Vref+ (ADC)             | C1IN1+           | -                    | -   |                     | _     | IOCA3                        | —                      | MDCIN1 <sup>(1)</sup> | _                                            | Y       | —              |

| RA4                | 6                        | 3             | ANA4 | _                                      | _                | T0CKI <sup>(1)</sup> | _   | _                   | -     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Y       | _              |

| RA5                | 7                        | 4             | ANA5 | _                                      | _                | _                    | _   | _                   | _     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Y       | _              |

| RA6                | 10                       | 7             | ANA6 | _                                      | —                | -                    | —   | —                   | _     | IOCA6                        | —                      | —                     | _                                            | Y       | CLKOUT<br>OSC2 |

| RA7                | 9                        | 6             | ANA7 | _                                      | _                | _                    | _   | _                   | _     | IOCA7                        | —                      | —                     | _                                            | Y       | OSC1<br>CLKIN  |

| RB0                | 21                       | 18            | ANB0 | _                                      | C2IN1+           | _                    | —   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | —                      | —                     | SS2 <sup>(1)</sup>                           | Y       | —              |

| RB1                | 22                       | 19            | ANB1 | _                                      | C1IN3-<br>C2IN3- | _                    | _   | _                   | _     | IOCB1<br>INT1 <sup>(1)</sup> | —                      | —                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | —              |

| RB2                | 23                       | 20            | ANB2 | _                                      | _                | _                    | _   | _                   | _     | IOCB2<br>INT2 <sup>(1)</sup> | —                      | —                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | —              |

| RB3                | 24                       | 21            | ANB3 | _                                      | C1IN2-<br>C2IN2- | _                    | _   | _                   | _     | IOCB3                        | —                      | —                     | _                                            | Y       | —              |

| RB4                | 25                       | 22            | ANB4 | _                                      | _                | T5G <sup>(1)</sup>   | _   | _                   | _     | IOCB4                        | _                      | _                     | _                                            | Y       | —              |

| RB5                | 26                       | 23            | ANB5 | _                                      | _                | T1G <sup>(1)</sup>   | _   | _                   | _     | IOCB5                        | —                      | _                     | _                                            | Y       | _              |

| RB6                | 27                       | 24            | ANB6 | _                                      | _                | —                    | _   |                     | _     | IOCB6                        | CK2 <sup>(1)</sup>     | _                     | _                                            | Y       | ICSPCLK        |

| RB7                | 28                       | 25            | ANB7 | DAC1OUT2                               |                  | T6AIN <sup>(1)</sup> | _   | _                   | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> | _                     | _                                            | Y       | ICSPDAT        |

PIC18(L)F26/45/46K40

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

**3:** These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for 1<sup>2</sup>C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the 1<sup>2</sup>C specific or SMBus input buffer thresholds.

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F26K40

PIC18LF26K40

- PIC18F45K40 PIC18LF45K40

- PIC18F46K40

PIC18LF46K40

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Program Flash Memory. In addition to these features, the PIC18(L)F2x/4xK40 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

### 1.1 New Core Features

### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2x/4xK40 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the secondary oscillator or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-fly Mode Switching: The powermanaged modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- **Peripheral Module Disable:** Modules that are not being used in the code can be selectively disabled using the PMD module. This further reduces the power consumption.

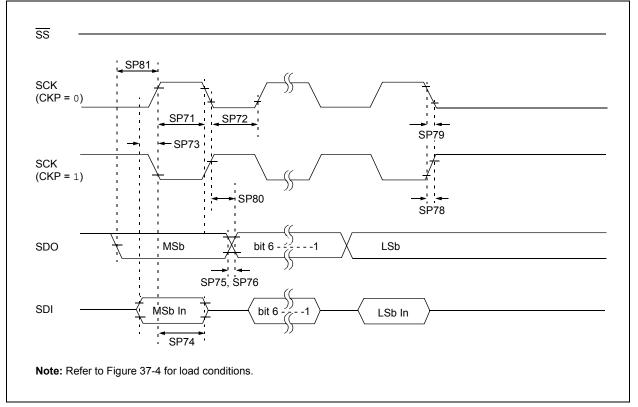

### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2x/4xK40 family offer several different oscillator options. The PIC18(L)F2x/4xK40 family can be clocked from several different sources:

- HFINTOSC

- 1-64 MHz precision digitally controlled internal oscillator

- LFINTOSC

- 31 kHz internal oscillator

- EXTOSC

- External clock (EC)

- Low-power oscillator (LP)

- Medium power oscillator (XT)

- High-power oscillator (HS)

- SOSC

- Secondary oscillator circuit operating at 31 kHz

- A Phase Lock Loop (PLL) frequency multiplier (4x) is available to the External Oscillator modes enabling clock speeds of up to 64 MHz

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

## 3.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection, Device ID and Rev ID.

## 3.1 Configuration Words

There are six Configuration Word bits that allow the user to setup the device with several choices of oscillators, Resets and memory protection options. These are implemented as Configuration Word 1 through Configuration Word 6 at 300000h through 30000Bh.

| Note: | The DEBUG bit in Configuration Words is     |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

## FIGURE 4-1:

## 6.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-On-Interrupt bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 6-1, the interrupt occurs during the 2<sup>nd</sup> instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-On-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

### EXAMPLE 6-1: DOZE SOFTWARE EXAMPLE

```

//Mainline operation

bool somethingToDo = FALSE:

void main()

initializeSystem();

// DOZE = 64:1 (for example)

// ROI = 1;

GIE = 1; // enable interrupts

while (1)

{

// If ADC completed, process data

if (somethingToDo)

{

doSomething();

DOZEN = 1; // resume low-power

}

}

// Data interrupt handler

void interrupt()

// DOZEN = 0 because ROI = 1

if (ADIF)

{

somethingToDo = TRUE;

DOE = 0; // make main() go fast

ADIF = 0;

// else check other interrupts...

if (TMROIF)

{

timerTick++;

DOE = 1; // make main() go slow

TMROIF = 0;

}

```

## 6.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0).

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The PD bit of the STATUS register is cleared (Register 10-2)

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set (Register 10-2)

- 4. The CPU clock is disabled

- 5. LFINTOSC, SOSC, HFINTOSC and ADCRC are unaffected and peripherals using them may continue operation in Sleep.

- I/O ports maintain the status they had before Sleep was executed (driving high, low, or highimpedance)

- 7. Resets other than WDT are not affected by Sleep mode

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module" and Section 28.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

## 6.4 Register Definitions: Voltage Regulator Control

## **REGISTER 6-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0                                   | U-0                                     | U-0          | U-0 | U-0                                                   | U-0 | R/W-0/0 | R/W-1/1  |  |  |

|---------------------------------------|-----------------------------------------|--------------|-----|-------------------------------------------------------|-----|---------|----------|--|--|

| _                                     | —                                       | —            | —   | —                                                     | _   | VREGPM  | Reserved |  |  |

| bit 7                                 |                                         |              |     |                                                       |     |         | bit 0    |  |  |

|                                       |                                         |              |     |                                                       |     |         |          |  |  |

| Legend:                               |                                         |              |     |                                                       |     |         |          |  |  |

| R = Readable b                        | oit                                     | W = Writable | bit | U = Unimplemented bit, read as '0'                    |     |         |          |  |  |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |              |     | -n/n = Value at POR and BOR/Value at all other Resets |     |         |          |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                         |              |     |                                                       |     |         |          |  |  |

bit 7-2 Unimplemented: Read as '0'

VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

- Draws lowest current in Sleep, slower wake-up

- 0 =Normal Power mode enabled in Sleep<sup>(2)</sup>

- Draws higher current in Sleep, faster wake-up

bit 0 **Reserved:** Read as '1'. Maintain this bit set.

Note 1: PIC18F2x/4xK40 only.

bit 1

2: See Section 37.0 "Electrical Specifications".

### TABLE 10-3: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/45/46K40 DEVICES

| Address | Namo                    | Addross |               | Addross |                      | Addross | Namo                   |

|---------|-------------------------|---------|---------------|---------|----------------------|---------|------------------------|

| r       | Name                    | Address | Name          | Address | Name                 | Address | Name                   |

| FFFh    | TOSU                    | FD7h    | PCON0         | FAFh    | T6TMR                | F87h    | LATE <sup>(2)</sup>    |

| FFEh    | TOSH                    | FD6h    | T0CON1        | FAEh    | CCPTMRS              | F86h    | LATD <sup>(2)</sup>    |

| FFDh    | TOSL                    | FD5h    | T0CON0        | FADh    | CCP1CAP              | F85h    | LATC                   |

| FFCh    | STKPTR                  | FD4h    | TMR0H         | FACh    | CCP1CON              | F84h    | LATB                   |

| FFBh    | PCLATU                  | FD3h    | TMR0L         | FABh    | CCP1H                | F83h    | LATA                   |

| FFAh    | PCLATH                  | FD2h    | T1CLK         | FAAh    | CCP1L                | F82h    | NVMCON2                |

| FF9h    | PCL                     | FD1h    | T1GATE        | FA9h    | CCP2CAP              | F81h    | NVMCON1                |

| FF8h    | TBLPTRU                 | FD0h    | T1GCON        | FA8h    | CCP2CON              | F80h    | NVMDAT                 |

| FF7h    | TBLPTRH                 | FCFh    | T1CON         | FA7h    | CCP2H                | F7Fh    | NVMADRH <sup>(3)</sup> |

| FF6h    | TBLPTRL                 | FCEh    | TMR1H         | FA6h    | CCP2L                | F7Eh    | NVMADRL                |

| FF5h    | TABLAT                  | FCDh    | TMR1L         | FA5h    | PWM3CON              | F7Dh    | CRCCON1                |

| FF4h    | PRODH                   | FCCh    | T3CLK         | FA4h    | PWM3DCH              | F7Ch    | CRCCON0                |

| FF3h    | PRODL                   | FCBh    | <b>T3GATE</b> | FA3h    | PWM3DCL              | F7Bh    | CRCXORH                |

| FF2h    | INTCON                  | FCAh    | T3GCON        | FA2h    | PWM4CON              | F7Ah    | CRCXORL                |

| FF1h    | —                       | FC9h    | T3CON         | FA1h    | PWM4DCH              | F79h    | CRCSHIFTH              |

| FF0h    | —                       | FC8h    | TMR3H         | FA0h    | PWM4DCL              | F78h    | CRCSHIFTL              |

| FEFh    | INDF0 <sup>(1)</sup>    | FC7h    | TMR3L         | F9Fh    | BAUD1CON             | F77h    | CRCACCH                |

| FEEh    | POSTINC0 <sup>(1)</sup> | FC6h    | T5CLK         | F9Eh    | TX1STA               | F76h    | CRCACCL                |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FC5h    | T5GATE        | F9Dh    | RC1STA               | F75h    | CRCDATH                |

| FECh    | PREINC0 <sup>(1)</sup>  | FC4h    | T5GCON        | F9Ch    | SP1BRGH              | F74h    | CRCDATL                |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FC3h    | T5CON         | F9Bh    | SP1BRGL              | F73h    | ADFLTRH                |

| FEAh    | FSR0H                   | FC2h    | TMR5H         | F9Ah    | TX1REG               | F72h    | ADFLTRL                |

| FE9h    | FSR0L                   | FC1h    | TMR5L         | F99h    | RC1REG               | F71h    | ADACCH                 |

| FE8h    | WREG                    | FC0h    | T2RST         | F98h    | SSP1CON3             | F70h    | ADACCL                 |

| FE7h    | INDF1 <sup>(1)</sup>    | FBFh    | T2CLKCON      | F97h    | SSP1CON2             | F6Fh    | ADERRH                 |

| FE6h    | POSTINC1 <sup>(1)</sup> | FBEh    | T2HLT         | F96h    | SSP1CON1             | F6Eh    | ADERRL                 |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FBDh    | T2CON         | F95h    | SSP1STAT             | F6Dh    | ADUTHH                 |

| FE4h    | PREINC1 <sup>(1)</sup>  | FBCh    | T2PR          | F94h    | SSP1MSK              | F6Ch    | ADUTHL                 |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FBBh    | T2TMR         | F93h    | SSP1ADD              | F6Bh    | ADLTHH                 |

| FE2h    | FSR1H                   | FBAh    | T4RST         | F92h    | SSP1BUF              | F6Ah    | ADLTHL                 |

| FE1h    | FSR1L                   | FB9h    | T4CLKCON      | F91h    | PORTE                | F69h    | ADSTPTH                |

| FE0h    | BSR                     | FB8h    | T4HLT         | F90h    | PORTD <sup>(2)</sup> | F68h    | ADSTPTL                |

| FDFh    | INDF2 <sup>(1)</sup>    | FB7h    | T4CON         | F8Fh    | PORTC                | F67h    | ADCNT                  |

| FDEh    | POSTINC2 <sup>(1)</sup> | FB6h    | T4PR          | F8Eh    | PORTB                | F66h    | ADRPT                  |

| FDDh    | POSTDEC2 <sup>(1)</sup> | FB5h    | T4TMR         | F8Dh    | PORTA                | F65h    | ADSTAT                 |

| FDCh    | PREINC2 <sup>(1)</sup>  | FB4h    | T6RST         | F8Ch    | TRISE <sup>(2)</sup> | F64h    | ADRESH                 |

| FDBh    | PLUSW2 <sup>(1)</sup>   | FB3h    | T6CLKCON      | F8Bh    | TRISD <sup>(2)</sup> | F63h    | ADRESL                 |

| FDAh    | FSR2H                   | FB2h    | T6HLT         | F8Ah    | TRISC                | F62h    | ADPREVH                |

| FD9h    | FSR2L                   | FB1h    | T6CON         | F89h    | TRISB                | F61h    | ADPREVL                |

| FD8h    | STATUS                  | FB0h    | T6PR          | F88h    | TRISA                | F60h    | ADCON0                 |

| L       | is is not a physical re | J I     |               |         |                      |         |                        |

**Note 1:** This is not a physical register.

2: Not available on PIC18(L)F26K40 (28-pin variants).

3: Not available on PIC18(L)F45K40.

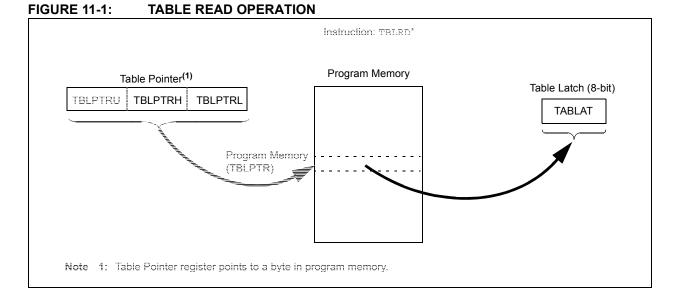

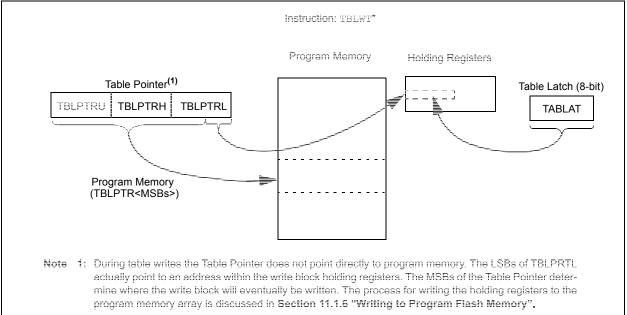

### 11.1.1 TABLE READS AND TABLE WRITES

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is eight bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 11-1 shows the operation of a table read.

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 11.1.6 "Writing to Program Flash Memory"**. Figure 11-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

## FIGURE 11-2: TABLE WRITE OPERATION

| <b>NEGISTER</b> | 14-II. FILI.I |                     |                | TENADLE          | REGISTER I       |                 |         |  |  |  |  |  |

|-----------------|---------------|---------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| R/W-0/0         | R/W-0/0       | U-0                 | U-0            | U-0              | U-0              | R/W-0/0         | R/W-0/0 |  |  |  |  |  |

| OSCFIE          | CSWIE         | —                   | _              | _                | —                | ADTIE           | ADIE    |  |  |  |  |  |

| bit 7           |               |                     |                | ·                |                  |                 | bit 0   |  |  |  |  |  |

|                 |               |                     |                |                  |                  |                 |         |  |  |  |  |  |

| Legend:         |               |                     |                |                  |                  |                 |         |  |  |  |  |  |

| R = Readable    | e bit         | W = Writable        | bit            | U = Unimpler     | mented bit, read | as '0'          |         |  |  |  |  |  |

| -n = Value at   | POR           | '1' = Bit is set    |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|                 |               |                     |                |                  |                  |                 |         |  |  |  |  |  |

| bit 7           | OSCFIE: Osc   | cillator Fail Inter | rupt Enable b  | it               |                  |                 |         |  |  |  |  |  |

|                 | 1 = Enabled   |                     |                |                  |                  |                 |         |  |  |  |  |  |

|                 | 0 = Disabled  |                     |                |                  |                  |                 |         |  |  |  |  |  |

| bit 6           | CSWIE: Cloc   | k-Switch Interru    | upt Enable bit |                  |                  |                 |         |  |  |  |  |  |

|                 | 1 = Enabled   |                     |                |                  |                  |                 |         |  |  |  |  |  |

|                 | 0 = Disabled  |                     |                |                  |                  |                 |         |  |  |  |  |  |

| bit 5-2         | Unimplemen    | ted: Read as '      | כ'             |                  |                  |                 |         |  |  |  |  |  |

| bit 1           | ADTIE: ADC    | Threshold Inte      | rrupt Enable b | oit              |                  |                 |         |  |  |  |  |  |

|                 | 1 = Enabled   |                     |                |                  |                  |                 |         |  |  |  |  |  |

| 0 = Disabled    |               |                     |                |                  |                  |                 |         |  |  |  |  |  |

| bit 0           | ADIE: ADC Ir  | nterrupt Enable     | bit            |                  |                  |                 |         |  |  |  |  |  |

|                 | 1 = Enabled   |                     |                |                  |                  |                 |         |  |  |  |  |  |

|                 | 0 = Disabled  |                     |                |                  |                  |                 |         |  |  |  |  |  |

|                 |               |                     |                |                  |                  |                 |         |  |  |  |  |  |

## REGISTER 14-11: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

## 19.2 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1/3/5 is enabled by configuring the ON and GE bits in the TxCON and TxGCON registers, respectively. Table 19-2 displays the Timer1/3/5 enable selections.

## TABLE 19-2:TIMER1/3/5 ENABLESELECTIONS

| ON | GE | Timer1/3/5<br>Operation |

|----|----|-------------------------|

| 1  | 1  | Count Enabled           |

| 1  | 0  | Always On               |

| 0  | 1  | Off                     |

| 0  | 0  | Off                     |

## 19.3 Clock Source Selection

The CS<3:0> bits of the TMRxCLK register (Register 19-3) are used to select the clock source for Timer1/3/5. The four TMRxCLK bits allow the selection of several possible synchronous and asynchronous clock sources. Register 19-3 displays the clock source selections.

### 19.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used at the Timer1/3/5 gate:

- · Asynchronous event on the TxGPPS pin

- TMR0OUT

- TMR1/3/5OUT (excluding the TMR for which it is being used)

- TMR 2/4/6OUT (post-scaled)

- CCP1/2OUT

- PWM3/4OUT

- CMP1/2OUT

- ZCDOUT

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge after any one or    |

|       | more of the following conditions:            |

- Timer1/3/5 enabled after POR

- Write to TMRxH or TMRxL

- Timer1/3/5 is disabled

- Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON = 1) when TxCKI is low.

## 19.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input of the TxCKIPPS pin. This external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated secondary internal oscillator circuit.

# PIC18(L)F26/45/46K40

| Name     | Bit 7    | Bit 6        | Bit 5          | Bit 4          | Bit 3              | Bit 2        | Bit 1   | Bit 0   | Reset<br>Values<br>on<br>Page |

|----------|----------|--------------|----------------|----------------|--------------------|--------------|---------|---------|-------------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL    | IPEN           | _              |                    | INT2EDG      | INT1EDG | INT0EDG | 170                           |

| PIE4     | _        | _            | TMR6IE         | TMR5IE         | TMR4IE             | TMR3IE       | TMR2IE  | TMR1IE  | 183                           |

| PIE5     | —        | _            | _              | _              | _                  | TMR5GIE      | TMR3GIE | TMR1GIE | 184                           |

| PIR4     | —        | —            | TMR6IF         | TMR5IF         | TMR4IF             | TMR3IF       | TMR2IF  | TMR1IF  | 174                           |

| PIR5     | _        | _            | _              | _              |                    | TMR5GIF      | TMR3GIF | TMR1GIF | 175                           |

| IPR4     | _        | _            | TMR6IP         | TMR5IP         | TMR4IP             | TMR3IP       | TMR2IP  | TMR1IP  | 191                           |

| IPR5     | —        | —            | _              | _              | _                  | TMR5GIP      | TMR3GIP | TMR1GIP | 192                           |

| PMD1     | —        | TMR6MD       | TMR5MD         | TMR4MD         | TMR3MD             | TMR2MD       | TMR1MD  | TMR0MD  | 69                            |

| T1CON    | —        | —            | CKPS           | <1:0>          | _                  | SYNC         | RD16    | ON      | 229                           |

| T1GCON   | GE       | GPOL         | GTM            | GSPM           | GO/DONE            | GVAL         | _       | _       | 230                           |

| T3CON    | _        | —            | CKPS           | i<1:0>         |                    | SYNC         | RD16    | ON      | 229                           |

| T3GCON   | GE       | GPOL         | GTM            | GSPM           | GO/DONE            | GVAL         | _       | _       | 230                           |

| T5CON    | _        | —            | CKPS           | i<1:0>         |                    | SYNC         | RD16    | ON      | 229                           |

| T5GCON   | GE       | GPOL         | GTM            | GSPM           | GO/DONE            | GVAL         | —       | —       | 230                           |

| TMR1H    |          | Holding Regi | ster for the N | lost Significa | ant Byte of the 16 | 6-bit TMR1 R | egister |         | 233                           |

| TMR1L    |          | L            | east Significa | ant Byte of th | ne 16-bit TMR1 F   | Register     |         |         | 233                           |

| TMR3H    |          | Holding Regi | ster for the N | lost Significa | ant Byte of the 16 | 6-bit TMR3 R | egister |         | 233                           |

| TMR3L    |          | L            | east Significa | ant Byte of th | ne 16-bit TMR3 F   | Register     |         |         | 233                           |

| TMR5H    |          | Holding Regi | ster for the N | lost Significa | ant Byte of the 16 | 6-bit TMR5 R | egister |         | 233                           |

| TMR5L    |          | L            | east Significa | ant Byte of th | ne 16-bit TMR5 F   | Register     |         |         | 233                           |

| T1CKIPPS | _        | —            |                |                | T1C                | CKIPPS<4:0>  |         |         | 216                           |

| T1GPPS   | —        | —            | _              |                | T1                 | GPPS<4:0>    |         |         | 216                           |

| T3CKIPPS | _        | _            | _              |                | ТЗС                | KIPPS<4:0>   |         |         | 216                           |

| T3GPPS   | _        | _            | —              |                | Т3                 | GPPS<4:0>    |         |         | 216                           |

| T5CKIPPS | _        | —            | _              |                | T5C                | CKIPPS<4:0>  |         |         | 216                           |

| T5GPPS   |          | _            | _              |                | T5                 | GPPS<4:0>    |         |         | 216                           |

### TABLE 19-4: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1/3/5 AS A TIMER/COUNTER

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by TIMER1/3/5.

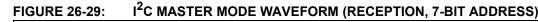

## 26.8 I<sup>2</sup>C Mode Operation

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

### 26.8.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

## 26.8.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

## 26.8.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

- Note 1: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

- 2: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA input is selected with the SSPxDATPPS registers. The SCL input is selected with the SSPxCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

### 26.8.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

### TABLE 26-2: I<sup>2</sup>C BUS TERMS

| TABLE 26-2:         | I <sup>2</sup> C BUS TERMS                                                                                                                                                            |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                           |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                        |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                         |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                              |

| Slave               | The device addressed by the master.                                                                                                                                                   |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                     |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                   |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                          |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                          |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                          |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                   |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                  |

| Read Request        | Master sends an address byte with the $R/W$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                         |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                            |

<sup>© 2015-2017</sup> Microchip Technology Inc.

PIC18(L)F26/45/46K4(

## 27.1 Register Definitions: EUSART Control

| CSRC           |                                                      |                                                        |                 | R/W-0/0         | R/W-0/0          | R-1/1            | R/W-0/0      |

|----------------|------------------------------------------------------|--------------------------------------------------------|-----------------|-----------------|------------------|------------------|--------------|

| 00100          | TX9                                                  | TXEN <sup>(1)</sup>                                    | SYNC            | SENDB           | BRGH             | TRMT             | TX9D         |

| bit 7          | ·                                                    | ·                                                      | ·               | ·               | •                |                  | bit          |

| Legend:        |                                                      |                                                        |                 |                 |                  |                  |              |

| R = Reada      | ble bit                                              | W = Writable                                           | bit             | U = Unimpler    | mented bit, read | as '0'           |              |

| u = Bit is ur  | nchanged                                             | x = Bit is unkr                                        | nown            | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is s | set                                                  | '0' = Bit is cle                                       | ared            |                 |                  |                  |              |

| bit 7          | <u>Asynchrono</u><br>Don't care<br><u>Synchronou</u> | <u>s mode</u> :                                        |                 |                 |                  |                  |              |

|                |                                                      | mode (clock ge<br>node (clock fron                     |                 |                 | )                |                  |              |

| bit 6          | 1 = Selects                                          | ransmit Enable I<br>9-bit transmiss<br>8-bit transmiss | ion             |                 |                  |                  |              |

| bit 5          | <b>TXEN:</b> Trans<br>1 = Transm<br>0 = Transm       |                                                        | )               |                 |                  |                  |              |

| bit 4          | 1 = Synchro                                          | ART Mode Sele<br>phous mode<br>ronous mode             | ct bit          |                 |                  |                  |              |

| bit 3          | Asynchrono                                           | ync Break on ne<br>eak transmissio                     | ext transmissio |                 | hardware upon o  | completion)      |              |

| bit 2          | Asynchrono                                           | eed, if BRG16 =<br>eed<br><u>s mode:</u>               |                 | is baudclk/4; e | lse baudclk/16   |                  |              |

| bit 1          |                                                      | smit Shift Regist<br>pty                               | er Status bit   |                 |                  |                  |              |

| bit 0          |                                                      | bit of Transmit<br>ess/data bit or a                   |                 |                 |                  |                  |              |

## REGISTER 27-1: TXxSTA: TRANSMIT STATUS AND CONTROL REGISTER

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | _                 |                               | _                           | _                 |            | _                           | _                 |            | _                           | _                  |            |                             |  |

| 1200   | —                 | —                             | —                           | 1221              | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1200               | 0.00       | 143                         |  |

| 2400   | 2404              | 0.16                          | 207                         | 2404              | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2400               | 0.00       | 71                          |  |

| 9600   | 9615              | 0.16                          | 51                          | 9470              | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9600               | 0.00       | 17                          |  |

| 10417  | 10417             | 0.00                          | 47                          | 10417             | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10165              | -2.42      | 16                          |  |

| 19.2k  | 19.23k            | 0.16                          | 25                          | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |  |

| 57.6k  | 55.55k            | -3.55                         | 3                           | —                 | _          | _                           | 57.60k            | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |  |

| 115.2k | —                 | _                             | _                           | —                 | —          | —                           | —                 | —          | —                           | —                  | —          | —                           |  |

### TABLE 27-5: SAMPLE BAUD RATES FOR ASYNCHRONOUS MODES

|        | <b>SYNC =</b> 0, <b>BRGH =</b> 0, <b>BRG16 =</b> 0 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|----------------------------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                   |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                                     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    |                                                    | _          | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |

| 1200   | 1202                                               | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |

| 2400   | 2404                                               | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | _                | _          | _                           |

| 9600   | 9615                                               | 0.16       | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | _                | _          | _                           |

| 10417  | 10417                                              | 0.00       | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | _                | _          | _                           |

| 19.2k  | _                                                  | _          | _                           | _                | _          | _                           | 19.20k            | 0.00       | 2                           | _                | _          | _                           |

| 57.6k  | —                                                  | —          | —                           | —                | —          | —                           | 57.60k            | 0.00       | 0                           | —                | _          | —                           |

| 115.2k | —                                                  | _          | _                           | —                | _          | —                           | —                 | _          | —                           | —                | —          | —                           |

| BAUD<br>RATE | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

|              | Fosc = 32.000 MHz             |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

|              | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300          |                               |            | _                           |                   |            | _                           |                   | _          |                             |                    | _          | _                           |

| 1200         | _                             | _          | —                           | _                 | _          | —                           | —                 | _          | —                           | —                  | _          | _                           |

| 2400         |                               | _          | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |

| 9600         | 9615                          | 0.16       | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417        | 10417                         | 0.00       | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k        | 19.23k                        | 0.16       | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k        | 57.14k                        | -0.79      | 34                          | 56.82k            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k       | 117.64k                       | 2.12       | 16                          | 113.64k           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

### 31.1.3 ADC VOLTAGE REFERENCE

The ADPREF<1:0> bits of the ADREF register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- Vdd

- FVR 1.024V

- FVR 2.048V

- FVR 4.096V

The ADNREF bit of the ADREF register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See Section 28.0 "Fixed Voltage Reference (FVR)" for more details on the Fixed Voltage Reference.

### 31.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCLK register and the ADCS bits of the ADCON0 register. There are 66 possible clock options:

- Fosc/2

- Fosc/4

- Fosc/6

- Fosc/8

- Fosc/10

- •

- •

- •

- Fosc/128

- FRC (dedicated RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 31-2.

For correct conversion, the appropriate TAD specification must be met. Refer to Table 37-14 for more information. Table 31-1 gives examples of appropriate ADC clock selections.

| Note 1: | Unless using the FRC, any changes in the<br>system clock frequency will change the<br>ADC clock frequency, which may<br>adversely affect the ADC result.                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | The internal control logic of the ADC runs<br>off of the clock selected by the ADCS bit<br>of ADCON0. What this can mean is when<br>the ADCS bit of ADCON0 is set to '1'<br>(ADC runs on FRC), there may be<br>unexpected delays in operation when<br>setting ADC control bits. |

|                    |      | Bit Clear Conditions                                  | Value after Trig                                                                         | Value after Trigger completion                              |                                                                                                                                                                                        |                        | Threshold Operations   |                |                          | Value at ADTIF interrupt |  |  |  |  |

|--------------------|------|-------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|----------------|--------------------------|--------------------------|--|--|--|--|

| Mode               | ADMD | ADACC and ADCNT                                       | ADACC                                                                                    | ADCNT                                                       | Retrigger                                                                                                                                                                              | Threshold<br>Test      | Interrupt              | ADAOV          | ADFLTR                   | ADCNT                    |  |  |  |  |

| Basic              | 0    | ADACLR = 1                                            | Unchanged                                                                                | Unchanged                                                   | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | N/A            | N/A                      | count                    |  |  |  |  |

| Accumulate         | 1    | ADACLR = 1                                            | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | ADACC Overflow | ADACC/2 <sup>ADCRS</sup> | count                    |  |  |  |  |

| Average            | 2    | ADACLR = 1 or<br>ADCNT>=ADRPT at ADGO<br>or retrigger | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow | ADACC/2 <sup>ADCRS</sup> | count                    |  |  |  |  |

| Burst<br>Average   | 3    | ADACLR = 1 or ADGO set or<br>retrigger                | Each repetition: same as<br>Average<br>End with sum of all<br>samples                    | Each repetition: same as<br>Average<br>End with ADCNT=ADRPT | Repeat while<br>ADCNT <adrpt< td=""><td>lf<br/>ADCNT&gt;=<br/>ADRPT</td><td>If thresh-<br/>old=true</td><td>ADACC Overflow</td><td>ADACC/2<sup>ADCRS</sup></td><td>ADRPT</td></adrpt<> | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow | ADACC/2 <sup>ADCRS</sup> | ADRPT                    |  |  |  |  |

| Low-pass<br>Filter | 4    | ADACLR = 1                                            | S+ADACC-ADACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ADACC-ADACC/<br>2 <sup>ADCRS</sup> | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow | Filtered Value           | count                    |  |  |  |  |

Note: S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = ADREV and S2 = ADRES.

| R/W-0/       | /0 R/W-0/0                                       | R/W-0/0                                                                                             | R/W-0/0        | R/W/HC-0                 | R/W-0/0                   | R/W-0/0           | R/W-0/0      |  |  |  |  |  |

|--------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|--------------------------|---------------------------|-------------------|--------------|--|--|--|--|--|

| ADPSI        | S                                                | ADCRS<2:0>                                                                                          |                | ADACLR                   |                           | ADMD<2:0>         |              |  |  |  |  |  |

| bit 7        |                                                  |                                                                                                     |                |                          |                           |                   | bit C        |  |  |  |  |  |

|              |                                                  |                                                                                                     |                |                          |                           |                   |              |  |  |  |  |  |

| Legend:      |                                                  |                                                                                                     |                |                          |                           |                   |              |  |  |  |  |  |

| R = Read     |                                                  | W = Writable b                                                                                      |                | U = Unimplem             |                           |                   |              |  |  |  |  |  |

|              | unchanged                                        | x = Bit is unkn                                                                                     |                |                          |                           | OR/Value at all c | other Resets |  |  |  |  |  |

| '1' = Bit is | set                                              | ʻ0' = Bit is clea                                                                                   | red            | HC = Bit is cle          | eared by hard             | ware              |              |  |  |  |  |  |

| bit 7        | ADPSIS: A                                        | ADC Previous Sam                                                                                    | ple Input Sel  | ect bits                 |                           |                   |              |  |  |  |  |  |

|              |                                                  | R is transfered to<br>S is transfered to A                                                          |                |                          |                           |                   |              |  |  |  |  |  |

| bit 6-4      | ADCRS<2                                          | ADCRS<2:0>: ADC Accumulated Calculation Right Shift Select bits                                     |                |                          |                           |                   |              |  |  |  |  |  |

|              | If ADMD =                                        |                                                                                                     | 1:             | 0                        | d by 2 <sup>ADCRS</sup> ) | (1,2)             |              |  |  |  |  |  |

| bit 3        | ADACLR:                                          | ADACLR: A/D Accumulator Clear Command bit <sup>(3)</sup>                                            |                |                          |                           |                   |              |  |  |  |  |  |

|              | 0 = Clearir                                      | ng action is comple                                                                                 | te (or not sta | rted)                    |                           |                   |              |  |  |  |  |  |

|              |                                                  | C, ADAOV and AD                                                                                     | •              |                          |                           |                   |              |  |  |  |  |  |

| bit 2-0      |                                                  | 0>: ADC Operating                                                                                   | Mode Selec     | tion bits <sup>(4)</sup> |                           |                   |              |  |  |  |  |  |

|              | 100 = Low<br>011 = Bur<br>010 = Ave<br>001 = Acc | = Reserved<br>-pass Filter mode<br>st Average mode<br>rage mode<br>umulate mode<br>ic (Legacy) mode |                |                          |                           |                   |              |  |  |  |  |  |

| Note 1:      | To correctly cal                                 | culate an average,                                                                                  | the number     | of samples (set          | in ADRPT) m               | ust be 2ADCRS     |              |  |  |  |  |  |

| 2:           |                                                  | 111 is a reserved o                                                                                 | •              |                          |                           |                   |              |  |  |  |  |  |

| 3:           |                                                  | ed by hardware wh<br>delay may be man                                                               |                |                          | n is complete             | ; depending on (  | oscillator   |  |  |  |  |  |

| 4:           | See Table 31-2                                   | for Full mode des                                                                                   | criptions.     |                          |                           |                   |              |  |  |  |  |  |

## REGISTER 31-3: ADCON2: ADC CONTROL REGISTER 2

# PIC18(L)F26/45/46K40

| ANDWF                                                    | AND W w                                                                                                                                                                                    | ith f                                                                                                                                                                      |                                                                                                                                                                            | BC                                                           | Branch i                                                                                                                         | Branch if Carry                                                                                                                                                                                                                                               |                 |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| Syntax:                                                  | ANDWF                                                                                                                                                                                      | f {,d {,a}}                                                                                                                                                                |                                                                                                                                                                            | Syntax:                                                      | BC n                                                                                                                             |                                                                                                                                                                                                                                                               |                 |  |  |

| Operands:                                                | $0 \le f \le 255$                                                                                                                                                                          |                                                                                                                                                                            |                                                                                                                                                                            | Operands:                                                    | -128 ≤ n ≤                                                                                                                       | 127                                                                                                                                                                                                                                                           |                 |  |  |

|                                                          | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                     |                                                                                                                                                                            |                                                                                                                                                                            | Operation:                                                   | if CARRY<br>(PC) + 2 +                                                                                                           |                                                                                                                                                                                                                                                               |                 |  |  |