#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                                                     |

| Core Processor             | ARM7®                                                                                                   |

| Core Size                  | 16/32-Bit                                                                                               |

| Speed                      | 72MHz                                                                                                   |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, LCD, POR, PWM, WDT                                                    |

| Number of I/O              | 160                                                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                                   |

| EEPROM Size                | -                                                                                                       |

| RAM Size                   | 96K x 8                                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                               |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                    |

| Oscillator Type            | Internal                                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                       |

| Mounting Type              | Surface Mount                                                                                           |

| Package / Case             | 208-TFBGA                                                                                               |

| Supplier Device Package    | 208-TFBGA (15x15)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2478fet208-551                               |

**LPC2478 NXP Semiconductors**

## Single-chip 16-bit/32-bit microcontroller

## 4.1 Ordering options

Table 2. **Ordering options**

| Type number   | Flash<br>(kB) | Local bus | Ethernet buffer | GP/USB M | RTC (B) | Total | External<br>bus | Ethernet | USB<br>OTG/<br>OHC/<br>device<br>+ 4 kB<br>FIFO | CAN channels | SD/<br>MMC | GP<br>DMA | ADC channels | DAC channels | Temp range       |

|---------------|---------------|-----------|-----------------|----------|---------|-------|-----------------|----------|-------------------------------------------------|--------------|------------|-----------|--------------|--------------|------------------|

| LPC2478FBD208 | 512           | 64        | 16              | 16       | 2       | 98    | Full<br>32-bit  | MII/RMII | yes                                             | 2            | yes        | yes       | 8            | 1            | –40 °C to +85 °C |

| LPC2478FET208 | 512           | 64        | 16              | 16       | 2       | 98    | Full<br>32-bit  | MII/RMII | yes                                             | 2            | yes        | yes       | 8            | 1            | –40 °C to +85 °C |

## Single-chip 16-bit/32-bit microcontroller

Table 3.

Pin allocation table ...continued

| Pin    | Symbol                                            | Pin | Symbol                                                       | Pin       | Symbol                                                       | Pin | Symbol                                                 |

|--------|---------------------------------------------------|-----|--------------------------------------------------------------|-----------|--------------------------------------------------------------|-----|--------------------------------------------------------|

| 13     | P3[20]/D20/<br>PWM0[5]/DSR1                       | 14  | P1[11]/ENET_RXD2/<br>MCIDAT2/PWM0[6]                         | 15        | P0[8]/l2STX_WS/<br>LCDVD[16]/MISO1/<br>MAT2[2]               | 16  | P1[12]/ENET_RXD3/<br>MCIDAT3/PCAP0[0]                  |

| 17     | P1[5]/ENET_TX_ER/<br>MCIPWR/PWM0[3]               |     | -                                                            |           | -                                                            |     | -                                                      |

| Rov    | <i>I</i> B                                        |     |                                                              | •         |                                                              | •   |                                                        |

| 1      | P3[2]/D2                                          | 2   | P3[10]/D10                                                   | 3         | P3[1]/D1                                                     | 4   | P3[0]/D0                                               |

| 5      | P1[1]/ENET_TXD1                                   | 6   | V <sub>SSIO</sub>                                            | 7         | P4[30]/CS0                                                   | 8   | P4[24]/ <del>OE</del>                                  |

| 9      | P4[25]/WE                                         | 10  | P4[29]/BLS3/MAT2[1]/<br>LCDVD[7]/LCDVD[11]/<br>LCDVD[3]/RXD3 | 11        | P1[6]/ENET_TX_CLK/<br>MCIDAT0/PWM0[4]                        | 12  | P0[4]/I2SRX_CLK/<br>LCDVD[0]/RD2/CAP2[0]               |

| 13     | V <sub>DD(3V3)</sub>                              | 14  | P3[19]/D19/<br>PWM0[4]/DCD1                                  | 15        | P4[14]/A14                                                   | 16  | P4[13]/A13                                             |

| 17     | P2[0]/PWM1[1]/TXD1/<br>TRACECLK/LCDPWR            |     | -                                                            |           | -                                                            |     | -                                                      |

| Rov    | ı C                                               |     |                                                              |           |                                                              |     |                                                        |

| 1      | P3[13]/D13                                        | 2   | TDI                                                          | 3         | RTCK                                                         | 4   | P0[2]/TXD0                                             |

| 5      | P3[9]/D9                                          | 6   | P3[22]/D22/<br>PCAP0[0]/RI1                                  | 7         | P1[8]/ENET_CRS_DV/<br>ENET_CRS                               | 8   | P1[10]/ENET_RXD1                                       |

| 9      | V <sub>DD(3V3)</sub>                              | 10  | P3[21]/D21/<br>PWM0[6]/DTR1                                  | 11        | P4[28]/BLS2/MAT2[0]/<br>LCDVD[6]/LCDVD[10]/<br>LCDVD[2]/TXD3 | 12  | P0[5]/I2SRX_WS/<br>LCDVD[1]/TD2/CAP2[1]                |

| 13     | P0[7]/I2STX_CLK/<br>LCDVD[9]/SCK1/<br>MAT2[1]     | 14  | P0[9]/I2STX_SDA/<br>LCDVD[17]/MOSI1/<br>MAT2[3]              | 15        | P3[18]/D18/<br>PWM0[3]/CTS1                                  | 16  | P4[12]/A12                                             |

| 17     | V <sub>DD(3V3)</sub>                              |     | -                                                            |           | -                                                            |     | -                                                      |

| Rov    | <i>I</i> D                                        |     |                                                              | •         |                                                              | •   |                                                        |

| 1      | TRST                                              | 2   | P3[28]/D28/<br>CAP1[1]/PWM1[5]                               | 3         | TDO                                                          | 4   | P3[12]/D12                                             |

| 5      | P3[11]/D11                                        | 6   | P0[3]/RXD0                                                   | 7         | V <sub>DD(3V3)</sub>                                         | 8   | P3[8]/D8                                               |

| 9      | P1[2]/ENET_TXD2/<br>MCICLK/PWM0[1]                | 10  | P1[16]/ENET_MDC                                              | 11        | V <sub>DD(DCDC)(3V3)</sub>                                   | 12  | V <sub>SSCORE</sub>                                    |

| 13     | P0[6]/I2SRX_SDA/<br>LCDVD[8]/SSEL1/<br>MAT2[0]    | 14  | P1[7]/ENET_COL/<br>MCIDAT1/PWM0[5]                           | 15        | P2[2]/PWM1[3]/CTS1/<br>PIPESTAT1/LCDDCLK                     | 16  | P1[13]/ENET_RX_DV                                      |

| 17     | P2[4]/PWM1[5]/<br>DSR1/TRACESYNC/<br>LCDENAB/LCDM |     | -                                                            |           | -                                                            |     | -                                                      |

| Rov    | <i>I</i> E                                        |     |                                                              |           |                                                              |     |                                                        |

| 1      | P0[26]/AD0[3]/<br>AOUT/RXD3                       | 2   | TCK                                                          | 3         | TMS                                                          | 4   | P3[3]/D3                                               |

| 14     | P2[1]/PWM1[2]/RXD1/<br>PIPESTAT0/LCDLE            | 15  | V <sub>SSIO</sub>                                            | 16        | P2[3]/PWM1[4]/DCD1/<br>PIPESTAT2/LCDFP                       | 17  | P2[6]/PCAP1[0]/RI1/<br>TRACEPKT1/<br>LCDVD[0]/LCDVD[4] |

| Rov    | <i>I</i> F                                        |     |                                                              |           |                                                              | ,   |                                                        |

| 1      | P0[25]/AD0[2]/<br>I2SRX_SDA/TXD3                  | 2   | P3[4]/D4                                                     | 3         | P3[29]/D29/<br>MAT1[0]/PWM1[6]                               | 4   | DBGEN                                                  |

| LPC247 | 8                                                 | •   | All information provided in this do                          | rument is | subject to legal disclaimers                                 | •   | © NXP B.V. 2013. All rights reserved.                  |

LPC2478

## Single-chip 16-bit/32-bit microcontroller

## 6.2 Pin description

Table 4. Pin description

| Symbol                     | Pin                | Ball               | Type | Description                                                                                                                                                                                |     |                                                                                                                                                                                           |

|----------------------------|--------------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[0] to P0[31]            |                    |                    | I/O  | <b>Port 0:</b> Port 0 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 0 pins depends upon the pin function selected via the pin connect block. |     |                                                                                                                                                                                           |

|                            |                    | U15 <sup>[1]</sup> | I/O  | P0[0] — General purpose digital input/output pin.                                                                                                                                          |     |                                                                                                                                                                                           |

| SDA1                       |                    |                    | I    | RD1 — CAN1 receiver input.                                                                                                                                                                 |     |                                                                                                                                                                                           |

|                            |                    |                    | 0    | TXD3 — Transmitter output for UART3.                                                                                                                                                       |     |                                                                                                                                                                                           |

|                            |                    |                    | I/O  | SDA1 — I <sup>2</sup> C1 data input/output (this is not an open-drain pin).                                                                                                                |     |                                                                                                                                                                                           |

| P0[1]/TD1/RXD3/            | 96 <sup>[1]</sup>  | T14[1]             | I/O  | P0[1] — General purpose digital input/output pin.                                                                                                                                          |     |                                                                                                                                                                                           |

| SCL1                       |                    |                    | 0    | TD1 — CAN1 transmitter output.                                                                                                                                                             |     |                                                                                                                                                                                           |

|                            |                    |                    | I    | RXD3 — Receiver input for UART3.                                                                                                                                                           |     |                                                                                                                                                                                           |

|                            |                    |                    | I/O  | SCL1 — I <sup>2</sup> C1 clock input/output (this is not an open-drain pin).                                                                                                               |     |                                                                                                                                                                                           |

| P0[2]/TXD0                 | 202[1]             | C4[1]              | I/O  | P0[2] — General purpose digital input/output pin.                                                                                                                                          |     |                                                                                                                                                                                           |

|                            |                    |                    | 0    | <b>TXD0</b> — Transmitter output for UART0.                                                                                                                                                |     |                                                                                                                                                                                           |

| P0[3]/RXD0                 | 204 <u>[1]</u>     | D6[1]              | I/O  | P0[3] — General purpose digital input/output pin.                                                                                                                                          |     |                                                                                                                                                                                           |

|                            |                    |                    | I    | RXD0 — Receiver input for UART0.                                                                                                                                                           |     |                                                                                                                                                                                           |

|                            |                    | B12[1]             | I/O  | P0[4] — General purpose digital input/output pin.                                                                                                                                          |     |                                                                                                                                                                                           |

| LCDVD[0]/RD2/<br>CAP2[0]   |                    |                    | I/O  | <b>I2SRX_CLK</b> — I <sup>2</sup> S Receive clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the I <sup>2</sup> S-bus specification. [17]     |     |                                                                                                                                                                                           |

|                            |                    |                    | 0    | <b>LCDVD[0]</b> — LCD data.[17]                                                                                                                                                            |     |                                                                                                                                                                                           |

|                            |                    |                    | 1    | RD2 — CAN2 receiver input.                                                                                                                                                                 |     |                                                                                                                                                                                           |

|                            |                    |                    | I    | CAP2[0] — Capture input for Timer 2, channel 0.                                                                                                                                            |     |                                                                                                                                                                                           |

| P0[5]/I2SRX_WS/            | 166 <sup>[1]</sup> | C12[1]             | I/O  | P0[5] — General purpose digital input/output pin.                                                                                                                                          |     |                                                                                                                                                                                           |

| LCDVD[1]/TD2/<br>CAP2[1]   |                    |                    |      |                                                                                                                                                                                            | I/O | <b>I2SRX_WS</b> — I <sup>2</sup> S Receive word select. It is driven by the master and received by the slave. Corresponds to the signal WS in the I <sup>2</sup> S-bus specification.[17] |

|                            |                    |                    | 0    | <b>LCDVD[1]</b> — LCD data.[17]                                                                                                                                                            |     |                                                                                                                                                                                           |

|                            |                    |                    | 0    | TD2 — CAN2 transmitter output.                                                                                                                                                             |     |                                                                                                                                                                                           |

|                            |                    |                    | I    | CAP2[1] — Capture input for Timer 2, channel 1.                                                                                                                                            |     |                                                                                                                                                                                           |

| P0[6]/I2SRX_SDA/           | 164 <u>[1]</u>     | D13[1]             | I/O  | P0[6] — General purpose digital input/output pin.                                                                                                                                          |     |                                                                                                                                                                                           |

| LCDVD[8]/<br>SSEL1/MAT2[0] |                    |                    | I/O  | <b>I2SRX_SDA</b> — I <sup>2</sup> S Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $I^2S$ -bus specification.[17]             |     |                                                                                                                                                                                           |

|                            |                    |                    | 0    | <b>LCDVD[8]</b> — LCD data.[17]                                                                                                                                                            |     |                                                                                                                                                                                           |

|                            |                    |                    | I/O  | SSEL1 — Slave Select for SSP1.                                                                                                                                                             |     |                                                                                                                                                                                           |

|                            |                    |                    | 0    | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                             |     |                                                                                                                                                                                           |

Table 4.

Pin description ...continued

| Symbol          | Pin | Ball | Туре | Description                                                                                                                                                                                |

|-----------------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2[0] to P2[31] |     |      | I/O  | <b>Port 2:</b> Port 2 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 2 pins depends upon the pin function selected via the pin connect block. |

Table 4. Pin description ... continued

| Symbol                     | Pin                | Ball               | Type          | Description                                                                                                    |  |  |  |  |   |                                               |

|----------------------------|--------------------|--------------------|---------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|---|-----------------------------------------------|

| P2[0]/PWM1[1]/             | 154 <sup>[1]</sup> | B17[1]             | I/O           | P2[0] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| TXD1/TRACECLK/<br>LCDPWR   |                    |                    | 0             | PWM1[1] — Pulse Width Modulator 1, channel 1 output.                                                           |  |  |  |  |   |                                               |

| LODI WIX                   |                    |                    | 0             | TXD1 — Transmitter output for UART1.                                                                           |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | TRACECLK — Trace clock.[19]                                                                                    |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | LCDPWR — LCD panel power enable.[19]                                                                           |  |  |  |  |   |                                               |

| P2[1]/PWM1[2]/             | 152 <sup>[1]</sup> | E14[1]             | I/O           | P2[1] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| RXD1/PIPESTAT0/<br>LCDLE   |                    |                    | 0             | PWM1[2] — Pulse Width Modulator 1, channel 2 output.                                                           |  |  |  |  |   |                                               |

| LODEL                      |                    |                    | I             | RXD1 — Receiver input for UART1.                                                                               |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | PIPESTAT0 — Pipeline status, bit 0.[19]                                                                        |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | LCDLE — Line end signal.[19]                                                                                   |  |  |  |  |   |                                               |

| P2[2]/PWM1[3]/             | 150 <u>[1]</u>     | D15[1]             | I/O           | P2[2] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| CTS1/PIPESTAT1/            |                    |                    | 0             | PWM1[3] — Pulse Width Modulator 1, channel 3 output.                                                           |  |  |  |  |   |                                               |

| LCDDCLK                    |                    |                    | I             | CTS1 — Clear to Send input for UART1.                                                                          |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | PIPESTAT1 — Pipeline status, bit 1.[19]                                                                        |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | LCDDCLK — LCD panel clock.[19]                                                                                 |  |  |  |  |   |                                               |

| P2[3]/PWM1[4]/             | 144 <sup>[1]</sup> | E16[1]             | I/O           | P2[3] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| DCD1/PIPESTAT2/            |                    |                    | 0             | PWM1[4] — Pulse Width Modulator 1, channel 4 output.                                                           |  |  |  |  |   |                                               |

| LCDFP                      |                    |                    | I             | DCD1 — Data Carrier Detect input for UART1.                                                                    |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | PIPESTAT2 — Pipeline status, bit 2.[19]                                                                        |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | <b>LCDFP</b> — Frame pulse (STN). Vertical synchronization pulse (TFT).[19]                                    |  |  |  |  |   |                                               |

| P2[4]/PWM1[5]/             | 142 <sup>[1]</sup> | 142[1] D17[1]      |               | P2[4] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| DSR1/                      |                    |                    | 0             | PWM1[5] — Pulse Width Modulator 1, channel 5 output.                                                           |  |  |  |  |   |                                               |

| TRACESYNC/<br>LCDENAB/LCDM |                    |                    |               |                                                                                                                |  |  |  |  | I | <b>DSR1</b> — Data Set Ready input for UART1. |

|                            |                    |                    | 0             | TRACESYNC — Trace Synchronization.[19]                                                                         |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | LCDENAB/LCDM — STN AC bias drive or TFT data enable output.[19]                                                |  |  |  |  |   |                                               |

| P2[5]/PWM1[6]/             | 140 <sup>[1]</sup> | F16 <sup>[1]</sup> | I/O           | P2[5] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| DTR1/                      |                    |                    | 0             | PWM1[6] — Pulse Width Modulator 1, channel 6 output.                                                           |  |  |  |  |   |                                               |

| TRACEPKT0/<br>LCDLP        |                    |                    | 0             | DTR1 — Data Terminal Ready output for UART1.                                                                   |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | TRACEPKT0 — Trace Packet, bit 0.[19]                                                                           |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | <b>LCDLP</b> — Line synchronization pulse (STN). Horizontal synchronization pulse (TFT). $\underline{^{[19]}}$ |  |  |  |  |   |                                               |

| P2[6]/PCAP1[0]/            | 138 <u>[1]</u>     | E17[1]             | I/O           | P2[6] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| RI1/                       |                    |                    | I             | PCAP1[0] — Capture input for PWM1, channel 0.                                                                  |  |  |  |  |   |                                               |

| TRACEPKT1/<br>LCDVD[0]/    |                    |                    | I             | RI1 — Ring Indicator input for UART1.                                                                          |  |  |  |  |   |                                               |

| LCDVD[4]                   |                    |                    | 0             | TRACEPKT1 — Trace Packet, bit 1.[19]                                                                           |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | LCDVD[0]/LCDVD[4] — LCD data.[19]                                                                              |  |  |  |  |   |                                               |

| P2[7]/RD2/                 | 136 <sup>[1]</sup> | G16 <sup>[1]</sup> | I/O           | P2[7] — General purpose digital input/output pin.                                                              |  |  |  |  |   |                                               |

| RTS1/                      |                    |                    | I             | RD2 — CAN2 receiver input.                                                                                     |  |  |  |  |   |                                               |

| TRACEPKT2/<br>LCDVD[1]/    |                    |                    | 0             | RTS1 — Request to Send output for UART1.                                                                       |  |  |  |  |   |                                               |

| LCDVD[1]<br>LCDVD[5]       |                    |                    | 0             | TRACEPKT2 — Trace Packet, bit 2.[19]                                                                           |  |  |  |  |   |                                               |

|                            |                    |                    | 0             | LCDVD[1]/LCDVD[5] — LCD data.[19]                                                                              |  |  |  |  |   |                                               |

|                            |                    |                    |               |                                                                                                                |  |  |  |  |   |                                               |

| PC2478                     |                    |                    | All informati | on provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserve              |  |  |  |  |   |                                               |

Table 4. Pin description ... continued

| Symbol      | Pin                | Ball               | Type | Description                                                                  |

|-------------|--------------------|--------------------|------|------------------------------------------------------------------------------|

| P4[7]/A7    | 121 <sup>[1]</sup> | L16 <sup>[1]</sup> | I/O  | P4[7] — General purpose digital input/output pin.                            |

|             |                    |                    | I/O  | A7 — External memory address line 7.                                         |

| P4[8]/A8    | 127 <u>[1]</u>     | J17[1]             | I/O  | P4[8] — General purpose digital input/output pin.                            |

|             |                    |                    | I/O  | A8 — External memory address line 8.                                         |

| P4[9]/A9    | 131 <u>[1]</u>     | H17[1]             | I/O  | P4[9] — General purpose digital input/output pin.                            |

|             |                    |                    | I/O  | A9 — External memory address line 9.                                         |

| P4[10]/A10  | 135 <u>[1]</u>     | G17[1]             | I/O  | P4[10] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A10 — External memory address line 10.                                       |

| P4[11]/A11  | 145 <u>[1]</u>     | F14[1]             | I/O  | P4[11] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A11 — External memory address line 11.                                       |

| P4[12]/A12  | 149 <sup>[1]</sup> | C16[1]             | I/O  | P4[12] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A12 — External memory address line 12.                                       |

| P4[13]/A13  | 155 <u>[1]</u>     | B16[1]             | I/O  | P4[13] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A13 — External memory address line 13.                                       |

| P4[14]/A14  | 159 <sup>[1]</sup> | B15[1]             | I/O  | P4[14] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A14 — External memory address line 14.                                       |

| P4[15]/A15  | 173 <u>[1]</u>     | A11[1]             | I/O  | P4[15] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A15 — External memory address line 15.                                       |

| P4[16]/A16  | 101 <u>[1]</u>     | U17[1]             | I/O  | P4[16] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A16 — External memory address line 16.                                       |

| P4[17]/A17  | 104 <sup>[1]</sup> | P14 <sup>[1]</sup> | I/O  | P4[17] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A17 — External memory address line 17.                                       |

| P4[18]/A18  | 105 <u>[1]</u>     | P15 <sup>[1]</sup> | I/O  | P4[18] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A18 — External memory address line 18.                                       |

| P4[19]/A19  | 111 <sup>[1]</sup> | P16 <sup>[1]</sup> | I/O  | P4[19] — General purpose digital input/output pin.                           |

|             |                    |                    | I/O  | A19 — External memory address line 19.                                       |

| P4[20]/A20/ | 109 <sup>[1]</sup> | R17[1]             | I/O  | P4[20] — General purpose digital input/output pin.                           |

| SDA2/SCK1   |                    |                    | I/O  | A20 — External memory address line 20.                                       |

|             |                    |                    | I/O  | SDA2 — I <sup>2</sup> C2 data input/output (this is not an open-drain pin).  |

|             |                    |                    | I/O  | SCK1 — Serial Clock for SSP1.                                                |

| P4[21]/A21/ | 115 <sup>[1]</sup> | M15 <sup>[1]</sup> | I/O  | P4[21] — General purpose digital input/output pin.                           |

| SCL2/SSEL1  |                    |                    | I/O  | A21 — External memory address line 21.                                       |

|             |                    |                    | I/O  | SCL2 — I <sup>2</sup> C2 clock input/output (this is not an open-drain pin). |

|             |                    |                    | I/O  | SSEL1 — Slave Select for SSP1.                                               |

| P4[22]/A22/ | 123 <sup>[1]</sup> | K14[1]             | I/O  | P4[22] — General purpose digital input/output pin.                           |

| TXD2/MISO1  |                    |                    | I/O  | A22 — External memory address line 22.                                       |

|             |                    |                    | 0    | TXD2 — Transmitter output for UART2.                                         |

|             |                    |                    | I/O  | MISO1 — Master In Slave Out for SSP1.                                        |

## Single-chip 16-bit/32-bit microcontroller

## 7.4 Memory map

The LPC2478 memory map incorporates several distinct regions as shown in  $\underline{\text{Table 5}}$  and  $\underline{\text{Figure 4}}$ .

In addition, the CPU interrupt vectors may be remapped to allow them to reside in either flash memory (default), boot ROM, or SRAM (see <u>Section 7.27.6</u>).

Table 5. LPC2478 memory usage and details

| Address range                 | General use                            | Address range details and des    | cription              |

|-------------------------------|----------------------------------------|----------------------------------|-----------------------|

| 0x0000 0000 to                | on-chip                                | 0x0000 0000 - 0x0007 FFFF        | flash memory (512 kB) |

| 0x3FFF FFFF                   | non-volatile<br>memory and Fast<br>I/O | 0x3FFF C000 - 0x3FFF FFFF        | fast GPIO registers   |

| 0x4000 0000 to                | on-chip RAM                            | 0x4000 0000 - 0x4000 FFFF        | RAM (64 kB)           |

| 0x7FFF FFFF                   |                                        | 0x7FE0 0000 - 0x7FE0 3FFF        | Ethernet RAM (16 kB)  |

|                               |                                        | 0x7FD0 0000 - 0x7FD0 3FFF        | USB RAM (16 kB)       |

| 0x8000 0000 to                | off-chip Memory                        | four static memory banks, 16 MB  | each                  |

| 0xDFFF FFFF                   |                                        | 0x8000 0000 - 0x80FF FFFF        | static memory bank 0  |

|                               |                                        | 0x8100 0000 - 0x81FF FFFF        | static memory bank 1  |

|                               |                                        | 0x8200 0000 - 0x82FF FFFF        | static memory bank 2  |

|                               |                                        | 0x8300 0000 - 0x83FF FFFF        | static memory bank 3  |

|                               |                                        | four dynamic memory banks, 256   | 6 MB each             |

|                               |                                        | 0xA000 0000 - 0xAFFF FFFF        | dynamic memory bank 0 |

|                               |                                        | 0xB000 0000 - 0xBFFF FFFF        | dynamic memory bank 1 |

|                               |                                        | 0xC000 0000 - 0xCFFF FFFF        | dynamic memory bank 2 |

|                               |                                        | 0xD000 0000 - 0xDFFF FFFF        | dynamic memory bank 3 |

| 0xE000 0000 to<br>0xEFFF FFFF | APB peripherals                        | 36 peripheral blocks, 16 kB each |                       |

| 0xF000 0000 to<br>0xFFFF FFFF | AHB peripherals                        |                                  |                       |

### Single-chip 16-bit/32-bit microcontroller

The Ethernet block and the CPU share a dedicated AHB subsystem that is used to access the Ethernet SRAM for Ethernet data, control, and status information. All other AHB traffic in the LPC2478 takes place on a different AHB subsystem, effectively separating Ethernet activity from the rest of the system. The Ethernet DMA can also access off-chip memory via the EMC, as well as the SRAM located on another AHB. However, using memory other than the Ethernet SRAM, especially off-chip memory, will slow Ethernet access to memory and increase the loading of its AHB.

The Ethernet block interfaces between an off-chip Ethernet PHY using the Media Independent Interface (MII) or Reduced MII (RMII) protocol and the on-chip Media Independent Interface Management (MIIM) serial bus.

#### 7.11.1 Features

- Ethernet standards support:

- Supports 10 Mbit/s or 100 Mbit/s PHY devices including 10 Base-T, 100 Base-TX, 100 Base-FX, and 100 Base-T4.

- Fully compliant with IEEE standard 802.3.

- Fully compliant with 802.3x Full Duplex Flow Control and Half Duplex back pressure.

- Flexible transmit and receive frame options.

- Virtual Local Area Network (VLAN) frame support.

#### Memory management:

- Independent transmit and receive buffers memory mapped to shared SRAM.

- DMA managers with scatter/gather DMA and arrays of frame descriptors.

- Memory traffic optimized by buffering and pre-fetching.

### • Enhanced Ethernet features:

- Receive filtering.

- Multicast and broadcast frame support for both transmit and receive.

- Optional automatic Frame Check Sequence (FCS) insertion with Circular Redundancy Check (CRC) for transmit.

- Selectable automatic transmit frame padding.

- Over-length frame support for both transmit and receive allows any length frames.

- Promiscuous receive mode.

- Automatic collision back-off and frame retransmission.

- Includes power management by clock switching.

- Wake-on-LAN power management support allows system wake-up: using the receive filters or a magic frame detection filter.

#### Physical interface:

- Attachment of external PHY chip through standard MII or RMII interface.

- PHY register access is available via the MIIM interface.

### Single-chip 16-bit/32-bit microcontroller

#### 7.12 USB interface

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot plugging and dynamic configuration of the devices. All transactions are initiated by the host controller.

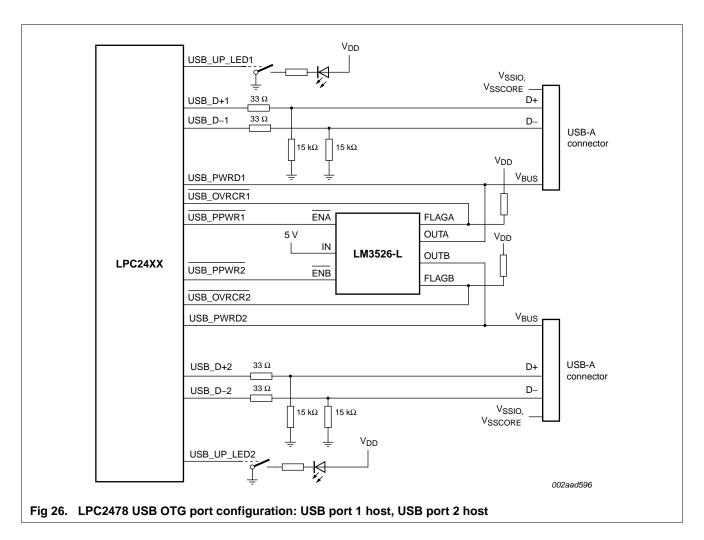

The LPC2478 USB interface includes a device, host, and OTG controller. Details on typical USB interfacing solutions can be found in <u>Section 14.2 "Suggested USB interface solutions" on page 77</u>

#### 7.12.1 USB device controller

The device controller enables 12 Mbit/s data exchange with a USB host controller. It consists of a register interface, serial interface engine, endpoint buffer memory, and a DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled. When enabled, the DMA controller transfers data between the endpoint buffer and the USB RAM.

#### 7.12.1.1 Features

- Fully compliant with *USB 2.0 Specification* (full speed).

- Supports 32 physical (16 logical) endpoints with a 4 kB endpoint buffer RAM.

- Supports Control, Bulk, Interrupt and Isochronous endpoints.

- · Scalable realization of endpoints at run time.

- Endpoint Maximum packet size selection (up to USB maximum specification) by software at run time.

- Supports SoftConnect and GoodLink features.

- While USB is in the Suspend mode, the LPC2478 can enter one of the reduced power modes and wake up on USB activity.

- Supports DMA transfers with the DMA RAM of 16 kB on all non-control endpoints.

- Allows dynamic switching between CPU-controlled and DMA modes.

- Double buffer implementation for Bulk and Isochronous endpoints.

#### 7.12.2 USB host controller

The host controller enables full- and low-speed data exchange with USB devices attached to the bus. It consists of register interface, serial interface engine and DMA controller. The register interface complies with the Open Host Controller Interface (OHCI) specification.

#### **7.12.2.1 Features**

- OHCI compliant

- Two downstream ports

- Supports per-port power switching

### Single-chip 16-bit/32-bit microcontroller

#### 7.12.3 USB OTG controller

USB OTG is a supplement to the *USB 2.0 Specification* that augments the capability of existing mobile devices and USB peripherals by adding host functionality for connection to USB peripherals.

The OTG Controller integrates the host controller, device controller, and a master-only I<sup>2</sup>C interface to implement OTG dual-role device functionality. The dedicated I<sup>2</sup>C interface controls an external OTG transceiver.

#### 7.12.3.1 Features

- Fully compliant with On-The-Go supplement to the USB 2.0 Specification, Revision

- Hardware support for Host Negotiation Protocol (HNP).

- Includes a programmable timer required for HNP and Session Request Protocol (SRP).

- Supports any OTG transceiver compliant with the OTG Transceiver Specification (CEA-2011), Rev. 1.0.

## 7.13 CAN controller and acceptance filters

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real-time control with a very high level of security. Its domain of application ranges from high-speed networks to low cost multiplex wiring.

The CAN block is intended to support multiple CAN buses simultaneously, allowing the device to be used as a gateway, switch, or router between two of CAN buses in industrial or automotive applications.

Each CAN controller has a register structure similar to the NXP SJA1000 and the PeliCAN Library block, but the 8-bit registers of those devices have been combined in 32-bit words to allow simultaneous access in the ARM environment. The main operational difference is that the recognition of received Identifiers, known in CAN terminology as Acceptance Filtering, has been removed from the CAN controllers and centralized in a global Acceptance Filter.

## 7.13.1 Features

- Two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes 11-bit and 29-bit receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- FullCAN messages can generate interrupts.

### Single-chip 16-bit/32-bit microcontroller

#### **7.21.1 Features**

- The interface has separate input/output channels each of which can operate in master or slave mode.

- Capable of handling 8-bit, 16-bit, and 32-bit word sizes.

- Mono and stereo audio data supported.

- The sampling frequency can range from 16 kHz to 48 kHz (16, 22.05, 32, 44.1, 48) kHz.

- Configurable word select period in master mode (separately for I<sup>2</sup>S input and output).

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive.

- Generates interrupt requests when buffer levels cross a programmable boundary.

- Two DMA requests, controlled by programmable buffer levels. These are connected to the GPDMA block.

- Controls include reset, stop and mute options separately for I<sup>2</sup>S input and I<sup>2</sup>S output.

## 7.22 General purpose 32-bit timers/external event counters

The LPC2478 includes four 32-bit Timer/Counters. The Timer/Counter is designed to count cycles of the system derived clock or an externally-supplied clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. The Timer/Counter also includes four capture inputs to trap the timer value when an input signal transitions, optionally generating an interrupt.

#### 7.22.1 Features

- A 32-bit Timer/Counter with a programmable 32-bit prescaler.

- Counter or Timer operation.

- Up to four 32-bit capture channels per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event may also optionally generate an interrupt.

- Four 32-bit match registers that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

### Single-chip 16-bit/32-bit microcontroller

#### **CAUTION**

If level three Code Read Protection (CRP3) is selected, no future factory testing can be performed on the device.

#### 7.27.4 AHB

The LPC2478 implements two AHB in order to allow the Ethernet block to operate without interference caused by other system activity. The primary AHB, referred to as AHB1, includes the Vectored Interrupt Controller, GPDMA controller, USB interface, and 16 kB SRAM.

The second AHB, referred to as AHB2, includes only the Ethernet block and an associated 16 kB SRAM. In addition, a bus bridge is provided that allows the secondary AHB to be a bus master on AHB1, allowing expansion of Ethernet buffer space into off-chip memory or unused space in memory residing on AHB1.

In summary, bus masters with access to AHB1 are the ARM7 itself, the USB block, the GPDMA function, and the Ethernet block (via the bus bridge from AHB2). Bus masters with access to AHB2 are the ARM7 and the Ethernet block.

#### 7.27.5 External interrupt inputs

The LPC2478 includes up to 68 edge sensitive interrupt inputs combined with up to four level sensitive external interrupt inputs as selectable pin functions. The external interrupt inputs can optionally be used to wake up the processor from Power-down mode.

#### 7.27.6 Memory mapping control

The memory mapping control alters the mapping of the interrupt vectors that appear at the beginning at address 0x0000 0000. Vectors may be mapped to the bottom of the Boot ROM, the SRAM, or external memory. This allows code running in different memory spaces to have control of the interrupts.

## 7.28 Emulation and debugging

The LPC2478 support emulation and debugging via a JTAG serial port. A trace port allows tracing program execution. Debugging and trace functions are multiplexed only with GPIOs on P2[0] to P2[9]. This means that all communication, timer, and interface peripherals residing on other pins are available during the development and debugging phase as they are when the application is run in the embedded system itself.

## 7.28.1 EmbeddedICE

The EmbeddedICE logic provides on-chip debug support. The debugging of the target system requires a host computer running the debugger software and an EmbeddedICE protocol convertor. The EmbeddedICE protocol convertor converts the Remote Debug Protocol commands to the JTAG data needed to access the ARM7TDMI-S core present on the target system.

The ARM core has a Debug Communication Channel (DCC) function built-in. The DCC allows a program running on the target to communicate with the host debugger or another separate host without stopping the program flow or even entering the debug state. The

### Single-chip 16-bit/32-bit microcontroller

## 9. Thermal characteristics

The average chip junction temperature,  $T_j$  (°C), can be calculated using the following equation:

$$T_j = T_{amb} + (P_D \times R_{th(j-a)}) \tag{1}$$

- T<sub>amb</sub> = ambient temperature (°C),

- R<sub>th(j-a)</sub> = the package junction-to-ambient thermal resistance (°C/W)

- P<sub>D</sub> = sum of internal and I/O power dissipation

The internal power dissipation is the product of  $I_{DD}$  and  $V_{DD}$ . The I/O power dissipation of the I/O pins is often small and many times can be negligible. However it can be significant in some applications.

Table 7. Thermal characteristics

$V_{DD}$  = 3.0 V to 3.6 V;  $T_{amb}$  = -40 °C to +85 °C unless otherwise specified;

| Symbol              | Parameter                    | Conditions | Min | Тур | Max | Unit |

|---------------------|------------------------------|------------|-----|-----|-----|------|

| T <sub>j(max)</sub> | maximum junction temperature |            | -   | -   | 125 | °C   |

Table 8. Thermal resistance value (C/W): ±15 %

$V_{DD}$  = 3.0 V to 3.6 V;  $T_{amb}$  = -40 °C to +85 °C unless otherwise specified;

| LQFP208                               |              | TFBGA208                         |              |  |  |

|---------------------------------------|--------------|----------------------------------|--------------|--|--|

| θја                                   |              | θја                              |              |  |  |

| JEDEC (4.5 in × 4 in)                 |              | JEDEC (4.5 in × 4 in)            |              |  |  |

| 0 m/s                                 | 27.4         | 0 m/s                            | 41           |  |  |

| 1 m/s                                 | 25.7         | 1 m/s                            | 35           |  |  |

| 2.5 m/s                               | 24.4         | 2.5 m/s                          | 31           |  |  |

|                                       |              | 8-layer (4.5 in × 3 in)          |              |  |  |

| Single-layer (4.5 in × 3 in)          |              | 8-layer (4.5 in × 3 in)          |              |  |  |

| Single-layer (4.5 in × 3 in)<br>0 m/s | 35.4         | 8-layer (4.5 in × 3 in)<br>0 m/s | 34.9         |  |  |

|                                       | 35.4<br>31.2 |                                  | 34.9<br>30.9 |  |  |

| 0 m/s                                 |              | 0 m/s                            |              |  |  |

| 0 m/s<br>1 m/s                        | 31.2         | 0 m/s<br>1 m/s                   | 30.9         |  |  |

## Single-chip 16-bit/32-bit microcontroller

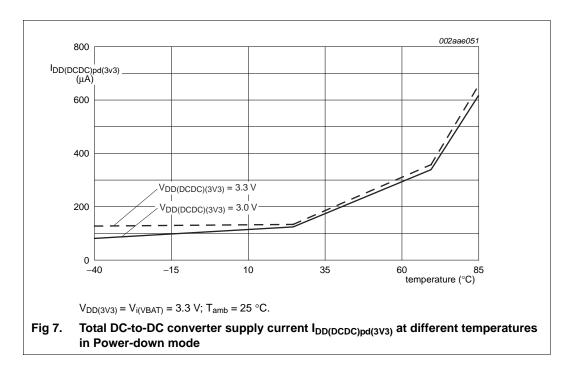

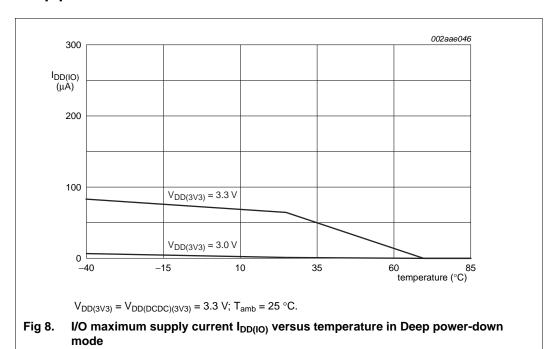

## 10.2 Deep power-down mode

LPC2478

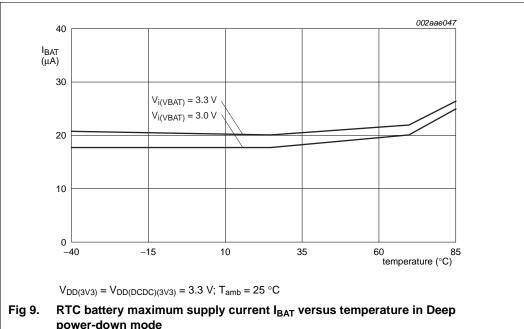

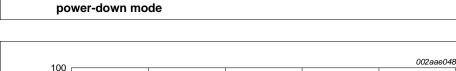

Fig 10. Total DC-to-DC converter maximum supply current  $I_{DD(DCDC)dpd(3V3)}$  versus temperature in Deep power-down mode

## Single-chip 16-bit/32-bit microcontroller

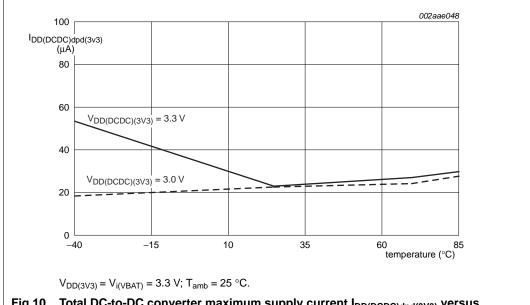

# 11. Dynamic characteristics

Table 10. Dynamic characteristics

$T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  for commercial applications;  $V_{DD(3V3)}$  over specified ranges.[1]

| Symbol                      | Parameter            | Conditions                                                                       | Min                       | Typ[2] | Max  | Unit |

|-----------------------------|----------------------|----------------------------------------------------------------------------------|---------------------------|--------|------|------|

| External cloci              | K                    |                                                                                  |                           |        |      |      |

| f <sub>osc</sub>            | oscillator frequency |                                                                                  | 1                         | -      | 25   | MHz  |

| T <sub>cy(clk)</sub>        | clock cycle time     |                                                                                  | 40                        | -      | 1000 | ns   |

| t <sub>CHCX</sub>           | clock HIGH time      |                                                                                  | $T_{cy(clk)} \times 0.4$  | -      | -    | ns   |

| t <sub>CLCX</sub>           | clock LOW time       |                                                                                  | $T_{cy(clk)} \times 0.4$  | -      | -    | ns   |

| t <sub>CLCH</sub>           | clock rise time      |                                                                                  | -                         | -      | 5    | ns   |

| t <sub>CHCL</sub>           | clock fall time      |                                                                                  | -                         | -      | 5    | ns   |

| I <sup>2</sup> C-bus pins ( | P0[27] and P0[28])   |                                                                                  |                           |        |      |      |

| t <sub>f(O)</sub>           | output fall time     | V <sub>IH</sub> to V <sub>IL</sub>                                               | $20 + 0.1 \times C_b$ [3] | -      | -    | ns   |

| SSP interface               |                      |                                                                                  |                           |        |      |      |

| $t_{su(SPI\_MISO)}$         | SPI_MISO set-up time | T <sub>amb</sub> = 25 °C;<br>measured in<br>SPI Master<br>mode; see<br>Figure 17 | -                         | 11     | -    | ns   |

- [1] Parameters are valid over operating temperature range unless otherwise specified.

- [2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

- [3] Bus capacitance  $C_b$  in pF, from 10 pF to 400 pF.

#### Single-chip 16-bit/32-bit microcontroller

## 14.3 Crystal oscillator XTAL input and component selection

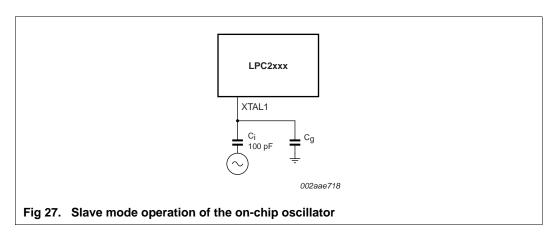

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100$  pF. To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i$  / ( $C_i + C_g$ ). In slave mode, a minimum of 200 mV (RMS) is needed.

### Single-chip 16-bit/32-bit microcontroller

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (<u>Figure 27</u>), with an amplitude between 200 mV (RMS) and 1000 mV (RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTAL2 pin in this configuration can be left unconnected.

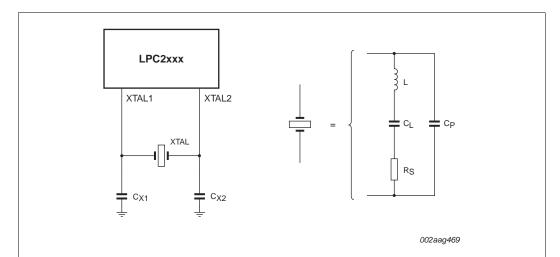

External components and models used in oscillation mode are shown in <u>Figure 28</u> and in <u>Table 23</u> and <u>Table 24</u>. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (the fundamental frequency is represented by L,  $C_L$  and  $R_S$ ). Capacitance  $C_P$  in <u>Figure 28</u> represents the parallel package capacitance and should not be larger than 7 pF. Parameters  $F_{OSC}$ ,  $C_L$ ,  $R_S$  and  $C_P$  are supplied by the crystal manufacturer.

Fig 28. Oscillator modes and models: oscillation mode of operation and external crystal model used for  $C_{X1}/C_{X2}$  evaluation

Table 23. Recommended values for C<sub>X1</sub>/C<sub>X2</sub> in oscillation mode (crystal and external components parameters): low frequency mode

| Crystal load capacitance C <sub>L</sub> | Maximum crystal series resistance R <sub>S</sub>                                                | External load capacitors C <sub>X1</sub> /C <sub>X2</sub> |

|-----------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 10 pF                                   | < 300 Ω                                                                                         | 18 pF, 18 pF                                              |

| 20 pF                                   | < 300 Ω                                                                                         | 39 pF, 39 pF                                              |

| 30 pF                                   | < 300 Ω                                                                                         | 57 pF, 57 pF                                              |

| 10 pF                                   | < 300 Ω                                                                                         | 18 pF, 18 pF                                              |

| 20 pF                                   | < 200 Ω                                                                                         | 39 pF, 39 pF                                              |

| 30 pF                                   | < 100 Ω                                                                                         | 57 pF, 57 pF                                              |

| 10 pF                                   | < 160 Ω                                                                                         | 18 pF, 18 pF                                              |

| 20 pF                                   | < 60 Ω                                                                                          | 39 pF, 39 pF                                              |

| 10 pF                                   | < 80 Ω                                                                                          | 18 pF, 18 pF                                              |

|                                         | 10 pF<br>20 pF<br>30 pF<br>10 pF<br>20 pF<br>30 pF<br>10 pF<br>20 pF<br>30 pF<br>10 pF<br>20 pF | $\begin{array}{llllllllllllllllllllllllllllllllllll$      |

## Single-chip 16-bit/32-bit microcontroller

39 pF, 39 pF

| components parameters): nign frequency mode |                                         |                                                  |                                                            |  |

|---------------------------------------------|-----------------------------------------|--------------------------------------------------|------------------------------------------------------------|--|

| Fundamental oscillation frequency Fosc      | Crystal load capacitance C <sub>L</sub> | Maximum crystal series resistance R <sub>S</sub> | External load capacitors C <sub>X1</sub> , C <sub>X2</sub> |  |

| 15 MHz to 20 MHz                            | 10 pF                                   | < 180 Ω                                          | 18 pF, 18 pF                                               |  |

|                                             | 20 pF                                   | < 100 Ω                                          | 39 pF, 39 pF                                               |  |

| 20 MHz to 25 MHz                            | 10 pF                                   | < 160 Ω                                          | 18 pF, 18 pF                                               |  |

< 80  $\Omega$

Table 24. Recommended values for  $C_{X1}/C_{X2}$  in oscillation mode (crystal and external components parameters): high frequency mode

## 14.4 RTC 32 kHz oscillator component selection

20 pF

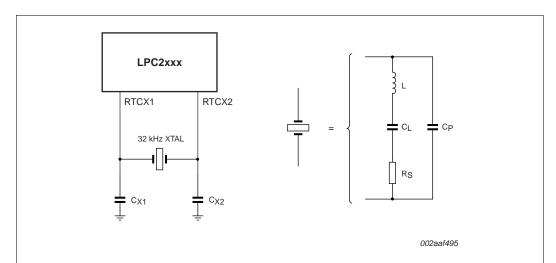

Fig 29. RTC oscillator modes and models: oscillation mode of operation and external crystal model used for  $C_{X1}/C_{X2}$  evaluation

The RTC external oscillator circuit is shown in <u>Figure 29</u>. Since the feedback resistance is integrated on chip, only a crystal, the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally to the microcontroller.

Table 25. Recommended values for the RTC external 32 kHz oscillator C<sub>X1</sub>/C<sub>X2</sub> components

| Crystal load capacitance C <sub>L</sub> | Maximum crystal series resistance R <sub>S</sub> | External load capacitors C <sub>X1</sub> /C <sub>X2</sub> |

|-----------------------------------------|--------------------------------------------------|-----------------------------------------------------------|

| 11 pF                                   | < 100 kΩ                                         | 18 pF, 18 pF                                              |

| 13 pF                                   | < 100 kΩ                                         | 22 pF, 22 pF                                              |

| 15 pF                                   | < 100 kΩ                                         | 27 pF, 27 pF                                              |

## Single-chip 16-bit/32-bit microcontroller

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

#### 18.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

## 19. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>