#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | R32C/100                                                                     |

| Core Size                  | 16/32-Bit                                                                    |

| Speed                      | 50MHz                                                                        |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IEBus, UART/USART                                 |

| Peripherals                | DMA, LVD, PWM, WDT                                                           |

| Number of I/O              | 82                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 8K x 8                                                                       |

| RAM Size                   | 40K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-LFQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f64114dfb |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.1.2 Performance Overview

Tables 1.1 to 1.4 show the performance overview of the R32C/111 Group.

#### Table 1.1 Performance Overview for the 100-pin Package (1/2)

| Unit                      | Function                   | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU<br>Memory             | Central<br>processing unit | <ul> <li>R32C/100 Series CPU Core</li> <li>Basic instructions: 108</li> <li>Minimum instruction execution time: 20 ns (f(CPU) = 50 MHz)</li> <li>Multiplier: 32-bit × 32-bit → 64-bit</li> <li>Multiply-accumulate unit: 32-bit × 32-bit + 64-bit → 64-bit</li> <li>IEEE-754 compatible FPU: Single precision</li> <li>32-bit barrel shifter</li> <li>Operating mode: Single-chip mode, memory expansion mode, microprocessor mode (optional <sup>(1)</sup>)</li> <li>Flash memory: 256 to 512 Kbytes</li> <li>RAM: 32 to 63 Kbytes</li> <li>Data flash: 4 Kbytes × 2 blocks</li> <li>Refer to Table 1.5 for memory size of each product group</li> </ul> |

| Valtaga                   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Voltage<br>Detector       | Low voltage<br>detector    | Optional <sup>(1)</sup><br>Low voltage detection interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Clock                     | Clock generator            | <ul> <li>4 circuits (main clock, sub clock, PLL, on-chip oscillator)</li> <li>Oscillation stop detector: Main clock oscillator stop/restart detection</li> <li>Frequency divide circuit: Divide-by-2 to divide-by-24 selectable</li> <li>Low power modes: Wait mode, stop mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |

| External Bus<br>Expansion | Bus and memory expansion   | Address space: 4 Gbytes (of which up to 64 Mbytes is user accessible)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                           | o,puncion                  | <ul> <li>External bus Interface: Support for wait-state insertion, 4 chip select outputs, 3V/5V interface</li> <li>Bus format: Separate bus/Multiplexed bus selectable, data bus width selectable (8/16 bits)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupts                |                            | Interrupt vectors: 261<br>External interrupt inputs: NMI, INT × 6, key input × 4<br>Interrupt priority levels: 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Watchdog Tim              | er                         | 15 bits × 1 (selectable input frequency from prescaler output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DMA                       | DMAC                       | <ul> <li>4 channels</li> <li>Cycle-steal transfer mode</li> <li>Request sources: 51</li> <li>2 transfer modes: Single transfer, repeat transfer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                           | DMAC II                    | <ul> <li>Triggered by an interrupt request of any peripheral</li> <li>3 characteristic transfer functions: Immediate data transfer, calculation result transfer, chain transfer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I/O Ports                 | Programmable<br>I/O ports  | <ul> <li>2 input-only ports</li> <li>82 CMOS I/O ports</li> <li>2 N-channel open drain ports</li> <li>A pull-up resistor is selectable for every 4 input ports</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Note:

1. Contact a Renesas Electronics sales office to use the optional features.

| Unit        | Function                   | Explanation                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CPU         | Central<br>processing unit | <ul> <li>R32C/100 Series CPU Core</li> <li>Basic instructions: 108</li> <li>Minimum instruction execution time: 20 ns (f(CPU) = 50 MHz)</li> <li>Multiplier: 32-bit × 32-bit → 64-bit</li> <li>Multiply-accumulate unit: 32-bit × 32-bit + 64-bit → 64-bit</li> <li>IEEE-754 compatible FPU: Single precision</li> <li>32-bit barrel shifter</li> <li>Operating mode: Single-chip mode</li> </ul> |  |  |

| Memory      |                            | Flash memory: 128/256 Kbytes<br>RAM: 32 Kbytes<br>Data flash: 4 Kbytes × 2 blocks<br>Refer to Table 1.5 for memory size of each product group                                                                                                                                                                                                                                                     |  |  |

| Voltage     | Low voltage                | Optional <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Detector    | detector                   | Low voltage detection interrupt                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Clock       | Clock generator            | <ul> <li>4 circuits (main clock, sub clock, PLL, on-chip oscillator)</li> <li>Oscillation stop detector: Main clock oscillator stop/restart detection</li> <li>Frequency divide circuit: Divide-by-2 to divide-by-24 selectable</li> <li>Low power modes: Wait mode, stop mode</li> </ul>                                                                                                         |  |  |

| Interrupts  |                            | Interrupt vectors: 261<br>External interrupt inputs: $\overline{\text{NMI}}$ , $\overline{\text{INT}} \times 6$ , key input × 4<br>Interrupt priority levels: 7                                                                                                                                                                                                                                   |  |  |

| Watchdog Ti | mer                        | 15 bits × 1 (selectable input frequency from prescaler output)                                                                                                                                                                                                                                                                                                                                    |  |  |

| DMA         | DMAC                       | <ul> <li>4 channels</li> <li>Cycle-steal transfer mode</li> <li>Request sources: 45</li> <li>2 transfer modes: Single transfer, repeat transfer</li> </ul>                                                                                                                                                                                                                                        |  |  |

|             | DMAC II                    | <ul> <li>Triggered by an interrupt request of any peripheral</li> <li>3 characteristic transfer functions: Immediate data transfer, calculation result transfer, chain transfer</li> </ul>                                                                                                                                                                                                        |  |  |

| I/O Ports   | Programmable<br>I/O ports  | <ul> <li>1 input-only port</li> <li>49 CMOS I/O ports</li> <li>2 N-channel open drain ports</li> <li>A pull-up resistor is selectable for every 4 input ports</li> </ul>                                                                                                                                                                                                                          |  |  |

| Table 1.3 | Performance Overview for the 64-pin Package (1/2) |

|-----------|---------------------------------------------------|

|-----------|---------------------------------------------------|

Note:

1. Contact a Renesas Electronics sales office to use the optional features.

| Pin No. | Control Pin | Port | Interrupt Pin | Timer Pin       | UART Pin                      | Intelligent I/O Pin             | Analog Pin |

|---------|-------------|------|---------------|-----------------|-------------------------------|---------------------------------|------------|

| 1       | VDC1        |      |               |                 |                               |                                 |            |

| 2       | NSD         |      |               |                 |                               |                                 |            |

| 3       | CNVSS       |      |               |                 |                               |                                 |            |

| 4       | XCIN        | P8_7 |               |                 |                               |                                 |            |

| 5       | XCOUT       | P8_6 |               |                 |                               |                                 |            |

| 6       | RESET       |      |               |                 |                               |                                 |            |

| 7       | XOUT        |      |               |                 |                               |                                 |            |

| 8       | VSS         |      |               |                 |                               |                                 |            |

| 9       | XIN         |      |               |                 |                               |                                 |            |

| 10      | VCC1        |      |               |                 |                               |                                 |            |

| 11      |             | P8_5 | NMI           |                 |                               |                                 |            |

| 12      |             | P8_4 | INT2          |                 |                               |                                 |            |

| 13      |             | P8_3 | INT1          |                 |                               |                                 |            |

| 14      |             | P8_2 | INT0          |                 |                               |                                 |            |

| 15      |             | P8_1 |               | TA4IN/Ū         | CTS5/RTS5/SS5                 | IIO1_5/UD0B/UD1B                |            |

| 16      |             | P8_0 |               | TA4OUT/U        | RXD5/SCL5/STXD5               | UD0A/UD1A                       |            |

| 17      |             | P7_7 |               | TA3IN           | CLK5                          | IIO1_4/UD0B/UD1B                |            |

| 18      |             | P7_6 |               | TA3OUT          | TXD5/SDA5/SRXD5/<br>CTS8/RTS8 | IIO1_3/UD0A/UD1A                |            |

| 19      |             | P7_5 |               | TA2IN/W         | RXD8                          | IIO1_2                          |            |

| 20      |             | P7_4 |               | TA2OUT/W        | CLK8                          | IIO1_1                          |            |

| 21      |             | P7_3 |               | TA1IN/V         | CTS2/RTS2/SS2/TXD8            | IIO1_0                          |            |

| 22      |             | P7_2 |               | TA1OUT/V        | CLK2                          |                                 |            |

| 23      |             | P7_1 |               | TA0IN/<br>TB5IN | RXD2/SCL2/STXD2               | IIO1_7/OUTC2_2/<br>ISRXD2/IEIN  |            |

| 24      |             | P7_0 |               | TA0OUT          | TXD2/SDA2/SRXD2               | IIO1_6/OUTC2_0/<br>ISTXD2/IEOUT |            |

| 25      |             | P6_7 |               |                 | TXD1/SDA1/SRXD1               |                                 |            |

| 26      |             | P6_6 |               |                 | RXD1/SCL1/STXD1               |                                 |            |

| 27      |             | P6_5 |               |                 | CLK1                          |                                 |            |

| 28      |             | P6_4 |               |                 | CTS1/RTS1/SS1                 | OUTC2_1/ISCLK2                  |            |

| 29      |             | P3_3 |               | TA1IN/V         | CTS3/RTS3/SS3                 |                                 |            |

| 30      |             | P3_2 |               | TA1OUT/V        | TXD3/SDA3/SRXD3               |                                 |            |

| 31      |             | P3_1 |               | TA3OUT          | RXD3/SCL3/STXD3               | UD0B/UD1B                       | 1          |

| 32      |             | P3_0 |               | TA0OUT          | CLK3                          | UD0A/UD1A                       | 1          |

| 33      |             | P6_3 |               |                 | TXD0/SDA0/SRXD0               |                                 | 1          |

| 34      |             | P6_2 |               | TB2IN           | RXD0/SCL0/STXD0               |                                 | 1          |

| 35      |             | P6_1 |               | TB1IN           | CLK0                          |                                 |            |

| 36      |             | P6_0 |               | TB0IN           | CTS0/RTS0/SS0                 |                                 |            |

| 37      |             | P2_7 |               |                 |                               | IIO0_7                          | AN2_7      |

| 38      |             | P2_6 |               |                 |                               | IIO0_6                          | AN2_6      |

| 39      |             | P2_5 | 1             |                 |                               | IIO0_5                          | AN2_5      |

| 40      |             | P2_4 |               |                 |                               | IIO0_4                          | AN2_4      |

RENESAS

Table 1.9

Pin Characteristics for the 64-pin Package (1/2)

#### **1.5 Pin Definitions and Functions**

Tables 1.11 to 1.17 show the pin definitions and functions.

|                                                |                    | Functio | is for the      | Tuu-pin Fackage (1/4)                                                                                           |

|------------------------------------------------|--------------------|---------|-----------------|-----------------------------------------------------------------------------------------------------------------|

| Function                                       | Symbol             | I/O     | Power<br>Supply | Description                                                                                                     |

| Power supply                                   | VCC1, VCC2,<br>VSS | I       | _               | Applicable as follows: VCC1 and VCC2 = 3.0 to 5.5 V (VCC1 $\ge$ VCC2), VSS = 0 V                                |

| Connecting pins<br>for decoupling<br>capacitor | VDC0, VDC1         | _       | _               | A decoupling capacitor for internal voltage should be connected between VDC0 and VDC1                           |

| Analog power<br>supply                         | AVCC, AVSS         | I       | VCC1            | Power supply for the A/D converter. AVCC and AVSS should be connected to VCC1 and VSS, respectively             |

| Reset input                                    | RESET              | I       | VCC1            | The MCU is reset when this pin is driven low                                                                    |

| CNVSS                                          | CNVSS              | I       | VCC1            | This pin should be connected to VSS via a resistor                                                              |

| Debug port                                     | NSD                | I/O     | VCC1            | This pin is to communicate with a debugger. It should be connected to VCC1 via a resistor of 1 to 4.7 $k\Omega$ |

| Main clock input                               | XIN                | I       | VCC1            | Input/output for the main clock oscillator. A crystal, or a ceramic resonator should be connected               |

| Main clock output                              | XOUT               | 0       | VCC1            | between pins XIN and XOUT. An external clock<br>should be input at the XIN while leaving the XOUT<br>open       |

| Sub clock input                                | XCIN               | I       | VCC1            | Input/output for the sub clock oscillator. A crystal oscillator should be connected between pins XCIN           |

| Sub clock output                               | XCOUT              | 0       | VCC1            | and XCOUT. An external clock should be input at the XCIN while leaving the XCOUT open                           |

| BCLK output                                    | BCLK               | 0       | VCC2            | BCLK output                                                                                                     |

| Clock output                                   | CLKOUT             | 0       | VCC2            | Output of the clock with the same frequency as low speed clocks, f8, or f32                                     |

| External interrupt input                       | INTO to INT5       | I       | VCC1<br>VCC2    | Input for external interrupts                                                                                   |

| NMI input                                      | P8_5/NMI           | I       | VCC1            | Input for NMI                                                                                                   |

| Key input interrupt                            | KIO to KI3         | I       | VCC1            | Input for the key input interrupt                                                                               |

| Bus control pins                               | D0 to D7           | I/O     | VCC2            | Input/output of data (D0 to D7) while accessing an external memory space with a separate bus                    |

|                                                | D8 to D15          | I/O     | VCC2            | Input/output of data (D8 to D15) while accessing<br>an external memory space with 16-bit separate<br>bus        |

|                                                | A0 to A23          | 0       | VCC2            | Output of address bits A0 to A23                                                                                |

#### Table 1.11 Pin Definitions and Functions for the 100-pin Package (1/4)

| Function                                       | Symbol                                                                                                                                                        | I/O | Description                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply                                   | VCC1, VSS                                                                                                                                                     | I   | Applicable as follows: VCC1 = 3.0 to 5.5 V, VSS = 0 V                                                                                                                                                                                                                                                                                              |

| Connecting pins<br>for decoupling<br>capacitor | VDC0, VDC1                                                                                                                                                    | _   | A decoupling capacitor for internal voltage should be<br>connected between VDC0 and VDC1                                                                                                                                                                                                                                                           |

| Analog power<br>supply                         | AVCC, AVSS                                                                                                                                                    | I   | Power supply for the A/D converter. AVCC and AVSS should be connected to VCC and VSS, respectively                                                                                                                                                                                                                                                 |

| Reset input                                    | RESET                                                                                                                                                         |     | The MCU is reset when this pin is driven low                                                                                                                                                                                                                                                                                                       |

| CNVSS                                          | CNVSS                                                                                                                                                         | I   | This pin should be connected to VSS via a resistor                                                                                                                                                                                                                                                                                                 |

| Debug port                                     | NSD                                                                                                                                                           | I/O | This pin is to communicate with a debugger. It should be connected to VCC1 via a resistor of 1 to 4.7 $k\Omega$                                                                                                                                                                                                                                    |

| Main clock input                               | XIN                                                                                                                                                           | I   | Input/output for the main clock oscillator. A crystal, or a ceramic resonator should be connected between pins XIN                                                                                                                                                                                                                                 |

| Main clock output                              | XOUT                                                                                                                                                          | 0   | and XOUT. An external clock should be input at the XIN while leaving the XOUT open                                                                                                                                                                                                                                                                 |

| Sub clock input                                | XCIN                                                                                                                                                          | Ι   | Input/output for the sub clock oscillator. A crystal oscillator should be connected between pins XCIN and XCOUT. An                                                                                                                                                                                                                                |

| Sub clock output                               | XCOUT                                                                                                                                                         | 0   | external clock should be input at the XCIN while leaving the XCOUT open                                                                                                                                                                                                                                                                            |

| External interrupt input                       | INTO to INT5                                                                                                                                                  | I   | Input for external interrupts                                                                                                                                                                                                                                                                                                                      |

| NMI input                                      | P8_5/NMI                                                                                                                                                      | I   | Input for NMI                                                                                                                                                                                                                                                                                                                                      |

| Key input interrupt                            | KIO to KI3                                                                                                                                                    | I   | Input for the key input interrupt                                                                                                                                                                                                                                                                                                                  |

| I/O port                                       | P0_0 to P0_3,<br>P1_5 to P1_7,<br>P2_0 to P2_7,<br>P3_0 to P3_3,<br>P6_0 to P6_7,<br>P7_0 to P7_7,<br>P8_0 to P8_4,<br>P8_6, P8_7,<br>P9_3,<br>P10_0 to P10_7 | I/O | I/O ports in CMOS. Each port can be programmed to input or<br>output under the control of the direction register.<br>Pull-up resistors are selected for the following 4-pin units:<br>Pi_0 to Pi_3 and Pi_4 to Pi_7 (i = 0 to 3, 6 to 10); however,<br>they are enabled only for the input pins.<br>P7_0 and P7_1 outputs are N-channel open drain |

| Timer A                                        | TA0OUT to<br>TA4OUT                                                                                                                                           | I/O | Timers A0 to A4 input/output.<br>TA0OUT output assigned for port P7_0 is N-channel open<br>drain                                                                                                                                                                                                                                                   |

|                                                | TA0IN to TA4IN                                                                                                                                                |     | Timers A0 to A4 input                                                                                                                                                                                                                                                                                                                              |

| Timer B                                        | TB0IN to<br>TB3IN, TB5IN                                                                                                                                      | I   | Timers B0 to B3, and B5 input                                                                                                                                                                                                                                                                                                                      |

| Three-phase<br>motor control<br>timer output   | U, Ū, V, V, W, W                                                                                                                                              | 0   | Three-phase motor control timer output                                                                                                                                                                                                                                                                                                             |

| Table 1.15 | Pin Definitions and Functions for 64-pin Package (1/3) |

|------------|--------------------------------------------------------|

|            |                                                        |

### 2.1 General Purpose Registers

#### 2.1.1 Data Registers (R2R0, R3R1, R6R4, and R7R5)

These 32-bit registers are primarily used for transfers and arithmetic/logic operations. Each of the registers can be divided into upper and lower 16-bit registers, e.g. R2R0 can be divided into R2 and R0, R3R1 can be divided into R3 and R1, etc.

Moreover, data registers R2R0 and R3R1 can be divided into four 8-bit data registers: upper (R2H and R3H), mid-upper (R2L and R3L), mid-lower (R0H and R1H), and lower (R0L and R1L).

#### 2.1.2 Address Registers (A0, A1, A2, and A3)

These 32-bit registers have functions similar to data registers. They are also used for address register indirect addressing and address register relative addressing.

#### 2.1.3 Static Base Register (SB)

This 32-bit register is used for SB relative addressing.

#### 2.1.4 Frame Base Register (FB)

This 32-bit register is used for FB relative addressing.

#### 2.1.5 **Program Counter (PC)**

This 32-bit counter indicates the address of the instruction to be executed next.

#### 2.1.6 Interrupt Vector Table Base Register (INTB)

This 32-bit register indicates the start address of a relocatable vector table.

### 2.1.7 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

Two types of 32-bit stack pointers (SPs) are provided: user stack pointer (USP) and interrupt stack pointer (ISP).

Use the stack pointer select flag (U flag) to select either the user stack pointer (USP) or the interrupt stack pointer (ISP). The U flag is bit 7 in the flag register (FLG). Refer to 2.1.8 "Flag Register (FLG)" for details.

To minimize the overhead of interrupt sequence due to less memory access, set the user stack pointer (USP) or the interrupt stack pointer (ISP) to a multiple of 4.

### 2.1.8 Flag Register (FLG)

This 32-bit register indicates the CPU status.

### 2.1.8.1 Carry Flag (C flag)

This flag retains a carry, borrow, or shifted-out bit generated by the arithmetic logic unit (ALU).

### 2.1.8.2 Debug Flag (D flag)

This flag is only for debugging. Only set this bit to 0.

#### 2.1.8.3 Zero Flag (Z flag)

This flag becomes 1 when the result of an operation is 0; otherwise it is 0.

### 2.1.8.4 Sign Flag (S flag)

This flag becomes 1 when the result of an operation is a negative value; otherwise it is 0.

### 2.1.8.5 Register Bank Select Flag (B flag)

This flag selects a register bank. It indicates 0 when register bank 0 is selected, and 1 when register bank 1 is selected.

## 2.1.8.6 Overflow Flag (O flag)

This flag becomes 1 when the result of an operation overflows; otherwise it is 0.

#### 2.1.8.7 Interrupt Enable Flag (I flag)

This flag enables maskable interrupts. To disable maskable interrupts, set this flag to 0. To enable them, set this flag to 1. When an interrupt is accepted, the flag becomes 0.

#### 2.1.8.8 Stack Pointer Select Flag (U flag)

To select the interrupt stack pointer (ISP), set this flag to 0. To select the user stack pointer (USP), set this flag to 1.

It becomes 0 when a hardware interrupt is accepted or when an INT instruction designated by a software interrupt number from 0 to 127 is executed.

#### 2.1.8.9 Floating-point Underflow Flag (FU flag)

This flag becomes 1 when an underflow occurs in a floating-point operation; otherwise it is 0. It also becomes 1 when the operand contains invalid numbers (subnormal numbers).

#### 2.1.8.10 Floating-point Overflow Flag (FO flag)

This flag becomes 1 when an overflow occurs in a floating-point operation; otherwise it is 0. It also becomes 1 when the operand contains invalid numbers (subnormal numbers).

### 2.1.8.11 Processor Interrupt Priority Level (IPL)

The processor interrupt priority level (IPL), consisting of 3 bits, selects a processor interrupt priority level from level 0 to 7. An interrupt is enabled when the interrupt request level is higher than the selected IPL.

When the processor interrupt priority level (IPL) is set to 111b (level 7), all interrupts are disabled.

#### 2.1.8.12 Fixed-point Radix Point Designation Bit (DP bit)

This bit designates the radix point. It also specifies which portion of the fixed-point multiplication result to extract. It is used for the MULX instruction.

#### 2.1.8.13 Floating-point Rounding Mode (RND)

The 2-bit floating-point rounding mode selects a rounding mode for floating-point calculation results.

#### 2.1.8.14 Reserved

Only set this bit to 0. The read value is undefined.

| Table 4.12 | SFR List (12) |

|------------|---------------|

|------------|---------------|

| Address            | Register                                            | Symbol | Reset Value |

|--------------------|-----------------------------------------------------|--------|-------------|

| 0002F0h            |                                                     |        |             |

| 0002F1h            |                                                     |        |             |

| 0002F2h            |                                                     |        |             |

| 0002F3h            |                                                     |        |             |

| 0002F4h            | UART4 Special Mode Register 4                       | U4SMR4 | 00h         |

| 0002F5h            | UART4 Special Mode Register 3                       | U4SMR3 | 00h         |

| 0002F6h            | UART4 Special Mode Register 2                       | U4SMR2 | 00h         |

| 0002F7h            | UART4 Special Mode Register                         | U4SMR  | 00h         |

| 0002F8h            | UART4 Transmit/Receive Mode Register                | U4MR   | 00h         |

|                    | UART4 Bit Rate Register                             | U4BRG  | XXh         |

| 0002FAh            | UART4 Transmit Buffer Register                      | U4TB   | XXXXh       |

| 0002FBh            | •                                                   |        |             |

| 0002FCh            | UART4 Transmit/Receive Control Register 0           | U4C0   | 0000 1000b  |

|                    | UART4 Transmit/Receive Control Register 1           | U4C1   | 0000 0010b  |

|                    | UART4 Receive Buffer Register                       | U4RB   | XXXXh       |

| 0002FFh            | •                                                   |        |             |

|                    | Count Start Register for Timers B3, B4, and B5      | TBSR   | 000X XXXXb  |

| 000301h            |                                                     | -      |             |

|                    | Timer A1-1 Register                                 | TA11   | XXXXh       |

| 000303h            | •                                                   |        |             |

|                    | Timer A2-1 Register                                 | TA21   | XXXXh       |

| 000305h            |                                                     |        |             |

|                    | Timer A4-1 Register                                 | TA41   | XXXXh       |

| 000307h            |                                                     |        | 70000       |

|                    | Three-phase PWM Control Register 0                  | INVC0  | 00h         |

|                    | Three-phase PWM Control Register 1                  | INVC1  | 00h         |

|                    | Three-phase Output Buffer Register 0                | IDB0   | XX11 1111b  |

|                    | Three-phase Output Buffer Register 1                | IDB1   | XX11 1111b  |

|                    | Dead Time Timer                                     | DTT    | XXh         |

|                    | Timer B2 Interrupt Generating Frequency Set Counter | ICTB2  | XXh         |

| 00030Eh            |                                                     | 10102  |             |

| 00030Fh            |                                                     |        |             |

|                    | Timer B3 Register                                   | TB3    | XXXXh       |

| 000311h            |                                                     | 100    | 700011      |

|                    | Timer B4 Register                                   | TB4    | XXXXh       |

| 000312h            |                                                     |        | //////      |

|                    | Timer B5 Register                                   | TB5    | XXXXh       |

| 000314h            |                                                     | 105    | ~~~~        |

| 000315h            |                                                     |        |             |

| 000310h            |                                                     |        |             |

| 000317h<br>000318h |                                                     |        |             |

| 000318h            |                                                     |        |             |

| 000319h            |                                                     |        |             |

|                    |                                                     |        | 0022 00006  |

|                    | Timer B3 Mode Register                              | TB3MR  | 00XX 0000b  |

|                    | Timer B4 Mode Register                              | TB4MR  | 00XX 0000b  |

| -00031Dh           | Timer B5 Mode Register                              | TB5MR  | 00XX 0000b  |

|                    |                                                     |        |             |

| 00031Eh<br>00031Fh |                                                     |        |             |

X: Undefined

Blanks are reserved. No access is allowed.

| Table 4.13 | SFR List (13) |

|------------|---------------|

|------------|---------------|

| Address            | Register                                  | Symbol     | Reset Value                             |

|--------------------|-------------------------------------------|------------|-----------------------------------------|

| 000320h            |                                           |            |                                         |

| 000321h            |                                           |            |                                         |

| 000322h            |                                           |            |                                         |

| 000323h            |                                           |            |                                         |

| 000324h            | UART3 Special Mode Register 4             | U3SMR4     | 00h                                     |

| 000325h            | UART3 Special Mode Register 3             | U3SMR3     | 00h                                     |

| 000326h            | UART3 Special Mode Register 2             | U3SMR2     | 00h                                     |

| 000327h            | UART3 Special Mode Register               | U3SMR      | 00h                                     |

| 000328h            | UART3 Transmit/Receive Mode Register      | U3MR       | 00h                                     |

| 000329h            | UART3 Bit Rate Register                   | U3BRG      | XXh                                     |

| 00032Ah            | UART3 Transmit Buffer Register            | U3TB       | XXXXh                                   |

| 00032Bh            |                                           |            |                                         |

| 00032Ch            | UART3 Transmit/Receive Control Register 0 | U3C0       | 0000 1000b                              |

|                    | UART3 Transmit/Receive Control Register 1 | U3C1       | 0000 0010b                              |

|                    | UART3 Receive Buffer Register             | U3RB       | XXXXh                                   |

| 00032Fh            |                                           |            |                                         |

| 000330h            |                                           |            |                                         |

| 000331h            |                                           |            |                                         |

| 000332h            |                                           |            |                                         |

| 000333h            |                                           |            |                                         |

|                    | UART2 Special Mode Register 4             | U2SMR4     | 00h                                     |

|                    | UART2 Special Mode Register 3             | U2SMR3     | 00h                                     |

|                    | UART2 Special Mode Register 2             | U2SMR2     | 00h                                     |

|                    | UART2 Special Mode Register               | U2SMR      | 00h                                     |

|                    | UART2 Transmit/Receive Mode Register      | U2MR       | 00h                                     |

|                    | UART2 Bit Rate Register                   | U2BRG      | XXh                                     |

|                    | UART2 Transmit Buffer Register            | U2TB       | XXXXh                                   |

| 00033Bh            | 5                                         |            | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|                    | UART2 Transmit/Receive Control Register 0 | U2C0       | 0000 1000b                              |

|                    | UART2 Transmit/Receive Control Register 1 | U2C1       | 0000 0010b                              |

|                    | UART2 Receive Buffer Register             | U2RB       | XXXXh                                   |

| 00033Fh            |                                           | 02110      | ,                                       |

|                    | Count Start Register                      | TABSR      | 0000 0000b                              |

|                    | Clock Prescaler Reset Register            | CPSRF      | 0XXX XXXXb                              |

|                    | One-shot Start Register                   | ONSF       | 0000 0000b                              |

|                    | Trigger Select Register                   | TRGSR      | 0000 0000b                              |

|                    | Increment/Decrement Select Register       | UDF        | 0000 0000b                              |

| 000345h            |                                           |            |                                         |

|                    | Timer A0 Register                         | TA0        | XXXXh                                   |

| 000347h            |                                           |            |                                         |

|                    | Timer A1 Register                         | TA1        | XXXXh                                   |

| 000348h            |                                           |            |                                         |

|                    | Timer A2 Register                         | TA2        | XXXXh                                   |

|                    |                                           |            |                                         |

| 0003105            |                                           | 1          |                                         |

| 00034Bh            |                                           | ΤΛ 2       | VVVVh                                   |

| 00034Ch            | Timer A3 Register                         | TA3        | XXXXh                                   |

| 00034Ch<br>00034Dh | Timer A3 Register                         |            |                                         |

| 00034Ch<br>00034Dh | Timer A3 Register<br>Timer A4 Register    | TA3<br>TA4 | XXXXh<br>XXXXh                          |

X: Undefined

Blanks are reserved. No access is allowed.

| Table 4.20 | SFR List (20) |

|------------|---------------|

|------------|---------------|

| Address | Register                                        | Symbol | Reset Value               |

|---------|-------------------------------------------------|--------|---------------------------|

| 040094h |                                                 |        |                           |

| 040095h |                                                 |        |                           |

| 040096h |                                                 |        |                           |

|         | Three-phase Output Buffer Control Register      | IOBC   | 0XXX XXXXb                |

| 040098h | Input Function Select Register 0                | IFS0   | X000 0000b (1)            |

| 040099h |                                                 |        |                           |

| 04009Ah | Input Function Select Register 2                | IFS2   | 0000 00X0b <sup>(2)</sup> |

| 04009Bh | Input Function Select Register 3                | IFS3   | XXXX XX00b                |

| 04009Ch |                                                 |        |                           |

| 04009Dh |                                                 |        |                           |

| 04009Eh |                                                 |        |                           |

| 04009Fh | Input Function Select Register 7 <sup>(3)</sup> | IFS7   | XXXX XX0Xb                |

| 0400A0h | Port P0_0 Function Select Register              | P0_0S  | 0XXX X000b                |

|         | Port P1_0 Function Select Register              | P1_0S  | XXXX X000b                |

|         | Port P0_1 Function Select Register              | P0_1S  | 0XXX X000b                |

| 0400A3h | Port P1_1 Function Select Register              | P1_1S  | XXXX X000b                |

|         | Port P0_2 Function Select Register              | P0_2S  | 0XXX X000b                |

|         | Port P1_2 Function Select Register              | P1_2S  | XXXX X000b                |

|         | Port P0_3 Function Select Register              | P0_3S  | 0XXX X000b                |

|         | Port P1_3 Function Select Register              | P1_3S  | XXXX X000b                |

|         | Port P0_4 Function Select Register              | P0_4S  | 0XXX X000b                |

| 0400A9h | Port P1_4 Function Select Register              | P1_4S  | XXXX X000b                |

| 0400AAh | Port P0_5 Function Select Register              | P0_5S  | 0XXX X000b                |

|         | Port P1_5 Function Select Register              | P1_5S  | XXXX X000b                |

|         | Port P0_6 Function Select Register              | P0_6S  | 0XXX X000b                |

|         | Port P1_6 Function Select Register              | P1_6S  | XXXX X000b                |

|         | Port P0_7 Function Select Register              | P0_7S  | 0XXX X000b                |

|         | Port P1_7 Function Select Register              | P1_7S  | XXXX X000b                |

|         | Port P2_0 Function Select Register              | P2_0S  | 0XXX X000b                |

|         | Port P3_0 Function Select Register              | P3_0S  | XXXX X000b                |

|         | Port P2_1 Function Select Register              | P2_1S  | 0XXX X000b                |

|         | Port P3_1 Function Select Register              | P3_1S  | XXXX X000b                |

|         | Port P2_2 Function Select Register              | P2_2S  | 0XXX X000b                |

|         | Port P3_2 Function Select Register              | P3_2S  | XXXX X000b                |

|         | Port P2_3 Function Select Register              | P2_3S  | 0XXX X000b                |

|         | Port P3_3 Function Select Register              | P3_3S  | XXXX X000b                |

|         | Port P2_4 Function Select Register              | P2_4S  | 0XXX X000b                |

|         | Port P3_4 Function Select Register              | P3_4S  | XXXX X000b                |

|         | Port P2_5 Function Select Register              | P2_5S  | 0XXX X000b                |

|         | Port P3_5 Function Select Register              | P3_5S  | XXXX X000b                |

|         | Port P2_6 Function Select Register              | P2_6S  | 0XXX X000b                |

|         | Port P3_6 Function Select Register              | P3_6S  | XXXX X000b                |

|         | Port P2_7 Function Select Register              | P2_7S  | 0XXX X000b                |

| 0400BFh | Port P3_7 Function Select Register              | P3_7S  | XXXX X000b                |

X: Undefined

Blanks are reserved. No access is allowed.

Notes:

- 1. The reset value is 0000 0000b in the 64-pin package.

- 2. The reset value is 0000 000Xb in the 64-pin package.

- 3. This register is provided for the 64-pin package only. No access is allowed in the 100-pin package.

| 14016 4.22              | 31 K LISI (22)                      |         |             |

|-------------------------|-------------------------------------|---------|-------------|

| Address                 | Register                            | Symbol  | Reset Value |

| 0400F0h                 | Port P10_0 Function Select Register | P10_0S  | 0XXX X000b  |

| 0400F1h                 |                                     |         |             |

| 0400F2h                 | Port P10_1 Function Select Register | P10_1S  | 0XXX X000b  |

| 0400F3h                 |                                     |         |             |

|                         | Port P10 2 Function Select Register | P10 2S  | 0XXX X000b  |

| 0400F5h                 |                                     |         |             |

|                         | Port P10_3 Function Select Register | P10_3S  | 0XXX X000b  |

| 0400F7h                 |                                     |         |             |

|                         | Port P10_4 Function Select Register | P10_4S  | 0XXX X000b  |

| 0400F9h                 |                                     |         | 0,000,0000  |

|                         | Port P10_5 Function Select Register | P10_5S  | 0XXX X000b  |

| 0400FBh                 |                                     | 1 10_00 |             |

|                         | Port P10_6 Function Select Register | P10_6S  | 0XXX X000b  |

| 0400FCh                 |                                     | F 10_03 |             |

|                         |                                     | D10 79  |             |

|                         | Port P10_7 Function Select Register | P10_7S  | 0XXX X000b  |

| 0400FFh                 |                                     |         |             |

| 040100h                 |                                     |         |             |

| 040101h                 |                                     |         |             |

| 040102h                 |                                     |         |             |

| 040103h                 |                                     |         |             |

| 040104h                 |                                     |         |             |

| 040105h                 |                                     |         |             |

| 040106h                 |                                     |         |             |

| 040107h                 |                                     |         |             |

| 040108h                 |                                     |         |             |

| 040109h                 |                                     |         |             |

| 04010Ah                 |                                     |         |             |

| 04010Bh                 |                                     |         |             |

| 04010Ch                 |                                     |         |             |

| 04010Dh                 |                                     |         |             |

| 04010Eh                 |                                     |         |             |

| 04010Fh                 |                                     |         |             |

| 040110h                 |                                     |         |             |

| 040111h                 |                                     |         |             |

| 040112h                 |                                     |         |             |

| 040113h                 |                                     |         |             |

| 040114h                 |                                     |         |             |

| 040115h                 |                                     |         |             |

| 040116h                 |                                     |         |             |

| 040117h                 |                                     |         |             |

| 040118h                 |                                     |         |             |

| 040110h                 |                                     |         |             |

| 040119h                 |                                     |         |             |

|                         |                                     |         |             |

| 04011Bh                 |                                     |         |             |

| 04011Ch                 |                                     |         |             |

| 04011Dh                 |                                     |         |             |

| 04011Eh                 |                                     |         |             |

| 04011Fh                 |                                     |         |             |

| X <sup>·</sup> Undefine |                                     |         |             |

#### Table 4.22SFR List (22)

X: Undefined

Blanks are reserved. No access is allowed.

## 5. Electrical Characteristics

| Symbol                             |                   | Characteristic                                                                                                                                  | Condition             | Value <sup>(2)</sup>           | Unit |

|------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------|------|

| V <sub>CC1,</sub> V <sub>CC2</sub> | Supply volta      | age                                                                                                                                             | $V_{CC1} = AV_{CC}$   | -0.3 to 6.0                    | V    |

| V <sub>CC2</sub>                   | Supply volta      | age                                                                                                                                             | —                     | -0.3 to V <sub>CC1</sub>       | V    |

| AV <sub>CC</sub>                   | Analog sup        | ply voltage                                                                                                                                     | $V_{CC1} = AV_{CC}$   | -0.3 to 6.0                    | V    |

| VI                                 | Input<br>voltage  | XIN, RESET, CNVSS, NSD, V <sub>REF</sub> ,<br>P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_7, P9_1, P9_3 to P9_7,<br>P10_0 to P10_7 <sup>(3)</sup> |                       | -0.3 to V <sub>CC1</sub> + 0.3 | V    |

|                                    |                   | P0_0 to P0_7, P1_0 to P1_7,<br>P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7 <sup>(3)</sup>                                         |                       | -0.3 to V <sub>CC2</sub> + 0.3 | V    |

|                                    |                   | P7_0, P7_1                                                                                                                                      |                       | -0.3 to 6.0                    | V    |

| V <sub>O</sub>                     | Output<br>voltage | XOUT, P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7,<br>P9_3 to P9_7, P10_0 to P10_7 <sup>(3)</sup>                                   |                       | -0.3 to V <sub>CC1</sub> + 0.3 | V    |

|                                    |                   | P0_0 to P0_7, P1_0 to P1_7,<br>P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7 <sup>(3)</sup>                                         |                       | -0.3 to V <sub>CC2</sub> + 0.3 | V    |

|                                    |                   | P7_0, P7_1                                                                                                                                      |                       | -0.3 to 6.0                    | V    |

| P <sub>d</sub>                     | Power cons        | sumption                                                                                                                                        | T <sub>a</sub> = 25°C | 500                            | mW   |

|                                    | Operating t       | emperature range                                                                                                                                |                       | -40 to 85                      | °C   |

| T <sub>stg</sub>                   | Storage ten       | nperature range                                                                                                                                 |                       | -65 to 150                     | °C   |

Table 5.1

Absolute Maximum Ratings <sup>(1)</sup>

Notes:

- 1. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. The V<sub>CC2</sub> pin is available in the 100-pin package only. It should be considered as V<sub>CC1</sub> in the 64-pin package.

- 3. Ports P0\_4 to P0\_7, P1\_0 to P1\_4, P3\_4 to P3\_7, P4, P5, P9\_1, and P9\_4 to P9\_7 are available in the 100-pin package only.

# Table 5.3Operating Conditions (2/5) $(V_{CC1} = V_{CC2} = 3.0 \text{ to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, \text{ and } T_a = T_{opr}, \text{ unless otherwise noted})$ <sup>(1)</sup>

| Symbol           | Characteristic                               |                          | Value <sup>(2)</sup> |      |      | Unit |

|------------------|----------------------------------------------|--------------------------|----------------------|------|------|------|

| Gynnoor          | Characteristic                               |                          | Min.                 | Тур. | Max. | Onic |

| C <sub>VDC</sub> | Decoupling capacitance for voltage regulator | Inter-pin voltage: 1.5 V | 2.4                  |      | 10.0 | μF   |

Notes:

1. The device is operationally guaranteed under these operating conditions.

2. This value should be met with due consideration to the following conditions: operating temperature, DC bias, aging, etc.

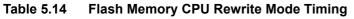

## Timing Requirements ( $V_{CC1} = V_{CC2} = 3.0$ to 5.5 V, $V_{SS} = 0$ V, and Ta = T<sub>opr</sub>, unless otherwise noted)

| Symbol               | Characteristics                     | Value |      | Unit |

|----------------------|-------------------------------------|-------|------|------|

| Symbol               | Characteristics                     | Min.  | Max. | Unit |

| t <sub>cR</sub>      | Read cycle time                     | 200   |      | ns   |

| t <sub>su(S-R)</sub> | Chip-select setup time before read  | 200   |      | ns   |

| t <sub>h(R-S)</sub>  | Chip-select hold time after read    | 0     |      | ns   |

| t <sub>su(A-R)</sub> | Address setup time before read      | 200   |      | ns   |

| t <sub>h(R-A)</sub>  | Address hold time after read        | 0     |      | ns   |

| t <sub>w(R)</sub>    | Read pulse width                    | 100   |      | ns   |

| t <sub>cW</sub>      | Write cycle time                    | 200   |      | ns   |

| t <sub>su(S-W)</sub> | Chip-select setup time before write | 0     |      | ns   |

| t <sub>h(W-S)</sub>  | Chip-select hold time after write   | 30    |      | ns   |

| t <sub>su(A-W)</sub> | Address setup time before write     | 0     |      | ns   |

| t <sub>h(W-A)</sub>  | Address hold time after write       | 30    |      | ns   |

| t <sub>w(W)</sub>    | Write pulse width                   | 50    |      | ns   |

Figure 5.5 Flash Memory CPU Rewrite Mode Timing

## $V_{CC1} = V_{CC2} = 5 V$

# Table 5.15Electrical Characteristics (1/3)<br/>(V<sub>CC1</sub> = V<sub>CC2</sub> = 4.2 to 5.5 V, V<sub>SS</sub> = 0 V, T<sub>a</sub> = T<sub>opr</sub>, and f<sub>(CPU)</sub> = 50 MHz, unless otherwise<br/>noted)

| Symbol          |                                   | Characteristic                                                                                                                                                                         | Measurement               | Val                   | ue <sup>(2)</sup> |                  | Unit |

|-----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|-------------------|------------------|------|

| Cymbol          |                                   | Characteristic                                                                                                                                                                         | Condition                 | Min.                  | Тур.              | Max.             | Onic |

| V <sub>OH</sub> | High<br>level<br>output           | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7<br>(1)                                                                                           | I <sub>OH</sub> = -5 mA   | V <sub>CC2</sub> -2.0 |                   | V <sub>CC2</sub> | V    |

|                 | voltage                           | P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_3 to P9_7, P10_0 to P10_7<br>(1)                                                                                           |                           | V <sub>CC1</sub> -2.0 |                   | V <sub>CC1</sub> | V    |

|                 |                                   | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7<br>(1)                                                                                           | I <sub>OH</sub> = -200 μA | V <sub>CC2</sub> -0.3 |                   | V <sub>CC2</sub> | V    |

|                 |                                   | P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_3 to P9_7, P10_0 to P10_7<br>(1)                                                                                           |                           | V <sub>CC1</sub> -0.3 |                   | V <sub>CC1</sub> | V    |

| V <sub>OL</sub> | Low<br>level<br>output<br>voltage | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_3 to P9_7, P10_0 to P10_7<br>(1) |                           |                       |                   | 2.0              | v    |

|                 |                                   | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_3 to P9_7, P10_0 to P10_7<br>(1) |                           |                       |                   | 0.45             | v    |

Notes:

1. Ports P0\_4 to P0\_7, P1\_0 to P1\_4, P3\_4 to P3\_7, P4, P5, and P9\_4 to P9\_7 are available in the 100-pin package only.

2. The V<sub>CC2</sub> pin is available in the 100-pin package only. It should be considered as V<sub>CC1</sub> in the 64-pin package.

# $V_{CC1} = V_{CC2} = 5 V$

# Timing Requirements ( $V_{CC1} = V_{CC2} = 4.2$ to 5.5 V, $V_{SS} = 0$ V, and $T_a = T_{opr}$ , unless otherwise noted)

| Symbol Characteristic | Characteristic                                           | Value |      | Unit |

|-----------------------|----------------------------------------------------------|-------|------|------|

| Symbol                | Characteristic                                           | Min.  | Max. | Unit |