### E. Renesas Electronics America Inc - <u>UPD78F9232MC-5A4-A Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                   |

| Core Size                  | -                                                                                   |

| Speed                      | -                                                                                   |

| Connectivity               | -                                                                                   |

| Peripherals                | -                                                                                   |

| Number of I/O              | -                                                                                   |

| Program Memory Size        | -                                                                                   |

| Program Memory Type        | -                                                                                   |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | -                                                                                   |

| Voltage - Supply (Vcc/Vdd) | -                                                                                   |

| Data Converters            | -                                                                                   |

| Oscillator Type            | -                                                                                   |

| Operating Temperature      | -                                                                                   |

| Mounting Type              | -                                                                                   |

| Package / Case             | -                                                                                   |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f9232mc-5a4-a |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

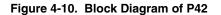

- PU4: Pull-up resistor option register 4

- P4: Port register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

#### 5.4 System Clock Oscillators

The following three types of system clock oscillators are available.

- High-speed internal oscillator: Internally oscillates a clock of 8 MHz (TYP.).

- Crystal/ceramic oscillator: Oscillates a clock of 2 to 10 MHz.

- External clock input circuit: Supplies a clock of 2 to 10 MHz to the X1 pin.

#### 5.4.1 High-speed internal oscillator

The 78K0S/KB1+ includes a high-speed internal oscillator (8 MHz (TYP.)).

If the high-speed internal oscillation is selected by the option byte as the clock source, the X1 and X2 pins can be used as I/O port pins.

For details of the option byte, refer to **CHAPTER 18 OPTION BYTE**. For details of I/O ports, refer to **CHAPTER 4 PORT FUNCTIONS**.

#### 5.4.2 Crystal/ceramic oscillator

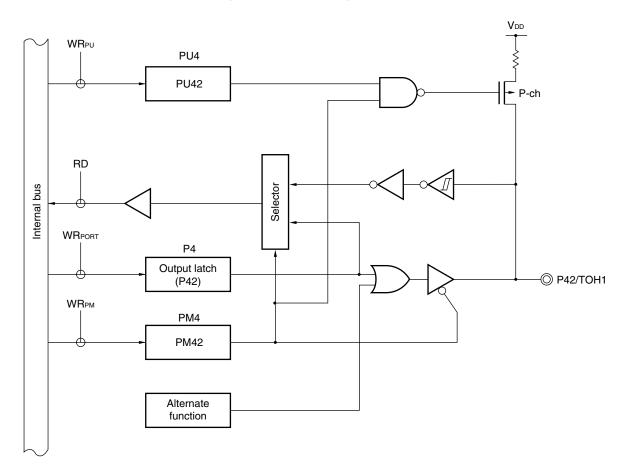

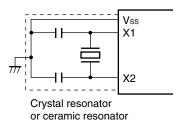

The crystal/ceramic oscillator oscillates using a crystal or ceramic resonator connected between the X1 and X2 pins.

If the crystal/ceramic oscillator is selected by the option byte as the system clock source, the X1 and X2 pins are used as crystal or ceramic resonator connection pins.

For details of the option byte, refer to **CHAPTER 18 OPTION BYTE**. For details of I/O ports, refer to **CHAPTER 4 PORT FUNCTIONS**.

Figure 5-6 shows the external circuit of the crystal/ceramic oscillator.

Caution When using the crystal/ceramic oscillator, wire as follows in the area enclosed by the broken lines in Figure 5-6 to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines. Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss. Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

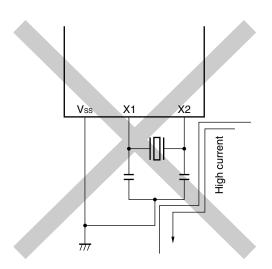

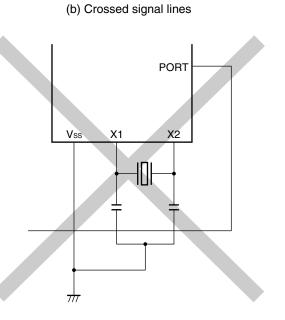

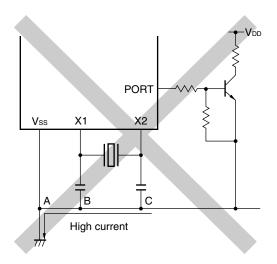

Figure 5-7 shows examples of incorrect resonator connection.

(a) Too long wiring of connected circuit

Х2 Vss X1 40  $\frac{1}{1}$

#### (c) Wiring near high fluctuating current

(d) Current flowing through ground line of oscillator (Potential at points A, B, and C fluctuates.)

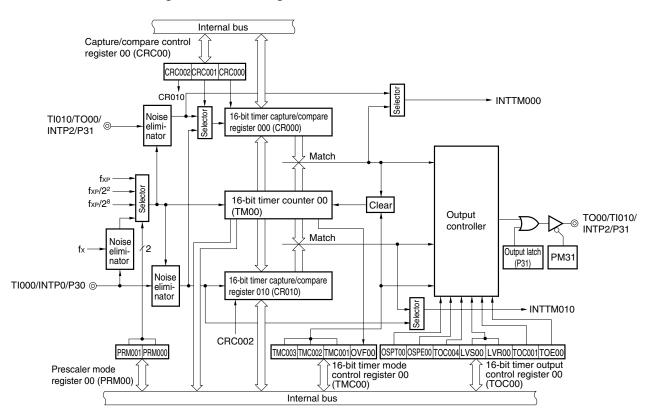

### 6.2 Configuration of 16-bit Timer/Event Counter 00

16-bit timer/event counter 00 consists of the following hardware.

| Table 6-1. | Configuration | of 16-bit Tim | ner/Event ( | Counter 00 |

|------------|---------------|---------------|-------------|------------|

|------------|---------------|---------------|-------------|------------|

| Item              | Configuration                                                                                                                                                                                                                               |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Timer counter     | 16-bit timer counter 00 (TM00)                                                                                                                                                                                                              |  |

| Register          | 16-bit timer capture/compare registers 000, 010 (CR000, CR010)                                                                                                                                                                              |  |

| Timer input       | TI000, TI010                                                                                                                                                                                                                                |  |

| Timer output      | TO00, output controller                                                                                                                                                                                                                     |  |

| Control registers | 16-bit timer mode control register 00 (TMC00)<br>Capture/compare control register 00 (CRC00)<br>16-bit timer output control register 00 (TOC00)<br>Prescaler mode register 00 (PRM00)<br>Port mode register 3 (PM3)<br>Port register 3 (P3) |  |

Figure 6-1 shows a block diagram of these counters.

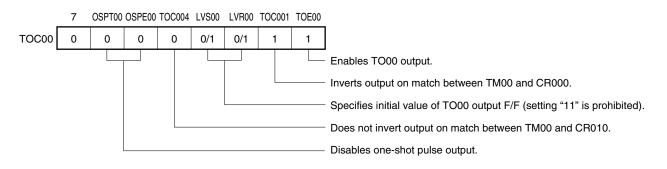

#### (3) 16-bit timer output control register 00 (TOC00)

This register controls the operation of the 16-bit timer/event counter output controller. It sets timer output F/F set/reset, output inversion enable/disable, 16-bit timer/event counter 00 timer output enable/disable, one-shot pulse output operation enable/disable, and output trigger of one-shot pulse by software.

TOC00 is set by a 1-bit or 8-bit memory manipulation instruction.

Generation of reset signal sets the value of TOC00 to 00H.

#### Figure 6-7. Format of 16-bit Timer Output Control Register 00 (TOC00)

Address: FF63H After reset: 00H R/W

| Symbol | 7 | <6>    | <5>    | 4      | <3>   | <2>   | 1      | <0>   |

|--------|---|--------|--------|--------|-------|-------|--------|-------|

| TOC00  | 0 | OSPT00 | OSPE00 | TOC004 | LVS00 | LVR00 | TOC001 | TOE00 |

| 1 | OSPT00 | One-shot pulse output trigger control via software |  |  |  |

|---|--------|----------------------------------------------------|--|--|--|

|   | 0      | No one-shot pulse output trigger                   |  |  |  |

|   | 1      | One-shot pulse output trigger                      |  |  |  |

| Ī | OSPE00 | One-shot pulse output operation control    |  |  |

|---|--------|--------------------------------------------|--|--|

| ſ | 0      | Successive pulse output mode               |  |  |

| ĺ | 1      | One-shot pulse output mode <sup>Note</sup> |  |  |

| TOC004 | Timer output F/F control using match of CR010 and TM00 |  |

|--------|--------------------------------------------------------|--|

| 0      | Disables inversion operation                           |  |

| 1      | 1 Enables inversion operation                          |  |

| LVS00 | LVR00 | Timer output F/F status setting |  |  |  |

|-------|-------|---------------------------------|--|--|--|

| 0     | 0     | No change                       |  |  |  |

| 0     | 1     | imer output F/F reset (0)       |  |  |  |

| 1     | 0     | Fimer output F/F set (1)        |  |  |  |

| 1     | 1     | Setting prohibited              |  |  |  |

| TOC001 | Timer output F/F control using match of CR000 and TM00 |  |  |  |

|--------|--------------------------------------------------------|--|--|--|

| 0      | Disables inversion operation                           |  |  |  |

| 1      | Enables inversion operation                            |  |  |  |

| TOE00 | Timer output control                      |  |

|-------|-------------------------------------------|--|

| 0     | Disables output (output fixed to level 0) |  |

| 1     | Enables output                            |  |

- **Note** The one-shot pulse output mode operates correctly only in the free-running mode and the mode in which clear & start occurs at the TI000 pin valid edge. In the mode in which clear & start occurs on a match between TM00 and CR000, one-shot pulse output is not possible because an overflow does not occur.

- Cautions 1. The timer operation must be stopped before setting other than OSPT00.

- 2. If LVS00 and LVR00 are read, 0 is read.

- 3. OSPT00 is automatically cleared after data is set, so 0 is read.

- 4. Do not set OSPT00 to 1 other than in one-shot pulse output mode.

- 5. A write interval of two cycles or more of the count clock selected by prescaler mode register 00 (PRM00) is required, when OSPT00 is set to 1 successively.

- 6. When TOE00 is 0, set TOE00, LVS00, and LVR00 at the same time with the 8-bit memory manipulation instruction. When TOE00 is 1, LVS00 and LVR00 can be set with the 1-bit memory manipulation instruction.

The external event counter counts the number of external clock pulses to be input to the TI000 pin with using 16-bit timer counter 00 (TM00).

TM00 is incremented each time the valid edge specified by prescaler mode register 00 (PRM00) is input.

When the TM00 count value matches the 16-bit timer capture/compare register 000 (CR000) value, TM00 is cleared to 0 and the interrupt request signal (INTTM000) is generated.

Input a value other than 0000H to CR000. (A count operation with a pulse cannot be carried out.)

The rising edge, the falling edge, or both edges can be selected using bits 4 and 5 (ES000 and ES010) of prescaler mode register 00 (PRM00).

Because an operation is carried out only when the valid edge of the TI000 pin is detected twice after sampling with the internal clock (fxp), noise with a short pulse width can be removed.

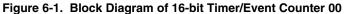

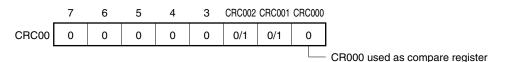

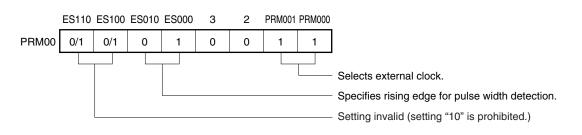

#### Figure 6-14. Control Register Settings in External Event Counter Mode (with Rising Edge Specified)

(a) Capture/compare control register 00 (CRC00)

(b) Prescaler mode register 00 (PRM00)

(c) 16-bit timer mode control register 00 (TMC00)

**Remark** 0/1: Setting 0 or 1 allows another function to be used simultaneously with the external event counter. See the description of the respective control registers for details.

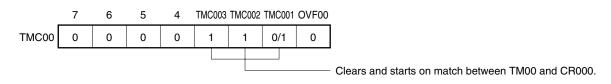

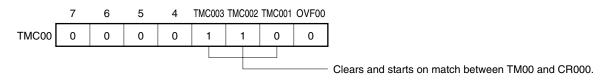

#### Figure 6-27. Control Register Settings in Square-Wave Output Mode (2/2)

#### (c) 16-bit timer output control register 00 (TOC00)

#### (d) 16-bit timer mode control register 00 (TMC00)

### **Remark** 0/1: Setting 0 or 1 allows another function to be used simultaneously with square-wave output. See the description of the respective control registers for details.

#### 6.4.5 PPG output operations

Setting 16-bit timer mode control register 00 (TMC00) and capture/compare control register 00 (CRC00) as shown in Figure 6-29 allows operation as PPG (Programmable Pulse Generator) output.

#### Setting

The basic operation setting procedure is as follows.

- <1> Set the CRC00 register (see Figure 6-29 for the set value).

- <2> Set any value to the CR000 register as the cycle.

- <3> Set any value to the CR010 register as the duty factor.

- <4> Set the TOC00 register (see Figure 6-29 for the set value).

- <5> Set the count clock by using the PRM00 register.

- <6> Set the TMC00 register to start the operation (see Figure 6-29 for the set value).

- Caution Changing the CRC0n0 setting during TM00 operation may cause a malfunction. To change the setting, refer to 6.5 Cautions Related to 16-bit Timer/Event Counter 00 (17) Changing compare register during timer operation.

- Remarks 1. For the setting of the TO00 pin, see 6.3 (5) Port mode register 3 (PM3).

- 2. For how to enable the INTTM000 interrupt, see CHAPTER 13 INTERRUPT FUNCTIONS.

- **3.** n = 0 or 1

In the PPG output operation, rectangular waves are output from the TO00 pin with the pulse width and the cycle that correspond to the count values preset in 16-bit timer capture/compare register 010 (CR010) and in 16-bit timer capture/compare register 000 (CR000), respectively.

#### (2) Timing chart

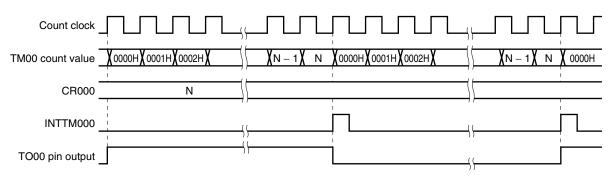

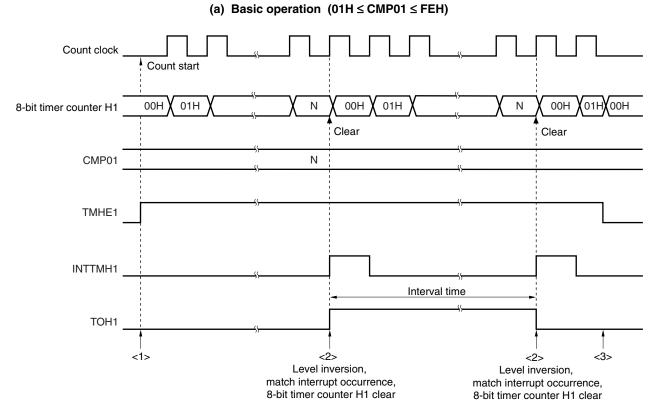

The timing of the interval timer/square-wave output operation is shown below.

# Figure 8-7. Timing of Interval Timer/Square-Wave Output Operation (1/2)

- <1> The count operation is enabled by setting the TMHE1 bit to 1. The count clock starts counting no more than 1 clock after the operation is enabled.

- <2> When the values of 8-bit timer counter H1 and the CMP01 register match, the value of 8-bit timer counter H1 is cleared, the TOH1 output level is inverted, and the INTTMH1 signal is output.

- <3> The INTTMH1 signal and TOH1 output become inactive by clearing the TMHE1 bit to 0 during timer H1 operation. If these are inactive from the first, the level is retained.

**Remark**  $01H \le N \le FEH$

#### 14.1.2 Registers used during standby

The oscillation stabilization time after the standby mode is released is controlled by the oscillation stabilization time select register (OSTS).

Remark For the registers that start, stop, or select the clock, see CHAPTER 5 CLOCK GENERATORS.

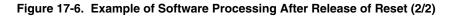

#### (1) Oscillation stabilization time select register (OSTS)

This register is used to select oscillation stabilization time of the clock supplied from the oscillator when the STOP mode is released. The wait time set by OSTS is valid only when the crystal/ceramic oscillation clock is selected as the system clock and after the STOP mode is released. If the high-speed internal oscillation or external clock input is selected as the system clock source, no wait time elapses.

The system clock oscillator and the oscillation stabilization time that elapses after power application or release of reset are selected by the option byte. For details, refer to **CHAPTER 18 OPTION BYTE**. OSTS is set by using the 8-bit memory manipulation instruction.

#### Figure 14-1. Format of Oscillation Stabilization Time Select Register (OSTS)

Address: FFF4H After reset: Undefined R/W

| Symbol 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0     |

|----------|---|---|---|---|---|-------|-------|

| OSTS 0   | 0 | 0 | 0 | 0 | 0 | OSTS1 | OSTS0 |

| OSTS1 | OSTS0 | Selection of oscillation stabilization time |

|-------|-------|---------------------------------------------|

| 0     | 0     | 2 <sup>10</sup> /fx (102.4 μs)              |

| 0     | 1     | 2 <sup>12</sup> /fx (409.6 μs)              |

| 1     | 0     | 2 <sup>15</sup> /fx (3.27 ms)               |

| 1     | 1     | 2 <sup>17</sup> /fx (13.1 ms)               |

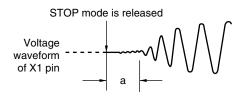

- Cautions 1. To set and then release the STOP mode, set the oscillation stabilization time as follows. Expected oscillation stabilization time of resonator ≤ Oscillation stabilization time set by OSTS

- 2. The wait time after the STOP mode is released does not include the time from the release of the STOP mode to the start of clock oscillation ("a" in the figure below), regardless of whether STOP mode was released by reset signal generation or interrupt generation.

3. The oscillation stabilization time that elapses on power application or after release of reset is selected by the option byte. For details, refer to CHAPTER 18 OPTION BYTE.

Remarks 1. (): fx = 10 MHz

**2.** Determine the oscillation stabilization time of the resonator by checking the characteristics of the resonator to be used.

#### 14.2.2 STOP mode

#### (1) STOP mode setting and operating statuses

The STOP mode is set by executing the STOP instruction.

Caution Because an interrupt request signal is used to clear the standby mode, if there is an interrupt source with the interrupt request flag set and the interrupt mask flag reset, the standby mode is immediately cleared if set. Thus, in the STOP mode, the normal operation mode is restored after the STOP instruction is executed and then the operation is stopped for 34  $\mu$ s (TYP.) (after an additional wait time for stabilizing the oscillation set by the oscillation stabilization time select register (OSTS) has elapsed when crystal/ceramic oscillation is used).

The operating statuses in the STOP mode are shown below.

| Setting of HALT Mode   |                                                                          | Low-Speed Internal                                                                                            | Low-Speed Internal Osc | illator Can Be Stopped <sup>Note</sup>          |  |

|------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------|--|

| Item                   |                                                                          | Oscillator Cannot Be         When Low-Speed Internation           Stopped <sup>№0®</sup> Oscillation Continue |                        | al When Low-Speed Internal<br>Oscillation Stops |  |

| System cloc            | ж                                                                        | Oscillation stops.                                                                                            |                        |                                                 |  |

| CPU                    |                                                                          | Operation stops.                                                                                              |                        |                                                 |  |

| Port (latch)           |                                                                          | Holds status before STOP r                                                                                    | node is set.           |                                                 |  |

| 16-bit timer/          | event counter 00                                                         | Operation stops.                                                                                              |                        |                                                 |  |

| 8-bit timer 80         |                                                                          | Operation stops.                                                                                              |                        |                                                 |  |

| 8-bit timer            | Sets count clock to fxp to fxp/2 <sup>12</sup>                           | Operation stops.                                                                                              |                        |                                                 |  |

| H1                     | Sets count clock to fRL/27                                               | Operable                                                                                                      | Operable               | Operation stops.                                |  |

| Watchdog<br>timer      | "Clock to peripheral hardware" selected as operating clock               | Setting prohibited                                                                                            | Operation stops.       |                                                 |  |

|                        | "Low-speed internal oscillation<br>clock" selected as operating<br>clock | Operable (Operation continues.)                                                                               | Operation stops.       |                                                 |  |

| A/D convert            | er                                                                       | Operation stops.                                                                                              |                        |                                                 |  |

| Serial interface UART6 |                                                                          | Operation stops.                                                                                              |                        |                                                 |  |

| Power-on-clear circuit |                                                                          | Always operates.                                                                                              |                        |                                                 |  |

| Low-voltage detector   |                                                                          | Operable                                                                                                      |                        |                                                 |  |

| External inte          | errupt                                                                   | Operable                                                                                                      |                        |                                                 |  |

#### Table 14-4. Operating Statuses in STOP Mode

**Note** "Cannot be stopped" or "Stopped by software" is selected for low-speed internal oscillator by the option byte (for the option byte, see **CHAPTER 18 OPTION BYTE**).

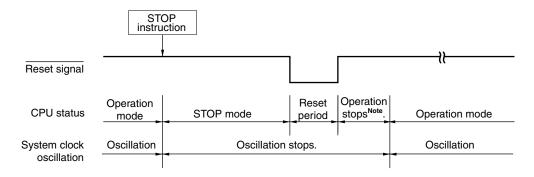

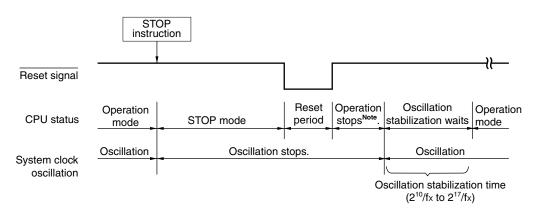

#### (b) Release by reset signal generation

When the reset signal is generated, STOP mode is released and a reset operation is performed after the oscillation stabilization time has elapsed.

#### (1) If CPU clock is high-speed internal oscillation clock or external input clock

**Note** Operation is stopped (277  $\mu$ s (MIN.), 544  $\mu$ s (TYP.), 1.075 ms (MAX.)) because the option byte is referenced.

(2) If CPU clock is crystal/ceramic oscillation clock

- **Note** Operation is stopped (276 μs (MIN.), 544 μs (TYP.), 1.074 ms (MAX.)) because the option byte is referenced.

- Remark fx: System clock oscillation frequency

| Table 14-5. | Operation in Re | sponse to Interru | ipt Request ir | STOP Mode |

|-------------|-----------------|-------------------|----------------|-----------|

|             |                 |                   |                |           |

| Release Source             | MK×× | IE | Operation                          |

|----------------------------|------|----|------------------------------------|

| Maskable interrupt request | 0    | 0  | Next address instruction execution |

|                            | 0    | 1  | Interrupt servicing execution      |

|                            | 1    | ×  | STOP mode held                     |

| Reset signal generation    | _    | ×  | Reset processing                   |

×: don't care

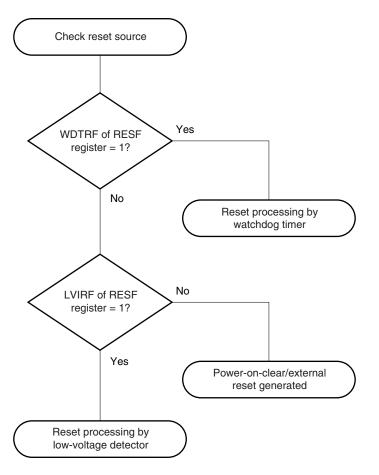

Checking reset source

| ;               |                            |  |  |  |  |  |  |

|-----------------|----------------------------|--|--|--|--|--|--|

| StatusErro      | StatusError:               |  |  |  |  |  |  |

|                 |                            |  |  |  |  |  |  |

| ;               |                            |  |  |  |  |  |  |

| ;END (norm      | al termination processing) |  |  |  |  |  |  |

|                 |                            |  |  |  |  |  |  |

| ,<br>StatusNorm |                            |  |  |  |  |  |  |

|                 |                            |  |  |  |  |  |  |

|                 |                            |  |  |  |  |  |  |

|                 | be written                 |  |  |  |  |  |  |

|                 |                            |  |  |  |  |  |  |

| ,               |                            |  |  |  |  |  |  |

| DataAdrTop      | :                          |  |  |  |  |  |  |

| DB              | ХХН                        |  |  |  |  |  |  |

| DB              | XXH                        |  |  |  |  |  |  |

| DB              | ХХН                        |  |  |  |  |  |  |

| DB              | ХХН                        |  |  |  |  |  |  |

| :               |                            |  |  |  |  |  |  |

| :               |                            |  |  |  |  |  |  |

| DB              | ХХН                        |  |  |  |  |  |  |

| DataAdrBtm      |                            |  |  |  |  |  |  |

|                 | ·                          |  |  |  |  |  |  |

| ,               |                            |  |  |  |  |  |  |

**Remark** Internal verify 2 is used in the above program example. Use internal verify 1 to verify a whole block.

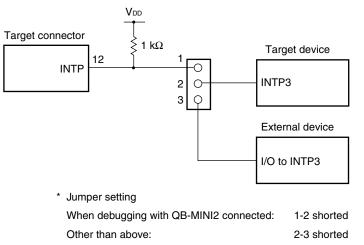

## Figure 20-4. Circuit Connection for the Case Where QB-MINI2 Is Used for Debugging and Debugging of INTP3 Pin Is Performed Only with Real Machine

Caution If debugging is performed with a real machine running, without using QB-MINI2, write the user program using the QB-Programmer. Programs downloaded by the debugger include the monitor program, and such a program malfunctions if it is not controlled via QB-MINI2.

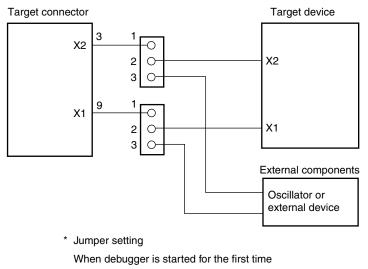

#### 20.1.2 Connection of X1 and X2 pins

The X1 and X2 pins are used when the debugger is started for the first time (when downloading the monitor program) and when programming is performed with the QB-Programmer.

#### Figure 20-5. Circuit Connection for the Case Where X1 and X2 Pins Are Used in Target System

(downloading the monitor program) or when

programming is performed with QB-Programmer: 1-2 shorted Other than above: 2-3 shorted

| ,         |                |                                   |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                             | (2/                                                                                                                                      | /20)          |    |

|-----------|----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------|----|

| Chapter   | Classification | Function                          | Details of<br>Function                                                                                                                                                  | Cautions                                                                                                                                                                                                                                                                                                    | Pag                                                                                                                                      | le            |    |

| Chapter 5 | Soft           | Main clock                        | OSTS: Oscillation<br>stabilization time<br>select register                                                                                                              | To set and then release the STOP mode, set the oscillation stabilization time as follows.<br>Expected oscillation stabilization time of resonator ≤ Oscillation stabilization time set by OSTS                                                                                                              | p.77                                                                                                                                     |               |    |

|           |                |                                   |                                                                                                                                                                         | The wait time after the STOP mode is released does not include the time from the release of the STOP mode to the start of clock oscillation ("a" in the figure below), regardless of whether STOP mode was released by reset signal generation or interrupt generation.                                     | p.77                                                                                                                                     |               |    |

|           |                |                                   |                                                                                                                                                                         | The oscillation stabilization time that elapses on power application or after release of reset is selected by the option byte. For details, refer to CHAPTER 18 OPTION BYTE.                                                                                                                                | p.77                                                                                                                                     |               |    |

|           | Hard           | Crystal/<br>ceramic<br>oscillator | _                                                                                                                                                                       | <ul> <li>When using the crystal/ceramic oscillator, wire as follows in the area enclosed by the broken lines in Figure 5-6 to avoid an adverse effect from wiring capacitance.</li> <li>Keep the wiring length as short as possible.</li> </ul>                                                             | p.78                                                                                                                                     |               |    |

|           |                |                                   |                                                                                                                                                                         | <ul> <li>Do not cross the wiring with the other signal lines. Do not route the wiring<br/>near a signal line through which a high fluctuating current flows.</li> </ul>                                                                                                                                     |                                                                                                                                          |               |    |

|           |                |                                   |                                                                                                                                                                         | <ul> <li>Always make the ground point of the oscillator capacitor the same potentia<br/>as Vss. Do not ground the capacitor to a ground pattern through which a<br/>high current flows.</li> </ul>                                                                                                          |                                                                                                                                          |               |    |

|           |                |                                   |                                                                                                                                                                         | Do not fetch signals from the oscillator.                                                                                                                                                                                                                                                                   |                                                                                                                                          |               |    |

| Chapter 6 | Hard           | 16-bit<br>timer/event             | TM00: 16-bit<br>timer counter 00                                                                                                                                        | Even if TM00 is read, the value is not captured by CR010.                                                                                                                                                                                                                                                   | pp.<br>90, 12                                                                                                                            | □<br>22       |    |

| Ch        |                | counter 00                        | counter 00                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             | When TM00 is read, count misses do not occur, since the input of the count clock is temporarily stopped and then resumed after the read. | pp.<br>90, 12 | 22 |

|           | Soft           | 201                               | CR000: 16-bit<br>timer capture/<br>compare register                                                                                                                     | Set CR000 to other than 0000H in the clear & start mode entered on match<br>between TM00 and CR000. This means a 1-pulse count operation cannot be<br>performed when this register is used as an external event counter.                                                                                    | pp.<br>91, 12                                                                                                                            | 22            |    |

|           |                |                                   |                                                                                                                                                                         | TI000 pin, if CR000 is set to 0000H, an interrupt request (INTTM000) is                                                                                                                                                                                                                                     | generated when CR000 changes from 0000H to 0001H following overflow                                                                      | pp.<br>91, 12 | 22 |

|           |                |                                   | (TM00), TM00 continues counting, overflows, and then starts counting again. If the new value of CR000 is less than the old value, therefore, the starts counting again. | If the new value of CR000 is less than the value of 16-bit timer counter 0 (TM00), TM00 continues counting, overflows, and then starts counting from 0 again. If the new value of CR000 is less than the old value, therefore, the timer must be reset to be restarted after the value of CR000 is changed. | pp.<br>91, 12                                                                                                                            | 22            |    |

|           |                |                                   |                                                                                                                                                                         | The value of CR000 after 16-bit timer/event counter 00 has stopped is not guaranteed.                                                                                                                                                                                                                       | pp.<br>91, 12                                                                                                                            | □<br>23       |    |

|           | Hard           |                                   |                                                                                                                                                                         | The capture operation may not be performed for CR000 set in compare mode even if a capture trigger is input.                                                                                                                                                                                                | pp.<br>91, 12                                                                                                                            |               |    |

|           |                |                                   |                                                                                                                                                                         | When using P31 as the input pin (TI010) of the valid edge, it cannot be used as a timer output pin (TO00). When using P31 as the timer output pin (TO00), it cannot be used as the input pin (TI010) of the valid edge.                                                                                     | pp.<br>91, 12                                                                                                                            |               |    |

|           |                |                                     | Γ                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (6/20)            |

|-----------|----------------|-------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Chapter   | Classification | Function                            | Details of<br>Function                                    | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page              |

| Chapter 6 | Hard           | 16-bit<br>timer/event<br>counter 00 | One-shot pulse<br>output with<br>external trigger         | Do not input the external trigger again while the one-shot pulse is being<br>output. To output the one-shot pulse again, wait until the current one-shot<br>pulse output is completed.                                                                                                                                                                                                                                                                                    | рр. 🗌<br>119, 124 |

| 0         | Soft           |                                     |                                                           | Do not set 0000H to the CR000 and CR010 registers.                                                                                                                                                                                                                                                                                                                                                                                                                        | pp. 🗌<br>120, 124 |

|           |                |                                     |                                                           | 16-bit timer counter 00 starts operating as soon as a value other than 00 (operation stop mode) is set to the TMC003 and TMC002 bits.                                                                                                                                                                                                                                                                                                                                     | рр. 🗌<br>121, 122 |

|           | Hard           |                                     | Timer start errors                                        | An error of up to one clock may occur in the time required for a match signal to be generated after timer start. This is because 16-bit timer counter 00 (TM00) is started asynchronously to the count clock.                                                                                                                                                                                                                                                             | p.122 🗌           |

|           | Soft           |                                     | One-shot pulse<br>output                                  | One-shot pulse output normally operates only in the free-running mode or in the clear & start mode at the valid edge of the TI000 pin. Because an overflow does not occur in the clear & start mode on a match between TM00 and CR000, one-shot pulse output is not possible.                                                                                                                                                                                             | p.123 🗌           |

|           |                |                                     | Capture operation                                         | If both the rising and falling edges are selected as the valid edges of the TI000 pin, capture is not performed.                                                                                                                                                                                                                                                                                                                                                          | p.125 🗌           |

|           |                |                                     |                                                           | When the CRC001 bit value is 1, the TM00 count value is not captured in the CR000 register when a valid edge of the Tl010 pin is detected, but the input from the Tl010 pin can be used as an external interrupt source because INTTM000 is generated at that timing.                                                                                                                                                                                                     | p.125 🗌           |

|           |                |                                     | Changing<br>compare register<br>during timer<br>operation | With the 16-bit timer capture/compare register 0n0 (CR0n0) used as a compare register, when changing CR0n0 around the timing of a match between 16-bit timer counter 00 (TM00) and 16-bit timer capture/compare register 0n0 (CR0n0) during timer counting, the change timing may conflict with the timing of the match, so the operation is not guaranteed in such cases. To change CR0n0 during timer counting, follow the procedure below using an INTTM000 interrupt. | p.126 🗌           |

|           |                |                                     |                                                           | If CR010 is changed during timer counting without performing processing <1><br>above, the value in CR010 may be rewritten twice or more, causing an<br>inversion of the output level of the TO00 pin at each rewrite.                                                                                                                                                                                                                                                     | p.126 🗌           |

|           |                |                                     | External event counter                                    | The timing of the count start is after two valid edge detections.                                                                                                                                                                                                                                                                                                                                                                                                         | p.127 🗌           |

|           | Hard           |                                     | External clock<br>limitation                              | When using an input pulse of the TI000 pin as a count clock (external trigger), be sure to input the pulse width which satisfies the AC characteristics. For the AC characteristics, refer to CHAPTER 22 and CHAPTER 23 ELECTRICAL SPECIFICATIONS.                                                                                                                                                                                                                        | p.128 🗌           |

|           |                |                                     |                                                           | When an external waveform is input to 16-bit timer/event counter 00, it is sampled by the noise limiter circuit and thus an error occurs on the timing to become valid inside the device.                                                                                                                                                                                                                                                                                 | p.128 🗌           |

| Chapter 7 | Soft           | 8-bit timer<br>80                   | CR80: 8-bit<br>compare register<br>80                     | When changing the value of CR80, be sure to stop the timer operation. If the value of CR80 is changed with the timer operation enabled, a match interrupt request signal is generated immediately and the timer may be cleared.                                                                                                                                                                                                                                           | p.131 🗌           |

|           |                |                                     | TMC80: 8-bit<br>timer mode                                | Be sure to set TMC80 after stopping the timer operation.                                                                                                                                                                                                                                                                                                                                                                                                                  | p.132 🗌           |

|           |                |                                     | control register<br>80                                    | Be sure to clear bits 0 and 6 to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                       | p.132 🗌           |

|            |                |                  | •                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (8/20)                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                   |         |

|------------|----------------|------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Chapter    | Classification | Function         | Details of<br>Function                                                                                    | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                   |         |

| er 9       | Soft           | Watchdog         | WDTM:                                                                                                     | WDTM cannot be set by a 1-bit memory manipulation instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p.155 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

| Chapter 9  | ••             | timer            | Watchdog timer<br>mode register                                                                           | When using the flash memory programming by self programming, set the overflow time for the watchdog timer so that enough overflow time is secured (Example 1-byte writing: 200 $\mu$ s MIN., 1-block deletion: 10 ms MIN.).                                                                                                                                                                                                                                                                                         | p.155 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                |                  | WDTE:<br>Watchdog timer                                                                                   | If a value other than ACH is written to WDTE, an internal reset signal is generated.                                                                                                                                                                                                                                                                                                                                                                                                                                | p.155 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                |                  | enable register                                                                                           | If a 1-bit memory manipulation instruction is executed for WDTE, an internal reset signal is generated.                                                                                                                                                                                                                                                                                                                                                                                                             | p.155 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                |                  |                                                                                                           | The value read from WDTE is 9AH (this differs from the written value (ACH)).                                                                                                                                                                                                                                                                                                                                                                                                                                        | p.155 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            | Hard           |                  | When "low-speed<br>internal oscillator<br>cannot be<br>stopped" is<br>selected by<br>option byte          | In this mode, operation of the watchdog timer cannot be stopped even during STOP instruction execution. For 8-bit timer H1 (TMH1), a division of the low-speed internal oscillation clock can be selected as the count source, so clear the watchdog timer using the interrupt request of TMH1 before the watchdog timer overflows after STOP instruction execution. If this processing is not performed, an internal reset signal is generated when the watchdog timer overflows after STOP instruction execution. | p.156 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                |                  | When "low-speed<br>internal oscillator<br>can be stopped<br>by software" is<br>selected by<br>option byte | In this mode, watchdog timer operation is stopped during HALT/STOP instruction execution. After HALT/STOP mode is released, counting is started again using the operation clock of the watchdog timer set before HALT/STOP instruction execution by WDTM. At this time, the counter is not cleared to 0 but holds its value.                                                                                                                                                                                        | p.158 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

| Chapter 10 | Soft           | A/D<br>converter | Sampling time<br>and conversion<br>time                                                                   | The above sampling time and conversion time do not include the clock frequency error. Select the sampling time and conversion time such that Notes 2 and 3 above are satisfied, while taking the clock frequency error into consideration (an error margin maximum of $\pm 5\%$ when using the high-speed internal oscillator).                                                                                                                                                                                     | p.164 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                |                  |                                                                                                           | ADM: A/D<br>converter mode<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The above sampling time and conversion time do not include the clock frequency error. Select the sampling time and conversion time such that Notes 3 and 4 above are satisfied, while taking the clock frequency error into consideration (an error margin maximum of $\pm 5\%$ when using the high-speed internal oscillator). | p.169 🗌                                                                                                                                                                                                                           |         |

|            |                |                  |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                 | If a bit other than ADCS of ADM is manipulated while A/D conversion is stopped (ADCS = 0) and then A/D conversion is started, execute two NOP instructions or an instruction equivalent to two machine cycles, and set ADCS to 1. | p.170 🗌 |

|            |                |                  |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A/D conversion must be stopped (ADCS = 0) before rewriting bits FR0 to FR2.                                                                                                                                                                                                                                                     | p.170 🗌                                                                                                                                                                                                                           |         |

|            |                |                  |                                                                                                           | Be sure to clear bits 6, 2, and 1 to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | p.170 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                |                  | ADS: Analog<br>input channel<br>specification<br>register                                                 | Be sure to clear bits 2 to 7 of ADS to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | p.170 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                |                  | ADCR: 10-bit A/D<br>conversion result<br>register                                                         | When writing to the A/D converter mode register (ADM) and analog input channel specification register (ADS), the contents of ADCR may become undefined. Read the conversion result following conversion completion before writing to ADM and ADS. Using timing other than the above may cause an incorrect conversion result to be read.                                                                                                                                                                            | p.170 🗌                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                   |         |

|            |                     |                              |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (10/20) |

|------------|---------------------|------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Chapter    | Classification      | Function                     | Details of<br>Function                                               | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page    |

| Chapter 10 | Hard                | A/D<br>converter             | Input impedance<br>of ANI0 to ANI3<br>pins                           | In this A/D converter, the internal sampling capacitor is charged and sampling is performed during sampling time.<br>Since only the leakage current flows other than during sampling and the current for charging the capacitor also flows during sampling, the input impedance fluctuates both during sampling and otherwise.<br>If the shortest conversion time of the reference voltage is used, to perform sufficient sampling, it is recommended to make the output impedance of the analog input source 1 k $\Omega$ or lower, or attach a capacitor of around 0.01 $\mu$ F to 0.1 $\mu$ F to the ANI0 to ANI3 pins (see Figure 10-19). | p.180 🗌 |

|            | Soft                |                              | ADIF: Interrupt<br>request flag                                      | The interrupt request flag (ADIF) is not cleared even if the analog input channel specification register (ADS) is changed.<br>Therefore, if an analog input pin is changed during A/D conversion, the A/D conversion result and ADIF for the pre-change analog input may be set just before the ADS rewrite. Caution is therefore required since, at this time, when ADIF is read immediately after the ADS rewrite, ADIF is set despite the fact A/D conversion for the post-change analog input has not ended.<br>When A/D conversion is stopped and then resumed, clear ADIF before the A/D conversion is resumed.                         | p.180 🗌 |

|            |                     |                              | Conversion<br>results just after<br>A/D conversion<br>start          | The first A/D conversion value immediately after A/D conversion starts may<br>not fall within the rating range if the ADCS bit is set to 1 within 1 $\mu$ s after the<br>ADCE bit was set to 1, or if the ADCS bit is set to 1 with the ADCE bit = 0.<br>Take measures such as polling the A/D conversion end interrupt request<br>(INTAD) and removing the first conversion result.                                                                                                                                                                                                                                                          | p.181 🗌 |

|            |                     |                              | A/D conversion<br>result register<br>(ADCR, ADCRH)<br>read operation | When a write operation is performed to the A/D converter mode register (ADM) and analog input channel specification register (ADS), the contents of ADCR and ADCRH may become undefined. Read the conversion result following conversion completion before writing to ADM and ADS. Using a timing other than the above may cause an incorrect conversion result to be read.                                                                                                                                                                                                                                                                   | p.181 🗌 |

|            | Hard                |                              | Operating current<br>at conversion<br>waiting mode                   | The DC characteristic of the operating current during the STOP mode is not satisfied due to the conversion waiting mode (only the comparator consumes power), when bit 7 (ADCS) and bit 0 (ADCE) of the A/D converter mode register (ADM) are set to 0 and 1 respectively.                                                                                                                                                                                                                                                                                                                                                                    | p.181 🗌 |