Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

#### Details

ĿXFI

| Decalis                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Active                                                                       |

| Applications            | Automotive                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                              |

| Program Memory Type     | FLASH (64kB)                                                                 |

| Controller Series       | -                                                                            |

| RAM Size                | 6K x 8                                                                       |

| Interface               | LIN, SSI, UART                                                               |

| Number of I/O           | 10                                                                           |

| Voltage - Supply        | 5.5V ~ 28V                                                                   |

| Operating Temperature   | -40°C ~ 175°C                                                                |

| Mounting Type           | Surface Mount                                                                |

| Package / Case          | 48-VFQFN Exposed Pad                                                         |

| Supplier Device Package | PG-VQFN-48-29                                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/tle9877qxw40xuma1 |

|                         |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Device Pinout and Pin Configuration**

| Symbol        | Pin Number | Туре | Reset<br>State <sup>1)</sup> | Function                                                                                                                                                                     |                                                                      |  |  |  |  |

|---------------|------------|------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

| P2            |            |      |                              | Port 2<br>Port 2 is a 5-bit general purpose input-only port.<br>Alternate functions can be assigned and are listed in the Por<br>description. Main function is listed below. |                                                                      |  |  |  |  |

| P2.0/XTAL1    | 29         | 1/1  | I                            | AN0                                                                                                                                                                          | ADC analog input 0<br>Alternate function mapping see <b>Table 10</b> |  |  |  |  |

| P2.2/XTAL2    | 30         | I/O  | I                            | AN2                                                                                                                                                                          | ADC analog input 2<br>Alternate function mapping see <b>Table 10</b> |  |  |  |  |

| P2.3          | 35         | I    | I                            | AN3                                                                                                                                                                          | ADC analog input 3<br>Alternate function mapping see <b>Table 10</b> |  |  |  |  |

| P2.4          | 32         | I    | I                            | AN4                                                                                                                                                                          | ADC analog input 4<br>Alternate function mapping see <b>Table 10</b> |  |  |  |  |

| P2.5          | 31         | I    | I                            | AN5                                                                                                                                                                          | ADC analog input 5<br>Alternate function mapping see <b>Table 10</b> |  |  |  |  |

| Power Supply  | /          |      |                              | 1                                                                                                                                                                            |                                                                      |  |  |  |  |

| VS            | 45         | Р    | -                            | Battery su                                                                                                                                                                   | ipply input                                                          |  |  |  |  |

| VDDP          | 40         | Р    | _                            | <sup>2)</sup> I/O port supply (5.0 V). Connect external buffer capacitor.                                                                                                    |                                                                      |  |  |  |  |

| VDDC          | 38         | Ρ    | -                            | <sup>3)</sup> Core supply (1.5 V during Active Mode).<br>Do not connect external loads, connect external buffer<br>capacitor.                                                |                                                                      |  |  |  |  |

| VDDEXT        | 41         | Р    | _                            | External voltage supply output (5.0 V, 20 mA)                                                                                                                                |                                                                      |  |  |  |  |

| GND           | 19         | Р    | _                            | GND digit                                                                                                                                                                    | al                                                                   |  |  |  |  |

| GND           | 28         | Р    | _                            | GND digit                                                                                                                                                                    | al                                                                   |  |  |  |  |

| GND           | 39         | Р    | _                            | GND anal                                                                                                                                                                     | og                                                                   |  |  |  |  |

| Monitor Input |            |      | -                            | 4                                                                                                                                                                            |                                                                      |  |  |  |  |

| MON           | 14         | I    | _                            | High Volta                                                                                                                                                                   | age Monitor Input                                                    |  |  |  |  |

| LIN Interface | 1          |      |                              |                                                                                                                                                                              |                                                                      |  |  |  |  |

| LIN           | 43         | I/O  | _                            | LIN bus ir                                                                                                                                                                   | terface input/output                                                 |  |  |  |  |

| GND_LIN       | 42         | Р    | _                            | LIN groun                                                                                                                                                                    | d                                                                    |  |  |  |  |

| Charge Pump   | )          |      |                              |                                                                                                                                                                              |                                                                      |  |  |  |  |

| CP1H          | 48         | Р    | _                            | Charge P                                                                                                                                                                     | ump Capacity 1 High, connect external C                              |  |  |  |  |

| CP1L          | 1          | Р    | -                            | Charge P                                                                                                                                                                     | ump Capacity 1 Low, connect external C                               |  |  |  |  |

| CP2H          | 3          | Р    | -                            | Charge P                                                                                                                                                                     | ump Capacity 2 High, connect external C                              |  |  |  |  |

| CP2L          | 4          | Р    | -                            | Charge P                                                                                                                                                                     | ump Capacity 2 Low, connect external C                               |  |  |  |  |

| VCP           | 2          | Р    | -                            | Charge P                                                                                                                                                                     | ump Capacity                                                         |  |  |  |  |

| VSD           | 47         | Р    | -                            | Battery su                                                                                                                                                                   | ipply input for Charge Pump                                          |  |  |  |  |

| MOSFET Driv   | er         |      |                              | •                                                                                                                                                                            |                                                                      |  |  |  |  |

| VDH           | 44         | Р    | _                            | Voltage D                                                                                                                                                                    | rain High Side MOSFET Driver                                         |  |  |  |  |

| SH3           | 46         | Р    | -                            | Source Hi                                                                                                                                                                    | gh Side FET 3                                                        |  |  |  |  |

| SH2           | 6          | Р    | _                            | Source Hi                                                                                                                                                                    | gh Side FET 2                                                        |  |  |  |  |

#### **Modes of Operation**

# 4 Modes of Operation

This highly integrated circuit contains analog and digital functional blocks. An embedded 32-bit microcontroller is available for system and interface control. On-chip, low-dropout regulators are provided for internal and external power supply. An internal oscillator provides a cost effective clock that is particularly well suited for LIN communications. A LIN transceiver is available as a communication interface. Driver stages for a Motor Bridge or BLDC Motor Bridge with external MOSFET are integrated, featuring PWM capability, protection features and a charge pump for operation at low supply voltage. A 10-bit SAR ADC is implemented for high precision sensor measurement. An 8-bit ADC is used for diagnostic measurements.

The Micro Controller Unit supervision and system protection (including a reset feature) is complemented by a programmable window watchdog. A cyclic wake-up circuit, supply voltage supervision and integrated temperature sensors are available on-chip.

All relevant modules offer power saving modes in order to support automotive applications connected to terminal 30. A wake-up from power-save mode is possible via a LIN bus message, via the monitoring input or using a programmable time period (cyclic wake-up).

Featuring LTI, the integrated circuit is available in a VQFN-48-29 package with 0.5 mm pitch, and is designed to withstand the severe conditions of automotive applications.

The TLE9877QXW40 has several operation modes mainly to support low power consumption requirements.

### **Reset Mode**

The Reset Mode is a transition mode used e.g. during power-up of the device after a power-on reset, or after wakeup from Sleep Mode. In this mode, the on-chip power supplies are enabled and all other modules are initialized. Once the core supply VDDC is stable, the device enters Active Mode. If the watchdog timer WDT1 fails more than four times, the device performs a fail-safe transition to Sleep Mode.

### Active Mode

In Active Mode, all modules are activated and the TLE9877QXW40 is fully operational.

### Stop Mode

Stop Mode is one of two major low power modes. The transition to the low power modes is performed by setting the corresponding bits in the mode control register. In Stop Mode the embedded microcontroller is still powered, allowing faster wake-up response times. Wake-up from this mode is possible through LIN bus activity, by using the high-voltage monitoring pin or the corresponding 5V GPIOs.

### Stop Mode with Cyclic Wake-Up

The Cyclic Wake-Up Mode is a special operating mode of the Stop Mode. The transition to the Cyclic Wake-Up Mode is done by first setting the corresponding bits in the mode control register followed by the Stop Mode command. In addition to the cyclic wake-up behavior (wake-up after a programmable time period), asynchronous wake events via the activated sources (LIN and/or MON) are available, as in normal Stop Mode.

### Sleep Mode

The Sleep Mode is a low-power mode. The transition to the low-power mode is done by setting the corresponding bits in the MCU mode control register or in case of failure, see below. In Sleep Mode the embedded microcontroller power supply is deactivated allowing the lowest system power consumption. A wake-up from this mode is possible by LIN bus activity, the High Voltage Monitor Input pin or Cyclic Wake-up.

### Sleep Mode in Case of Failure

Power Management Unit (PMU)

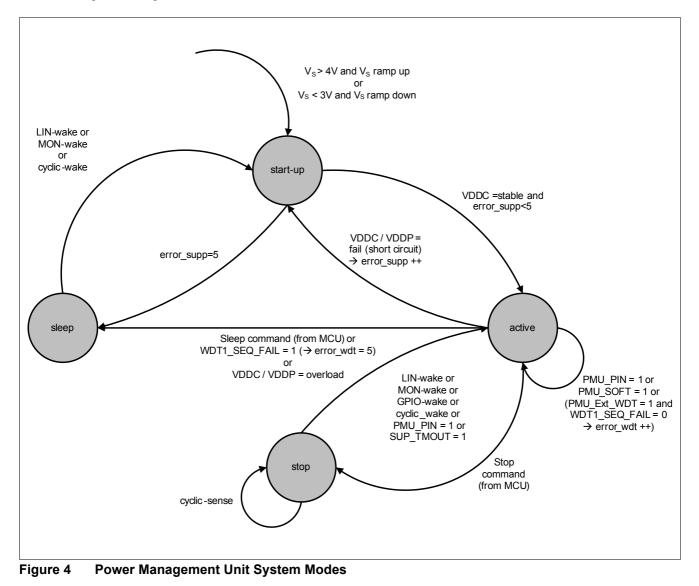

# 5.2.2 PMU Modes Overview

The following state diagram shows the available modes of the device.

### Power Management Unit (PMU)

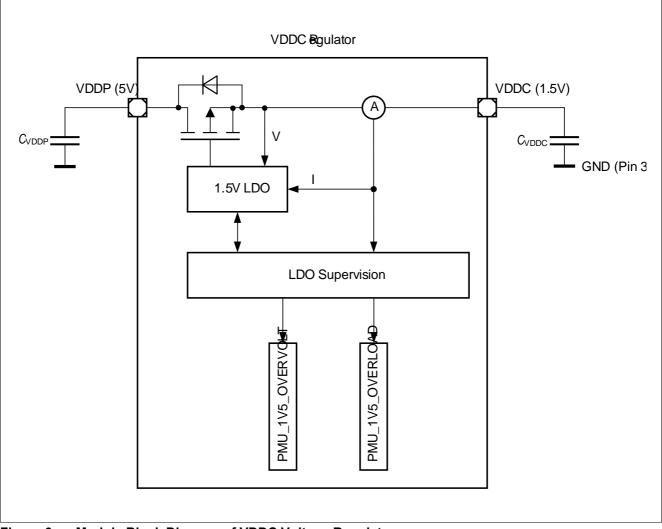

# 5.3.2 Voltage Regulator 1.5V (VDDC)

This module represents the 1.5 V voltage regulator, which provides the supply for the microcontroller core, the digital peripherals and other internal analog 1.5 V functions (e.g. ADC2) of the chip. To further reduce the current consumption of the MCU during Stop Mode the output voltage can be lowered to 1.1 V.

## Features

- 1.5 V low-drop voltage regulator

- Overcurrent monitoring and shutdown with MCU signaling (interrupt)

- Overvoltage monitoring with MCU signaling (interrupt)

- Undervoltage monitoring with MCU signaling (interrupt)

- Undervoltage monitoring with reset

- Pull Down Current Source at the output for Sleep Mode only (typ. 100 A)

The output capacitor  $C_{\mbox{\scriptsize VDDC}}$  is mandatory to ensure a proper regulator functionality.

Figure 6 Module Block Diagram of VDDC Voltage Regulator

## System Control Unit - Digital Modules (SCU-DM)

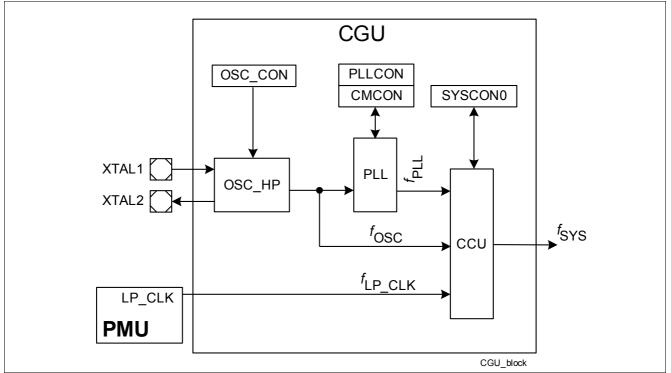

## Figure 9 Clock Generation Unit Block Diagram

The following sections describe the different parts of the CGU.

# 6.3.1 Low Precision Clock

The clock source LP\_CLK is a low-precision RC oscillator (LP-OSC) with a nominal frequency of 18 MHz that is enabled by hardware as an independent clock source for the TLE9877QXW40 startup after reset and during the power-down wake-up sequence.  $f_{LP \ CLK}$  is not user configurable.

# 6.3.2 High Precision Oscillator Circuit (OSC\_HP)

The high precision oscillator circuit, designed to work with both an external crystal oscillator or an external stable clock source, consists of an inverting amplifier with XTAL1 as the input, and XTAL2 as the output.

**Figure 10** shows the recommended external circuitry for both operating modes, External Crystal Mode and External Input Clock Mode.

# 6.3.2.1 External Input Clock Mode

When supplying the clock signal directly, not using an external crystal and bypassing the oscillator, the input frequency needs to be equal or greater than 4 MHz if the PLL VCO part is used.

When using an external clock signal it must be connected to XTAL1. XTAL2 is left open (unconnected).

## 6.3.2.2 External Crystal Mode

When using an external crystal, its frequency can be within the range of 4 MHz to 25 MHz. An external oscillator load circuitry must be used, connected to both pins, XTAL1 and XTAL2. It normally consists of the two load capacitances C1 and C2. A series damping resistor could be required for some crystals. The exact values and the corresponding operating ranges depend on the crystal and have to be determined and optimized in cooperation with the crystal vendor using the negative resistance method. The following load cap values can be used as starting point for the evaluation:

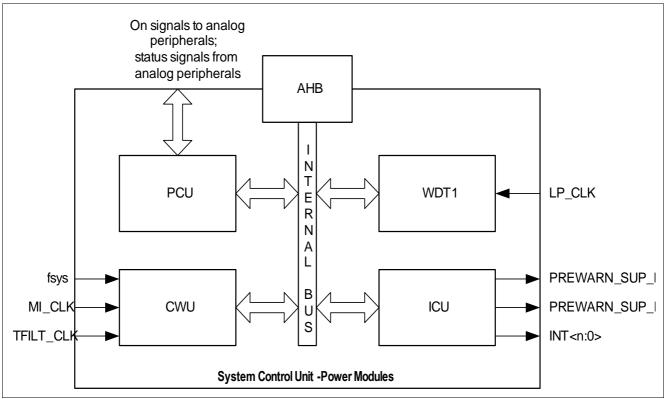

System Control Unit - Power Modules (SCU-PM)

# 7 System Control Unit - Power Modules (SCU-PM)

# 7.1 Features

- Clock Watchdog Unit (CWU): supervision of all clocks with NMI signaling relevant to power modules

- · Interrupt Control Unit (ICU): all interrupt flags and status flags with system relevance

- Power Control Unit (PCU): takes over control when device enters and exits Sleep and Stop Mode

- External Watchdog (WDT1): independent system watchdog for monitoring system activity

# 7.2 Introduction

## 7.2.1 Block Diagram

The System Control Unit of the power modules consists of the sub-modules in the figure shown below:

## AHB (Advanced High-Performance Bus)

## CWU (Clock Watchdog Unit)

- f<sub>sys</sub> system frequency: PLL output

- MI\_CLK measurement interface clock (analog clock): derived from fsys using division factors 1/2/3/4

- TFILT\_CLK clock used for digital filters: derived from fsys using configurable division factors

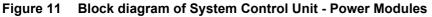

### Address Space Organization

# 10 Address Space Organization

The TLE9877QXW40 manipulates operands in the following memory spaces:

- 64 KByte of Flash memory in code space

- 32 KByte Boot ROM memory in code space (used for boot code and IP storage)

- 6 KByte RAM memory in code space and data space (RAM can be read/written as program memory or external data memory)

- Special function registers (SFRs) in peripheral space

The figure below shows the detailed address alignment of TLE9877QXW40:

Figure 14 TLE9877QXW40 Memory Map

**GPIO Ports and Peripheral I/O**

## 14.3 TLE9877QXW40 Port Module

14.3.1 Port 0

## 14.3.1.1 Port 0 Functions

## Table 8 Port 0 Input/Output Functions

| Port Pin | Input/Output | Select | Connected Signal(s) | From/to Module  |

|----------|--------------|--------|---------------------|-----------------|

| P0.0     | Input        | GPI    | P0_DATA.P0          |                 |

|          |              | INP1   | SWCLK / TCK_0       | SW              |

|          |              | INP2   | T12HR_0             | CCU6            |

|          |              | INP3   | T4INA               | GPT12T4         |

|          |              | INP4   | T2_0                | Timer 2         |

|          |              | INP5   | -                   | -               |

|          |              | INP6   | EXINT2_3            | SCU             |

|          | Output       | GPO    | P0_DATA.P0          |                 |

|          |              | ALT1   | T3OUT               | GPT12T3         |

|          |              | ALT2   | EXF21_0             | Timer 21        |

|          |              | ALT3   | RXDO_2              | UART2           |

| P0.1     | Input        | GPI    | P0_DATA.P1          |                 |

|          |              | INP2   | T13HR_0             | CCU6            |

|          |              | INP3   | TxD1                | LIN_TxD         |

|          |              | INP4   | CAPINA              | GPT12CAP        |

|          |              | INP5   | T21_0               | Timer 21        |

|          |              | INP6   | T4INC               | GPT12T4         |

|          |              | INP7   | MRST_1_2            | SSC1            |

|          |              | INP8   | EXINT0_2            | SCU             |

|          | Output       | GPO    | P0_DATA.P1          |                 |

|          |              | ALT1   | TxD1                | UART1 / LIN_TxD |

|          |              | ALT2   | -                   | -               |

|          |              | ALT3   | T6OUT               | GPT12T6         |

**Timer2 and Timer21**

# 16 Timer2 and Timer21

## 16.1 Features

- 16-bit auto-reload mode

- selectable up or down counting

- One channel 16-bit capture mode

## 16.2 Introduction

The timer modules are general-purpose 16-bit timers. Timer 2/21 can function as a timer or counter in each of its modes. As a timer, it counts with an input clock of  $f_{PCLK}/12$  (if prescaler is disabled). As a counter, Timer 2 counts 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is  $f_{PCLK}/24$  (if prescaler is disabled).

# 16.2.1 Timer2 and Timer21 Modes Overview

| Mode            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Auto-reload     | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmable reload value in register RC2</li> <li>Interrupt is generated with reload events.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Auto-reload     | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up         <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmable reload value in register RC2</li> </ul> </li> <li>Count down         <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by the start of the start counting from FFFF<sub>H</sub>, underflow condition</li> <li>Reload event triggered by the start counting from FFFF<sub>H</sub>, underflow condition</li> <li>Reload event triggered by the start counting from FFFF<sub>H</sub>, underflow condition</li> </ul> </li> </ul> |  |  |  |  |  |  |  |

| Channel capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated by reload or capture events</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

## Table 11 Timer2 and Timer21 Modes

| Timer3 |

|--------|

|        |

| Mode | Sub-<br>Mode    | Operation                                                                                                                                                                                                                                                                                                            |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | No Sub-<br>Mode | <b>8-bit Timer with auto-reload</b><br>The timer register TL3 is reloaded with a user-defined 8-bit value in TH3 upon overflow.                                                                                                                                                                                      |

| 3    | а               | <b>Timer3 operates as two 8-bit timers</b><br>The timer registers TL3 and TH3, operate as two separate 8-bit counters.                                                                                                                                                                                               |

| 3    | b               | <b>Timer3 operates as Two 8-bit timers for clock measurement</b><br>The timer registers, TL3 and TH3 operate as two separate 8-bit counters. In this mode the LP_CLK2 Low Power Clock can be measured. TL3 acts as an edge counter for the clock edges and TH3 as a counter which counts the time between the edges. |

# TLE9877QXW40

**Application Information**

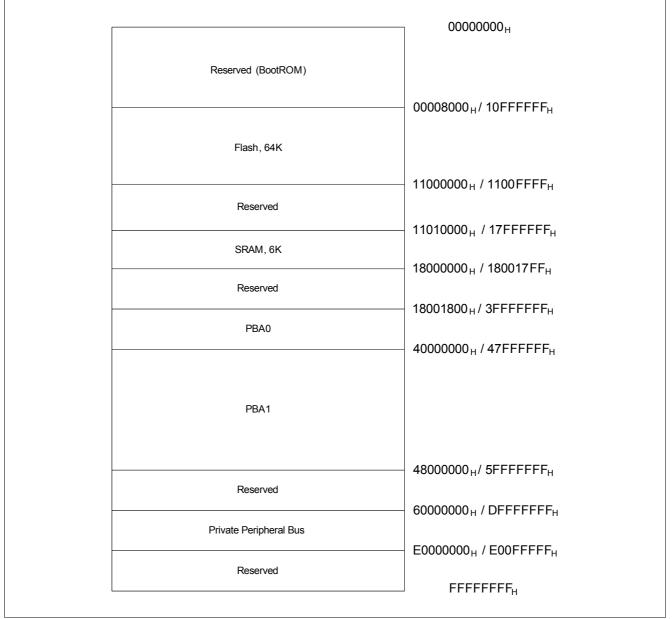

# 28 Application Information

# 28.1 BLDC Driver

**Figure 32** shows the TLE9877QXW40 in an electric drive application setup controlling a BLDC motor. Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 32 Simplified Application Diagram Example

Note: This is a very simplified example of an application circuit and bill of materials. The function must be verified in the actual application.

- 4) Min voltage -2.8V with external 1k series resistor only.

- 5) To achieve max. ratings on this pin, Parameter P\_1.1.44 has to be taken into account resulting in the following dependency:  $V_{GH} < V_{SH} + V_{GHvsSH}$  min and additionally  $V_{SH} < V_{GH} + 0.3V$ .

- 6) To achieve max. ratings on this pin, Parameter P\_1.1.45 has to be taken into account resulting in the following dependency:  $V_{GL} < V_{SL} + V_{GLvsSL\_min}$  and additionally  $V_{SL} < V_{GL} + 0.3V$ .

- 7) These limits can be kept if max current drawn out of pin does not exceed limit of 200  $\mu A.$

- 8) See XTAL parameter specification, when GPIOs (Port Pin P2.0 and P2.2) are used as XTAL.

- 9) Includes TMS and RESET.

- 10) Maximum rating for injection current of GPIO with  $V_{IN}$  respected.

- 11) ESD susceptibility HBM according to ANSI/ESDA/JEDEC JS-001 (1.5k , 100pF)

- 12) MON with external circuitry of a series resistor of 3.9k and 10nF (at connector); VS with an external ceramic capacitor of 100nF; VSD with an external capacitor of 470nF; VDH with external circuitry of a series resistor of 1k and 3.3nF (at pin).

- 13) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JESD22-C101F

#### Notes

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

## 29.4 Flash Memory

This chapter includes the parameters for the 64 kByte embedded flash module.

# 29.4.1 Flash Parameters

### Table 29 Flash Characteristics<sup>1)</sup>

$V_s$  = 3.0 V to 28 V,  $T_j$  = -40 °C to +175 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                | Symbol                 | Values |                 |      | Unit    | Note /                                                      | Number   |

|------------------------------------------|------------------------|--------|-----------------|------|---------|-------------------------------------------------------------|----------|

|                                          |                        | Min.   | Тур.            | Max. |         | Test Condition                                              |          |

| Programming time per 128 byte page       | t <sub>PR</sub>        | _      | 3 <sup>2)</sup> | 3.5  | ms      | 3V < V <sub>S</sub> < 28V                                   | P_4.1.1  |

| Erase time per sector/page               | t <sub>ER</sub>        | _      | 4 <sup>2)</sup> | 4.5  | ms      | 3V < V <sub>S</sub> < 28V                                   | P_4.1.2  |

| Data retention time                      | t <sub>RET</sub>       | 20     | -               | -    | years   | 1,000 erase /<br>program cycles                             | P_4.1.3  |

| Data retention time                      | t <sub>RET</sub>       | 50     | -               | -    | years   | 1,000 erase /<br>program cycles<br>$T_j = 30^{\circ}C^{3)}$ | P_4.1.9  |

| Flash erase endurance for user sectors   | N <sub>ER</sub>        | 30     | -               | -    | kcycles | Data retention time 5 years                                 | P_4.1.4  |

| Flash erase endurance for security pages | N <sub>SEC</sub>       | 10     | -               | -    | cycles  | <sup>4)</sup> Data retention<br>time 20 years               | P_4.1.5  |

| Drain disturb limit                      | N <sub>DD</sub>        | 32     | -               | -    | kcycles | 5)                                                          | P_4.1.6  |

| Junction temperature range 1             | T <sub>j_extend_</sub> | -40    | -               | 150  | °C      |                                                             | P_4.1.10 |

| Junction temperature range 2             | T <sub>j_extend_</sub> | -40    | -               | 165  | °C      | <sup>1)</sup> incl. Flash<br>erase/write/rea<br>d           | P_4.1.11 |

| Junction temperature range 3             | T <sub>j_extend_</sub> | 165    | -               | 175  | °C      | <sup>1)</sup> incl. Flash<br>read                           | P_4.1.12 |

1) Not subject for production test, specified by design.

2) Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. The requirement is only relevant for extremely low system frequencies.

3) Derived by extrapolation of lifetime tests.

4) T<sub>i</sub> = 25 °C.

5) This parameter limits the number of subsequent programming operations within a physical sector without a given page in this sector being (re-)programmed. The drain disturb limit is applicable if wordline erase is used repeatedly. For normal sector erase/program cycles this limit will not be violated. For data sectors the integrated EEPROM emulation firmware routines handle this limit automatically, for wordline erases in code sectors (without EEPROM emulation) it is recommended to execute a software based refresh, which may make use of the integrated random number generator NVMBRNG to statistically start a refresh.

# 29.5.2 DC Parameters of Port 0, Port 1, TMS and Reset

## Note: Operating Conditions apply.

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the maximum allowed ocurrent which can be taken out of VDDP.

| Port Output Driver Mode     | Maximum O<br>(I <sub>OLmax</sub> , - I <sub>OF</sub> | utput Current<br>Imax)         | Maximum Ou<br>(I <sub>OLnom</sub> , - I <sub>OH</sub> | Number                         |          |

|-----------------------------|------------------------------------------------------|--------------------------------|-------------------------------------------------------|--------------------------------|----------|

|                             | V <sub>DDP</sub> 4.5V                                | 2.6V < V <sub>DDP</sub> < 4.5V | V <sub>DDP</sub> 4.5V                                 | 2.6V < V <sub>DDP</sub> < 4.5V |          |

| Strong driver <sup>2)</sup> | 5 mA                                                 | 3 mA                           | 1.6 mA                                                | 1.0 mA                         | P_5.1.15 |

| Medium driver <sup>3)</sup> | 3 mA                                                 | 1.8 mA                         | 1.0 mA                                                | 0.8 mA                         | P_5.1.1  |

| Weak driver <sup>3)</sup>   | 0.5 mA                                               | 0.3 mA                         | 0.25 mA                                               | 0.15 mA                        | P_5.1.2  |

#### Table 30 Current Limits for Port Output Drivers<sup>1)</sup>

1) Not subject to production test, specified by design.

2) Not available for port pins P0.4, P1.0, P1.1 and P1.2

3) All P0.x and P1.x

### Table 31 DC Characteristics Port0, Port1

$V_s$  = 5.5 V to 28 V,  $T_j$  = -40 °C to +175 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter        | Symbol                         | Values                  |                            |      |   | Note /                                                             | Number   |

|------------------|--------------------------------|-------------------------|----------------------------|------|---|--------------------------------------------------------------------|----------|

|                  |                                | Min.                    | Тур.                       | Max. |   | Test Condition                                                     |          |

| Input hysteresis | HYS <sub>P0_P1</sub>           | 0.11 x V <sub>DDP</sub> | -                          | _    | V | <sup>1)</sup> Series<br>resistance = 0 ;<br>$4.5V V_{DDP}$<br>5.5V | P_5.1.5  |

| Input hysteresis | HYS <sub>P0_P1</sub><br>_exend | -                       | 0.09 x<br>V <sub>DDP</sub> | -    | V | <sup>1)</sup> Series<br>resistance = 0 ;<br>2.6V $V_{DDP}$<br>4.5V | P_5.1.16 |

## Table 31 DC Characteristics Port0, Port1 (cont'd)

$V_s$  = 5.5 V to 28 V,  $T_j$  = -40 °C to +175 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                   | Symbol                  | Values                 |                            |                        |    | Note /                                                                                         | Number   |

|-----------------------------|-------------------------|------------------------|----------------------------|------------------------|----|------------------------------------------------------------------------------------------------|----------|

|                             |                         | Min.                   | Тур.                       | Max.                   |    | Test Condition                                                                                 |          |

| Input low voltage           | V <sub>IL</sub>         | -0.3                   | -                          | 0.3 x V <sub>DDP</sub> | V  | <sup>2)</sup> 4.5V V <sub>DDP</sub><br>5.5V                                                    | P_5.1.3  |

| Input low voltage           | V <sub>IL_extend</sub>  | -0.3                   | 0.42 x<br>V <sub>DDP</sub> | -                      | V  | <sup>1)</sup> 2.6V V <sub>DDP</sub><br>4.5V                                                    | P_5.1.17 |

| Input high voltage          | V <sub>IH</sub>         | 0.7 x V <sub>DDP</sub> | -                          | V <sub>DDP</sub> + 0.3 | V  | <sup>2)</sup> 4.5V V <sub>DDP</sub><br>5.5V                                                    | P_5.1.4  |

| Input high voltage          | V <sub>IH_extend</sub>  | -                      | 0.52 x<br>V <sub>DDP</sub> | V <sub>DDP</sub> + 0.3 | V  | <sup>1)</sup> 2.6V V <sub>DDP</sub><br>4.5V                                                    | P_5.1.18 |

| Output low voltage          | V <sub>OL</sub>         | -                      | -                          | 1.0                    | V  | <sup>3) 4)</sup> I <sub>OL</sub> I <sub>OLmax</sub>                                            | P_5.1.6  |

| Output low voltage          | V <sub>OL</sub>         | -                      | -                          | 0.4                    | V  | <sup>3) 5)</sup>   <sub>OL</sub>   <sub>OLnom</sub>                                            | P_5.1.7  |

| Output high voltage         | V <sub>OH</sub>         | V <sub>DDP</sub> - 1.0 | -                          | -                      | V  | <sup>3) 4)</sup> I <sub>OH</sub> I <sub>OHmax</sub>                                            | P_5.1.8  |

| Output high voltage         | V <sub>OH</sub>         | V <sub>DDP</sub> - 0.4 | -                          | -                      | V  | <sup>3) 5)</sup> I <sub>OH</sub> I <sub>OHnom</sub>                                            | P_5.1.9  |

| Input leakage current       | I <sub>OZ_extend1</sub> | -500                   | -                          | +500                   | nA | -40°C T <sub>J</sub><br>25°C,<br>0.45 V < V <sub>IN</sub><br>< V <sub>DDP</sub>                | P_5.1.20 |

| Input leakage current       | I <sub>OZ1</sub>        | -5                     | _                          | +5                     | μA | <sup>6)</sup> 25°C <<br>T <sub>J</sub> 85°C,<br>0.45 V < V <sub>IN</sub><br>< V <sub>DDP</sub> | P_5.1.10 |

| Input leakage current       | I <sub>OZ_extend2</sub> | -15                    | _                          | +15                    | μA | 85°C < T <sub>J</sub><br>150°C,<br>0.45 V < V <sub>IN</sub><br>< V <sub>DDP</sub>              | P_5.1.21 |

| Input leakage current       | I <sub>OZ_extend3</sub> | -20                    | -                          | +20                    | μA | 85°C < T <sub>J</sub><br>175°C,<br>0.45 V < V <sub>IN</sub><br>< V <sub>DDP</sub>              | P_5.1.11 |

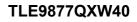

| Pull level keep current     | I <sub>PLK</sub>        | -200                   | -                          | +200                   | μA | $^{7)}$ V <sub>PIN</sub> V <sub>IH</sub> (up) V <sub>PIN</sub> V <sub>IL</sub> (dn)            | P_5.1.12 |

| Pull level force current    | I <sub>PLF</sub>        | -1.5                   | -                          | +1.5                   | mA | $^{7)}$ V <sub>PIN</sub> V <sub>IL</sub> (up) V <sub>PIN</sub> V <sub>IH</sub> (dn)            | P_5.1.13 |

| Pin capacitance             | C <sub>IO</sub>         | -                      | -                          | 10                     | pF | 1)                                                                                             | P_5.1.14 |

| Reset Pin Timing            |                         | •                      |                            |                        |    |                                                                                                | •        |

| Reset Pin Input Filter Time | $t_{filt\_RESET}$       |                        | 5                          | _                      | μs | 1)                                                                                             | P_5.1.19 |

1) Not subject to production test, specified by design.

2) Tested at  $V_{DDP}$  = 5V, specified for 4.5V <  $V_{DDP}$  < 5.5V.

3) The maximum deliverable output current of a port driver depends on the selected output driver mode. The limit for pin groups must be respected.

4) Tested at 4.9V <  $V_{DDP}$  < 5.1V,  $I_{OL}$  = 4mA,  $I_{OH}$  = -4mA, specified for 4.5V <  $V_{DDP}$  < 5.5V.

## Table 35 Supply Voltage Signal Conditioning (cont'd)

$V_s$  = 5.5 V to 28 V,  $T_j$  = -40 °C to +175 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                                                                         | Symbol                               |       | Values | 5    | Unit | Note / Test Condition                              | Number   |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|--------|------|------|----------------------------------------------------|----------|

|                                                                                                                                   |                                      | Min.  | Тур.   | Max. |      |                                                    |          |

| Accuracy of $V_{VDH}$ -10-bit<br>ADC -measurement<br>without calibration,<br>ATT <sub>VDH_2</sub>                                 | ßV <sub>VDHADC10B</sub>              | -400  | -      | 400  | mV   | V <sub>DH</sub> = 5.5V to 17.5V,<br>-40°C Tj 150°C | P_8.1.71 |

| Accuracy of $V_{VDH}$ -10-bit<br>ADC -measurement<br>without calibration,<br>ATT <sub>VDH_2</sub> - Extended<br>temperature range | ßV <sub>VDHADC10B</sub>              | -1.5  | _      | 1.5  | V    | V <sub>DH</sub> = 5.5V to 17.5V,<br>-40°C Tj 175°C | P_8.1.78 |

| 10-Bit ADC measurement-<br>input resistance for VDH                                                                               | $R_{in\_VDH,measure}$                | 200   | 390    | 470  | k    | PD_N=1 (on-state)                                  | P_8.1.3  |

| Measurement input leakage current for $V_{\text{VDH}}$                                                                            | Ileak_VDH, measure                   | -0.05 | -      | 2.0  | μA   | PD_N=0 (off-state),<br>T <sub>j</sub> = -40150°C   | P_8.1.10 |

| Measurement input<br>leakage current for V <sub>VDH</sub> -<br>Extended temperature<br>range                                      | I <sub>leak_VDH,</sub><br>measure_HT | -0.05 | -      | 4.0  | μA   | PD_N=0 (off-state),<br>T <sub>j</sub> = 150175°C   | P_8.1.79 |

1) Not subject to production test, specified by design.

2) Accuracy is valid for a calibrated device.

# 29.8.2 Central Temperature Sensor Parameters

## Table 36 Electrical Characteristics Temperature Sensor Module

$V_s$  = 5.5 V to 28 V,  $T_j$  = -40 °C to +175 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                   | Symbol | Values |       |      | Unit | Note / Test Condition                        | Number  |

|-----------------------------------------------------------------------------|--------|--------|-------|------|------|----------------------------------------------|---------|

|                                                                             |        | Min.   | Тур.  | Max. |      |                                              |         |

| Output voltage $V_{\text{TEMP}}$ at $T_0=273 \text{ K} (0^{\circ}\text{C})$ | а      | -      | 0.666 | -    | V    | <sup>1)</sup><br>T <sub>0</sub> =273 K (0°C) | P_8.2.2 |

| Temperature sensitivity b                                                   | b      | _      | 2.31  | -    | mV/K | 1)                                           | P_8.2.4 |

| Accuracy_1                                                                  | Acc_1  | -10    | _     | 10   | °C   | <sup>2)1)</sup> -40°C < Tj < 85°C            | P_8.2.5 |

| Accuracy_2                                                                  | Acc_2  | -10    | _     | 10   | °C   | <sup>2)1)</sup> 125°C < Tj < 150°C           | P_8.2.6 |

| Accuracy_3                                                                  | Acc_3  | -5     | _     | 5    | °C   | <sup>2)1)</sup> 85°C < Tj < 125°C            | P_8.2.7 |

1) Not subject to production test, specified by design

2) Accuracy with reference to on-chip temperature calibration measurement, valid for Mode1