Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka304-e-mv |

**TABLE 4-6:**

| File<br>Name | Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100 |        |         |        |        |        |        |        | TM     | IR1   |       |        |        |       |       |       |       | 0000          |

| PR1          | 0102 |        |         |        |        |        |        |        | Pl     | R1    |       |        |        |       |       |       |       | FFFF          |

| T1CON        | 0104 | TON    | _       | TSIDL  | _      | _      | _      | T1ECS1 | T1ECS0 | _     | TGATE | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0106 |        |         |        |        |        |        |        | TM     | IR2   |       |        |        |       |       |       |       | 0000          |

| TMR3HLD      | 0108 |        | TMR3HLD |        |        |        |        |        |        |       |       |        | 0000   |       |       |       |       |               |

| TMR3         | 010A |        | TMR3    |        |        |        |        |        |        |       |       |        | 0000   |       |       |       |       |               |

| PR2          | 010C |        | PR2     |        |        |        |        |        |        |       |       |        | 0000   |       |       |       |       |               |

| PR3          | 010E |        |         |        |        |        |        |        | Pl     | R3    |       |        |        |       |       |       |       | FFFF          |

| T2CON        | 0110 | TON    | _       | TSIDL  | _      | _      | _      | _      | _      | _     | TGATE | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | FFFF          |

| T3CON        | 0112 | TON    | _       | TSIDL  | _      | _      | _      | _      | _      | _     | TGATE | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4         | 0114 |        |         |        |        |        |        |        | TM     | IR4   |       |        |        |       |       |       |       | 0000          |

| TMR5HLD      | 0116 |        |         |        |        |        |        |        | TMR    | 5HLD  |       |        |        |       |       |       |       | 0000          |

| TMR5         | 0118 |        |         |        |        |        |        |        | TM     | IR5   |       |        |        |       |       |       |       | 0000          |

| PR4          | 011A |        |         |        |        |        |        |        | Pl     | R4    |       |        |        |       |       |       |       | FFFF          |

| PR5          | 011C |        |         |        |        |        |        |        | P      | ₹5    |       |        |        |       |       |       |       | FFFF          |

| T4CON        | 011E | TON    | _       | TSIDL  | _      | _      | _      | _      | _      | _     | TGATE | TCKPS1 | TCKPS0 | T45   | _     | TCS   | _     | 0000          |

| T5CON        | 0120 | TON    | _       | TSIDL  | -      | ı      | _      | _      | _      | _     | TGATE | TCKPS1 | TCKPS0 | 1     | _     | TCS   | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TIMER REGISTER MAP

## TABLE 4-7: INPUT CAPTURE REGISTER MAP

| File<br>Name | Addr | Bit 15    | Bit 14                                                                                         | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9 | Bit 8 | Bit 7  | Bit 6    | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|-----------|------------------------------------------------------------------------------------------------|--------|----------|----------|----------|-------|-------|--------|----------|-------|----------|----------|----------|----------|----------|---------------|

| IC1CON1      | 0140 | _         | _                                                                                              | ICSIDL | ICTSEL2  | ICTSEL1  | ICTSEL0  | _     | _     | _      | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2      | 0142 | _         | _                                                                                              | _      | _        | _        | _        | _     | IC32  | ICTRIG | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF       | 0144 |           |                                                                                                |        |          |          |          |       |       | IC1BU  | F        |       |          |          |          |          |          | 0000          |

| IC1TMR       | 0146 |           | IC1TMR ×                                                                                       |        |          |          |          |       |       |        |          |       | xxxx     |          |          |          |          |               |

| IC2CON1      | 0148 | _         | ICSIDL   IC2TSEL2   IC2TSEL1   IC2TSEL0   IC11   IC10   ICOV   ICBNE   ICM2   ICM1   ICM0   00 |        |          |          |          |       |       |        |          |       |          | 0000     |          |          |          |               |

| IC2CON2      | 014A | _         | _                                                                                              | _      | _        | _        | _        | _     | IC32  | ICTRIG | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF       | 014C |           |                                                                                                |        |          |          |          |       |       | IC2BU  | F        |       |          |          |          |          |          | 0000          |

| IC2TMR       | 014E |           |                                                                                                |        |          |          |          |       |       | IC2TM  | ₹        |       |          |          |          |          |          | xxxx          |

| IC3CON1      | 0150 | _         | _                                                                                              | ICSIDL | IC3TSEL2 | IC3TSEL1 | IC3TSEL0 | _     | _     | _      | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2      | 0152 | _         | IC32 ICTRIG TRIGSTAT - SYNCSEL4 SYNCSEL3 SYNCSEL2 SYNCSEL1 SYNCSEL0 00                         |        |          |          |          |       |       |        |          |       |          | 000D     |          |          |          |               |

| IC3BUF       | 0154 | 54 IC3BUF |                                                                                                |        |          |          |          |       |       |        |          | 0000  |          |          |          |          |          |               |

| IC3TMR       | 0156 | LOCALID.  |                                                                                                |        |          |          |          |       |       |        |          | xxxx  |          |          |          |          |          |               |

PIC24FV32KA304 FAMILY

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-24: NVM REGISTER MAP**

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets <sup>(1)</sup> |

|--------------|------|--------|--------|--------|---------|--------|--------|-------|-------|--------|-------|--------|--------|--------|--------|--------|--------|------------------------------|

| NVMCON       | 0760 | WR     | WREN   | WRERR  | PGMONLY | -      | _      | _     | _     | _      | ERASE | NVMOP5 | NVMOP4 | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000                         |

| NVMKEY       | 0766 | _      | _      | _      | _       | _      | _      | _     | _     | NVMKEY |       |        |        |        |        | 0000   |        |                              |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

## TABLE 4-25: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON      | 0768 | ULPEN  | _      | ULPSIDL | _      | _      | 1      | 1     | ULPSINK | _     | -     | _     | -     | -     | -     | -     | -     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-26: PMD REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|-------|---------|-------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _      | _     | I2C1MD  | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | -      | ADC1MD | 0000          |

| PMD2         | 0772 | _      | -      | 1      | _      | _      | IC3MD  | IC2MD  | IC1MD | _       | _     | -     | _      | _      | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0774 | _      | -      | 1      | _      | _      | CMPMD  | RTCCMD | -     | CRCPMD  | _     | -     | _      | _      | _      | I2C2MD | _      | 0000          |

| PMD4         | 0776 | _      | 1      | 1      | _      | _      | 1      | -      | -     | ULPWUMD | _     | -     | EEMD   | REFOMD | CTMUMD | HLVDMD | _      | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| _     | _   | _   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | _     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 NSTDIS: Interrupt Nesting Disable bit

1 = Interrupt nesting is disabled0 = Interrupt nesting is enabled

bit 14-5 **Unimplemented:** Read as '0'

bit 4 MATHERR: Arithmetic Error Trap Status bit

1 = Overflow trap has occurred0 = Overflow trap has not occurred

bit 3 ADDRERR: Address Error Trap Status bit

1 = Address error trap has occurred0 = Address error trap has not occurred

bit 2 STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred0 = Stack error trap has not occurred

bit 1 OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred0 = Oscillator failure trap has not occurred

bit 0 Unimplemented: Read as '0'

#### REGISTER 8-20: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0    | R/W-1  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|--------|-----|-----|-----|-------|

| _      | NVMIP2 | NVMIP1 | NVMIP0 | _   | _   | _   | _     |

| bit 15 |        |        |        |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|--------|--------|--------|-----|---------|---------|---------|

| _     | AD1IP2 | AD1IP1 | AD1IP0 | _   | U1TXIP2 | U1TXIP1 | U1TXIP0 |

| bit 7 |        |        |        |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 **NVMIP<2:0>:** NVM Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11-7 **Unimplemented:** Read as '0'

bit 6-4 AD1IP<2:0>: A/D Conversion Complete Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

:

:

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

:

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

## REGISTER 10-1: DSCON: DEEP SLEEP CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    |

|--------|-----|-----|-----|-----|-----|-----|----------|

| DSEN   | _   | _   | _   | _   | _   | _   | RTCCWDIS |

| bit 15 |     |     |     |     |     |     | bit 8    |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0                | R/C-0, HS |

|-------|-----|-----|-----|-----|----------|----------------------|-----------|

| _     | _   | _   | _   | _   | ULPWUDIS | DSBOR <sup>(2)</sup> | RELEASE   |

| bit 7 |     |     |     |     |          |                      | bit 0     |

| Legend:           | C = Clearable bit HS = Hardware Settable bit |                                    |                    |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 DSEN: Deep Sleep Enable bit

1 = Enters Deep Sleep on execution of PWRSAV #0 0 = Enters normal Sleep on execution of PWRSAV #0

bit 14-9 Unimplemented: Read as '0'

bit 8 RTCCWDIS: RTCC Wake-up Disable bit

1 = Wake-up from Deep Sleep with RTCC disabled 0 = Wake-up from Deep Sleep with RTCC enabled

bit 7-3 **Unimplemented:** Read as '0'

bit 2 **ULPWUDIS:** ULPWU Wake-up Disable bit

1 = Wake-up from Deep Sleep with ULPWU disabled 0 = Wake-up from Deep Sleep with ULPWU enabled

bit 1 DSBOR: Deep Sleep BOR Event bit<sup>(2)</sup>

1 = The DSBOR was active and a BOR event was detected during Deep Sleep

0 = The DSBOR was not active or was active but did not detect a BOR event during Deep Sleep

bit 0 RELEASE: I/O Pin State Release bit

1 = Upon waking from Deep Sleep, I/O pins maintain their previous states to Deep Sleep entry

0 = Release I/O pins from their state previous to Deep Sleep entry, and allow their respective TRISx and LATx bits to control their states

Note 1: All register bits are only reset in the case of a POR event outside of Deep Sleep mode.

2: Unlike all other events, a Deep Sleep BOR event will NOT cause a wake-up from Deep Sleep; this re-arms POR.

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | _   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _   | _     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R-0, HSC | R-0, HSC | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|----------|----------|-------|-------|-------|

| _     | ICI1  | ICI0  | ICOV     | ICBNE    | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |          |          |       |       | bit 0 |

**Legend:** HSC = Hardware Settable/Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 ICSIDL: Input Capture x Module Stop in Idle Control bit

1 = Input capture module halts in CPU Idle mode

0 = Input capture module continues to operate in CPU Idle mode

bit 12-10 ICTSEL<2:0>: Input Capture x Timer Select bits

111 = System clock (Fosc/2)

110 = Reserved

101 = Reserved

100 = Timer1

011 = Timer5

010 =T imer4

001 = Timer2

000 = Timer3

bit 9-7 **Unimplemented:** Read as '0'

bit 6-5 ICI<1:0>: Select Number of Captures per Interrupt bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 **ICOV:** Input Capture x Overflow Status Flag bit (read-only)

1 = Input capture overflow occurred

0 = No input capture overflow occurred

bit 3 **ICBNE:** Input Capture x Buffer Empty Status bit (read-only)

1 = Input capture buffer is not empty, at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Interrupt mode: Input capture functions as an interrupt pin only when the device is in Sleep or Idle mode (rising edge detect only, all other control bits are not applicable)

110 = Unused (module disabled)

101 = Prescaler Capture mode: Capture on every 16th rising edge

100 = Prescaler Capture mode: Capture on every 4th rising edge

011 = Simple Capture mode: Capture on every rising edge

010 = Simple Capture mode: Capture on every falling edge

001 = Edge Detect Capture mode: Capture on every edge (rising and falling); ICI<1:0 bits do not control interrupt generation for this mode

000 = Input capture module is turned off

## 15.4 Subcycle Resolution

The DCBx bits (OCxCON2<10:9>) provide for resolution better than one instruction cycle. When used, they delay the falling edge generated from a match event by a portion of an instruction cycle.

For example, setting DCB<1:0> = 10 causes the falling edge to occur halfway through the instruction cycle in which the match event occurs, instead of at the beginning. These bits cannot be used when OCM<2:0> = 001. When operating the module in PWM mode (OCM<2:0> = 110 or 111), the DCBx bits will be double-buffered.

The DCBx bits are intended for use with a clock source identical to the system clock. When an OCx module with enabled prescaler is used, the falling edge delay caused by the DCBx bits will be referenced to the system clock period, rather than the OCx module's period.

TABLE 15-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (FcY = 4 MHz)<sup>(1)</sup>

| PWM Frequency     | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-------------------|--------|-------|--------|--------|---------|----------|---------|

| Prescaler Ratio   | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Value      | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits) | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

TABLE 15-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (FcY = 16 MHz)<sup>(1)</sup>

| PWM Frequency     | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-------------------|---------|--------|--------|---------|----------|---------|---------|

| Prescaler Ratio   | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Value      | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits) | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

## REGISTER 19-6: WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| _      | _   | _   | _   | _   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits

Contains a value from 0 to 6.

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits

Contains a value from 0 to 2.

bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 19-7: MINSEC: MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| _      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits

Contains a value from 0 to 5.

bit 11-8 MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits

Contains a value from 0 to 9.

bit 7 **Unimplemented:** Read as '0'

bit 6-4 SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits

Contains a value from 0 to 5.

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits

Contains a value from 0 to 9.

#### 20.1.3 DATA SHIFT DIRECTION

The LENDIAN bit (CRCCON1<3>) is used to control the shift direction. By default, the CRC will shift data through the engine, MSb first. Setting LENDIAN (= 1) causes the CRC to shift data, LSb first. This setting allows better integration with various communication schemes and removes the overhead of reversing the bit order in software. Note that this only changes the direction of the data that is shifted into the engine. The result of the CRC calculation will still be a normal CRC result, not a reverse CRC result.

#### 20.1.4 INTERRUPT OPERATION

The module generates an interrupt that is configurable by the user for either of two conditions. If CRCISEL is '0', an interrupt is generated when the VWORD<4:0> bits make a transition from a value of '1' to '0'. If CRCISEL is '1', an interrupt will be generated after the CRC operation finishes and the module sets the CRCGO bit to '0'. Manually setting CRCGO to '0' will not generate an interrupt.

#### 20.1.5 TYPICAL OPERATION

To use the module for a typical CRC calculation:

- 1. Set the CRCEN bit to enable the module.

- 2. Configure the module for the desired operation:

- a) Program the desired polynomial using the CRCXORL and CRCXORH registers, and the PLEN<4:0> bits.

- b) Configure the data width and shift direction using the DWIDTHx and LENDIAN bits.

- Select the desired interrupt mode using the CRCISEL bit.

- Preload the FIFO by writing to the CRCDATL and CRCDATH registers until the CRCFUL bit is set or no data is left.

- Clear old results by writing 00h to CRCWDATL and CRCWDATH. CRCWDAT can also be left unchanged to resume a previously halted calculation.

- 5. Set the CRCGO bit to start calculation.

- 6. Write the remaining data into the FIFO as space becomes available.

- When the calculation completes, CRCGO is automatically cleared. An interrupt will be generated if CRCISEL = 1.

- 8. Read CRCWDATL and CRCWDATH for the result of the calculation.

### 20.2 Registers

There are eight registers associated with the module:

- CRCCON1

- CRCCON2

- CRCXORL

- CRCXORH

- CRCDATL

- CRCDATH

- CRCWDATL

- CRCWDATH

The CRCCON1 and CRCCON2 registers (Register 20-1 and Register 20-2) control the operation of the module, and configure the various settings. The CRCXOR registers (Register 20-3 and Register 20-4) select the polynomial terms to be used in the CRC equation. The CRCDAT and CRCWDAT registers are each register pairs that serve as buffers for the double-word, input data and CRC processed output, respectively.

## REGISTER 20-3: CRCXORL: CRC XOR POLYNOMIAL REGISTER, LOW BYTE

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | X<1   | 5:8>  |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | U-0   |

|-------|-------|-------|--------|-------|-------|-------|-------|

|       |       |       | X<7:1> |       |       |       | _     |

| bit 7 |       |       |        |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 **Unimplemented:** Read as '0'

## REGISTER 20-4: CRCXORH: CRC XOR POLYNOMIAL REGISTER, HIGH BYTE

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|

| X<31:24> |       |       |       |       |       |       |       |  |

| bit 15   |       |       |       |       |       |       |       |  |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| X<23:16>  |       |       |       |       |       |       |       |  |  |

| bit 7 bit |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 X<31:16>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 22-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0  | R-0    | r-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-------|-------|-------|-------|

| ADRC   | EXTSAM | _   | SAMC4 | SAMC3 | SAMC2 | SAMC1 | SAMC0 |

| bit 15 |        |     |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADCS7 | ADCS6 | ADCS5 | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 ADRC: A/D Conversion Clock Source bit

1 = RC clock

0 = Clock is derived from the system clock

bit 14 **EXTSAM:** Extended Sampling Time bit

1 = A/D is still sampling after SAMP = 0

0 = A/D is finished sampling

bit 13 Reserved: Maintain as '0'

bit 12-8 **SAMC<4:0>:** Auto-Sample Time Select bits

11111 = **31** TAD

•

Ī

•

00001 = 1 TAD00000 = 0 TAD

bit 7-0 ADCS<7:0>: A/D Conversion Clock Select bits

11111111-01000000 = Reserved 00111111 = 64 · Tcy = TAD

•

•

$00000001 = 2 \cdot \text{TCY} = \text{TAD}$ 00000000 = TCY = TAD

| PIC24FV3 | 2KA304 | FAMILY |  |  |

|----------|--------|--------|--|--|

| NOTES:   |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

|          |        |        |  |  |

## **REGISTER 26-10: DEVREV: DEVICE REVISION REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R   | R    | R     | R |  |  |

|-------|-----|-----|-----|-----|------|-------|---|--|--|

| _     | _   | _   | _   |     | REV- | <3:0> |   |  |  |

| bit 7 |     |     |     | bii |      |       |   |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-4 **Unimplemented:** Read as '0'

bit 3-0 **REV<3:0>:** Minor Revision Identifier bits

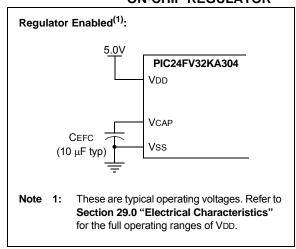

## 26.2 On-Chip Voltage Regulator

All of the PIC24FV32KA304 family devices power their core digital logic at a nominal 3.0V. This may create an issue for designs that are required to operate at a higher typical voltage, as high as 5.0V. To simplify system design, all devices in the "FV" family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator is always enabled and provides power to the core from the other VDD pins. A low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 26-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is discussed in Section 2.4 "Voltage Regulator Pin (VCAP)", and in Section 29.1 "DC Characteristics".

For "F" devices, the regulator is disabled. Instead, core logic is powered directly from VDD. This allows the devices to operate at an overall lower allowable voltage range (1.8V-3.6V).

# 26.2.1 VOLTAGE REGULATOR TRACKING MODE AND LOW-VOLTAGE DETECTION

For all PIC24FV32KA304 devices, the on-chip regulator provides a constant voltage of 3.2V nominal to the digital core logic. The regulator can provide this level from a VDD of about 3.2V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 3.2V. In order to prevent "brown-out" conditions when the voltage drops too low for the regulator, the regulator enters Tracking mode. In Tracking mode, the regulator output follows VDD with a typical voltage drop of 150 mV.

When the device enters Tracking mode, it is no longer possible to operate at full speed. To provide information about when the device enters Tracking mode, the on-chip regulator includes a simple, High/Low-Voltage Detect (HLVD) circuit. When VDD drops below full-speed operating voltage, the circuit sets the High/Low-Voltage Detect Interrupt Flag, HLVDIF (IFS4<8>). This can be used to generate an interrupt and put the application into a low-power operational mode or trigger an orderly shutdown. Maximum device speeds as a function of VDD are shown in **Section 29.1** "DC Characteristics", in Figure 29-1 and Figure 29-1.

#### 26.2.2 ON-CHIP REGULATOR AND POR

For PIC24FV32KA304 devices, it takes a brief time, designated as TPM, for the Voltage Regulator to generate a stable output. During this time, code execution is disabled. TPM (DC Specification SY71) is applied every time the device resumes operation after any power-down, including Sleep mode.

## FIGURE 26-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

## 26.3 Watchdog Timer (WDT)

For the PIC24FV32KA304 family of devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the Configuration bits, WDTPS<3:0> (FWDT<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranging from 1 ms to 131 seconds, can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

### 27.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 27.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 27.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 27.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

TABLE 29-12: DC CHARACTERISTICS: DATA EEPROM MEMORY

| DC CHARACTERISTICS |        |                                                         | Standard Operating Conditions: 1.8V to 3.6V PIC24F32KA3XX 2.0V to 5.5V PIC24FV32KA3XX Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                    |     |       |                                               |  |  |

|--------------------|--------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------------------------------|--|--|

| Param<br>No.       | Sym    | Characteristic                                          | Min                                                                                                                                                                                                                                                              | Typ <sup>(1)</sup> | Max | Units | Conditions                                    |  |  |

|                    |        | Data EEPROM Memory                                      |                                                                                                                                                                                                                                                                  |                    |     |       |                                               |  |  |

| D140               | EPD    | Cell Endurance                                          | 100,000                                                                                                                                                                                                                                                          | _                  | _   | E/W   |                                               |  |  |

| D141               | VPRD   | VDD for Read                                            | VMIN                                                                                                                                                                                                                                                             | _                  | 3.6 | V     | VMIN = Minimum operating voltage              |  |  |

| D143A              | Tiwd   | Self-Timed Write Cycle<br>Time                          | _                                                                                                                                                                                                                                                                | 4                  | _   | ms    |                                               |  |  |

| D143B              | TREF   | Number of Total<br>Write/Erase Cycles<br>Before Refresh | _                                                                                                                                                                                                                                                                | 10M                | _   | E/W   |                                               |  |  |

| D144               | TRETDD | Characteristic Retention                                | 40                                                                                                                                                                                                                                                               | _                  | _   | Year  | Provided no other specifications are violated |  |  |

| D145               | IDDPD  | Supply Current During Programming                       | _                                                                                                                                                                                                                                                                | 7                  | _   | mA    |                                               |  |  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

## TABLE 29-13: DC CHARACTERISTICS: COMPARATOR SPECIFICATIONS

| Operatir     | Operating Conditions: 2.0V < VDD < 3.6V, -40°C < TA < +125°C (unless otherwise stated) |                             |     |     |     |       |          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------|-----------------------------|-----|-----|-----|-------|----------|--|--|--|--|

| Param<br>No. | Symbol                                                                                 | Characteristic              | Min | Тур | Max | Units | Comments |  |  |  |  |

| D300         | VIOFF                                                                                  | Input Offset Voltage        | _   | 20  | 40  | mV    |          |  |  |  |  |

| D301         | VICM                                                                                   | Input Common-Mode Voltage   | 0   | _   | VDD | V     |          |  |  |  |  |

| D302         | CMRR                                                                                   | Common-Mode Rejection Ratio | 55  | _   | _   | dB    |          |  |  |  |  |

## TABLE 29-14: DC CHARACTERISTICS: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| Operating    | <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +125°C (unless otherwise stated) |                         |     |     |            |       |          |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------|-------------------------|-----|-----|------------|-------|----------|--|--|--|--|

| Param<br>No. | Symbol                                                                                        | Characteristic          | Min | Тур | Max        | Units | Comments |  |  |  |  |

| VRD310       | CVRES                                                                                         | Resolution              | -   | _   | VDD/32     | LSb   |          |  |  |  |  |

| VRD311       | CVRAA                                                                                         | Absolute Accuracy       | _   | _   | AVDD - 1.5 | LSb   |          |  |  |  |  |

| VRD312       | CVRur                                                                                         | Unit Resistor Value (R) | _   | 2k  | _          | Ω     |          |  |  |  |  |

**TABLE 29-19: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CH        | ARACT         | ERISTICS                                                                |                     |                    |                    |                          |                                   |

|--------------|---------------|-------------------------------------------------------------------------|---------------------|--------------------|--------------------|--------------------------|-----------------------------------|

| Param<br>No. | Sym           | Characteristic                                                          | Min                 | Typ <sup>(1)</sup> | Max                | Units                    | Conditions                        |

| OS10         | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode) | DC<br>4             | _                  | 32<br>8            | MHz<br>MHz               | EC<br>ECPLL                       |

| OS15         |               | Oscillator Frequency                                                    | 0.2<br>4<br>4<br>31 |                    | 4<br>25<br>8<br>33 | MHz<br>MHz<br>MHz<br>kHz | XT<br>HS<br>XTPLL<br>SOSC         |

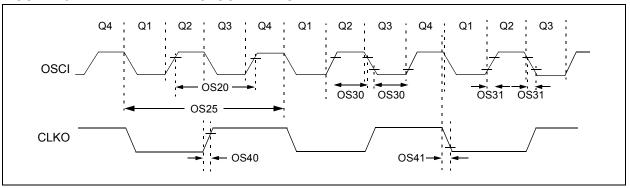

| OS20         | Tosc          | Tosc = 1/Fosc                                                           | _                   | _                  | _                  | _                        | See Parameter OS10 for Fosc value |

| OS25         | Tcy           | Instruction Cycle Time <sup>(2)</sup>                                   | 62.5                | _                  | DC                 | ns                       |                                   |

| OS30         | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                            | 0.45 x Tosc         | _                  | _                  | ns                       | EC                                |

| OS31         | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                           | _                   | _                  | 20                 | ns                       | EC                                |

| OS40         | TckR          | CLKO Rise Time <sup>(3)</sup>                                           | _                   | 6                  | 10                 | ns                       |                                   |

| OS41         | TckF          | CLKO Fall Time <sup>(3)</sup>                                           | _                   | 6                  | 10                 | ns                       |                                   |

- **Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- **3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 Tcy) and high for the Q3-Q4 period (1/2 Tcy).

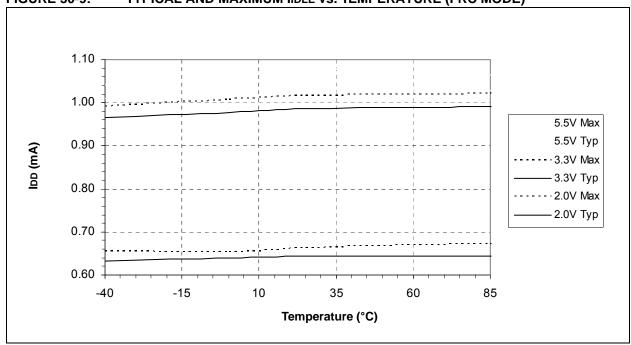

FIGURE 30-9: TYPICAL AND MAXIMUM lidle vs. TEMPERATURE (FRC MODE)

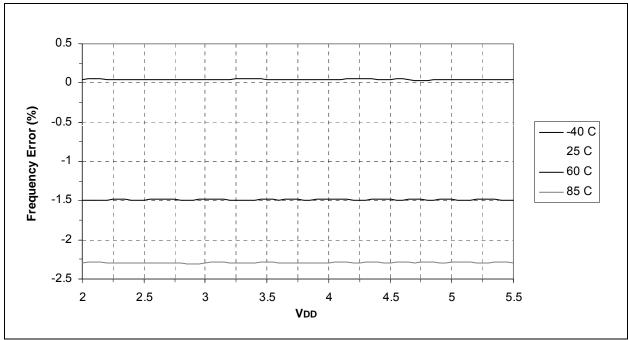

FIGURE 30-10: FRC FREQUENCY ACCURACY vs. VDD

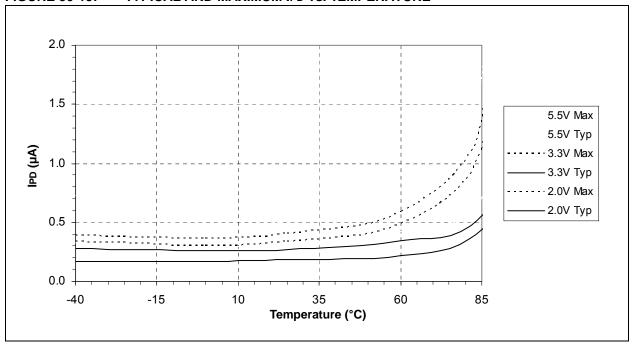

FIGURE 30-15: TYPICAL AND MAXIMUM IPD vs. TEMPERATURE

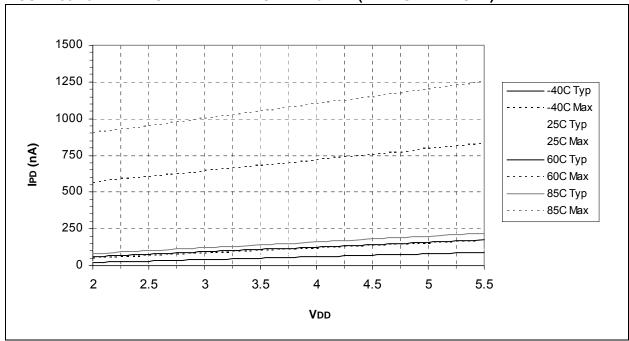

FIGURE 30-16: TYPICAL AND MAXIMUM IPD vs. VDD (DEEP SLEEP MODE)

| FIGURE 30-44: | TYPICAL AND MAXIMUM IPD vs. VDD (DEEP SLEEP MODE)         |

|---------------|-----------------------------------------------------------|

| Current (nA)  |                                                           |

|               | VDD                                                       |

| FIGURE 30-45: | TYPICAL AND MAXIMUM IPD vs. TEMPERATURE (DEEP SLEEP MODE) |

| Current (nA)  |                                                           |

|               | Temperature (°C)                                          |