Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Active                                                        |

|                            |                                                               |

| Core Processor             | HC08                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | IRSCI, SPI                                                    |

| Peripherals                | LCD, LVD, POR, PWM                                            |

| Number of I/O              | 32                                                            |

| Program Memory Size        | 12KB (12K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 512 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                     |

| Data Converters            | A/D 6x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-QFP                                                        |

| Supplier Device Package    | 64-QFP (14x14)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908lj12cfu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTE:

The location of the stack is arbitrary and may be relocated anywhere in RAM. Moving the SP out of page 0 (\$0000 to \$00FF) frees direct address (page 0) space. For correct operation, the stack pointer must point only to RAM locations.

### 6.4.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

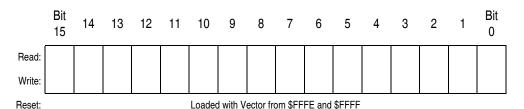

During reset, the program counter is loaded with the reset vector address located at \$FFFE and \$FFFF. The vector address is the address of the first instruction to be executed after exiting the reset state.

Figure 6-5. Program Counter (PC)

## **Central Processor Unit (CPU)**

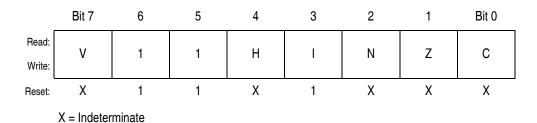

### 6.4.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to logic 1. The following paragraphs describe the functions of the condition code register.

Figure 6-6. Condition Code Register (CCR)

#### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

1 = Overflow

0 = No overflow

#### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

Table 6-1. Instruction Set Summary (Sheet 6 of 8)

| Source<br>Form                                                                                  | Operation                  | Description                                                                                                                                                                                                 |          |   | Effect on CCR |          |          |          |                                       | ode                                              | Operand                                         | es                                   |

|-------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|---------------|----------|----------|----------|---------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            |                            | ·                                                                                                                                                                                                           | ٧        | Н | I             | N        | Z        | С        | Address<br>Mode                       | Opcode                                           | obe                                             | Cycles                               |

| MOV opr,opr<br>MOV opr,X+<br>MOV #opr,opr<br>MOV X+,opr                                         | Move                       | $(M)_{Destination} \leftarrow (M)_{Source}$<br>$H:X \leftarrow (H:X) + 1 (IX+D, DIX+)$                                                                                                                      | 0        | _ | _             | <b>‡</b> | <b>‡</b> | _        | DD<br>DIX+<br>IMD<br>IX+D             | 4E<br>5E<br>6E<br>7E                             | dd dd<br>dd<br>ii dd<br>dd                      |                                      |

| MUL                                                                                             | Unsigned multiply          | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                             | -        | 0 | _             | -        | -        | 0        | INH                                   | 42                                               |                                                 | 5                                    |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG ,X<br>NEG opr,SP                                    | Negate (Two's Complement)  | $\begin{aligned} M &\leftarrow -(M) = \$00 - (M) \\ A &\leftarrow -(A) = \$00 - (A) \\ X &\leftarrow -(X) = \$00 - (X) \\ M &\leftarrow -(M) = \$00 - (M) \\ M &\leftarrow -(M) = \$00 - (M) \end{aligned}$ | <b>1</b> | _ | _             | <b>‡</b> | <b>‡</b> | \$       | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 30<br>40<br>50<br>60<br>70<br>9E60               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| NOP                                                                                             | No Operation               | None                                                                                                                                                                                                        | -        | _ | -             | -        | -        | -        | INH                                   | 9D                                               |                                                 | 1                                    |

| NSA                                                                                             | Nibble Swap A              | A ← (A[3:0]:A[7:4])                                                                                                                                                                                         | -        | _ | _             | -        | -        | -        | INH                                   | 62                                               |                                                 | 3                                    |

| ORA #opr<br>ORA opr<br>ORA opr,<br>ORA opr,X<br>ORA opr,X<br>ORA ,X<br>ORA opr,SP<br>ORA opr,SP | Inclusive OR A and M       | A ← (A)   (M)                                                                                                                                                                                               | 0        | _ | _             | <b>‡</b> | <b>‡</b> | _        | IMM DIR EXT IX2 IX1 IX SP1 SP2        | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EEA<br>9EDA | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| PSHA                                                                                            | Push A onto Stack          | Push (A); SP ← (SP) – 1                                                                                                                                                                                     | -        | - | _             | -        | -        | -        | INH                                   | 87                                               |                                                 | 2                                    |

| PSHH                                                                                            | Push H onto Stack          | Push (H); SP ← (SP) – 1                                                                                                                                                                                     | -        | _ | _             | -        | -        | -        | INH                                   | 8B                                               |                                                 | 2                                    |

| PSHX                                                                                            | Push X onto Stack          | Push (X); SP ← (SP) – 1                                                                                                                                                                                     | -        | _ | -             | -        | -        | -        | INH                                   | 89                                               |                                                 | 2                                    |

| PULA                                                                                            | Pull A from Stack          | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                          | -        | - | -             | -        | -        | -        | INH                                   | 86                                               |                                                 | 2                                    |

| PULH                                                                                            | Pull H from Stack          | $SP \leftarrow (SP + 1); Pull (H)$                                                                                                                                                                          | -        | - | _             | -        | -        | -        | INH                                   | 8A                                               |                                                 | 2                                    |

| PULX                                                                                            | Pull X from Stack          | $SP \leftarrow (SP + 1); Pull (X)$                                                                                                                                                                          | -        | - | -             | -        | -        | -        | INH                                   | 88                                               |                                                 | 2                                    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                    | Rotate Left through Carry  | b7 b0                                                                                                                                                                                                       | <b>‡</b> | _ | _             | <b>‡</b> | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                    | Rotate Right through Carry | b7 b0                                                                                                                                                                                                       | <b>‡</b> | _ | _             | <b>‡</b> | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| RSP                                                                                             | Reset Stack Pointer        | SP ← \$FF                                                                                                                                                                                                   | -        | - | _             | _        | -        | _        | INH                                   | 9C                                               |                                                 | 1                                    |

MC68HC908LJ12 - Rev. 2.1

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared). (See Figure 9-10.)

FROM RESET BREAK INTERRUPT? YES NO YES I-BIT SET? NO YES INTERRUPT? NO STACK CPU REGISTERS SET I-BIT AS MANY INTERRUPTS AS EXIST ON CHIP LOAD PC WITH INTERRUPT VECTOR **FETCH NEXT** INSTRUCTION SWI YES **INSTRUCTION?** NO YES **UNSTACK CPU REGISTERS** INSTRUCTION? NO **EXECUTE INSTRUCTION**

Figure 9-10. Interrupt Processing

MC68HC908LJ12 — Rev. 2.1

## **Monitor ROM (MON)**

Description

Executes PULH and RTI instructions

Operand

None

Data Returned

None

Opcode

\$28

Command Sequence

FROM HOST

V RUN

RUN

Table 10-9. RUN (Run User Program) Command

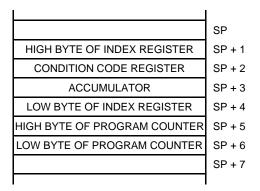

The MCU executes the SWI and PSHH instructions when it enters monitor mode. The RUN command tells the MCU to execute the PULH and RTI instructions. Before sending the RUN command, the host can modify the stacked CPU registers to prepare to run the host program. The READSP command returns the incremented stack pointer value, SP + 1. The high and low bytes of the program counter are at addresses SP + 5 and SP + 6.

Figure 10-7. Stack Pointer at Monitor Mode Entry

Technical Data MC68HC908LJ12 — Rev. 2.1

### 11.4 Pin Name Conventions

The text that follows describes both timers, TIM1 and TIM2. The TIM input/output (I/O) pin names are T[1,2]CH0 (timer channel 0) and T[1,2]CH1 (timer channel 1), where "1" is used to indicate TIM1 and "2" is used to indicate TIM2. The two TIMs share four I/O pins with four I/O port pins. The full names of the TIM I/O pins are listed in Table 11-1. The generic pin names appear in the text that follows.

**Table 11-1. Pin Name Conventions**

| TIM Generic Pir | n Names: | T[1,2]CH0  | T[1,2]CH1  |

|-----------------|----------|------------|------------|

| Full TIM        | TIM1     | PTB2/T1CH0 | PTB3/T1CH1 |

| Pin Names:      | TIM2     | PTB4/T2CH0 | PTB5/T2CH1 |

NOTE:

References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TCH0 may refer generically to T1CH0 and T2CH0, and TCH1 may refer to T1CH1 and T2CH1.

## 11.5 Functional Description

Figure 11-1 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels (per timer) are programmable independently as input capture or output compare channels.

### **Infrared Serial Communications**

PEIE — Receiver Parity Error Interrupt Enable Bit

This read/write bit enables SCI receiver CPU interrupt requests generated by the parity error bit, PE. (See 13.11.4 SCI Status Register 1.) Reset clears PEIE.

1 = SCI error CPU interrupt requests from PE bit enabled

0 = SCI error CPU interrupt requests from PE bit disabled

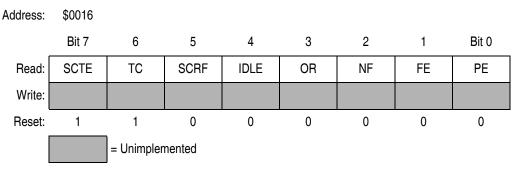

#### 13.11.4 SCI Status Register 1

SCI status register 1 contains flags to signal these conditions:

- Transfer of SCDR data to transmit shift register complete

- Transmission complete

- Transfer of receive shift register data to SCDR complete

- Receiver input idle

- Receiver overrun

- Noisy data

- Framing error

- Parity error

Figure 13-15. SCI Status Register 1 (SCS1)

### SCTE — SCI Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an SCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an SCI transmitter CPU interrupt request. In normal

**Technical Data**

MC68HC908LJ12 — Rev. 2.1

operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

#### TC — Transmission Complete Bit

This read-only bit is set when the SCTE bit is set, and no data, preamble, or break character is being transmitted. TC generates an SCI transmitter CPU interrupt request if the TCIE bit in SCC2 is also set. TC is automatically cleared when data, preamble or break is queued and ready to be sent. There may be up to 1.5 transmitter clocks of latency between queueing data, preamble, and break and the transmission actually starting. Reset sets the TC bit.

- 1 = No transmission in progress

- 0 = Transmission in progress

#### SCRF — SCI Receiver Full Bit

This clearable, read-only bit is set when the data in the receive shift register transfers to the SCI data register. SCRF can generate an SCI receiver CPU interrupt request. When the SCRIE bit in SCC2 is set, SCRF generates a CPU interrupt request. In normal operation, clear the SCRF bit by reading SCS1 with SCRF set and then reading the SCDR. Reset clears SCRF.

- 1 = Received data available in SCDR

- 0 = Data not available in SCDR

#### IDLE — Receiver Idle Bit

This clearable, read-only bit is set when 10 or 11 consecutive logic 1s appear on the receiver input. IDLE generates an SCI error CPU interrupt request if the ILIE bit in SCC2 is also set. Clear the IDLE bit by reading SCS1 with IDLE set and then reading the SCDR. After the receiver is enabled, it must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

# Section 14. Serial Peripheral Interface Module (SPI)

## 14.1 Contents

| 14.2 Introduction                                        | 270 |

|----------------------------------------------------------|-----|

| 14.3 Features                                            | 270 |

| 14.4 Pin Name Conventions and I/O Register Addresses     | 271 |

| 14.5 Functional Description                              |     |

| 14.5.1       Master Mode         14.5.2       Slave Mode |     |

| 14.6 Transmission Formats                                | 275 |

| 14.6.1 Clock Phase and Polarity Controls                 | 275 |

| 14.6.2 Transmission Format When CPHA = 0                 | 276 |

| 14.6.3 Transmission Format When CPHA = 1                 | 278 |

| 14.6.4 Transmission Initiation Latency                   | 279 |

| 14.7 Queuing Transmission Data                           | 281 |

| 14.8 Error Conditions                                    | 282 |

| 14.8.1 Overflow Error                                    | 282 |

| 14.8.2 Mode Fault Error                                  | 284 |

| 14.9 Interrupts                                          |     |

| 14.10 Resetting the SPI                                  | 288 |

| 14.11 Low-Power Modes                                    | 289 |

| 14.11.1 Wait Mode                                        | 289 |

| 14.11.2 Stop Mode                                        |     |

| 14.12 SPI During Break Interrupts                        | 290 |

| 14.13 I/O Signals                                        | 290 |

| 14.13.1 MISO (Master In/Slave Out)                       |     |

| 14.13.2 MOSI (Master Out/Slave In)                       |     |

| 11.10.2 Moor (Master Odvolave III)                       | 201 |

MC68HC908LJ12 - Rev. 2.1

## Serial Peripheral Interface Module (SPI)

| 14.13.3   | SPSCK (Serial Clock)            | 292 |

|-----------|---------------------------------|-----|

| 14.13.4   | SS (Slave Select)               | 292 |

| 14.13.5   | CGND (Clock Ground)             | 293 |

| 14.14 1/0 | O Registers                     | 294 |

| 14.14.1   | SPI Control Register            | 294 |

| 14.14.2   | SPI Status and Control Register | 296 |

| 14.14.3   | SPI Data Register               | 299 |

### 14.2 Introduction

This section describes the serial peripheral interface (SPI) module, which allows full-duplex, synchronous, serial communications with peripheral devices.

#### 14.3 Features

Features of the SPI module include the following:

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four master mode frequencies (maximum = bus frequency ÷ 2)

- Maximum slave mode frequency = bus frequency

- Serial clock with programmable polarity and phase

- Two separately enabled interrupts:

- SPRF (SPI receiver full)

- SPTE (SPI transmitter empty)

- Mode fault error flag with CPU interrupt capability

- Overflow error flag with CPU interrupt capability

- Programmable wired-OR mode

- I<sup>2</sup>C (inter-integrated circuit) compatibility

- I/O (input/output) port bit(s) software configurable with pullup device(s) if configured as input port bit(s)

## Serial Peripheral Interface Module (SPI)

The clock phase (CPHA) control bit selects one of two fundamentally different transmission formats. The clock phase and polarity should be identical for the master SPI device and the communicating slave device. In some cases, the phase and polarity are changed between transmissions to allow a master device to communicate with peripheral slaves having different requirements.

**NOTE:** Before writing to the CPOL bit or the CPHA bit, disable the SPI by clearing the SPI enable bit (SPE).

#### 14.6.2 Transmission Format When CPHA = 0

**Figure 14-4** shows an SPI transmission in which CPHA is logic 0. The figure should not be used as a replacement for data sheet parametric information.

Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The SS line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is at logic 0, so that only the selected slave drives to the master. The SS pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 14.8.2 Mode Fault Error.) When CPHA = 0, the first SPSCK edge is the MSB capture strobe. Therefore, the slave must begin driving its data before the first SPSCK edge, and a falling edge on the SS pin is used to start the slave data transmission. The slave's SS pin must be toggled back to high and then low again between each byte transmitted as shown in Figure 14-5.

### SPMSTR — SPI Master Bit

This read/write bit selects master mode operation or slave mode operation. Reset sets the SPMSTR bit.

- 1 = Master mode

- 0 = Slave mode

### CPOL — Clock Polarity Bit

This read/write bit determines the logic state of the SPSCK pin between transmissions. (See **Figure 14-4** and **Figure 14-6**.) To transmit data between SPI modules, the SPI modules must have identical CPOL values. Reset clears the CPOL bit.

#### CPHA — Clock Phase Bit

This read/write bit controls the timing relationship between the serial clock and SPI data. (See **Figure 14-4** and **Figure 14-6**.) To transmit data between SPI modules, the SPI modules must have identical CPHA values. When CPHA = 0, the  $\overline{SS}$  pin of the slave SPI module must be set to logic 1 between bytes. (See **Figure 14-12**.) Reset sets the CPHA bit.

#### SPWOM — SPI Wired-OR Mode Bit

This read/write bit disables the pullup devices on pins SPSCK, MOSI, and MISO so that those pins become open-drain outputs.

- 1 = Wired-OR SPSCK, MOSI, and MISO pins

- 0 = Normal push-pull SPSCK, MOSI, and MISO pins

#### SPE — SPI Enable

This read/write bit enables the SPI module. Clearing SPE causes a partial reset of the SPI. (See 14.10 Resetting the SPI.) Reset clears the SPE bit.

- 1 = SPI module enabled

- 0 = SPI module disabled

### SPTIE— SPI Transmit Interrupt Enable

This read/write bit enables CPU interrupt requests generated by the SPTE bit. SPTE is set when a byte transfers from the transmit data register to the shift register. Reset clears the SPTIE bit.

- 1 = SPTE CPU interrupt requests enabled

- 0 = SPTE CPU interrupt requests disabled

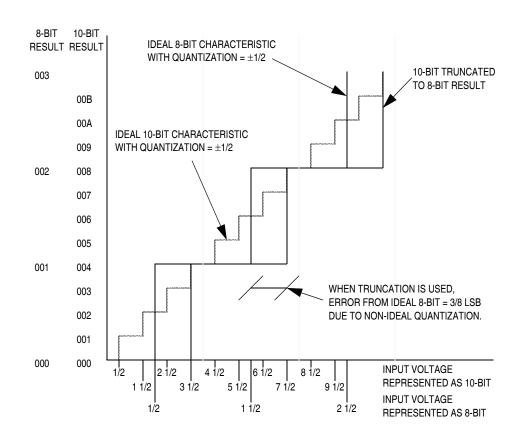

Finally, 8-bit truncation mode will place the eight MSBs in ADC data register low (ADRL). The two LSBs are dropped. This mode of operation is used when compatibility with 8-bit ADC designs are required. No interlocking between ADRH and ADRL is present.

**NOTE:** Quantization error is affected when only the most significant eight bits are used as a result. See **Figure 15-3**.

Figure 15-3. 8-Bit Truncation Mode Error

#### 15.4.6 Monotonicity

The conversion process is monotonic and has no missing codes.

## Analog-to-Digital Converter (ADC)

## 15.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating a CPU interrupt after each ADC conversion. A CPU interrupt is generated if the COCO bit is at logic 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled. The interrupt vector is defined in **Table 2-1**. **Vector Addresses**.

#### 15.6 Low-Power Modes

The STOP and WAIT instructions put the MCU in low powerconsumption standby modes.

#### 15.6.1 Wait Mode

The ADC continues normal operation in wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting the ADCH[4:0] bits to logic 1's before executing the WAIT instruction.

### 15.6.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

## 15.7 I/O Signals

The ADC module has nine channels, six channels are shared with port A and port C I/O pins; two channels are the ADC voltage reference inputs,  $V_{REFH}$  and  $V_{REFL}$ ; and one channel is the 1.2V bandgap reference voltage.

## **Liquid Crystal Display Driver (LCD)**

### 16.7.2 FP0-FP26 (Frontplane Drivers)

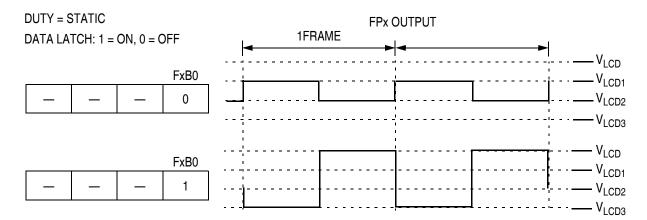

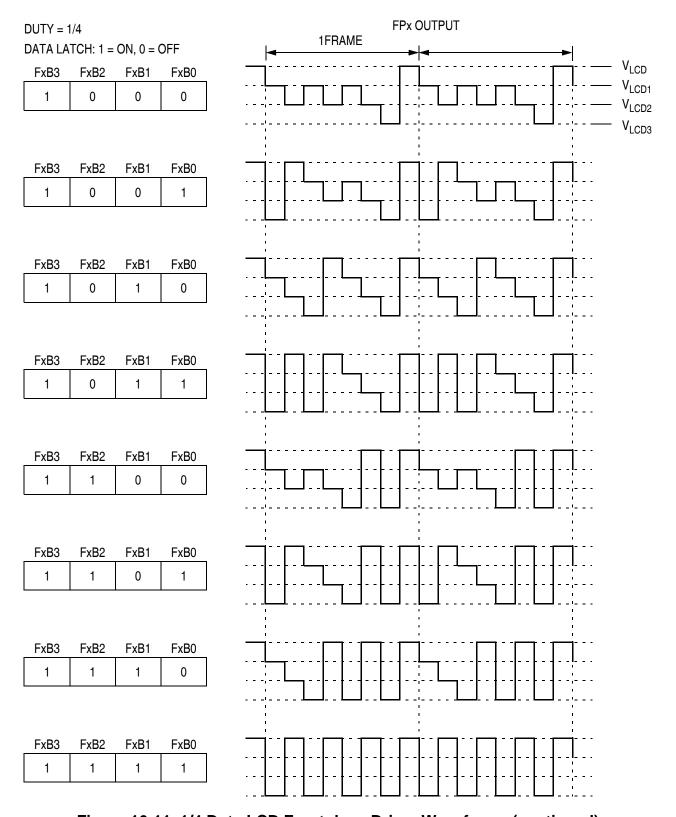

FP0–FP26 are the frontplane driver output pins. These are connected to the frontplane of the LCD panel. Depending on LCD duty selected and the contents in the LCD data registers, the voltage waveforms in **Figure 16-8**, **Figure 16-9**, and **Figure 16-10** appear on the frontplane pins.

FP19–FP26 are shared with port C I/O pins. These pins are configured for standard I/O or LCD use by the PCEL and PCEH bits in CONFIG2 register.

Figure 16-8. Static LCD Frontplane Driver Waveforms

Figure 16-11. 1/4 Duty LCD Frontplane Driver Waveforms (continued)

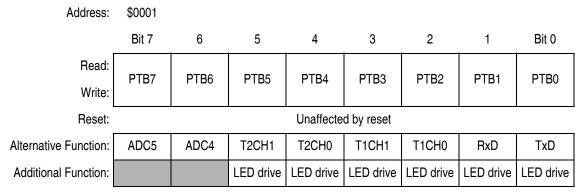

### 17.4 Port B

Port B is a 8-bit special function port that shares two of its port pins with the infrared serial communication interface (IRSCI) module, two of its port pins with the timer interface module 1 (TIM1) module, two of its port pins with the timer interface module 2 (TIM2), and two of its port pins with the ADC module.

Port pins PTB0-PTB5 can be configured for direct LED drive.

### 17.4.1 Port B Data Register (PTB)

The port B data register contains a data latch for each of the eight port B pins.

**NOTE:** Bit 4-bit 7 of PTB are not available in a 52-pin LQFP.

Figure 17-5. Port B Data Register (PTB)

#### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

#### TxD, RxD — SCI Data I/O Pins

The TxD and RxD pins are the transmit data output and receive data input for the IRSCI module. The enable SCI bit, ENSCI, in the SCI control register 1 enables the PTB0/TxD and PTB1/RxD pins as SCI TxD and RxD pins and overrides any control from the port I/O. See Section 13. Infrared Serial Communications Interface Module (IRSCI).

MC68HC908LJ12 — Rev. 2.1

### 19.5 Functional Description

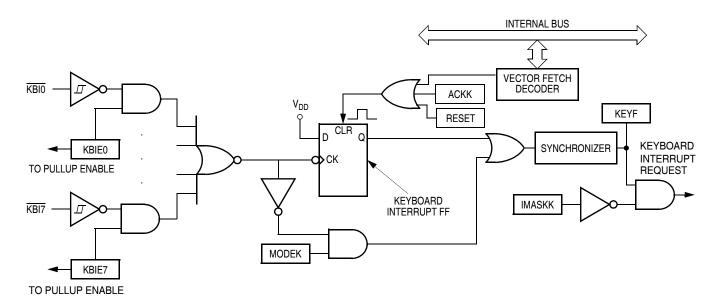

Figure 19-2. Keyboard Interrupt Block Diagram

Writing to the KBIE7–KBIE0 bits in the keyboard interrupt enable register independently enables or disables a port A or port D pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin in port A or port D also enables its internal pull-up device. A logic 0 applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

- If the keyboard interrupt is falling edge- and low level-sensitive, an interrupt request is present as long as any keyboard pin is low.

If the MODEK bit is set, the keyboard interrupt pins are both falling edgeand low level-sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

MC68HC908LJ12 — Rev. 2.1

## 23.4 Functional Operating Range

**Table 23-2. Operating Range**

| Characteristic              | Symbol          | Value                    | Unit |

|-----------------------------|-----------------|--------------------------|------|

| Operating temperature range | T <sub>A</sub>  | -40 to +85               | °C   |

| Operating voltage range     | V <sub>DD</sub> | 3.3V ± 10%<br>5.0V ± 10% | V    |

## 23.5 Thermal Characteristics

**Table 23-3. Thermal Characteristics**

| Characteristic                                                 | Symbol            | Value                                                                    | Unit |

|----------------------------------------------------------------|-------------------|--------------------------------------------------------------------------|------|

| Thermal resistance<br>52-pin LQFP<br>64-pin LQFP<br>64-pin QFP | $\theta_{\sf JA}$ | 85<br>80<br>70                                                           | °C/W |

| I/O pin power dissipation                                      | P <sub>I/O</sub>  | User determined                                                          | W    |

| Power dissipation <sup>(1)</sup>                               | P <sub>D</sub>    | $P_D = (I_{DD} \times V_{DD}) + P_{I/O} = K/(T_J + 273 ^{\circ}C)$       | W    |

| Constant <sup>(2)</sup>                                        | К                 | $P_{D} \times (T_{A} + 273 \text{ °C})$ $+ P_{D}^{2} \times \theta_{JA}$ | W/°C |

| Average junction temperature                                   | TJ                | $T_A + (P_D \times \theta_{JA})$                                         | °C   |

#### Notes:

- Power dissipation is a function of temperature.

K constant unique to the device. K can be determined for a known T<sub>A</sub> and measured P<sub>D</sub>. With this value of K, P<sub>D</sub> and T<sub>J</sub> can be determined for any value of T<sub>A</sub>.

## **Electrical Specifications**

### 23.10 5.0V Oscillator Characteristics

Table 23-8. 5.0 V Oscillator Specifications

| Characteristic                                  | Symbol            | Min  | Тур                      | Max     | Unit |

|-------------------------------------------------|-------------------|------|--------------------------|---------|------|

| Internal oscillator clock frequency             | f <sub>ICLK</sub> | 46 k | 47 k <sup>(1)</sup>      | 48k     | Hz   |

| External reference clock to OSC1 <sup>(2)</sup> | f <sub>OSC</sub>  | dc   | _                        | 20M     | Hz   |

| Crystal reference frequency <sup>(3)</sup>      | f <sub>XCLK</sub> |      | 32.768k                  | 4.9152M | Hz   |

| Crystal load capacitance <sup>(4)</sup>         | C <sub>L</sub>    | _    | _                        | _       |      |

| Crystal fixed capacitance                       | C <sub>1</sub>    | _    | 2 × C <sub>L</sub> (25p) | _       | F    |

| Crystal tuning capacitance                      | C <sub>2</sub>    | _    | 2 × C <sub>L</sub> (25p) | _       | F    |

| Feedback bias resistor                          | R <sub>B</sub>    | _    | 10M                      | _       | Ω    |

| Series resistor <sup>(5)</sup>                  | R <sub>S</sub>    | _    | 100k                     | _       | Ω    |

#### Notes:

- 1. Typical value reflect average measurements at midpoint of voltage range, 25 °C only.

- 2. No more than 10% duty cycle deviation from 50%.

- 3. Fundamental mode crystals only.

- 4. Consult crystal manufacturer's data.

- 5. Not Required for high frequency crystals.

### 23.11 3.3V Oscillator Characteristics

Table 23-9. 3.3 V Oscillator Specifications

| Characteristic                                  | Symbol            | Min   | Тур                      | Max     | Unit |

|-------------------------------------------------|-------------------|-------|--------------------------|---------|------|

| Internal oscillator clock frequency             | f <sub>ICLK</sub> | 42.8k | 43.4k <sup>(1)</sup>     | 44k     | Hz   |

| External reference clock to OSC1 <sup>(2)</sup> | f <sub>OSC</sub>  | dc    | _                        | 16M     | Hz   |

| Crystal reference frequency <sup>(3)</sup>      | f <sub>XCLK</sub> |       | 32.768k                  | 4.9152M | Hz   |

| Crystal load capacitance <sup>(4)</sup>         | C <sub>L</sub>    | _     | _                        | _       |      |

| Crystal fixed capacitance                       | C <sub>1</sub>    | _     | 2 × C <sub>L</sub> (25p) | _       | F    |

| Crystal tuning capacitance                      | C <sub>2</sub>    | _     | 2 × C <sub>L</sub> (25p) | _       | F    |

| Feedback bias resistor                          | R <sub>B</sub>    | _     | 10M                      | _       | Ω    |

| Series resistor <sup>(5)</sup>                  | R <sub>S</sub>    | _     | 100k                     | _       | Ω    |

#### Notes:

- 1. Typical value reflect average measurements at midpoint of voltage range, 25 °C only.

- 2. No more than 10% duty cycle deviation from 50%.

- 3. Fundamental mode crystals only.

- 4. Consult crystal manufacturer's data.

- 5. Not Required for high frequency crystals.

**Technical Data**

MC68HC908LJ12 — Rev. 2.1