Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

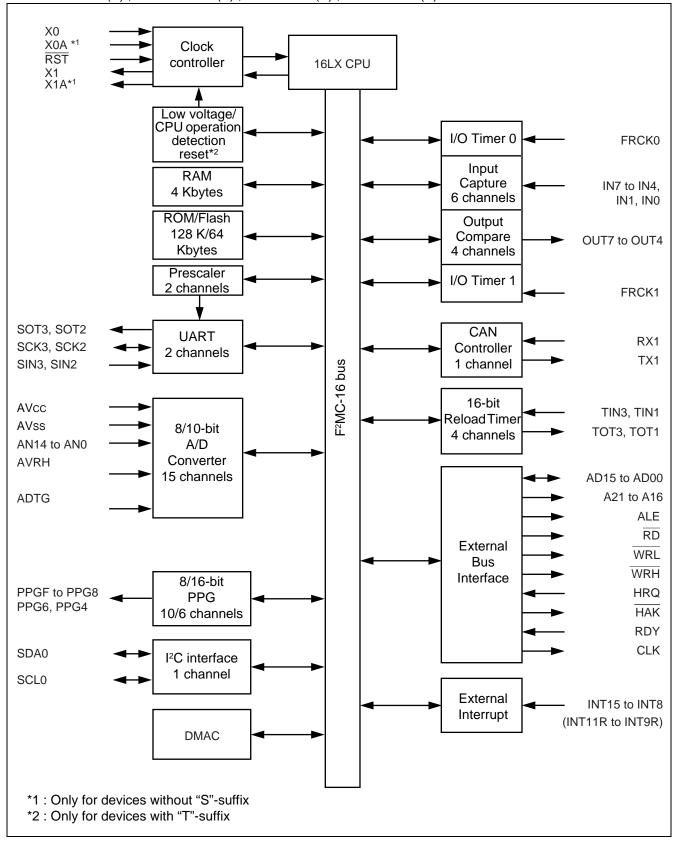

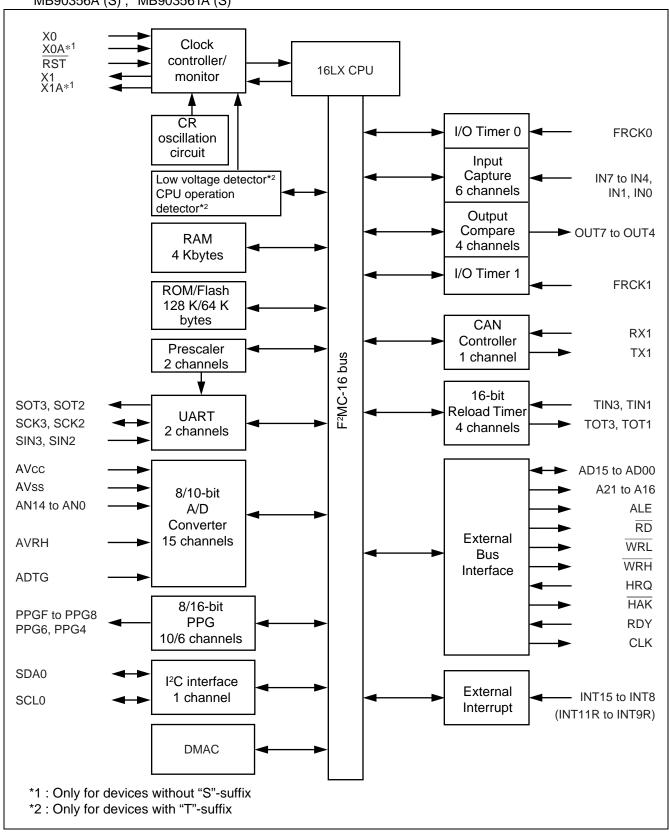

| Core Processor             | F <sup>2</sup> MC-16LX                                                      |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 24MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                       |

| Peripherals                | DMA, LVD, POR, WDT                                                          |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 15x8/10b                                                                |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-LQFP                                                                     |

| Supplier Device Package    | 64-LQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f351spfm-ge1 |

#### (Continued)

#### • Dual operation flash memory (only flash memory devices with A-suffix)

• Erase/write and read can be executed in the different bank (Upper Bank/Lower Bank) at the same time.

#### • Models that support + 125 °C

- Devices without A-suffix (excluding evaluation device) : The maximum operating frequency is 16 MHz (at  $T_A = +125$  °C).

- Devices with A-suffix (excluding evaluation device) : The maximum operating frequency is 24 MHz (at  $T_A = +125$  °C).

#### • Flash security function

• Protects the content of Flash memory (MB90F352x and MB90F357x only)

#### • External bus interface

• 4 Mbytes external memory space

#### \*: I2C license:

Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use, these components in an I<sup>2</sup>C system provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

### **■ PRODUCT LINEUP 1**

| Part Number                                  | MD00E3E4                                                                                                                                                                                                                                                                                                                               | MD0052546                            | MB005254.A                                                     | MD00E354TA                | MD005354 A C               | MD00505474.0                |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|---------------------------|----------------------------|-----------------------------|--|--|--|

| Parameter                                    | MB90F351,<br>MB90F352                                                                                                                                                                                                                                                                                                                  | MB90F351S,<br>MB90F352S              | MB90F351A,<br>MB90F352A                                        | MB90F351TA,<br>MB90F352TA | MB90F351AS,<br>MB90F352AS  | MB90F351TAS,<br>MB90F352TAS |  |  |  |

| CPU                                          |                                                                                                                                                                                                                                                                                                                                        | F <sup>2</sup> MC-16LX CPU           |                                                                |                           |                            |                             |  |  |  |

| System clock                                 |                                                                                                                                                                                                                                                                                                                                        |                                      | $(\times 1, \times 2, \times 3, \times 4,$<br>n time : 42 ns ( |                           |                            | 6)                          |  |  |  |

| ROM                                          | Flash memory<br>64Kbytes: N<br>128Kbytes: N                                                                                                                                                                                                                                                                                            | 1B90F351(S)                          | 64Kbytes: N                                                    | \ ,,                      | MB90F351TA(<br>MB90F352TA( | ,                           |  |  |  |

| RAM                                          |                                                                                                                                                                                                                                                                                                                                        |                                      | 4 Kb                                                           | ytes                      |                            |                             |  |  |  |

| Emulator-specific power supply*1             |                                                                                                                                                                                                                                                                                                                                        |                                      | _                                                              | _                         |                            |                             |  |  |  |

| Sub clock pin<br>(X0A, X1A)<br>(Max 100 kHz) | Yes                                                                                                                                                                                                                                                                                                                                    | No                                   | Y                                                              | es                        | N                          | Ю                           |  |  |  |

| Clock monitor function                       |                                                                                                                                                                                                                                                                                                                                        |                                      | N                                                              | lo                        |                            |                             |  |  |  |

| Low voltage/CPU operation detection reset    | N                                                                                                                                                                                                                                                                                                                                      | lo                                   | No                                                             | Yes                       | No                         | Yes                         |  |  |  |

| Operating voltage range                      | 3.5 V to 5.5 V : at normal operating (not using A/D converter) 4.0 V to 5.5 V : at using A/D converter/Flash programming 4.5 V to 5.5 V : at using external bus                                                                                                                                                                        |                                      |                                                                |                           |                            |                             |  |  |  |

| Operating temperature range                  | -40 °C to +10<br>up to 16 MHz r                                                                                                                                                                                                                                                                                                        | 5 °C (+125 °C<br>machine clock)      |                                                                | –40 °C to                 | ) +125 °C                  |                             |  |  |  |

| Package                                      |                                                                                                                                                                                                                                                                                                                                        |                                      | LQF                                                            | P-64                      |                            |                             |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                        |                                      |                                                                | nnels                     |                            |                             |  |  |  |

| UART                                         | Special synchi                                                                                                                                                                                                                                                                                                                         | ronous options                       | ngs using a deo<br>for adapting to<br>er as master or          | different synch           | ronous serial pr           | rotocols                    |  |  |  |

| I <sup>2</sup> C (400 Kbps)                  |                                                                                                                                                                                                                                                                                                                                        |                                      | 1 cha                                                          | annel                     |                            |                             |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                        |                                      | 15 cha                                                         | annels                    |                            |                             |  |  |  |

| A/D Converter                                | 10-bit or 8-bit in Conversion time                                                                                                                                                                                                                                                                                                     |                                      | cludes sample                                                  | time (per one o           | channel)                   |                             |  |  |  |

| 16-bit Reload Timer (4 channels)             |                                                                                                                                                                                                                                                                                                                                        | ck frequency : for<br>rnal Event Cou | sys/2¹, fsys/2³, f<br>nt function.                             | $fsys/2^5$ (fsys = 1      | Machine clock f            | requency)                   |  |  |  |

|                                              | I/O Timer 0 (clock input FRCK0) corresponds to ICU 0/1. I/O Timer 1 (clock input FRCK1) corresponds to ICU 4/5/6/7, OCU 4/5/6/7.                                                                                                                                                                                                       |                                      |                                                                |                           |                            |                             |  |  |  |

| 16-bit I/O Timer<br>(2 channels)             | Signals an interrupt when overflowing. Supports Timer Clear when a match with Output Compare (Channel 0, 4). Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> (fsys = Machine clock frequency) |                                      |                                                                |                           |                            |                             |  |  |  |

| 16-hit Output                                |                                                                                                                                                                                                                                                                                                                                        |                                      | 4 cha                                                          | nnels                     |                            |                             |  |  |  |

| 16-bit Output<br>Compare                     |                                                                                                                                                                                                                                                                                                                                        |                                      | bit I/O Timer m<br>an be used to g                             |                           |                            | gisters.                    |  |  |  |

### **■ PRODUCT LINEUP 3**

| Part Number                               | MB90F356A,                                                                                                                                                                                                                                   | MB90F356TA,                                                                             | MB90F356AS,                        | MB90F356TAS,                        |  |  |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|-------------------------------------|--|--|--|--|

| Parameter                                 | MB90F357A                                                                                                                                                                                                                                    | MB90F357TA                                                                              | MB90F357AS                         | MB90F357TAS                         |  |  |  |  |

| CPU                                       | F <sup>2</sup> MC-16LX CPU                                                                                                                                                                                                                   |                                                                                         |                                    |                                     |  |  |  |  |

| System clock                              |                                                                                                                                                                                                                                              | Itiplier ( $\times$ 1, $\times$ 2, $\times$ 3, $\times$ 4, xecution time : 42 ns (      |                                    |                                     |  |  |  |  |

| ROM                                       |                                                                                                                                                                                                                                              | nemory<br>56A(S), MB90F356TA(<br>57A(S), MB90F357TA(                                    |                                    |                                     |  |  |  |  |

| RAM                                       |                                                                                                                                                                                                                                              | 4 Kb                                                                                    | ytes                               |                                     |  |  |  |  |

| Emulator-specific power supply*1          |                                                                                                                                                                                                                                              | _                                                                                       | _                                  |                                     |  |  |  |  |

| Sub clock pin<br>(X0A, X1A)               | Ye                                                                                                                                                                                                                                           | es                                                                                      | _ ·                                | lo<br>tion can be used as<br>clock) |  |  |  |  |

| Clock monitor function                    |                                                                                                                                                                                                                                              | Yo                                                                                      | es                                 |                                     |  |  |  |  |

| Low voltage/CPU operation detection reset | No                                                                                                                                                                                                                                           | Yes                                                                                     | No                                 | Yes                                 |  |  |  |  |

| Operating voltage range                   |                                                                                                                                                                                                                                              | mal operating (not using A/D converter/Flashing external bus                            |                                    |                                     |  |  |  |  |

| Operating temperature range               |                                                                                                                                                                                                                                              | −40 °C to                                                                               | ) +125 °C                          |                                     |  |  |  |  |

| Package                                   |                                                                                                                                                                                                                                              | LQF                                                                                     | P-64                               |                                     |  |  |  |  |

| UART                                      | Special synchronous                                                                                                                                                                                                                          | 2 cha<br>ate settings using a dec<br>options for adapting to<br>ong either as master or | different synchronous              | serial protocols                    |  |  |  |  |

| I <sup>2</sup> C (400 Kbps)               | LIN Tunctionality worki                                                                                                                                                                                                                      |                                                                                         | annel                              |                                     |  |  |  |  |

| Τ Ο (400 Πορο)                            |                                                                                                                                                                                                                                              |                                                                                         | annels                             |                                     |  |  |  |  |

| A/D Converter                             | 10-bit or 8-bit resolution Conversion time : Min                                                                                                                                                                                             | on<br>3 μs includes sample                                                              | time (per one channel)             | )                                   |  |  |  |  |

| 16-bit Reload Timer (4 channels)          | Operation clock freque<br>Supports External Eve                                                                                                                                                                                              | ency: fsys/21, fsys/23, fent Count function.                                            | sys/2 <sup>5</sup> (fsys = Machine | e clock frequency)                  |  |  |  |  |

| 10 1 1/10 T                               | I/O Timer 0 (clock input FRCK0) corresponds to ICU 0/1. I/O Timer 1 (clock input FRCK1) corresponds to ICU 4/5/6/7, OCU 4/5/6/7.                                                                                                             |                                                                                         |                                    |                                     |  |  |  |  |

| 16-bit I/O Timer<br>(2 channels)          | Signals an interrupt when overflowing. Supports Timer Clear when a match with Output Compare (Channel 0, 4). Operation clock frequency: fsys, fsys/2¹, fsys/2², fsys/2³, fsys/2⁴, fsys/2⁵, fsys/2⁵, fsys/2⁵ (fsys = Machine clock frequency) |                                                                                         |                                    |                                     |  |  |  |  |

| 16-bit Output                             |                                                                                                                                                                                                                                              |                                                                                         | nnels                              |                                     |  |  |  |  |

| Compare                                   |                                                                                                                                                                                                                                              | hen 16-bit I/O Timer m<br>isters can be used to g                                       | •                                  |                                     |  |  |  |  |

| Part Number Parameter          | MB90356A,<br>MB90357A                                                                                                                                                                                                                                                                                                                                       | MB90356TA,<br>MB90357TA                                                 | MB90356AS,<br>MB90357AS                                                                                                                                        | MB90356TAS,<br>MB90357TAS | MB90V340A-<br>103 | MB90V340A-<br>104 |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------|-------------------|--|--|

| 16-bit Output                  |                                                                                                                                                                                                                                                                                                                                                             | 4 cha                                                                   | innels                                                                                                                                                         |                           | 8 cha             | nnels             |  |  |

| Compare                        |                                                                                                                                                                                                                                                                                                                                                             |                                                                         | atches with out<br>enerate an out                                                                                                                              | put compare registers.    |                   |                   |  |  |

|                                |                                                                                                                                                                                                                                                                                                                                                             | 6 cha                                                                   | innels                                                                                                                                                         |                           | 8 cha             | nnels             |  |  |

| 16-bit Input Capture           | Retains freerui                                                                                                                                                                                                                                                                                                                                             | n timer value by                                                        | / (rising edge, fa                                                                                                                                             | alling edge or ris        | sing & falling ed | ge), signals an   |  |  |

| 8/16-bit<br>Programmable Pulse | 8-bit re                                                                                                                                                                                                                                                                                                                                                    | annels (16-bit)<br>8-bit reload o<br>eload registers<br>eload registers | 8 channels (16-bit)/16 channels (8-bit) 8-bit reload counters × 16 8-bit reload registers for L pulse width × 16 8-bit reload registers for H pulse width × 16 |                           |                   |                   |  |  |

| Generator                      | Supports 8-bit and 16-bit operation modes.  A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler + 8-bit reload counter.  Operation clock frequency: fsys, fsys/2¹, fsys/2², fsys/2³, fsys/2⁴ or 128 µs@fosc = 4 MHz (fsys = Machine clock frequency, fosc = Oscillation clock frequency)                   |                                                                         |                                                                                                                                                                |                           |                   |                   |  |  |

|                                |                                                                                                                                                                                                                                                                                                                                                             | 1 cha                                                                   | 3 cha                                                                                                                                                          | nnels                     |                   |                   |  |  |

| CAN Interface                  | Conforms to CAN Specification Version 2.0 Part A and B. Automatic re-transmission in case of error Automatic transmission responding to Remote Frame Prioritized 16 message buffers for data and ID Supports multiple messages. Flexible configuration of acceptance filtering: Full bit compare/Full bit mask/Two partial bit masks Supports up to 1 Mbps. |                                                                         |                                                                                                                                                                |                           |                   |                   |  |  |

|                                |                                                                                                                                                                                                                                                                                                                                                             | 8 cha                                                                   | innels                                                                                                                                                         |                           | 16 ch             | annels            |  |  |

| External Interrupt             |                                                                                                                                                                                                                                                                                                                                                             |                                                                         | ng edge, startir<br>ces (El²OS) and                                                                                                                            |                           | vel input, extern | al interrupt,     |  |  |

| D/A converter                  |                                                                                                                                                                                                                                                                                                                                                             | _                                                                       | _                                                                                                                                                              |                           | 2 cha             | nnels             |  |  |

| I/O Ports                      | Virtually all external pins can be used as general purpose I/O port. All push-pull outputs Bit-wise settable as input/output or peripheral module signal Settable as CMOS schmitt trigger/ automotive inputs TTL input level settable for external bus (only for external bus pin)                                                                          |                                                                         |                                                                                                                                                                |                           |                   |                   |  |  |

| Flash Memory                   |                                                                                                                                                                                                                                                                                                                                                             |                                                                         | _                                                                                                                                                              | _                         |                   |                   |  |  |

| Corresponding EVA name         | MB90V3                                                                                                                                                                                                                                                                                                                                                      | 40A-104                                                                 | MB90V3                                                                                                                                                         | 40A-103                   | _                 | _                 |  |  |

<sup>\*:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

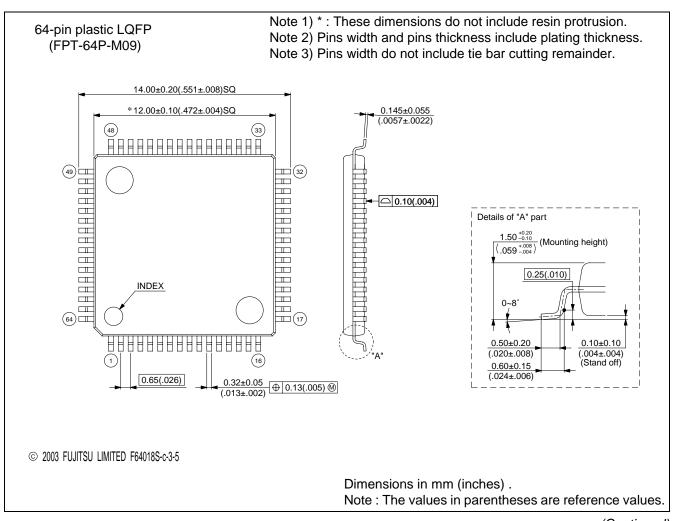

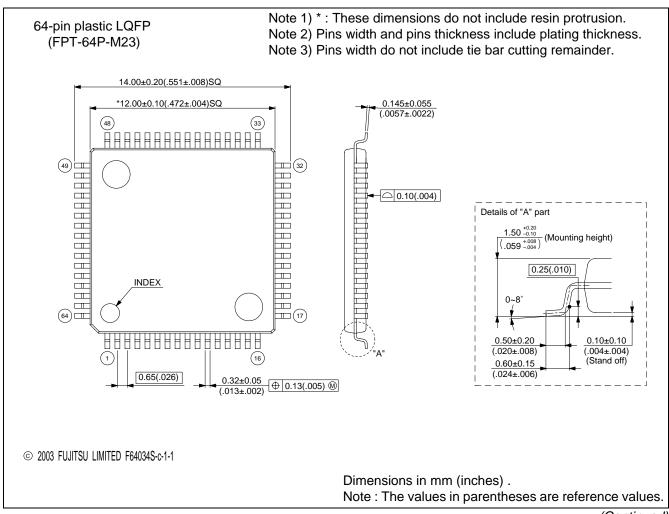

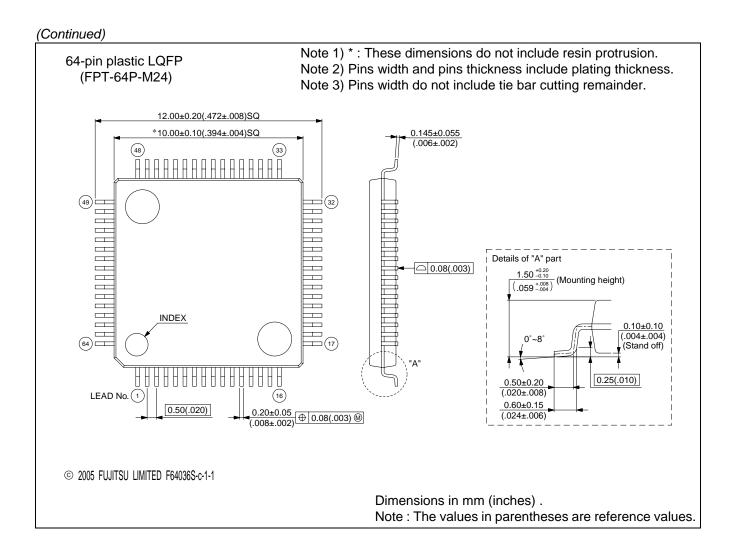

### ■ PACKAGES AND PRODUCT CORRESPONDENCE

| Package                               | MB90V340A<br>-101<br>-102<br>-103<br>-104 | MB90F351<br>MB90F351S<br>MB90F352<br>MB90F352S | MB90F351A (S) , MB90F351TA (S)<br>MB90F352A (S) , MB90F352TA (S)<br>MB90F356A (S) , MB90F356TA (S)<br>MB90F357A (S) , MB90F357TA (S)<br>MB90351A (S) , MB90351TA (S)<br>MB90352A (S) , MB90352TA (S)<br>MB90356A (S) , MB90356TA (S)<br>MB90357A (S) , MB90357TA (S) |

|---------------------------------------|-------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGA-299C-A01                          | 0                                         | ×                                              | ×                                                                                                                                                                                                                                                                    |

| FPT-64P-M09<br>(12 mm, 0.65 mm pitch) | ×                                         | 0                                              | ×                                                                                                                                                                                                                                                                    |

| FPT-64P-M23<br>(12 mm, 0.65 mm pitch) | ×                                         | ×                                              | 0                                                                                                                                                                                                                                                                    |

| FPT-64P-M24<br>(10 mm, 0.50 mm pitch) | ×                                         | ×                                              | O*                                                                                                                                                                                                                                                                   |

<sup>\*:</sup> This device is under development.

$\bigcirc$  : Yes,  $\times$  : No

Note: Refer to "■ PACKAGE DIMENSIONS" for detail of each package.

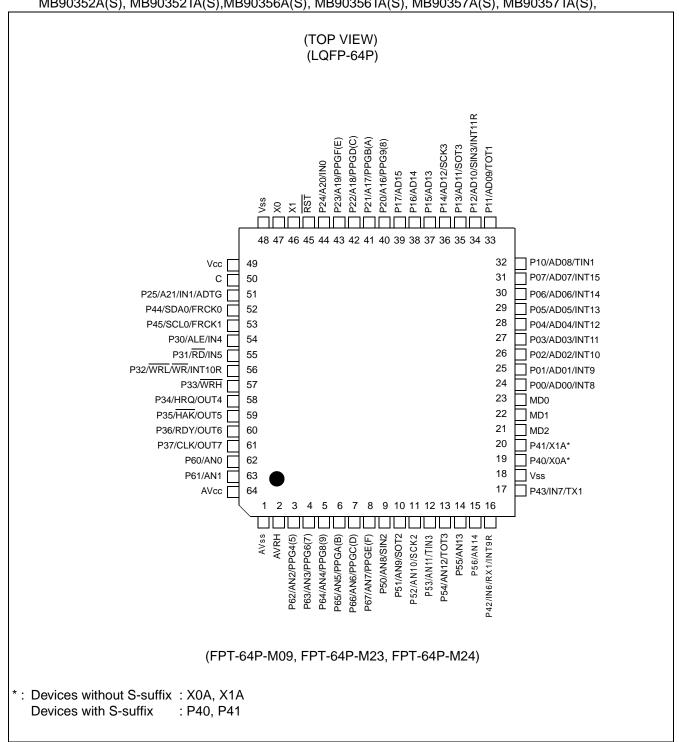

#### **■ PIN ASSIGNMENTS**

MB90F351(S), MB90F352(S), MB90F351A(S), MB90F351TA(S), MB90F352A(S), MB90F352TA(S), MB90F356A(S), MB90F356TA(S), MB90F357A(S), MB90F357TA(S), MB90351A(S), MB90352TA(S), MB90352TA(S), MB90356TA(S), MB90357TA(S), MB907TA(S), MB907TA(

| Pin No.  | Din nama      | Circuit | Franction                                                                                                                                     |  |  |  |  |  |

|----------|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LQFP64*  | Pin name      | type    | Function                                                                                                                                      |  |  |  |  |  |

|          | P00 to P07    |         | General purpose I/O ports. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode. |  |  |  |  |  |

| 24 to 31 | AD00 to AD07  | G       | Input/output pins of external address data bus lower 8 bits. This function is enabled when the external bus is enabled.                       |  |  |  |  |  |

|          | INT8 to INT15 |         | External interrupt request input pins for INT8 to INT15                                                                                       |  |  |  |  |  |

|          | P10           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |  |

| 32       | AD08          | G       | Input/output pin for external bus address data bus bit 8. This function is enabled when external bus is enabled.                              |  |  |  |  |  |

|          | TIN1          |         | Event input pin for reload timer1                                                                                                             |  |  |  |  |  |

|          | P11           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |  |

| 33       | AD09          | G       | Input/output pin for external bus address data bus bit 9. This function is enabled when external bus is enabled.                              |  |  |  |  |  |

|          | TOT1          |         | Output pin for reload timer1                                                                                                                  |  |  |  |  |  |

|          | P12           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |  |

| 34       | AD10          | N       | Input/output pin for external bus address data bus bit 10. This function enabled when external bus is enabled.                                |  |  |  |  |  |

|          | SIN3          |         | Serial data input pin for UART3                                                                                                               |  |  |  |  |  |

|          | INT11R        |         | External interrupt request input pin for INT11                                                                                                |  |  |  |  |  |

|          | P13           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |  |

| 35       | AD11          | G       | Input/output pin for external bus address data bus bit 11. This function is enabled when external bus is enabled.                             |  |  |  |  |  |

|          | SOT3          |         | Serial data output pin for UART3                                                                                                              |  |  |  |  |  |

|          | P14           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |  |

| 36       | AD12          | G       | Input/output pin for external bus address data bus bit 12. This function is enabled when external bus is enabled.                             |  |  |  |  |  |

|          | SCK3          |         | Clock input/output pin for UART3                                                                                                              |  |  |  |  |  |

| 37       | P15           | N       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |  |

| 31       | AD13          | IN      | Input/output pin for external bus address data bus bit 13. This function is enabled when external bus is enabled.                             |  |  |  |  |  |

| 38       | P16           | G       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |  |

| 30       | AD14          | G       | Input/output pin for external bus address data bus bit 14. This function is enabled when external bus is enabled.                             |  |  |  |  |  |

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                    | Remarks                                                                       |

|------|--------------------------------------------|-------------------------------------------------------------------------------|

| А    | X1 Xout  X0 Standby control signal         | Oscillation circuit • High-speed oscillation feedback resistor = approx. 1 MΩ |

| В    | X1A Xout X0A Standby control signal        | Oscillation circuit • Low-speed oscillation feedback resistor = approx. 10 MΩ |

| С    | R CMOS hysteresis inputs                   | Mask ROM device:                                                              |

| D    | R CMOS hysteresis inputs                   | Mask ROM device:                                                              |

| E    | Pull-up resistor  R CMOS hysteresis inputs | CMOS hysteresis input pin • Pull-up resistor value: approx. 50 kΩ             |

MB90F352 (S), MB90F351 (S), MB90F352A (S), MB90F352TA (S), MB90F351A (S), MB90F351TA (S), MB90352A (S), MB90352TA (S), MB90351TA (S)

MB90F357A (S), MB90F357TA (S), MB90F356A (S), MB90F356TA (S), MB90357A (S), MB90357TA (S),

MB90356A (S), MB90356TA (S)

| Address           | Register                                             | Abbrevia-<br>tion                                | Access      | Resource name                | Initial value |  |  |  |

|-------------------|------------------------------------------------------|--------------------------------------------------|-------------|------------------------------|---------------|--|--|--|

| 7950н             | Serial Mode Register 3                               | SMR3                                             | W, R/W      |                              | 0000000В      |  |  |  |

| 7951н             | Serial Control Register 3                            | SCR3                                             | W, R/W      |                              | 0000000В      |  |  |  |

| 7952н             | Reception/Transmission Data<br>Register 3            | RDR3/<br>TDR3                                    | R/W         |                              | 00000000в     |  |  |  |

| 7953н             | Serial Status Register 3                             | SSR3                                             | R,R/W       | UART3                        | 00001000в     |  |  |  |

| 7954н             | Extended Communication Control Register 3            | ECCR3                                            | R,W,<br>R/W | UARTS                        | 000000XXB     |  |  |  |

| 7955н             | Extended Status/Control Register 3                   | ESCR3                                            | R/W         |                              | 00000100в     |  |  |  |

| 7956н             | Baud Rate Generator Register 30                      | BGR30                                            | R/W         |                              | 0000000в      |  |  |  |

| 7957н             | Baud Rate Generator Register 31                      | BGR31                                            | R/W         |                              | 0000000в      |  |  |  |

| 7958н,<br>7959н   |                                                      | Reserve                                          | ed          |                              |               |  |  |  |

| 7960н             | Clock Monitor Function Control<br>Register           | CSVCR                                            | R, R/W      | Clock Monitor                | 00011100в     |  |  |  |

| 7961н to<br>796Dн | Reserved                                             |                                                  |             |                              |               |  |  |  |

| 796Ен             | CAN Direct Mode Register                             | CAN Direct Mode Register CDMR R/W CAN Clock Sync |             |                              |               |  |  |  |

| <b>796</b> Fн     |                                                      | Reserve                                          | ed          |                              |               |  |  |  |

| 7970н             | I <sup>2</sup> C Bus Status Register 0               | IBSR0                                            | R           |                              | 0000000В      |  |  |  |

| 7971н             | I <sup>2</sup> C Bus Control Register 0              | IBCR0                                            | W,R/W       |                              | 0000000В      |  |  |  |

| 7972н             | I <sup>2</sup> C 10-bit Slave Address Register 0     | ITBAL0                                           | R/W         | I <sup>2</sup> C Interface 0 | 0000000В      |  |  |  |

| 7973н             | 17-0 TO-bit Slave Address Register 0                 | ITBAH0                                           | R/W         |                              | 0000000В      |  |  |  |

| 7974н             | I <sup>2</sup> C 10-bit Slave Address Mask Register  | ITMKL0                                           | R/W         |                              | 111111111     |  |  |  |

| 7975н             | 0                                                    | ITMKH0                                           | R/W         |                              | 00111111в     |  |  |  |

| 7976н             | I <sup>2</sup> C 7-bit Slave Address Register 0      | ISBA0                                            | R/W         |                              | 0000000в      |  |  |  |

| 7977н             | I <sup>2</sup> C 7-bit Slave Address Mask Register 0 | ISMK0                                            | R/W         |                              | 01111111в     |  |  |  |

| 7978н             | I <sup>2</sup> C data register 0                     | IDAR0                                            | R/W         |                              | 0000000в      |  |  |  |

| 7979н,<br>797Ан   |                                                      | Reserve                                          | ed          |                              |               |  |  |  |

| 797Вн             | I <sup>2</sup> C Clock Control Register 0            | ICCR0                                            | R/W         | I <sup>2</sup> C Interface 0 | 00011111в     |  |  |  |

| 797Сн to<br>79А1н |                                                      | Reserve                                          | ed          |                              |               |  |  |  |

| 79А2н             | Flash Write Control Register 0                       | FWR0                                             | R/W         | D 10 "                       | 0000000В      |  |  |  |

| 79А3н             | Flash Write Control Register 1                       | FWR1                                             | R/W         | Dual Operation<br>Flash      | 0000000В      |  |  |  |

| 79А4н             | Sector Change Setting Register                       | SSR0                                             | R/W         | 1 10311                      | 00XXXXX0в     |  |  |  |

| 79А5н to<br>79С1н | Reserved                                             |                                                  |             |                              |               |  |  |  |

### (Continued)

| Address           | Register                                                   | Abbrevia-<br>tion | Access | Resource name             | Initial value |  |  |  |

|-------------------|------------------------------------------------------------|-------------------|--------|---------------------------|---------------|--|--|--|

| 79С2н             | Setting Prohibited                                         |                   |        |                           |               |  |  |  |

| 79С3н to<br>79DFн | Reserved                                                   |                   |        |                           |               |  |  |  |

| 79Е0н             | Detect Address Setting Register 0                          | PADR0             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79Е1н             | Detect Address Setting Register 0                          | PADR0             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79Е2н             | Detect Address Setting Register 0                          | PADR0             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79ЕЗн             | Detect Address Setting Register 1                          | PADR1             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79Е4н             | Detect Address Setting Register 1                          | PADR1             | R/W    | Address Match Detection 0 | XXXXXXXXB     |  |  |  |

| 79Е5н             | Detect Address Setting Register 1                          | PADR1             | R/W    | Detection                 | XXXXXXXX      |  |  |  |

| 79Е6н             | Detect Address Setting Register 2                          | PADR2             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79Е7н             | Detect Address Setting Register 2                          | PADR2             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79Е8н             | Detect Address Setting Register 2                          | PADR2             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79Е9н to<br>79ЕГн | Reserved                                                   |                   |        |                           |               |  |  |  |

| 79F0н             | Detect Address Setting Register 3                          | PADR3             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79F1н             | Detect Address Setting Register 3                          | PADR3             | R/W    |                           | XXXXXXXXB     |  |  |  |

| 79F2н             | Detect Address Setting Register 3                          | PADR3             | R/W    |                           | XXXXXXXX      |  |  |  |

| 79F3н             | Detect Address Setting Register 4                          | PADR4             | R/W    |                           | XXXXXXXXB     |  |  |  |

| 79F4 <sub>H</sub> | Detect Address Setting Register 4                          | PADR4             | R/W    | Address Match Detection 1 | XXXXXXXXB     |  |  |  |

| 79F5н             | Detect Address Setting Register 4                          | PADR4             | R/W    | Detection                 | XXXXXXXXB     |  |  |  |

| 79F6н             | Detect Address Setting Register 5                          | PADR5             | R/W    |                           | XXXXXXXXB     |  |  |  |

| 79F7н             | Detect Address Setting Register 5                          | PADR5             | R/W    |                           | XXXXXXXXB     |  |  |  |

| 79F8н             | Detect Address Setting Register 5                          | PADR5             | R/W    |                           | XXXXXXXXB     |  |  |  |

| 79F9н to<br>7BFFн | Reserved                                                   |                   |        |                           |               |  |  |  |

| 7C00н to<br>7CFFн | Reserved for CAN Interface 1. Refer to "■ CAN CONTROLLERS" |                   |        |                           |               |  |  |  |

| 7D00н to<br>7DFFн | Reserved for CAN Interface 1. Refer to "■ CAN CONTROLLERS" |                   |        |                           |               |  |  |  |

| 7E00н to<br>7FFFн |                                                            | Reserv            | ed     |                           |               |  |  |  |

|                   |                                                            |                   |        |                           |               |  |  |  |

Notes: • Initial value of "X" represents unknown value.

• Any write access to reserved addresses in I/O map should not be performed. A read access to reserved addresses results reading "X".

### **List of Message Buffers (ID Registers)**

| Address                  | - Register          | Abbreviation | Access    | Initial Value               |  |

|--------------------------|---------------------|--------------|-----------|-----------------------------|--|

| CAN1                     | Register            | Abbreviation | Access    | ilillai value               |  |

| 007С00н<br>to<br>007С1Fн | General-purpose RAM | _            | R/W       | XXXXXXXB<br>to<br>XXXXXXXXB |  |

| 007С20н                  |                     |              |           | XXXXXXXXB                   |  |

| 007С21н                  | ID as sisten 0      | IDDO         | DAA       | XXXXXXXXB                   |  |

| 007С22н                  | ID register 0       | IDR0         | R/W       | XXXXXXXXB                   |  |

| 007С23н                  |                     |              |           | XXXXXXXXB                   |  |

| 007С24н                  |                     |              |           | XXXXXXXXB                   |  |

| 007С25н                  | ID as sisten 4      | IDD4         | DAA       | XXXXXXXXB                   |  |

| 007С26н                  | ID register 1       | IDR1         | R/W       | XXXXXXXXB                   |  |

| 007С27н                  |                     |              |           | XXXXXXXXB                   |  |

| 007С28н                  |                     |              |           | XXXXXXXXB                   |  |

| 007С29н                  | ID register 2       | IDR2         | R/W       | XXXXXXXXB                   |  |

| 007С2Ан                  | ID register 2       |              |           | XXXXXXXXB                   |  |

| 007С2Вн                  |                     |              | XXXXXXXXB |                             |  |

| 007С2Сн                  |                     |              |           | XXXXXXXXB                   |  |

| 007С2Dн                  | ID register 3       | IDR3         | R/W       | XXXXXXXXB                   |  |

| 007С2Ен                  |                     | IDIO         | K/VV      | XXXXXXXXB                   |  |

| 007С2Гн                  |                     |              |           | XXXXXXXXB                   |  |

| 007С30н                  |                     |              |           | XXXXXXXX                    |  |

| 007С31н                  | ID register 4       | IDR4         | R/W       | XXXXXXX                     |  |

| 007С32н                  | Tib Tegister 4      | IDICT        | 10,00     | XXXXXXXX                    |  |

| 007С33н                  |                     |              |           | XXXXXXX                     |  |

| 007С34н                  |                     |              |           | XXXXXXXXB                   |  |

| 007С35н                  | ID register 5       | IDR5         | R/W       | XXXXXXX                     |  |

| 007С36н                  | Tib Tegister 3      | טולו         | 10,00     | XXXXXXXXB                   |  |

| 007С37н                  |                     |              |           | XXXXXXX                     |  |

| 007С38н                  |                     |              |           | XXXXXXXXB                   |  |

| 007С39н                  | ID register 6       | IDR6         | R/W       | XXXXXXXXB                   |  |

| 007С3Ан                  | ID TOGISTOR         | IDIO         | 1000      | XXXXXXXXB                   |  |

| 007С3Вн                  |                     |              |           | XXXXXXXXB                   |  |

| 007С3Сн                  |                     |              |           | XXXXXXXXB                   |  |

| 007С3Дн                  | ID register 7       | IDR7         | R/W       | XXXXXXXXB                   |  |

| 007С3Ен                  | ID Togistor 1       | IDI(I        | 10,44     | XXXXXXXXB                   |  |

| 007С3Гн                  |                     |              |           | XXXXXXX                     |  |

### (Continued)

| Interrupt cause   | El <sup>2</sup> OS<br>corre- | DMA ch<br>number | Interrup | ot vector           | Interrupt control register |         |

|-------------------|------------------------------|------------------|----------|---------------------|----------------------------|---------|

|                   | sponding                     | number           | Number   | Address             | Number                     | Address |

| UART 2 RX         | Y2                           | 14               | #39      | FFFF60⊦             | ICR14                      | 0000ВЕн |

| UART 2 TX         | Y1                           | 15               | #40      | FFFF5C <sub>H</sub> | ICK 14                     | UUUUDEH |

| Flash Memory      | N                            | _                | #41      | FFFF58 <sub>H</sub> | ICD45                      | 0000BFн |

| Delayed interrupt | N                            | _                | #42      | FFFF54 <sub>H</sub> | ICR15                      | ООООВЕН |

Y1: Usable

Y2: Usable, with EI2OS stop function

N : Unusable

Notes: • The peripheral resources sharing the ICR register have the same interrupt level.

• When two peripheral resources share the ICR register, only one can use El<sup>2</sup>OSat a time.

• When either of the two peripheral resources sharing the ICR register specifies El<sup>2</sup>OS, the other one cannot use interrupts.

```

(MB90F352(S)/MB90F351(S): T_A = -40 °C to +105 °C, V_{CC} = 5.0 V \pm 10%, f_{CP} \le 24 MHz, V_{SS} = AV_{SS} = 0 V) (MB90F352(S)/MB90F351(S): T_A = -40 °C to +125 °C, V_{CC} = 5.0 V \pm 10%, f_{CP} \le 24 MHz, V_{SS} = AV_{SS} = 0 V) (Device other than above: T_A = -40 °C to +125 °C, V_{CC} = 5.0 V \pm 10%, f_{CP} \le 24 MHz, V_{SS} = AV_{SS} = 0 V)

```

| Parameter                                           | Parameter Symbol Pin |      | Value |       |     | Unit   | Remarks                                                                             |

|-----------------------------------------------------|----------------------|------|-------|-------|-----|--------|-------------------------------------------------------------------------------------|

| Farameter                                           | Syllibol             | FIII | Min   | Тур   | Max | Offic  | Remarks                                                                             |

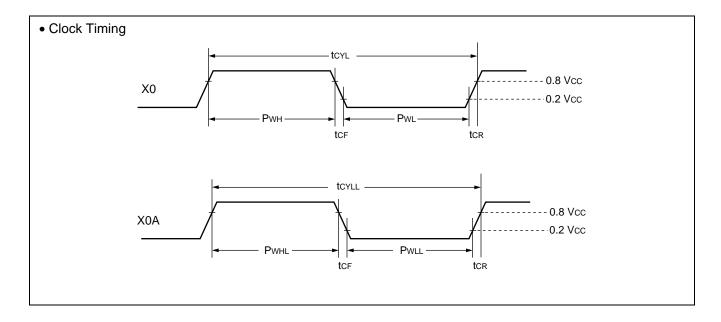

|                                                     |                      |      | 1.5   | 1.5 — | 24  | MHz    | MB90F352/(S), MB90F351/(S) When using main clock ( $T_A \le +105$ °C)               |

| Internal operating clock frequency (machine clock)  | fсР                  | _    |       |       | 16  | IVIIIZ | MB90F352/(S), MB90F351/(S) When using main clock $(T_A \le +125  ^{\circ}\text{C})$ |

|                                                     |                      |      | 1.5   |       | 24  | MHz    | Device other than above,<br>When using main clock                                   |

|                                                     | <b>f</b> CPL         |      | _     | 8.192 | 50  | kHz    | When using sub clock                                                                |

|                                                     | tcp                  |      | 41.67 | 7     | 666 | ns     | MB90F352/(S), MB90F351/(S) When using main clock $(T_A \le +105  ^{\circ}\text{C})$ |

| Internal operating clock cycle time (machine clock) |                      | _    | 62.5  | _     | 000 |        | MB90F352/(S), MB90F351/(S) When using main clock $(T_A \le +125  ^{\circ}\text{C})$ |

|                                                     |                      |      | 41.67 | _     | 666 | ns     | Device other than above,<br>When using main clock                                   |

|                                                     | <b>t</b> CPL         | _    | 20    | 122.1 | _   | μs     | When using sub clock                                                                |

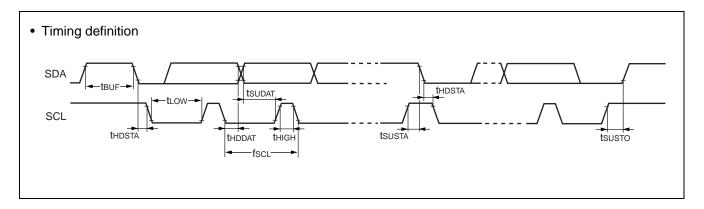

Note: The rating of the input data set-up time in the device connected to the bus cannot be satisfied depending on the load capacitance or pull-up resistor.

Be sure to adjust the pull-up resistor of SDA and SCL if the rating of the input data set-up time cannot be satisfied.

#### 5. A/D Converter

$(MB90F352(S)/MB90F351(S): T_A = -40 \, ^{\circ}C \, to \, +105 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{SS} = AV_{SS} = 0 \, V) \\ (MB90F352(S)/MB90F351(S): T_A = -40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 16 \, MHz, \, V_{SS} = AV_{SS} = 0 \, V) \\ (Device other than above: T_A = -40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{SS} = AV_{SS} = 0 \, V) \\ (Device other than above: T_A = -40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{SS} = AV_{SS} = 0 \, V) \\ (Device other than above: T_A = -40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{SS} = AV_{SS} = 0 \, V) \\ (Device other than above: T_A = -40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{SS} = AV_{SS} = 0 \, V) \\ (Device other than above: T_A = -40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{SS} = AV_{SS} = 0 \, V) \\ (Device other than above: T_A = -40 \, ^{\circ}C \, to \, +125 \, ^{\circ}C, \, 3.0 \, V \leq AVRH, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = 5.0 \, V \pm \, 10\%, \, f_{CP} \leq 24 \, MHz, \, V_{CC} = AV_{CC} = AV_{CC$

| Parameter                              | Symbol           | Pin         | Value      |            |            | Unit | Remarks              |

|----------------------------------------|------------------|-------------|------------|------------|------------|------|----------------------|

|                                        |                  |             | Min        | Тур        | Max        | Unit | Remarks              |

| Resolution                             | _                | _           | _          | _          | 10         | bit  |                      |

| Total error                            | _                | _           | _          | _          | ±3.0       | LSB  |                      |

| Nonlinearity error                     | _                | _           | _          | _          | ±2.5       | LSB  |                      |

| Differential nonlinearity error        |                  | _           | _          | _          | ±1.9       | LSB  |                      |

| Zero reading voltage                   | Vот              | AN0 to AN14 | AVss - 1.5 | AVss + 0.5 | AVss + 2.5 | LSB  |                      |

| Full scale reading voltage             | V <sub>FST</sub> | AN0 to AN14 | AVRH – 3.5 | AVRH – 1.5 | AVRH + 0.5 | LSB  |                      |

| Compare time                           | _                | _           | 1.0        |            | 16,500     | μs   | 4.5 V ≤ AVcc ≤ 5.5 V |

|                                        |                  |             | 2.0        |            |            |      | 4.0 V ≤ AVcc < 4.5 V |

| Sampling time                          | _                | _           | 0.5        |            | ∞          | μs   | 4.5 V ≤ AVcc ≤ 5.5 V |

|                                        |                  |             | 1.2        | _          | ω          |      | 4.0 V ≤ AVcc < 4.5 V |

| Analog port input current              | lain             | AN0 to AN14 | -0.3       | _          | +0.3       | μΑ   |                      |

| Analog input voltage range             | Vain             | AN0 to AN14 | AVss       | _          | AVRH       | V    |                      |

| Reference voltage range                |                  | AVRH        | AVss + 2.7 | _          | AVcc       | V    |                      |

| Power supply current                   | lΑ               | AVcc        | _          | 3.5        | 7.5        | mA   |                      |

|                                        | Іан              | AVcc        | _          | _          | 5          | μΑ   | *                    |

| Reference<br>voltage supply<br>current | lR               | AVRH        | _          | 600        | 900        | μΑ   |                      |

|                                        | lпн              | AVRH        | _          | _          | 5          | μΑ   | *                    |

| Offset between input channels          | _                | AN0 to AN14 | —          | _          | 4          | LSB  |                      |

<sup>\*:</sup> If A/D converter is not operating, a current when CPU is stopped is applicable (Vcc = AVcc = AVRH = 5.0 V).

#### **■ PACKAGE DIMENSIONS**