Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

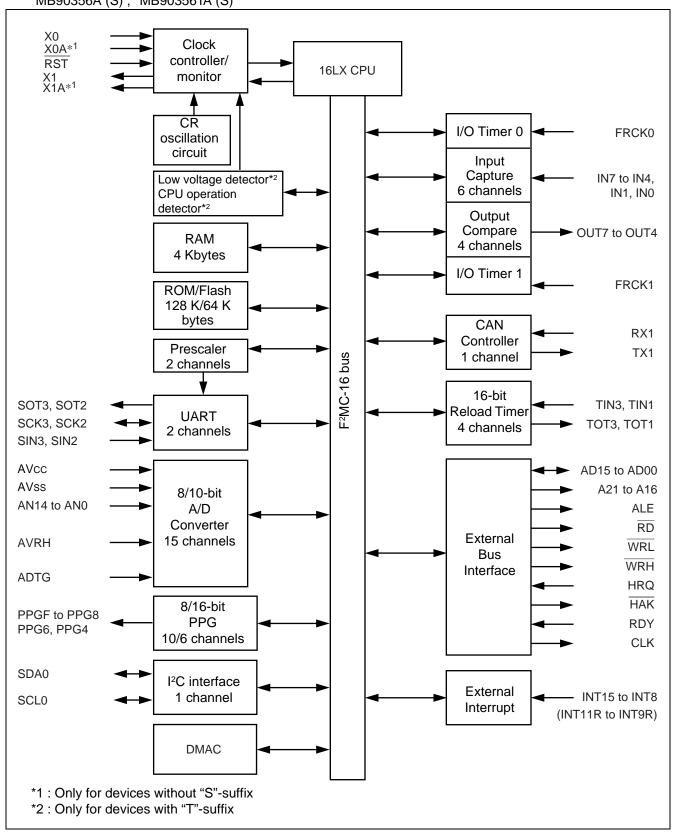

| Core Processor             | F <sup>2</sup> MC-16LX                                                        |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 24MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                         |

| Peripherals                | DMA, LVD, POR, WDT                                                            |

| Number of I/O              | 49                                                                            |

| Program Memory Size        | 128KB (128K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 15x8/10b                                                                  |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-LQFP                                                                       |

| Supplier Device Package    | 64-QFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f352pfm-g-jne1 |

#### **■ FEATURES**

#### Clock

- Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 6 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 24 MHz).

- Operation by sub clock (up to 50 kHz: 100 kHz oscillation clock divided by two) is allowed. (devices without S-suffix only)

- Minimum execution time of instruction: 42 ns (when operating with 4-MHz oscillation clock, and 6-time multiplied PLL clock).

- · Built-in clock modulation circuit

### • 16 Mbytes CPU memory space

24-bit internal addressing

### • Clock monitor function (MB90x356x and MB90x357x only)

- Main clock or sub clock is monitored independently.

- Internal CR oscillation clock (100 kHz typical) can be used as sub clock.

### • Instruction system best suited to controller

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions with sign and RETI instructions

- Enhanced high-precision computing with 32-bit accumulator

### • Instruction system compatible with high-level language (C language) and multitask

- Employing system stack pointer

- · Enhanced various pointer indirect instructions

- · Barrel shift instructions

### Increased processing speed

• 4-byte instruction queue

#### • Powerful interrupt function

- Powerful 8-level, 34-condition interrupt feature

- Up to 8 channels external interrupts are supported.

### Automatic data transfer function independent of CPU

- Extended intelligent I/O service function (El<sup>2</sup>OS): up to 16 channels

- DMA: up to 16 channels

#### • Low power consumption (standby) mode

- Sleep mode (a mode that halts CPU operating clock)

- Main timer mode (a timebase timer mode switched from the main clock mode)

- PLL timer mode (a timebase timer mode switched from the PLL clock mode)

- Watch mode (a mode that operates sub clock and watch timer only)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU intermittent operation mode

#### Process

CMOS technology

| Part Number                     | MB90F356A,                                                                                                                                                                                                                                                                                                                                                                                                                      | MB90F356TA,                                                                                | MB90F356AS,                                                     | MB90F356TAS,            |  |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------|--|--|--|--|

| Parameter                       | MB90F357A                                                                                                                                                                                                                                                                                                                                                                                                                       | MB90F357TA                                                                                 | MB90F357AS                                                      | MB90F357TAS             |  |  |  |  |

|                                 | 6 channels                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                            |                                                                 |                         |  |  |  |  |

| 16-bit Input Capture            | Retains freerun timer vinterrupt.                                                                                                                                                                                                                                                                                                                                                                                               | alue by (rising edge, fa                                                                   | ılling edge or rising & fa                                      | lling edge), signals an |  |  |  |  |

| 8/16-bit                        |                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6 channels (16-bit)<br>8-bit reload of<br>8-bit reload registers<br>8-bit reload registers | counters × 12                                                   |                         |  |  |  |  |

| Programmable Pulse<br>Generator | 8-bit prescaler + 8-bit<br>Operation clock frequency                                                                                                                                                                                                                                                                                                                                                                            | counters can be configureload counter.                                                     | s/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> or | 128 μs@fosc = 4 MHz     |  |  |  |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 cha                                                                                      | annel                                                           | <u>,</u>                |  |  |  |  |

| CAN Interface                   | Conforms to CAN Specification Version 2.0 Part A and B. Automatic re-transmission in case of error Automatic transmission responding to Remote Frame Prioritized 16 message buffers for data and ID Supports multiple messages. Flexible configuration of acceptance filtering: Full bit compare/Full bit mask/Two partial bit masks Supports up to 1 Mbps.                                                                     |                                                                                            |                                                                 |                         |  |  |  |  |

|                                 | 8 channels                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                            |                                                                 |                         |  |  |  |  |

| External Interrupt              |                                                                                                                                                                                                                                                                                                                                                                                                                                 | ge, falling edge, startin<br>O services (El²OS) and                                        |                                                                 | , external interrupt,   |  |  |  |  |

| D/A converter                   |                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                          | _                                                               |                         |  |  |  |  |

| I/O Ports                       | Virtually all external pins can be used as general purpose I/O port. All push-pull outputs Bit-wise settable as input/output or peripheral module signal Settable as CMOS schmitt trigger/ automotive inputs TTL input level settable for external bus (only for external bus pin)                                                                                                                                              |                                                                                            |                                                                 |                         |  |  |  |  |

| Flash Memory                    | Supports automatic programming, Embedded Algorithm <sup>TM*2</sup> Write/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Number of erase cycles: 10,000 times Data retention time: 10 years Boot block configuration Erase can be performed on each block. Block protection with external programming voltage Flash Security Feature for protecting the content of the Flash (MB90F357x only) |                                                                                            |                                                                 |                         |  |  |  |  |

| Corresponding EVA name          | MB90V3                                                                                                                                                                                                                                                                                                                                                                                                                          | MB90V340A-104 MB90V340A-103                                                                |                                                                 |                         |  |  |  |  |

<sup>\*1:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

<sup>\*2:</sup> Embedded Algorithm is a trademark of Advanced Micro Devices Inc.

| Pin No. |             | Circuit |                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |  |  |  |

|---------|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| LQFP64* | Pin name    | type    | Function                                                                                                                                                                                                                                                                                                                             |                                                                                                                |  |  |  |

|         | P30         |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                                                                                         |                                                                                                                |  |  |  |

| 54      | 54 ALE      |         | Address latch enable output pin. This function is enabled when external bus s enabled.                                                                                                                                                                                                                                               |                                                                                                                |  |  |  |

|         | IN4         |         | Data sample input pin for input capture ICU4                                                                                                                                                                                                                                                                                         |                                                                                                                |  |  |  |

|         | P31         |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                                                                                         |                                                                                                                |  |  |  |

| 55      | RD          | G       | Read strobe output pin for data bus. This function is enabled when external bus is enabled.                                                                                                                                                                                                                                          |                                                                                                                |  |  |  |

|         | IN5         |         | Data sample input pin for input capture ICU5                                                                                                                                                                                                                                                                                         |                                                                                                                |  |  |  |

|         | P32         |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the WR/WRL pin output disabled.                                                                                                                                           |                                                                                                                |  |  |  |

| 56      | 56 WR/WRL G |         | Write strobe output pin for the data bus. This function is enabled when both the external bus and the $\overline{WR}/\overline{WRL}$ pin output are enabled. $\overline{WRL}$ is used to write-strobe 8 lower bits of the data bus in 16-bit access. $\overline{WR}$ is used to write-strobe 8 bits of the data bus in 8-bit access. |                                                                                                                |  |  |  |

|         | INT10R      |         | External interrupt request input pin for INT10                                                                                                                                                                                                                                                                                       |                                                                                                                |  |  |  |

| 57      | P33         |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode, in external bus 8-bit mode or with the WRH pin output disabled.                                                                                                                  |                                                                                                                |  |  |  |

| 31      | WRH         | - G     | Write strobe output pin for the 8 higher bits of the data bus. This function is enabled when the external bus is enabled, when the external bus 16-bit mode is selected, and when the WRH output pin is enabled.                                                                                                                     |                                                                                                                |  |  |  |

|         | P34         |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the hold function disabled.                                                                                                                                               |                                                                                                                |  |  |  |

| 58      | 58 HRQ      | HRQ     | - G                                                                                                                                                                                                                                                                                                                                  | Hold request input pin. This function is enabled when both the external bus and the hold function are enabled. |  |  |  |

|         | OUT4        |         | Waveform output pin for output compare OCU4                                                                                                                                                                                                                                                                                          |                                                                                                                |  |  |  |

| 50      | P35         |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the hold function disabled.                                                                                                                                               |                                                                                                                |  |  |  |

| 59      | HAK         | G       | Hold acknowledge output pin. This function is enabled when both the external bus and the hold function are enabled.                                                                                                                                                                                                                  |                                                                                                                |  |  |  |

|         | OUT5        |         | Waveform output pin for output compare OCU5                                                                                                                                                                                                                                                                                          |                                                                                                                |  |  |  |

| 60      | P36         |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the external ready function disabled.                                                                                                                                     |                                                                                                                |  |  |  |

| 60      | RDY         | G       | Ready input pin. This function is enabled when both the external bus an the external ready function are enabled.                                                                                                                                                                                                                     |                                                                                                                |  |  |  |

|         | OUT6        |         | Waveform output pin for output compare OCU6                                                                                                                                                                                                                                                                                          |                                                                                                                |  |  |  |

| Pin No. | Pin name | Circuit | Function                                                                                                                                                                            |  |

|---------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP64* |          | type    |                                                                                                                                                                                     |  |

| 64      | P37      |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the CLK output disabled. |  |

| 61      | CLK      | G       | CLK output pin. This function is enabled when both the external bus and CLK output are enabled.                                                                                     |  |

|         | OUT7     |         | Waveform output pin for output compare OCU7                                                                                                                                         |  |

| 62, 63  | P60, P61 | ı       | General purpose I/O ports                                                                                                                                                           |  |

| 02, 03  | ANO, AN1 |         | Analog input pins for A/D converter                                                                                                                                                 |  |

| 64      | AVcc     | K       | Vcc power input pin for analog circuits                                                                                                                                             |  |

| 2       | AVRH     | L       | Reference voltage input for the A/D converter. This power supply must be turned on or off while a voltage higher than or equal to AVRH is applied to AVcc.                          |  |

| 1       | AVss     | K       | Vss power input pin for analog circuits                                                                                                                                             |  |

| 22, 23  | MD1, MD0 | С       | Input pins for specifying the operating mode                                                                                                                                        |  |

| 21      | MD2      | D       | Input pin for specifying the operating mode                                                                                                                                         |  |

| 49      | Vcc      |         | Power (3.5 V to 5.5 V) input pin                                                                                                                                                    |  |

| 18, 48  | Vss      |         | Power (0 V) input pins                                                                                                                                                              |  |

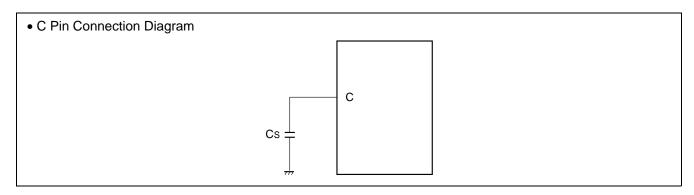

| 50      | С        | K       | This is the power supply stabilization capacitor pin. It should be connected to a higher than or equal to 0.1 $\mu\text{F}$ ceramic capacitor.                                      |  |

<sup>\*:</sup> FPT-64P-M09, FPT-64P-M23, FPT-64P-M24

### 16. Flash security Function

The security byte is located in the area of the flash memory.

If protection code 01H is written in the security byte, the flash memory is in the protected state by security.

Therefore please do not write 01H in this address if you do not use the security function.

Please refer to following table for the address of the security byte.

|                                                               | Flash memory size            | Address for security bit |

|---------------------------------------------------------------|------------------------------|--------------------------|

| MB90F352(S)<br>MB90F352A(S)<br>MB90F352TA(S)<br>MB90F357TA(S) | Embedded 1 Mbit Flash Memory | FE0001н                  |

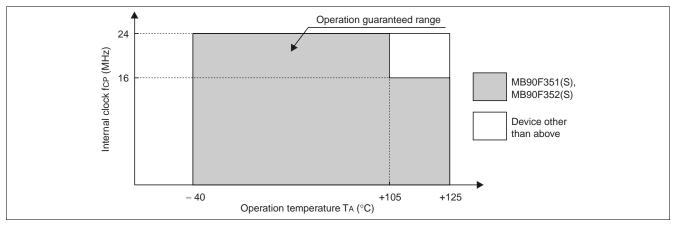

### 17. Correspondence with $T_A = +105$ °C or more

If used exceeding T<sub>A</sub> = +105 °C, please contact Fujitsu sales representatives for reliability limitations.

### 18. Low voltage/CPU operation reset circuit

The low voltage detection reset circuit is a function that monitors power supply voltage in order to detect when a voltage drops below a given voltage level. When a low voltage condition is detected, an internal reset signal is generated.

The CPU operation detection reset circuit is a 20-bit counter that uses oscillation as a count clock and generates an internal reset signal if not cleared within a given time after startup.

### (1) Low voltage detection reset circuit

| Detection voltage |

|-------------------|

| 4.0 V ± 0.3 V     |

When a low voltage condition is detected, the low voltage detection flag (LVRC : LVRF) is set to "1" and an internal reset signal is output.

Because the low voltage detection reset circuit continues to operate even in stop mode, detection of a low voltage condition generates an internal reset and releases stop mode.

During an internal RAM write cycle, low voltage reset is generated after the completion of writing. During the output of this internal reset, the reset output from the low voltage detection reset circuit is suppressed.

#### (2) CPU operation detection reset circuit

The CPU operation detection reset circuit is a counter that prevents program runaway. The counter starts automatically after a power-on reset, and must be continually cleared within a given time. If the given time interval elapses and the counter has not been cleared, a cause such as infinite program looping is assumed and an internal reset signal is generated. The internal reset generated from the CPU operation detection circuit has a width of 5 machine cycles.

| Interval time                         |

|---------------------------------------|

| 2 <sup>20</sup> /Fc (approx. 262 ms*) |

$<sup>^*</sup>$ : This value assumes the interval time at an oscillation clock frequency of 4 MHz. During recovery from standby mode, the detection period is the maximum interval plus 20  $\mu$ s.

MB90F357A (S), MB90F357TA (S), MB90F356A (S), MB90F356TA (S), MB90357A (S), MB90357TA (S),

MB90356A (S), MB90356TA (S)

| Address      | Register                                                      | Abbrevia-<br>tion                        | Access    | Resource name                                   | Initial value         |  |

|--------------|---------------------------------------------------------------|------------------------------------------|-----------|-------------------------------------------------|-----------------------|--|

| 5Ен          | Output Compare Control Status<br>Register 6                   | OCS6                                     | R/W       | Output Compare 6/7                              | 0000ХХ00в             |  |

| 5Fн          | Output Compare Control Status<br>Register 7                   | OCS7                                     | R/W       | Output Compare 6/7                              | 0ХХ00000в             |  |

| 60н          | Timer Control Status Register 0                               | TMCSR0                                   | R/W       | 4C hit Dolood Timer 0                           | 0000000В              |  |

| 61н          | Timer Control Status Register 0                               | TMCSR0                                   | R/W       | 16-bit Reload Timer 0                           | XXXX0000B             |  |

| 62н          | Timer Control Status Register 1                               | TMCSR1                                   | R/W       | 40 hit Daland Times 4                           | 00000000в             |  |

| 63н          | Timer Control Status Register 1                               | TMCSR1                                   | R/W       | 16-bit Reload Timer 1                           | XXXX0000B             |  |

| 64н          | Timer Control Status Register 2                               | TMCSR2                                   | R/W       | 40 L'C Dalam I T'                               | 0000000В              |  |

| 65н          | Timer Control Status Register 2                               | TMCSR2                                   | R/W       | 16-bit Reload Timer 2                           | ХХХХ0000в             |  |

| 66н          | Timer Control Status Register 3                               | TMCSR3                                   | R/W       | 401115115                                       | 0000000В              |  |

| 67н          | Timer Control Status Register 3                               | TMCSR3                                   | R/W       | 16-bit Reload Timer 3                           | XXXX0000 <sub>B</sub> |  |

| 68н          | A/D Control Status Register 0                                 | ADCS0                                    | R/W       |                                                 | 000XXXX0в             |  |

| 69н          | A/D Control Status Register 1                                 | ADCS1                                    | R/W       |                                                 | 000000XB              |  |

| 6Ан          | A/D Data Register 0                                           | ADCR0                                    | R         | 1/20                                            | 0000000               |  |

| 6Вн          | A/D Data Register 1                                           | ADCR1                                    | R         | A/D Converter                                   | XXXXXX00 <sub>B</sub> |  |

| 6Сн          | ADC Setting Register 0                                        | ADSR0                                    | R/W       |                                                 | 0000000               |  |

| 6Dн          | ADC Setting Register 1                                        | ADSR1                                    | R/W       |                                                 | 00000000в             |  |

| 6Ен          | Low Voltage/CPU Operation Detection<br>Reset Control Register | LVRC                                     | R/W, W    | Low Voltage/CPU<br>Operation Detection<br>Reset | 00111000в             |  |

| 6Fн          | ROM Mirror Function Select Register                           | ROMM                                     | W         | ROM Mirror                                      | XXXXXXX1 <sub>B</sub> |  |

| 70н to 7Fн   | Reserved                                                      |                                          |           |                                                 |                       |  |

| 80н to 8Fн   | Reserved for CAN Interface 1. Refer to                        | "■ CAN CO                                | NTROLLE   | ERS"                                            |                       |  |

| 90н to 9Ан   |                                                               | Reserv                                   | ed        |                                                 |                       |  |

| 9Вн          | DMA Descriptor Channel Specification<br>Register              | DCSR                                     | R/W       |                                                 | 00000000в             |  |

| 9Сн          | DMA Status Register L                                         | DSRL                                     | R/W       | DMA                                             | 0000000В              |  |

| 9Dн          | DMA Status Register H                                         | DSRH                                     | R/W       |                                                 | 0000000В              |  |

| 9Ен          | Address Detect Control Register 0                             | PACSR0                                   | R/W       | Address Match<br>Detection 0                    | 00000000в             |  |

| 9 <b>F</b> н | Delayed Interrupt/Release Register                            |                                          |           | XXXXXXX0 <sub>B</sub>                           |                       |  |

| А0н          | Low-power Consumption Mode<br>Control Register                | LPMCR                                    | W,R/W     | Low Power Consumption<br>Control Circuit        | 00011000в             |  |

| А1н          | Clock Selection Register                                      | Low Power Consumption<br>Control Circuit | 11111100в |                                                 |                       |  |

| А2н, А3н     | Reserved                                                      |                                          |           |                                                 |                       |  |

| Address           | Register                             | Abbrevia-<br>tion | Access | Resource name      | Initial value |

|-------------------|--------------------------------------|-------------------|--------|--------------------|---------------|

| 792Сн             | Input Capture Register 6             | IPCP6             | R      |                    | XXXXXXXXB     |

| 792Dн             | Input Capture Register 6             | IPCP6             | R      | Input Conturo 6/7  | XXXXXXXXB     |

| 792Ен             | Input Capture Register 7             | IPCP7             | R      | Input Capture 6/7  | XXXXXXXXB     |

| 792Fн             | Input Capture Register 7             | IPCP7             | R      |                    | XXXXXXXXB     |

| 7930н to<br>7937н |                                      | Reserve           | ed     |                    |               |

| 7938н             | Output Compare Register 4            | OCCP4             | R/W    |                    | XXXXXXX       |

| 7939н             | Output Compare Register 4            | OCCP4             | R/W    | Output Compare 4/E | XXXXXXX       |

| 793Ан             | Output Compare Register 5            | OCCP5             | R/W    | Output Compare 4/5 | XXXXXXXXB     |

| 793Вн             | Output Compare Register 5            | OCCP5             | R/W    |                    | XXXXXXXXB     |

| 793Сн             | Output Compare Register 6            | OCCP6             | R/W    |                    | XXXXXXXXB     |

| 793Dн             | Output Compare Register 6            | OCCP6             | R/W    | Output Compare 6/7 | XXXXXXXXB     |

| 793Ен             | Output Compare Register 7            | OCCP7             | R/W    | Output Compare 6/7 | XXXXXXXX      |

| 793Гн             | Output Compare Register 7            | OCCP7             | R/W    |                    | XXXXXXXX      |

| 7940н             | Timer Data Register 0                | TCDT0             | R/W    |                    | 00000000в     |

| 7941н             | Timer Data Register 0                | TCDT0             | R/W    | I/O Time or O      | 0000000в      |

| 7942н             | Timer Control Status Register 0      | TCCSL0            | R/W    | I/O Timer 0        | 0000000в      |

| 7943н             | Timer Control Status Register 0      | TCCSH0            | R/W    |                    | 0XXXXXXXB     |

| 7944н             | Timer Data Register 1                | TCDT1             | R/W    |                    | 00000000в     |

| 7945н             | Timer Data Register 1                | TCDT1             | R/W    | I/O Time on 4      | 0000000в      |

| 7946н             | Timer Control Status Register 1      | TCCSL1            | R/W    | I/O Timer 1        | 0000000в      |

| 7947н             | Timer Control Status Register 1      | TCCSH1            | R/W    |                    | 0XXXXXXXB     |

| 7948н             | Times Decister O/Deleged Decister O  | TMR0/             | R/W    | 16-bit Reload      | XXXXXXXXB     |

| 7949н             | Timer Register 0/Reload Register 0   | TMRLR0            | R/W    | Timer 0            | XXXXXXXX      |

| 794Ан             | Times Decister 4/Deleged Decister 4  | TMR1/             | R/W    | 16-bit Reload      | XXXXXXXXB     |

| 794Вн             | - Timer Register 1/Reload Register 1 | TMRLR1            | R/W    | Timer 1            | XXXXXXXX      |

| 794Сн             | Timer Degister 2/Delegel Degister 2  | TMR2/             | R/W    | 16-bit Reload      | XXXXXXXX      |

| 794Dн             | - Timer Register 2/Reload Register 2 | TMRLR2            | R/W    | Timer 2            | XXXXXXXX      |

| 794Ен             | Timer Degister 2/Delegal Degister 2  | TMR3/             | R/W    | 16-bit Reload      | XXXXXXXX      |

| 794Fн             | Timer Register 3/Reload Register 3   | TMRLR3            | R/W    | Timer 3            | XXXXXXXXB     |

| Address           | Register                                             | Abbrevia-<br>tion | Access                | Resource name                | Initial value |  |  |

|-------------------|------------------------------------------------------|-------------------|-----------------------|------------------------------|---------------|--|--|

| 7950н             | Serial Mode Register 3                               | SMR3              | W, R/W                |                              | 0000000В      |  |  |

| 7951н             | Serial Control Register 3                            | SCR3              | W, R/W                |                              | 0000000В      |  |  |

| 7952н             | Reception/Transmission Data<br>Register 3            | RDR3/<br>TDR3     | R/W                   |                              | 0000000В      |  |  |

| 7953н             | Serial Status Register 3                             | SSR3              | R,R/W                 | UART3                        | 00001000в     |  |  |

| 7954н             | Extended Communication Control Register 3            | ECCR3             | R,W,<br>R/W           | UARTS                        | 000000XXB     |  |  |

| 7955н             | Extended Status/Control Register 3                   | ESCR3             | R/W                   |                              | 00000100в     |  |  |

| 7956н             | Baud Rate Generator Register 30                      | BGR30             | R/W                   |                              | 0000000в      |  |  |

| 7957н             | Baud Rate Generator Register 31                      | BGR31             | R/W                   |                              | 0000000в      |  |  |

| 7958н,<br>7959н   |                                                      | Reserve           | ed                    |                              |               |  |  |

| 7960н             | Clock Monitor Function Control<br>Register           | CSVCR             | R, R/W                | Clock Monitor                | 00011100в     |  |  |

| 7961н to<br>796Dн | Reserved                                             |                   |                       |                              |               |  |  |

| 796Ен             | CAN Direct Mode Register                             | CAN Clock Sync    | XXXXXXX0 <sub>B</sub> |                              |               |  |  |

| <b>796</b> Fн     |                                                      | Reserve           | ed                    |                              |               |  |  |

| 7970н             | I <sup>2</sup> C Bus Status Register 0               | IBSR0             | R                     |                              | 0000000В      |  |  |

| 7971н             | I <sup>2</sup> C Bus Control Register 0              | IBCR0             | W,R/W                 |                              | 0000000В      |  |  |

| 7972н             | I <sup>2</sup> C 10-bit Slave Address Register 0     | ITBAL0            | R/W                   | I <sup>2</sup> C Interface 0 | 0000000В      |  |  |

| 7973н             | 1-C 10-bit Slave Address Register 0                  | ITBAH0            | R/W                   |                              | 0000000В      |  |  |

| 7974н             | I <sup>2</sup> C 10-bit Slave Address Mask Register  | ITMKL0            | R/W                   |                              | 11111111в     |  |  |

| 7975н             | 0                                                    | ITMKH0            | R/W                   |                              | 00111111в     |  |  |

| 7976н             | I <sup>2</sup> C 7-bit Slave Address Register 0      | ISBA0             | R/W                   |                              | 0000000в      |  |  |

| 7977н             | I <sup>2</sup> C 7-bit Slave Address Mask Register 0 | ISMK0             | R/W                   |                              | 01111111в     |  |  |

| 7978н             | I <sup>2</sup> C data register 0                     | IDAR0             | R/W                   |                              | 0000000в      |  |  |

| 7979н,<br>797Ан   | Reserved                                             |                   |                       |                              |               |  |  |

| 797Вн             | I <sup>2</sup> C Clock Control Register 0            | ICCR0             | R/W                   | I <sup>2</sup> C Interface 0 | 00011111в     |  |  |

| 797Сн to<br>79А1н |                                                      | Reserve           | ed                    |                              | •             |  |  |

| 79А2н             | Flash Write Control Register 0                       | FWR0              | R/W                   |                              | 0000000в      |  |  |

| 79А3н             | Flash Write Control Register 1                       | FWR1              | R/W                   | Dual Operation<br>Flash      | 0000000В      |  |  |

| 79А4н             | Sector Change Setting Register                       | SSR0              | R/W                   | 1 10311                      | 00XXXXX0в     |  |  |

| 79А5н to<br>79С1н | Reserved                                             |                   |                       |                              |               |  |  |

### **■ CAN CONTROLLERS**

The CAN controller has the following features:

- Conforms to CAN Specification Version 2.0 Part A and B

- Supports transmission/reception in standard frame and extended frame formats

- Supports transmitting of data frames by receiving remote frames

- 16 transmitting/receiving message buffers

- 29-bit ID and 8-byte data

- Multi-level message buffer configuration

- Provides full-bit comparison, full-bit mask, acceptance register 0/acceptance register 1 for each message buffer as ID acceptance mask

- Two acceptance mask registers in either standard frame format or extended frame formats

- Bit rate programmable from 10 Kbps to 2 Mbps (when input clock is at 16 MHz)

### **List of Control Registers**

| Address | Register                           | Abbreviation | Access   | Initial Value  |  |

|---------|------------------------------------|--------------|----------|----------------|--|

| CAN1    | Register                           | Appreviation | Access   | illitiai value |  |

| 000080н | Message buffer enable register     | BVALR        | R/W      | 0000000В       |  |

| 000081н | Wessage builer enable register     | DVALIC       | 10,44    | 0000000В       |  |

| 000082н | Transmit request register          | TREQR        | R/W      | 0000000В       |  |

| 000083н | Transmit request register          | INEQN        | IN/VV    | 0000000В       |  |

| 000084н | Transmit cancel register           | TCANR        | W        | 0000000В       |  |

| 000085н | Transmit cancer register           | TOANK        | VV       | 0000000В       |  |

| 000086н | Transmission complete register     | TCR          | R/W      | 0000000В       |  |

| 000087н | Transmission complete register     | TOIX         | 10,44    | 0000000в       |  |

| 000088н | Receive complete register          | RCR          | R/W      | 0000000В       |  |

| 000089н | Treceive complete register         | KOK          | 10,44    | 0000000В       |  |

| 00008Ан | Remote request receiving register  | RRTRR        | R/W      | 0000000В       |  |

| 00008Вн | Tremote request receiving register | KKIIKK       | 10,44    | 0000000В       |  |

| 00008Сн | Receive overrun register           | ROVRR        | R/W      | 0000000В       |  |

| 00008Dн | receive overrail register          | NOVIN        | 17/ / /  | 0000000В       |  |

| 00008Ен | Reception interrupt                | RIER         | R/W      | 0000000В       |  |

| 00008Fн | enable register                    | NILIX        | 1 (/ V V | 0000000В       |  |

### 2. Recommended Operating Conditions

(Vss = AVss = 0 V)

| Parameter             | Symbol       | Value |     | Unit | Remarks |                                                                                                                                           |

|-----------------------|--------------|-------|-----|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| i arameter            | Symbol       | Min   | Тур | Max  | Oilit   | Remarks                                                                                                                                   |

|                       |              | 4.0   | 5.0 | 5.5  | V       | Under normal operation                                                                                                                    |

| Power supply voltage  | Vcc,<br>AVcc | 3.5   | 5.0 | 5.5  | V       | Under normal operation, when not using the A/D converter and not Flash programming.                                                       |

|                       |              | 4.5   | 5.0 | 5.5  | V       | When External bus is used.                                                                                                                |

|                       |              | 3.0   | _   | 5.5  | V       | Maintains RAM data in stop mode                                                                                                           |

| Smooth capacitor      | Cs           | 0.1   | _   | 1.0  | μF      | Use a ceramic capacitor or capacitor of better AC characteristics. Bypass capacitor at the Vcc pin should be greater than this capacitor. |

|                       |              | -40   | _   | +105 | °C      | MB90F352(S) fcp ≤ 24MHz                                                                                                                   |

| Operating temperature | ТА           | -40   | _   | +125 | °C      | *, MB90F352(S) fcp ≤ 16MHz,<br>Devices with A-suffix                                                                                      |

<sup>\*:</sup> If used exceeding  $T_A = +105$  °C, be sure to contact Fujitsu for reliability limitations.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

```

\label{eq:mb90F352(S)/MB90F351(S): TA = -40 °C to +105 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) \\ \mbox{(MB90F352(S)/MB90F351(S): TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 16 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vss = AVss = 0 V) } \\ \mbox{(Device other than above: TA = -40 °C to +125 °C, Vcc = 5.0 V \pm 10\%, fcp \le 24 MHz, Vcc = 10\%, fcp \le 24 MHz, Vcc = 10\%, fcp \le 24 MHz, Vcc = 10\%, fcp \le

```

| Donomoton            | Sym-      | Pin                                                                                                                                 | Condition                                                                                                                           |     | Value |     | Unit                                                                                                                     | Domestre                                                                                                 |

|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Parameter            | bol       | Pin                                                                                                                                 | Condition                                                                                                                           | Min | Тур   | Max | Unit                                                                                                                     | Remarks                                                                                                  |

| Power supply current | Iccls Vcc |                                                                                                                                     | Vcc = 5.0 V,<br>Internal frequency: 8 kHz,<br>During operating clock<br>monitor function,<br>At sub sleep<br>T <sub>A</sub> = +25°C | _   | 60    | 200 | μА                                                                                                                       | MB90F356A<br>MB90F357A<br>MB90356A<br>MB90357A                                                           |

|                      |           | Vcc                                                                                                                                 | Vcc = 5.0 V,<br>Internal CR oscillation/<br>4 division,<br>At sub sleep<br>T <sub>A</sub> = +25°C                                   |     | 60    | 200 | μΑ                                                                                                                       | MB90F356AS<br>MB90F357AS<br>MB90356AS<br>MB90357AS                                                       |

|                      |           |                                                                                                                                     | Vcc = 5.0 V,<br>Internal frequency: 8 kHz,<br>During stopping clock<br>monitor function,<br>At sub sleep<br>T <sub>A</sub> = +25°C  | _   | 70    | 150 | μА                                                                                                                       | MB90F351TA<br>MB90F352TA<br>MB90F356TA<br>MB90F357TA<br>MB90351TA<br>MB90352TA<br>MB90356TA<br>MB90357TA |

|                      |           |                                                                                                                                     | Vcc = 5.0 V,<br>Internal frequency: 8 kHz,<br>During operating clock<br>monitor function,<br>At sub sleep<br>T <sub>A</sub> = +25°C | _   | 110   | 300 | μА                                                                                                                       | MB90F356TA<br>MB90F357TA<br>MB90356TA<br>MB90357TA                                                       |

|                      |           |                                                                                                                                     | Vcc = 5.0 V,<br>Internal CR oscillation/<br>4 division,<br>At sub sleep<br>T <sub>A</sub> = +25°C                                   | _   | 110   | 300 | μА                                                                                                                       | MB90F356TAS<br>MB90F357TAS<br>MB90356TAS<br>MB90357TAS                                                   |

|                      |           | Vcc = 5.0 V,<br>Internal frequency: 8 kHz,<br>During stopping clock<br>monitor function,<br>At watch mode<br>T <sub>A</sub> = +25°C | _                                                                                                                                   | 10  | 35    | μА  | MB90F351<br>MB90F352<br>MB90F351A<br>MB90F352A<br>MB90F356A<br>MB90F357A<br>MB90351A<br>MB90352A<br>MB90356A<br>MB90357A |                                                                                                          |

```

(MB90F352(S)/MB90F351(S): T_A = -40 °C to +105 °C, V_{CC} = 5.0 V \pm 10%, f_{CP} \le 24 MHz, V_{SS} = AV_{SS} = 0 V) (MB90F352(S)/MB90F351(S): T_A = -40 °C to +125 °C, V_{CC} = 5.0 V \pm 10%, f_{CP} \le 24 MHz, V_{SS} = AV_{SS} = 0 V) (Device other than above: T_A = -40 °C to +125 °C, V_{CC} = 5.0 V \pm 10%, f_{CP} \le 24 MHz, V_{SS} = AV_{SS} = 0 V)

```

| Parameter                                           | Symbol       | Pin         |       | Value |     | Unit    | Remarks                                                                             |

|-----------------------------------------------------|--------------|-------------|-------|-------|-----|---------|-------------------------------------------------------------------------------------|

| Farameter                                           | Syllibol     | FIII        | Min   | Тур   | Max | Offic   | Kemarks                                                                             |

|                                                     |              |             | 1.5   |       | 24  | MHz     | MB90F352/(S), MB90F351/(S) When using main clock ( $T_A \le +105$ °C)               |

| Internal operating clock frequency (machine clock)  | fсғ          | _           | 1.5   |       | 16  | IVII IZ | MB90F352/(S), MB90F351/(S) When using main clock $(T_A \leq +125~^{\circ}C)$        |

|                                                     |              |             | 1.5   |       | 24  | MHz     | Device other than above,<br>When using main clock                                   |

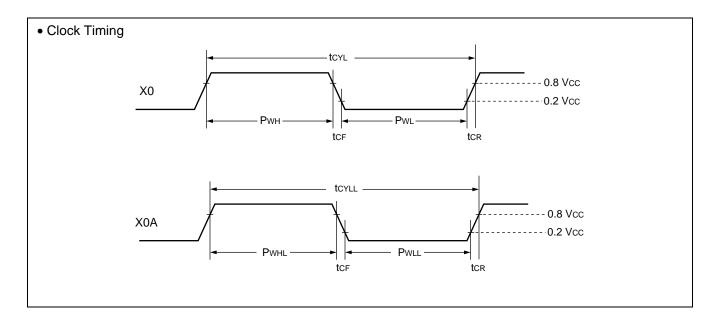

|                                                     | <b>f</b> CPL |             | _     | 8.192 | 50  | kHz     | When using sub clock                                                                |

|                                                     | tср          |             | 41.67 |       | 666 |         | MB90F352/(S), MB90F351/(S) When using main clock $(T_A \le +105  ^{\circ}\text{C})$ |

| Internal operating clock cycle time (machine clock) |              | <b>t</b> cp | _     | 62.5  | _   | 000     | ns                                                                                  |

|                                                     |              |             | 41.67 |       | 666 | ns      | Device other than above,<br>When using main clock                                   |

|                                                     | <b>t</b> CPL | _           | 20    | 122.1 | _   | μs      | When using sub clock                                                                |

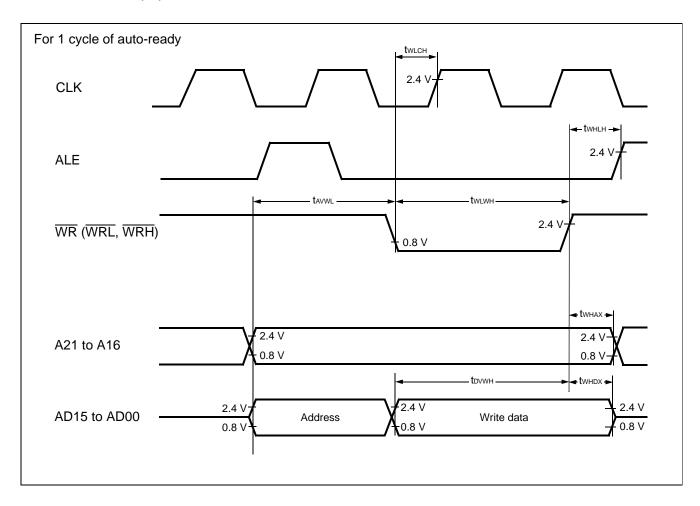

### (6) Bus Timing (Write)

$(T_A = -40^{\circ}C \text{ to } +105^{\circ}C, \text{ Vcc} = 5.0 \text{ V} \pm 10 \%, \text{ Vss} = 0.0 \text{ V}, \text{ fcp} \le 24 \text{ MHz})$

| Parameter                                                                                   | Symbol        | Pin                                | Condition | Value            | Unit | Remarks |             |

|---------------------------------------------------------------------------------------------|---------------|------------------------------------|-----------|------------------|------|---------|-------------|

| i arameter                                                                                  | Symbol        |                                    | Condition | Min              | Max  | Oilit   | iveillai ks |

| Valid address $\Rightarrow$ WR ↓ time                                                       | tavwl         | A21 to A16,<br>AD15 to AD00,<br>WR |           | tcp-15           | _    | ns      |             |

| WR pulse width                                                                              | twlwh         | WR                                 |           | (n*+3/2)tcp - 20 | _    | ns      |             |

| Valid data output $\Rightarrow$ $\overline{\text{WR}}$ $\uparrow$ time                      | <b>t</b> dvwh | AD15 to AD00,<br>WR                |           | (n*+3/2)tcp - 20 | _    | ns      |             |

| $\overline{\mathrm{WR}} \uparrow \Rightarrow \mathrm{Data} \ \mathrm{hold} \ \mathrm{time}$ | <b>t</b> whdx | AD15 to AD00,<br>WR                |           | 15               | _    | ns      |             |

| $\overline{\mathrm{WR}}\!\uparrow\Rightarrow\mathrm{Address}\mathrm{valid}\mathrm{time}$    | twhax         | A21 to A16,<br>WR                  |           | tcp/2 - 10       | _    | ns      |             |

| $\overline{WR} \uparrow \Rightarrow ALE \uparrow time$                                      | twhlh         | WR, ALE                            |           | tcp/2 - 15       | _    | ns      |             |

| $\overline{WR} \downarrow \Rightarrow CLK \uparrow time$                                    | twlch         | WR, CLK                            |           | tcp/2 - 15       | _    | ns      |             |

<sup>\*:</sup> n: Number of ready cycles

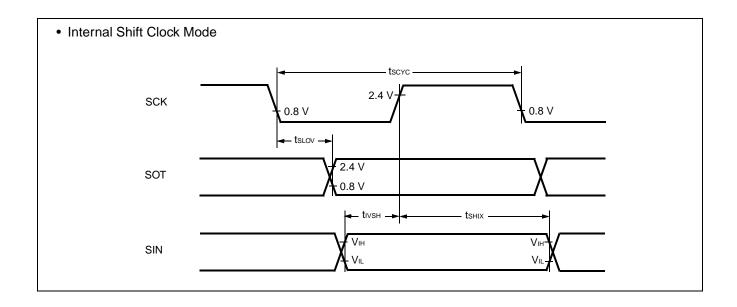

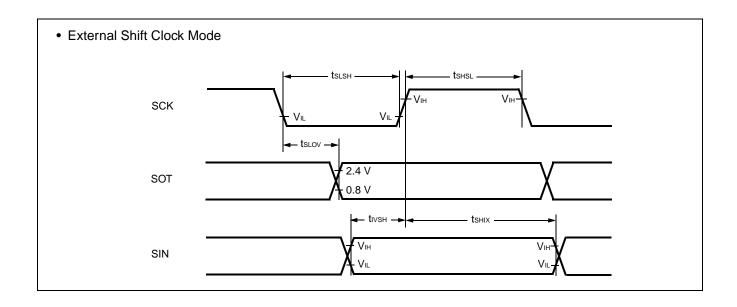

### (9) UART 2/3

$\begin{tabular}{ll} $(MB90F352(S)/MB90F351(S): $T_A = -40 $^\circ$C to $+105 $^\circ$C, $V_{CC} = 5.0 V \pm 10\%, f_{CP} \le 24 $MHz$, $V_{SS} = AV_{SS} = 0 V$) \\ $(MB90F352(S)/MB90F351(S): $T_A = -40 $^\circ$C to $+125 $^\circ$C, $V_{CC} = 5.0 V \pm 10\%, f_{CP} \le 16 $MHz$, $V_{SS} = AV_{SS} = 0 V$) \\ $(Device other than above: $T_A = -40 $^\circ$C to $+125 $^\circ$C, $V_{CC} = 5.0 V \pm 10\%, f_{CP} \le 24 $MHz$, $V_{SS} = AV_{SS} = 0 V$) \\ \end{tabular}$

| Parameter                                       | Symbol        | ool Pin Condition         |                                          | Value  |         | Unit | Remarks |

|-------------------------------------------------|---------------|---------------------------|------------------------------------------|--------|---------|------|---------|

| raiailletei                                     | Symbol        | FIII                      | Condition                                | Min    | Min Max |      | Kemarks |

| Serial clock cycle time                         | tscyc         | SCK2, SCK3                |                                          | 8 tcp* | _       | ns   |         |

| $SCK \downarrow \; 	o \; SOT \; delay \; time$  | <b>t</b> sLOV | SCK2, SCK3,<br>SOT2, SOT3 | Internal shift clock<br>mode output pins | -80    | +80     | ns   |         |

| Valid SIN → SCK ↑                               | <b>t</b> ıvsh | SCK2, SCK3,<br>SIN2, SIN3 | are<br>C <sub>L</sub> = 80 pF + 1 TTL    | 100    |         | ns   |         |

| $SCK \uparrow \rightarrow Valid SIN hold time$  | <b>t</b> sнıx | SCK2, SCK3,<br>SIN2, SIN3 |                                          | 60     | _       | ns   |         |

| Serial clock "H" pulse width                    | <b>t</b> shsl | SCK2, SCK3                |                                          | 4 tcp  | _       | ns   |         |

| Serial clock "L" pulse width                    | <b>t</b> slsh | SCK2, SCK3                |                                          | 4 tcp  | _       | ns   |         |

| $SCK \downarrow \; 	o \; SOT \; delay \; time$  | <b>t</b> sLOV | SCK2, SCK3,<br>SOT2, SOT3 | External shift clock mode output pins    | _      | 150     | ns   |         |

| Valid SIN → SCK ↑                               | <b>t</b> ıvsh | SCK2, SCK3,<br>SIN2, SIN3 | are<br>C <sub>L</sub> = 80 pF + 1 TTL    | 60     |         | ns   |         |

| $SCK  \! \uparrow  \to  Valid  SIN  hold  time$ | <b>t</b> sнıx | SCK2, SCK3,<br>SIN2, SIN3 |                                          | 60     |         | ns   |         |

<sup>\*:</sup> Refer to "(1) Clock timing" rating for top (internal operating clock cycle time).

Notes: • AC characteristic in CLK synchronized mode.

• C<sub>L</sub> is load capacity value of pins when testing.

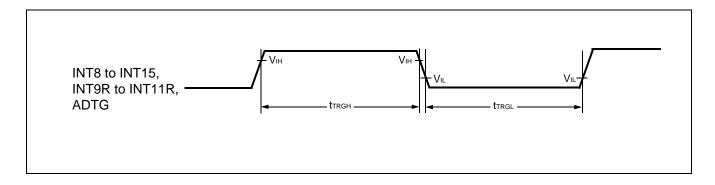

### (10) Trigger Input Timing

$\label{eq:mb90F352(S)/MB90F351(S): $T_A = -40 °C$ to $+105 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (MB90F352(S)/MB90F351(S): $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 16$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = 5.0 V$ $10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $-125 °C$, $V_{CC} = 5.0 V$ $10\%$, $T_{CC} = 10\%$, $T_{CC} =$

| Parameter         | Symbol         | Pin                                        | Condition | Va    | lue | Unit | Remarks     |

|-------------------|----------------|--------------------------------------------|-----------|-------|-----|------|-------------|

| raiametei         | Syllibol       | FIII                                       | Condition | Min   | Max | Onne | iveillai ks |

| Input pulse width | ttrgh<br>ttrgl | INT8 to INT15,<br>INT9R to INT11R,<br>ADTG | _         | 5 tcp | _   | ns   |             |

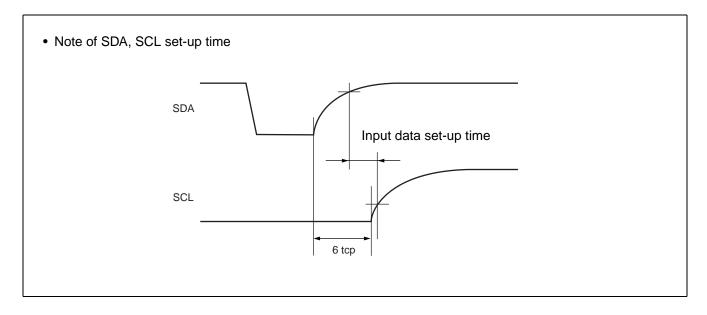

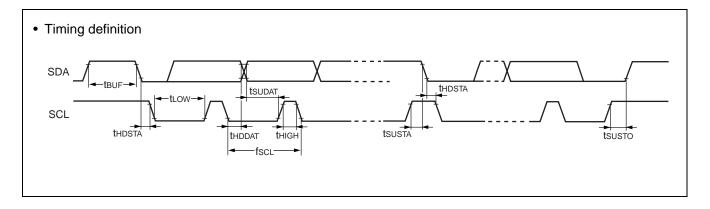

### (13) I2C Timing

$\label{eq:mb90F352(S)/MB90F351(S): $T_A = -40 °C$ to $+105 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (MB90F352(S)/MB90F351(S): $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 16$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0 V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0$ V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0$ V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0$ V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0$ V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0$ V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0$ V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$, $f_{CP} \le 24$ MHz, $V_{SS} = AV_{SS} = 0$ V$) $ (Device other than above: $T_A = -40 °C$ to $+125 °C$, $V_{CC} = AV_{CC} = 5.0 V$ $$ (Device other than above) $$ (Device other than a$

| Parameter                                                                              | Symbol         | Condition                   | Standar | d-mode | Fast-m | Unit  |       |

|----------------------------------------------------------------------------------------|----------------|-----------------------------|---------|--------|--------|-------|-------|

| Parameter                                                                              | Syllibol       | Condition                   | Min     | Max    | Min    | Max   | Ullit |

| SCL clock frequency                                                                    | fscL           |                             | 0       | 100    | 0      | 400   | kHz   |

| Hold time for (repeated) START condition SDA $\downarrow \rightarrow$ SCL $\downarrow$ | <b>t</b> HDSTA |                             | 4.0     |        | 0.6    | _     | μs    |

| "L" width of the SCL clock                                                             | <b>t</b> LOW   |                             | 4.7     |        | 1.3    | _     | μs    |

| "H" width of the SCL clock                                                             | <b>t</b> HIGH  |                             | 4.0     | _      | 0.6    | _     | μs    |

| Set-up time for a repeated START condition SCL $\uparrow \rightarrow$ SDA $\downarrow$ | <b>t</b> susta | $R = 1.7 \text{ k}\Omega$ , | 4.7     |        | 0.6    | _     | μs    |

| Data hold time<br>SCL↓→SDA↓↑                                                           | <b>t</b> hddat | $C = 50 \text{ pF}^{*1}$    | 0       | 3.45*2 | 0      | 0.9*3 | μs    |

| Data set-up time<br>SDA↓↑→SCL↑                                                         | <b>t</b> sudat |                             | 250*5   |        | 100*5  |       | ns    |

| Set-up time for STOP condition SCL↑→SDA↑                                               | tsusto         |                             | 4.0     | _      | 0.6    |       | μs    |

| Bus free time between STOP condition and START condition                               | <b>t</b> BUS   |                             | 4.7     |        | 1.3    |       | μs    |

- \*1: R,C: Pull-up resistor and load capacitor of the SCL and SDA lines.

- \*2: The maximum thddat has only to be met if the device does not stretch the "L" width (tLow) of the SCL signal.

- \*3 : A Fast-mode I<sup>2</sup>C -bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement tsudat ≥ 250 ns must then be met.

- \*4: For use at over 100 kHz, set the machine clock to at least 6 MHz.

- \*5: Refer to ". Note of SDA, SCL set-up time".

Note: The rating of the input data set-up time in the device connected to the bus cannot be satisfied depending on the load capacitance or pull-up resistor.

Be sure to adjust the pull-up resistor of SDA and SCL if the rating of the input data set-up time cannot be satisfied.

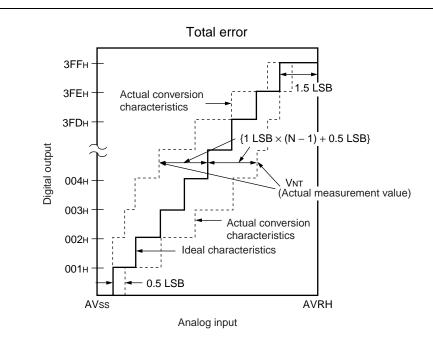

### 6. Definition of A/D Converter Terms

Resolution : Analog variation that is recognized by an A/D converter.

Non linearity : Deviation between a line across zero-transition line ( "00 0000 0000"  $\leftarrow$   $\rightarrow$  "00 0000 0001") error and full-scale transition line ( "11 1111 1110"  $\leftarrow$   $\rightarrow$  "11 1111 1111") and actual conversion

characteristics.

Differential : Deviation of input voltage, which is required for changing output code by 1 LSB, from an ideal linearity error value.

Total error : Difference between an actual value and a theoretical value. A total error includes zero tran-

sition error, full-scale transition error, and linear error.

Total error of digital output "N" =

$$\frac{V_{NT} - \{1 \text{ LSB} \times (N-1) + 0.5 \text{ LSB}\}}{1 \text{ LSB}}$$

[LSB]

1 LSB = (Ideal value)

$$\frac{AVRH - AV_{SS}}{1024}$$

[V]

N: A/D converter digital output value

Vot (Ideal value) = AVss + 0.5 LSB [V]

V<sub>FST</sub> (Ideal value) = AVRH - 1.5 LSB [V]

$V_{NT}$ : A voltage at which digital output transits from (N-1) to N.

| Part number     | Package                            | Remarks                                  |  |  |  |

|-----------------|------------------------------------|------------------------------------------|--|--|--|

| MB90F351APMC1   |                                    |                                          |  |  |  |

| MB90F351ASPMC1  |                                    |                                          |  |  |  |

| MB90F351TAPMC1  |                                    |                                          |  |  |  |