Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

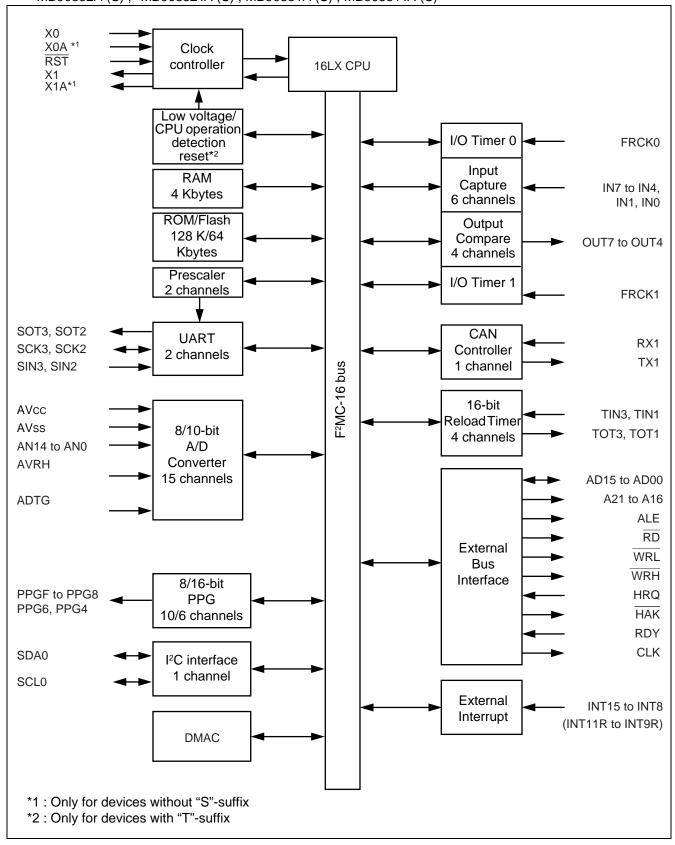

| Core Processor             | F <sup>2</sup> MC-16LX                                                           |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                            |

| Peripherals                | DMA, LVD, POR, WDT                                                               |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 15x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-QFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f352spfm-gs-118e1 |

#### **■ FEATURES**

#### Clock

- Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 6 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 24 MHz).

- Operation by sub clock (up to 50 kHz: 100 kHz oscillation clock divided by two) is allowed. (devices without S-suffix only)

- Minimum execution time of instruction: 42 ns (when operating with 4-MHz oscillation clock, and 6-time multiplied PLL clock).

- · Built-in clock modulation circuit

### • 16 Mbytes CPU memory space

24-bit internal addressing

## • Clock monitor function (MB90x356x and MB90x357x only)

- Main clock or sub clock is monitored independently.

- Internal CR oscillation clock (100 kHz typical) can be used as sub clock.

## • Instruction system best suited to controller

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions with sign and RETI instructions

- Enhanced high-precision computing with 32-bit accumulator

## • Instruction system compatible with high-level language (C language) and multitask

- Employing system stack pointer

- · Enhanced various pointer indirect instructions

- · Barrel shift instructions

### Increased processing speed

• 4-byte instruction queue

#### • Powerful interrupt function

- Powerful 8-level, 34-condition interrupt feature

- Up to 8 channels external interrupts are supported.

### Automatic data transfer function independent of CPU

- Extended intelligent I/O service function (El<sup>2</sup>OS): up to 16 channels

- DMA: up to 16 channels

#### • Low power consumption (standby) mode

- Sleep mode (a mode that halts CPU operating clock)

- Main timer mode (a timebase timer mode switched from the main clock mode)

- PLL timer mode (a timebase timer mode switched from the PLL clock mode)

- Watch mode (a mode that operates sub clock and watch timer only)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU intermittent operation mode

#### Process

CMOS technology

## ■ PACKAGES AND PRODUCT CORRESPONDENCE

| Package                               | MB90V340A<br>-101<br>-102<br>-103<br>-104 | MB90F351<br>MB90F351S<br>MB90F352<br>MB90F352S | MB90F351A (S) , MB90F351TA (S) MB90F352A (S) , MB90F352TA (S) MB90F356A (S) , MB90F356TA (S) MB90F357A (S) , MB90F357TA (S) MB90351A (S) , MB90351TA (S) MB90352A (S) , MB90352TA (S) MB90356A (S) , MB90356TA (S) MB90357A (S) , MB90357TA (S) |

|---------------------------------------|-------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGA-299C-A01                          | 0                                         | ×                                              | ×                                                                                                                                                                                                                                               |

| FPT-64P-M09<br>(12 mm, 0.65 mm pitch) | ×                                         | 0                                              | ×                                                                                                                                                                                                                                               |

| FPT-64P-M23<br>(12 mm, 0.65 mm pitch) | ×                                         | ×                                              | 0                                                                                                                                                                                                                                               |

| FPT-64P-M24<br>(10 mm, 0.50 mm pitch) | ×                                         | ×                                              | O*                                                                                                                                                                                                                                              |

<sup>\*:</sup> This device is under development.

$\bigcirc$  : Yes,  $\times$  : No

Note: Refer to "■ PACKAGE DIMENSIONS" for detail of each package.

| Pin No.  | Din nama      | Circuit | Franction                                                                                                                                     |  |  |  |  |

|----------|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LQFP64*  | Pin name      | type    | Function                                                                                                                                      |  |  |  |  |

|          | P00 to P07    |         | General purpose I/O ports. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode. |  |  |  |  |

| 24 to 31 | AD00 to AD07  | G       | Input/output pins of external address data bus lower 8 bits. This function is enabled when the external bus is enabled.                       |  |  |  |  |

|          | INT8 to INT15 |         | External interrupt request input pins for INT8 to INT15                                                                                       |  |  |  |  |

|          | P10           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 32       | AD08          | G       | Input/output pin for external bus address data bus bit 8. This function is enabled when external bus is enabled.                              |  |  |  |  |

|          | TIN1          |         | Event input pin for reload timer1                                                                                                             |  |  |  |  |

|          | P11           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 33       | AD09          | G       | Input/output pin for external bus address data bus bit 9. This function is enabled when external bus is enabled.                              |  |  |  |  |

|          | TOT1          |         | Output pin for reload timer1                                                                                                                  |  |  |  |  |

|          | P12           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 34       | AD10          | N       | Input/output pin for external bus address data bus bit 10. This function is enabled when external bus is enabled.                             |  |  |  |  |

|          | SIN3          |         | Serial data input pin for UART3                                                                                                               |  |  |  |  |

|          | INT11R        |         | External interrupt request input pin for INT11                                                                                                |  |  |  |  |

|          | P13           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 35       | AD11          | G       | Input/output pin for external bus address data bus bit 11. This function is enabled when external bus is enabled.                             |  |  |  |  |

|          | SOT3          |         | Serial data output pin for UART3                                                                                                              |  |  |  |  |

|          | P14           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 36       | AD12          | G       | Input/output pin for external bus address data bus bit 12. This function is enabled when external bus is enabled.                             |  |  |  |  |

|          | SCK3          |         | Clock input/output pin for UART3                                                                                                              |  |  |  |  |

| 37       | P15           | N       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 31       | AD13          |         | Input/output pin for external bus address data bus bit 13. This function is enabled when external bus is enabled.                             |  |  |  |  |

| 38       | P16           | G       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 30       | AD14          | G       | Input/output pin for external bus address data bus bit 14. This function is enabled when external bus is enabled.                             |  |  |  |  |

#### **■ HANDLING DEVICES**

Special care is required for the following when handling the device :

- Preventing latch-up

- Treatment of unused pins

- Using external clock

- · Precautions for when not using a sub clock signal

- Notes on during operation of PLL clock mode

- Power supply pins (Vcc/Vss)

- Pull-up/down resistors

- · Crystal Oscillator Circuit

- Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

- Connection of Unused Pins of A/D Converter

- · Notes on Energization

- Stabilization of power supply voltage

- Initialization

- Port0 to port3 output during Power-on (External-bus mode)

- Notes on using CAN Function

- Flash security Function

- Correspondence with T<sub>A</sub> = + 105 °C or more

- Low voltage/CPU operation detection reset circuit

- Internal CR oscillation circuit

## 1. Preventing latch-up

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than Vcc or lower than Vss is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between Vcc pin and Vss pin.

- The AVcc power supply is applied before the Vcc voltage.

Latch-up may increase the power supply current drastically, causing thermal damage to the device.

In using the devices, take sufficient care to avoid exceeding maximum ratings.

For the same reason, also be careful not to let the analog power-supply voltage (AVcc, AVRH) exceed the digital power-supply voltage.

### 2. Handling unused pins

Leaving unused input pins open may result in misbehavior or latch up and possible permanent damage of the device. Therefore they must be pulled up or pulled down through resistors. In this case those resistors should be more than  $2 \ k\Omega$ .

Unused I/O pins should be set to the output state and can be left open, or the input state with the above described connection.

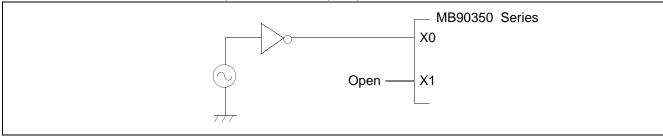

#### 3. Using external clock

To use external clock, drive the X0 pin and leave X1 pin open.

MB90F352 (S), MB90F351 (S), MB90F352A (S), MB90F352TA (S), MB90F351A (S), MB90F351TA (S), MB90352A (S), MB90352TA (S), MB90351TA (S)

| Address           | Register                                     | Abbrevia-<br>tion | Access      | Resource name        | Initial value |

|-------------------|----------------------------------------------|-------------------|-------------|----------------------|---------------|

| САн               | External Interrupt Enable Register 1         | ENIR1             | R/W         |                      | 00000000в     |

| СВн               | External Interrupt Source Register 1         | EIRR1             | R/W         |                      | XXXXXXXXB     |

| ССн               | External Interrupt Level Register 1          | ELVR1             | R/W         | External Interrupt 1 | 0000000В      |

| СДн               | External Interrupt Level Register 1          | ELVR1             | R/W         | External interrupt 1 | 0000000В      |

| СЕн               | External Interrupt Source Select<br>Register | EISSR             | R/W         |                      | 00000000в     |

| СҒн               | PLL/Sub clock Control register               | PSCCR             | W           | PLL                  | XXXX0000B     |

| D0н               | DMA Buffer Address Pointer L                 | BAPL              | R/W         |                      | XXXXXXXXB     |

| <b>D</b> 1н       | DMA Buffer Address Pointer M                 | BAPM              | R/W         |                      | XXXXXXX       |

| D2н               | DMA Buffer Address Pointer H                 | BAPH              | R/W         |                      | XXXXXXX       |

| D3 <sub>н</sub>   | DMA Control Register                         | DMACS             | R/W         | DMA                  | XXXXXXX       |

| <b>D4</b> н       | I/O Register Address Pointer L               | IOAL              | R/W         | DIVIA                | XXXXXXX       |

| <b>D</b> 5н       | I/O Register Address Pointer H               | IOAH              | R/W         |                      | XXXXXXX       |

| D6н               | Data Counter L                               | DCTL              | R/W         |                      | XXXXXXX       |

| <b>D7</b> н       | Data Counter H                               | DCTH              | R/W         |                      | XXXXXXX       |

| <b>D</b> 8н       | Serial Mode Register 2                       | SMR2              | W,R/W       |                      | 0000000В      |

| <b>D</b> 9н       | Serial Control Register 2                    | SCR2              | W,R/W       |                      | 0000000В      |

| DAн               | Reception/Transmission Data Register 2       | RDR2/<br>TDR2     | R/W         |                      | 00000000в     |

| DВн               | Serial Status Register 2                     | SSR2              | R,R/W       | UART2                | 00001000в     |

| DCн               | Extended Communication Control Register 2    | ECCR2             | R,W,<br>R/W | UARTZ                | 000000XXB     |

| DDн               | Extended Status/Control Register 2           | ESCR2             | R/W         |                      | 00000100в     |

| DЕн               | Baud Rate Generator Register 20              | BGR20             | R/W         |                      | 0000000в      |

| DFн               | Baud Rate Generator Register 21              | BGR21             | R/W         |                      | 0000000в      |

| E0н to EFн        |                                              | Reserve           | ed          |                      |               |

| F0н to FFн        |                                              | External a        | area        |                      |               |

| 7900н to<br>7907н |                                              | Reserve           | ed          |                      | (Cantinuad)   |

| Address           | Register                             | Register Abbrevia-<br>tion Access Resource name |                   | Initial value      |           |

|-------------------|--------------------------------------|-------------------------------------------------|-------------------|--------------------|-----------|

| 792Сн             | Input Capture Register 6             | IPCP6                                           | R                 |                    | XXXXXXXXB |

| 792Dн             | Input Capture Register 6             | IPCP6                                           | R                 | Input Conturo 6/7  | XXXXXXXXB |

| 792Ен             | Input Capture Register 7             | IPCP7                                           | R                 | Input Capture 6/7  | XXXXXXXXB |

| 792Fн             | Input Capture Register 7             | IPCP7                                           | R                 |                    | XXXXXXXXB |

| 7930н to<br>7937н |                                      | Reserve                                         | ed                |                    |           |

| 7938н             | Output Compare Register 4            | OCCP4                                           | R/W               |                    | XXXXXXX   |

| 7939н             | Output Compare Register 4            | OCCP4                                           | R/W               | Output Compare 4/E | XXXXXXX   |

| 793Ан             | Output Compare Register 5            | OCCP5                                           | R/W               | Output Compare 4/5 | XXXXXXXXB |

| 793Вн             | Output Compare Register 5            | OCCP5                                           | R/W               |                    | XXXXXXXXB |

| 793Сн             | Output Compare Register 6            | OCCP6                                           | R/W               |                    | XXXXXXXXB |

| 793Dн             | Output Compare Register 6            | OCCP6                                           | R/W               | Output Compare 6/7 | XXXXXXXXB |

| 793Ен             | Output Compare Register 7            | OCCP7                                           | R/W               | Output Compare 6/7 | XXXXXXXX  |

| 793Гн             | Output Compare Register 7            | OCCP7                                           | R/W               |                    | XXXXXXXX  |

| 7940н             | Timer Data Register 0                | TCDT0                                           | R/W               |                    | 00000000в |

| 7941н             | Timer Data Register 0                | TCDT0                                           | R/W               | I/O Time or O      | 0000000в  |

| 7942н             | Timer Control Status Register 0      | TCCSL0                                          | R/W               | I/O Timer 0        | 0000000в  |

| 7943н             | Timer Control Status Register 0      | TCCSH0                                          | R/W               |                    | 0XXXXXXXB |

| 7944н             | Timer Data Register 1                | TCDT1                                           | R/W               |                    | 00000000в |

| 7945н             | Timer Data Register 1                | TCDT1                                           | R/W               | I/O Time on 4      | 0000000в  |

| 7946н             | Timer Control Status Register 1      | TCCSL1                                          | R/W               | I/O Timer 1        | 0000000в  |

| 7947н             | Timer Control Status Register 1      | TCCSH1                                          | R/W               |                    | 0XXXXXXXB |

| 7948н             | Times Decister O/Deleged Decister O  | TMR0/                                           | R/W               | 16-bit Reload      | XXXXXXXXB |

| 7949н             | Timer Register 0/Reload Register 0   | TMRLR0                                          | R/W               | Timer 0            | XXXXXXXX  |

| 794Ан             | Times Decister 4/Deleged Decister 4  | TMR1/                                           | R/W               | 16-bit Reload      | XXXXXXXXB |

| 794Вн             | - Timer Register 1/Reload Register 1 | TMRLR1                                          | R/W               | Timer 1            | XXXXXXXX  |

| 794Сн             | Timer Degister 2/Delegel Degister 2  | TMR2/                                           | R/W 16-bit Reload |                    | XXXXXXXX  |

| 794Dн             | - Timer Register 2/Reload Register 2 | TMRLR2                                          | R/W               | Timer 2            | XXXXXXXX  |

| 794Ен             | Timer Degister 2/Delegal Degister 2  | TMR3/                                           | R/W               | 16-bit Reload      | XXXXXXXX  |

| 794Fн             | Timer Register 3/Reload Register 3   | TMRLR3                                          | R/W               | Timer 3            | XXXXXXXXB |

## (Continued)

| Address           | Register                                                   | Abbrevia-<br>tion | Access               | Resource name             | Initial value |  |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------|-------------------|----------------------|---------------------------|---------------|--|--|--|--|--|--|--|

| 79С2н             | Setting Prohibited                                         |                   |                      |                           |               |  |  |  |  |  |  |  |

| 79С3н to<br>79DFн | Reserved                                                   |                   |                      |                           |               |  |  |  |  |  |  |  |

| 79Е0н             | Detect Address Setting Register 0                          | PADR0             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79Е1н             | Detect Address Setting Register 0                          | PADR0             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79Е2н             | Detect Address Setting Register 0                          | PADR0             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79ЕЗн             | Detect Address Setting Register 1                          | PADR1             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79Е4н             | Detect Address Setting Register 1                          | PADR1             | R/W                  | Address Match Detection 0 | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79Е5н             | Detect Address Setting Register 1                          | PADR1             | R/W                  | Detection                 | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79Е6н             | Detect Address Setting Register 2                          | PADR2             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79Е7н             | Detect Address Setting Register 2                          | PADR2             | R/W                  |                           | XXXXXXXX      |  |  |  |  |  |  |  |

| 79Е8н             | Detect Address Setting Register 2                          | PADR2             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79Е9н to<br>79ЕFн |                                                            | Reserv            | ed                   |                           |               |  |  |  |  |  |  |  |

| <b>79F0</b> н     | Detect Address Setting Register 3                          | PADR3             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| <b>79F1</b> н     | Detect Address Setting Register 3                          | PADR3             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79F2н             | Detect Address Setting Register 3                          | PADR3             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79F3н             | Detect Address Setting Register 4                          | PADR4             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79F4н             | Detect Address Setting Register 4                          | PADR4             | R/W                  | Address Match Detection 1 | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79F5н             | Detect Address Setting Register 4                          | PADR4             | R/W                  | Detection                 | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79F6н             | Detect Address Setting Register 5                          | PADR5             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| <b>79F7</b> н     | Detect Address Setting Register 5                          | PADR5             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79F8⊦             | Detect Address Setting Register 5                          | PADR5             | R/W                  |                           | XXXXXXXXB     |  |  |  |  |  |  |  |

| 79F9н to<br>7BFFн |                                                            | Reserv            | ed                   |                           |               |  |  |  |  |  |  |  |

| 7C00н to<br>7CFFн | Reserved for CAN Int                                       | erface 1. Refe    | er to " <b>■</b> CAN | N CONTROLLERS"            |               |  |  |  |  |  |  |  |

| 7D00н to<br>7DFFн | Reserved for CAN Interface 1. Refer to "■ CAN CONTROLLERS" |                   |                      |                           |               |  |  |  |  |  |  |  |

| 7E00н to<br>7FFFн | Reserved                                                   |                   |                      |                           |               |  |  |  |  |  |  |  |

Notes: • Initial value of "X" represents unknown value.

• Any write access to reserved addresses in I/O map should not be performed. A read access to reserved addresses results reading "X".

| CAN1         Register         Abbreviation         Access         Initial value           007D00H         Control status register         CSR         R/W, W         00XXXX000s           007D02H         Last event indicator register         LEIR         R/W         000X0000s           007D03H         Control status register         LEIR         R/W         000X0000s           007D04H         Control status register         LEIR         R/W         000X0000s           007D05H         Receive/transmit error counter         RTEC         R         000000000s           007D06H         Bit timing register         BTR         R/W         111111111s           007D08H         IDE register         IDER         R/W         XXXXXXXXxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Address | - Register                     | Abbreviation | Access  | Initial Value  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------|--------------|---------|----------------|--|--|

| 007D01H         Control status register         CSR         RW, R         00XXX000B           007D02H         Last event indicator register         LEIR         R/W         000X0000B           007D03H         Receive/transmit error counter         RTEC         R         00000000B           007D05H         Bit timing register         BTR         R/W         11111111B           007D07H         Bit timing register         BTR         R/W         1111111B           007D08H         IDE register         IDER         R/W         XXXXXXXXB           007D09H         Transmit RTR register         TRTRR         R/W         00000000B           007D0AH         Transmit erceive waiting register         RFWTR         R/W         XXXXXXXXB           007D0CH         Remote frame receive waiting register         RFWTR         R/W         00000000B           007D0FH         Transmit interrupt enable register         TIER         R/W         00000000B           007D10H         Acceptance mask select register         AMSR         R/W         XXXXXXXXXB           007D13H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXXB           007D15H         Acceptance mask register 1         AMR1         AMR1         R/W | CAN1    | Register                       | Appleviation | Access  | illiliai value |  |  |

| 007D01H         007D02H         Last event indicator register         LEIR         R/W, R         000XX000b           007D03H         Last event indicator register         LEIR         R/W         000X0000b           007D04H         Receive/transmit error counter         RTEC         R         00000000b           007D05H         Bit timing register         BTR         R/W         11111111b           007D07H         IDE register         IDER         R/W         XXXXXXXXB           007D08H         IDE register         IDER         R/W         XXXXXXXXB           007D09H         Transmit RTR register         TRTRR         R/W         00000000b           007D0CH         Remote frame receive waiting register         RFWTR         R/W         XXXXXXXXB           007D0DH         Transmit interrupt enable register         TIER         R/W         00000000b           007D10H         Acceptance mask select register         AMSR         R/W         XXXXXXXXB           007D12H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXB           007D15H         Acceptance mask register 1         AMR0         R/W         XXXXXXXXB           007D16H         Acceptance mask register 1         AMR1         R/W     | 007D00н | Control status register        | CSB          | R/W, W  | 0XXXX0X1в      |  |  |

| DOTD03H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 007D01н | — Control status register      | CSK          | R/W, R  | 00XXX000в      |  |  |

| 007D03H         Receive/transmit error counter         RTEC         R         000000000s 00000000s 00000000s 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 007D02н | Last event indicator register  | I EID        | DAM     | 000Х0000в      |  |  |

| 007D05H         Receive/transmit error counter         RTEC         R         00000000B           007D06H         Bit timing register         BTR         R/W         11111111B           007D07H         107D08H         Bit timing register         IDER         R/W         XXXXXXXXB           007D09H         107D09H         IDE register         TRTRR         R/W         00000000B           007D0AH         Transmit RTR register         TRTRR         R/W         00000000B           007D0CH         Remote frame receive waiting register         RFWTR         R/W         XXXXXXXXB           007D0FH         Transmit interrupt enable register         TIER         R/W         00000000B           007D10H         Acceptance mask select register         AMSR         R/W         XXXXXXXXB           007D13H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXB           007D15H         XXXXXXXXB         XXXXXXXXB         XXXXXXXXB           007D17H         XXXXXXXXB         XXXXXXXXB           007D18H         XXXXXXXXB         XXXXXXXXB           007D19H         XXXXXXXXB         XXXXXXXXB           XXXXXXXXB         XXXXXXXXB                                                                                    | 007D03н | Last event indicator register  | LEIK         | K/VV    | XXXXXXXB       |  |  |

| 007D05H         007D06H         Bit timing register         BTR         R/W         11111111B X111111B X111111B X1111111B X1111111B X1111111B X1111111B X1111111B           007D08H         IDE register         IDER         R/W         XXXXXXXXB XXXXXXXB XXXXXXXB XXXXXXXB XXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 007D04н | Pagaiya/tranamit arrar aguntar | DTEC         | В       | 0000000В       |  |  |

| 007D07H         Bit timing register         BTR         R/W         X1111111B           007D08H         IDE register         IDER         R/W         XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 007D05н | Receive/transmit error counter | RIEC         | K       | 0000000в       |  |  |

| 007D07H         007D08H         IDE register         IDER         R/W         XXXXXXXX8<br>XXXXXXXX8<br>XXXXXXXX8<br>XXXXXXXX8           007D0AH<br>007D0BH         Transmit RTR register         TRTRR         R/W         000000000b<br>00000000b<br>00000000b           007D0CH<br>007D0CH         Remote frame receive waiting<br>register         RFWTR         R/W         XXXXXXXX8<br>XXXXXXXX8           007D0EH         Transmit interrupt<br>enable register         TIER         R/W         00000000b<br>0000000b<br>0000000b           007D10H         Acceptance mask<br>select register         AMSR         R/W         XXXXXXXXX<br>XXXXXXXX8<br>XXXXXXXX8<br>XXXXXXXX8<br>XXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 007D06н | Bit timing register            | DTD          | DΛΛ     |                |  |  |

| IDE register   IDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 007D07н |                                | DIK          | FX/VV   | Х1111111в      |  |  |

| 007D09H         XXXXXXXB           007D0AH         Transmit RTR register         TRTRR         R/W         00000000B 0000000B 00000000B 00000000B           007D0CH         Remote frame receive waiting register         RFWTR         R/W         XXXXXXXXXB XXXXXXXB XXXXXXXXB           007D0EH         Transmit interrupt enable register         TIER         R/W         00000000B 0000000B 0000000B 0000000B 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 007D08н | IDE register                   | IDED         | DΛΛ     |                |  |  |

| 007D0BH         Transmit RTR register         TRTRR         R/W         000000008           007D0CH         Remote frame receive waiting register         RFWTR         R/W         XXXXXXXXB XXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 007D09н | IDE Tegistei                   | IDEK         | FX/ V V | XXXXXXX        |  |  |

| 007D0BH         CO0000000B           007D0CH         Remote frame receive waiting register         RFWTR         R/W         XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 007D0Ан | Transmit DTD register          | TDTDD        | DΛΛ     | 0000000в       |  |  |

| 007D0DH         register         RFWTR         R/W         XXXXXXXXB           007D0EH         Transmit interrupt enable register         TIER         R/W         000000000B 00000000B 00000000B 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 007D0Вн | Transmit KTK register          | TIVITAL      | F/VV    | 0000000в       |  |  |

| 007D0DH         register         XXXXXXXXB           007D0EH         Transmit interrupt enable register         TIER         R/W         00000000B 0000000B 0000000B 00000000B 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 007D0Сн | Remote frame receive waiting   | DE\\/TD      | DΛΛ     |                |  |  |

| 007D0FH         enable register         TIER         R/W         000000000B           007D10H         Acceptance mask select register         AMSR         R/W         XXXXXXXXB XXXXXXB XXXXXXXXB XXXXXXXXB XXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 007D0Dн | register                       | IXI VVIIX    | 17/ 7/  | XXXXXXX        |  |  |

| 007D0FH         enable register         000000000B           007D10H         Acceptance mask select register         AMSR         R/W         XXXXXXXXBB           007D12H         Select register         XXXXXXXXBB         XXXXXXXXBB           007D13H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXBB           007D15H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXXBB           007D17H         Acceptance mask register 1         AMR1         R/W         XXXXXXXXXBB           007D19H         Acceptance mask register 1         AMR1         R/W         XXXXXXXXXBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 007D0Ен |                                | TIED         | DΛΛ     |                |  |  |

| 007D11H         Acceptance mask select register         AMSR         R/W         XXXXXXXXB           007D12H         007D13H         XXXXXXXXB         XXXXXXXXB           007D14H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXB           007D15H         XXXXXXXXXB         XXXXXXXXXB         XXXXXXXXXB           007D17H         Acceptance mask register 1         AMR1         R/W         XXXXXXXXXB           007D19H         Acceptance mask register 1         AMR1         R/W         XXXXXXXXXB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 007D0Fн | enable register                | HEIX         | 17/ 7/  | 0000000в       |  |  |

| 007D12H         Acceptance mask select register         AMSR         R/W           007D13H         XXXXXXXXB         XXXXXXXXB           007D14H         Acceptance mask register 0         AMR0         R/W           007D15H         XXXXXXXXB         XXXXXXXXB           007D16H         XXXXXXXXXB         XXXXXXXXB           007D17H         Acceptance mask register 1         AMR1         R/W           XXXXXXXXXB         XXXXXXXXXB           XXXXXXXXXB         XXXXXXXXXB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 007D10н |                                |              |         | XXXXXXXXB      |  |  |

| 007D12H         Select register         XXXXXXXXB           007D13H         XXXXXXXXXB           007D14H         XXXXXXXXXB           007D15H         XXXXXXXXXB           007D16H         XXXXXXXXXB           007D17H         XXXXXXXXB           007D18H         XXXXXXXXXB           007D19H         XXXXXXXXXB           007D1AH         XXXXXXXXXB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 007D11н | Acceptance mask                | AMCD         | D/M     | XXXXXXXXB      |  |  |

| 007D14H         007D15H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXXB           007D16H         007D17H         XXXXXXXXXB         XXXXXXXXXB           007D18H         007D19H         XXXXXXXXXB           007D1AH         Acceptance mask register 1         AMR1         R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 007D12н | select register                | AWON         | 17/ 7 7 |                |  |  |

| 007D15H         Acceptance mask register 0         AMR0         R/W         XXXXXXXXB           007D17H         007D18H         XXXXXXXXXB           007D19H         Acceptance mask register 1         AMR1         R/W           XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 007D13н |                                |              |         | XXXXXXXXB      |  |  |

| 007D16H         Acceptance mask register 0         AMR0         R/W           007D17H         XXXXXXXXXB           007D18H         XXXXXXXXXB           007D19H         Acceptance mask register 1           007D1AH         AMR1           R/W         XXXXXXXXXB           XXXXXXXXXXB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 007D14н |                                |              |         |                |  |  |

| 007D16H         XXXXXXXXB           007D17H         XXXXXXXXB           007D18H         XXXXXXXXB           007D19H         XXXXXXXXB           Acceptance mask register 1         AMR1           R/W         XXXXXXXXXB           XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 007D15н | Acceptance mask register 0     | ΔΜΡΩ         | P/M     | XXXXXXX        |  |  |

| 007D18H         007D19H         Acceptance mask register 1         AMR1         R/W         XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 007D16н | Acceptance mask register 0     | VINIVA       | 17/ 7/  |                |  |  |

| 007D19H     Acceptance mask register 1     AMR1     R/W     XXXXXXXXXB       XXXXXXXXXXB     XXXXXXXXXXB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 007D17н |                                |              |         | XXXXXXXXB      |  |  |

| O07D1AH Acceptance mask register 1 AMR1 R/W XXXXXXXXXB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 007D18н |                                |              |         |                |  |  |

| 007D1A <sub>H</sub> XXXXXXXX <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 007D19н | Acceptance meak register 4     | AMD4         | DAM     | XXXXXXX        |  |  |

| 007D1Bн XXXXXXXXв                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 007D1Ан | Acceptance mask register 1     | AIVIK I      | F/VV    |                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 007D1Вн | 7                              |              |         | XXXXXXXXB      |  |  |

| Address | Register        | Abbreviation | Access | Initial Value |

|---------|-----------------|--------------|--------|---------------|

| CAN1    | Register        | Abbieviation | Access | mitiai vaide  |

| 007С40н |                 |              |        | XXXXXXXXB     |

| 007С41н | ID register 8   | IDR8         | R/W    | XXXXXXXX      |

| 007С42н | ib register o   | IDINO        | 10,00  | XXXXXXXX      |

| 007С43н |                 |              |        | XXXXXXXXB     |

| 007С44н |                 |              |        | XXXXXXXX      |

| 007С45н | ID register 9   | IDR9         | R/W    | XXXXXXXXB     |

| 007С46н | ib register 9   | IDIN         | 10,00  | XXXXXXXX      |

| 007С47н |                 |              |        | XXXXXXXXB     |

| 007С48н |                 |              |        | XXXXXXXX      |

| 007С49н | ID register 10  | IDR10        | R/W    | XXXXXXXXB     |

| 007С4Ан | ib register to  | ואמו         | N/ VV  | XXXXXXXX      |

| 007С4Вн |                 |              |        | XXXXXXXXB     |

| 007С4Сн |                 |              |        | XXXXXXXX      |

| 007С4Dн | ID register 11  | IDR11        | R/W    | XXXXXXXXB     |

| 007С4Ен |                 | IDKII        |        | XXXXXXXX      |

| 007С4Гн |                 |              |        | XXXXXXXXB     |

| 007С50н |                 |              |        | XXXXXXXXB     |

| 007С51н | ID register 12  | IDR12        | R/W    | XXXXXXXXB     |

| 007С52н | ID register 12  | IDK12        | R/VV   | XXXXXXXX      |

| 007С53н |                 |              |        | XXXXXXXXB     |

| 007С54н |                 |              |        | XXXXXXXXB     |

| 007С55н | ID vaniatov 40  | IDD40        | DAM    | XXXXXXXXB     |

| 007С56н | ID register 13  | IDR13        | R/W    | XXXXXXXXB     |

| 007С57н |                 |              |        | XXXXXXXXB     |

| 007С58н |                 |              |        | XXXXXXXX      |

| 007С59н | ID register 4.4 | IDD44        | D ///  | XXXXXXXXB     |

| 007С5Ан | ID register 14  | IDR14        | R/W    | XXXXXXXX      |

| 007С5Вн |                 |              |        | XXXXXXXXB     |

| 007С5Сн |                 |              |        | XXXXXXXXB     |

| 007С5Dн | ID vanista v 45 | IDDAE        | D ///  | XXXXXXXXB     |

| 007С5Ен | ID register 15  | IDR15        | R/W    | XXXXXXXX      |

| 007С5Гн |                 |              |        | XXXXXXXXB     |

# ■ INTERRUPT FACTORS, INTERRUPT VECTORS, INTERRUPT CONTROL REGISTER

| Interrupt cause               | El <sup>2</sup> OS<br>corre- | DMA ch | Interru | pt vector           |        | ot control<br>ister |  |

|-------------------------------|------------------------------|--------|---------|---------------------|--------|---------------------|--|

| •                             | sponding                     | number | Number  | Address             | Number | Address             |  |

| Reset                         | N                            | _      | #08     | FFFFDCH             | _      | _                   |  |

| INT9 instruction              | N                            | _      | #09     | FFFFD8 <sub>H</sub> | _      |                     |  |

| Exception                     | N                            | _      | #10     | FFFFD4 <sub>H</sub> | _      | _                   |  |

| Reserved                      | N                            | _      | #11     | FFFFD0 <sub>H</sub> | ICDOO  | 000000              |  |

| Reserved                      | N                            | _      | #12     | FFFFCCH             | ICR00  | 0000B0⊦             |  |

| CAN 1 RX / Input Capture 6    | Y1                           | _      | #13     | FFFFC8 <sub>H</sub> | IOD04  | 0000004             |  |

| CAN 1 TX/NS / Input Capture 7 | Y1                           | _      | #14     | FFFFC4 <sub>H</sub> | ICR01  | 0000B1⊦             |  |

| I <sup>2</sup> C              | N                            | _      | #15     | FFFFC0 <sub>H</sub> | IODOO  | 000000              |  |

| Reserved                      | N                            |        | #16     | FFFFBCH             | ICR02  | 0000B2⊦             |  |

| 16-bit Reload Timer 0         | Y1                           | 0      | #17     | FFFFB8 <sub>H</sub> | IODOO  | 000000              |  |

| 16-bit Reload Timer 1         | Y1                           | 1      | #18     | FFFFB4 <sub>H</sub> | ICR03  | 0000B3⊦             |  |

| 16-bit Reload Timer 2         | Y1                           | 2      | #19     | FFFFB0 <sub>H</sub> | IOD04  | 0000004             |  |

| 16-bit Reload Timer 3         | Y1                           | _      | #20     | FFFFAC⊢             | ICR04  | 0000B4⊦             |  |

| PPG 4/5                       | N                            | _      | #21     | FFFFA8⊦             | IODOF  | 00000               |  |

| PPG 6/7                       | N                            | _      | #22     | FFFFA4 <sub>H</sub> | ICR05  | 0000B5⊦             |  |

| PPG 8/9/C/D                   | N                            | _      | #23     | FFFFA0 <sub>H</sub> | IODOG  | 000000              |  |

| PPG A/B/E/F                   | N                            | _      | #24     | FFFF9C <sub>H</sub> | ICR06  | 0000B6⊦             |  |

| Timebase Timer                | N                            | _      | #25     | FFFF98 <sub>H</sub> | 1000-  | 000007              |  |

| External Interrupt 8 to 11    | Y1                           | 3      | #26     | FFFF94 <sub>H</sub> | ICR07  | 0000B7⊦             |  |

| Watch Timer                   | N                            | _      | #27     | FFFF90 <sub>H</sub> | ICDOS  | 000000              |  |

| External Interrupt 12 to 15   | Y1                           | 4      | #28     | FFFF8C <sub>H</sub> | ICR08  | 0000B8⊦             |  |

| A/D Converter                 | Y1                           | 5      | #29     | FFFF88 <sub>H</sub> | IODOO  | 000000              |  |

| I/O Timer 0 / I/O Timer 1     | N                            | _      | #30     | FFFF84 <sub>H</sub> | ICR09  | 0000B9⊦             |  |

| Input Capture 4/5             | Y1                           | 6      | #31     | FFFF80 <sub>H</sub> | IOD40  | 000000              |  |

| Output Compare 4/5            | Y1                           | 7      | #32     | FFFF7C <sub>H</sub> | ICR10  | 0000BA              |  |

| Input Capture 0/1             | Y1                           | 8      | #33     | FFFF78⊦             | ICD44  | 000000              |  |

| Output Compare 6/7            | Y1                           | 9      | #34     | FFFF74 <sub>H</sub> | ICR11  | 0000ВВн             |  |

| Reserved                      | N                            | 10     | #35     | FFFF70⊦             | ICD40  | 000000              |  |

| Reserved                      | N                            | 11     | #36     | FFFF6C <sub>H</sub> | ICR12  | 0000ВСн             |  |

| UART 3 RX                     | Y2                           | 12     | #37     | FFFF68⊦             | IOD40  | 000000              |  |

| UART 3 TX                     | Y1                           | 13     | #38     | FFFF64 <sub>H</sub> | ICR13  | 0000ВДн             |  |

#### (Continued)

- \*1: This parameter is based on Vss = AVss = 0 V

- \*2: Set AVcc and Vcc to the same voltage. Make sure that AVcc does not exceed Vcc and that the voltage at the analog inputs does not exceed AVcc when the power is switched on.