Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

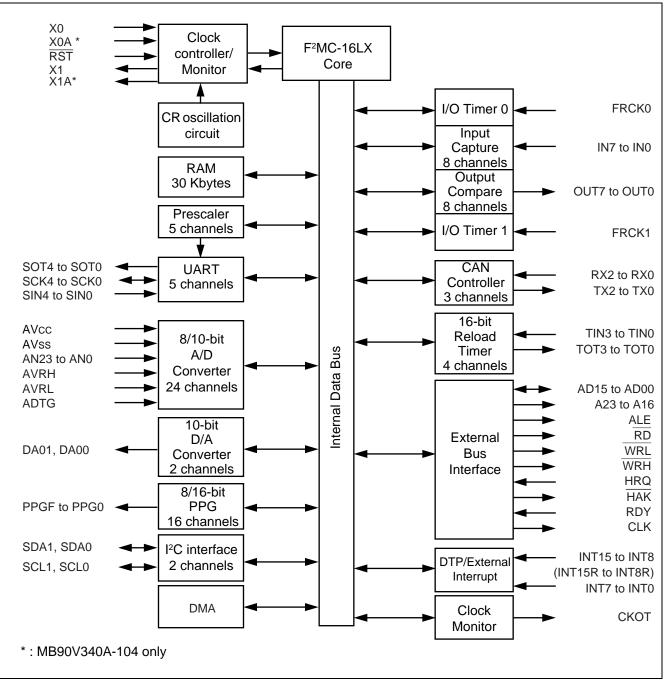

| Core Processor             | F <sup>2</sup> MC-16LX                                                           |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                            |

| Peripherals                | DMA, LVD, POR, WDT                                                               |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 15x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

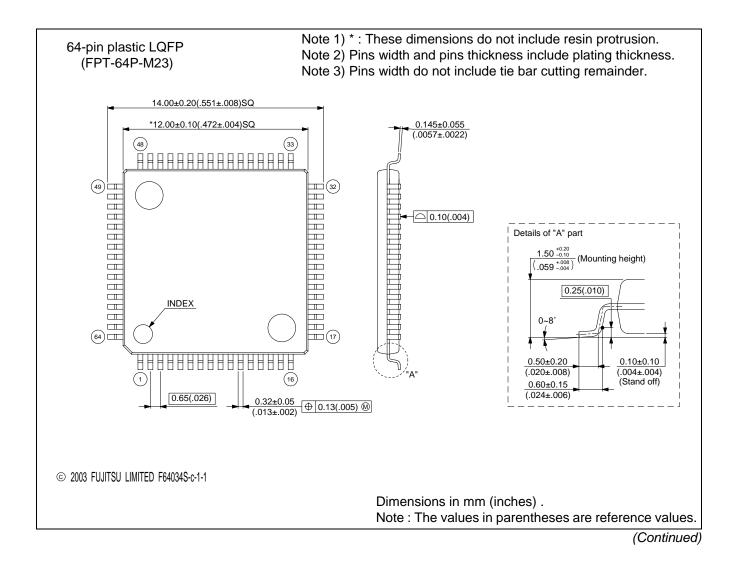

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-QFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f352spfm-gs-121e1 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

(Continued)

| Part Number                     | MB90F351,<br>MB90F352                                                                                                                                                                                                                                                                                                                                                                                                                                     | MB90F351S,<br>MB90F352S                                 | MB90F351A,<br>MB90F352A                                                  | MB90F351TA,<br>MB90F352TA             | MB90F351AS,<br>MB90F352AS                                   | MB90F351TAS,<br>MB90F352TAS |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------|-----------------------------|--|--|

| Parameter                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | MBOOL COEX                                                               |                                       |                                                             |                             |  |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | 6 cha                                                                    | innels                                |                                                             |                             |  |  |

| 16-bit Input Capture            | Retains freerui interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |                                                                          |                                       |                                                             |                             |  |  |

| 8/16-bit                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-bit r                                                 | nannels (16-bit)<br>8-bit reload o<br>eload registers<br>eload registers | counters $\times$ 12 for L pulse wide | th $\times$ 12                                              |                             |  |  |

| Programmable Pulse<br>Generator | 8-bit prescaler<br>Operation cloc                                                                                                                                                                                                                                                                                                                                                                                                                         | reload counters<br>+ 8-bit reload o<br>k frequency : fs | s can be configu<br>counter.                                             | s/2², fsys/2³, fsy                    | bit reload coun<br>/s/2 <sup>4</sup> or 128 μs(<br>equency) |                             |  |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | -                                                                        | annel                                 | ,                                                           |                             |  |  |

| CAN Interface                   | Conforms to CAN Specification Version 2.0 Part A and B.<br>Automatic re-transmission in case of error<br>Automatic transmission responding to Remote Frame<br>Prioritized 16 message buffers for data and ID<br>Supports multiple messages.<br>Flexible configuration of acceptance filtering :<br>Full bit compare/Full bit mask/Two partial bit masks<br>Supports up to 1 Mbps.                                                                         |                                                         |                                                                          |                                       |                                                             |                             |  |  |

|                                 | 8 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |                                                                          |                                       |                                                             |                             |  |  |

| External Interrupt              |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | ng edge, startir<br>ces (El²OS) and                                      |                                       | vel input, extern                                           | al interrupt,               |  |  |

| D/A converter                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | _                                                                        | _                                     |                                                             |                             |  |  |

| I/O Ports                       | Virtually all external pins can be used as general purpose I/O port.<br>All push-pull outputs<br>Bit-wise settable as input/output or peripheral signal<br>Settable as CMOS schmitt trigger/ automotive inputs<br>TTL input level settable for external bus (only for external bus pin)                                                                                                                                                                   |                                                         |                                                                          |                                       |                                                             |                             |  |  |

| Flash Memory                    | Supports automatic programming, Embedded Algorithm <sup>TM*2</sup><br>Write/Erase/Erase-Suspend/Resume commands<br>A flag indicating completion of the algorithm<br>Number of erase cycles : 10,000 times<br>Data retention time : 10 years<br>Boot block configuration<br>Erase can be performed on each block.<br>Block protection with external programming voltage<br>Flash Security Feature for protecting the content of the Flash (MB90F352x only) |                                                         |                                                                          |                                       |                                                             |                             |  |  |

| Corresponding EVA name          | MB90V340A-<br>102                                                                                                                                                                                                                                                                                                                                                                                                                                         | MB90V340A-<br>101                                       | MB90V3                                                                   | 40A-102                               | MB90V3                                                      | 340A-101                    |  |  |

\*1 : It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

\*2 : Embedded Algorithm is a trademark of Advanced Micro Devices Inc.

(Continued)

| Part Number<br>Parameter                    | MB90356A,<br>MB90357A                                                                                                                                                                                                                                                                                                                                                                                   | MB90356TA,<br>MB90357TA         | MB90356AS,<br>MB90357AS                                                | MB90356TAS,<br>MB90357TAS         | MB90V340A-<br>103                                                   | MB90V340A-<br>104                                                                                                              |  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                         | 4 cha                           | innels                                                                 |                                   | 8 cha                                                               | annels                                                                                                                         |  |

| 16-bit Output<br>Compare                    |                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |                                                                        | atches with out<br>enerate an out |                                                                     | egisters.                                                                                                                      |  |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                         | 6 cha                           | innels                                                                 |                                   | 8 cha                                                               | annels                                                                                                                         |  |

| 16-bit Input Capture                        | Retains freerui interrupt.                                                                                                                                                                                                                                                                                                                                                                              | n timer value by                | / (rising edge, fa                                                     | alling edge or ris                | sing & falling ed                                                   | ge), signals an                                                                                                                |  |

| 8/16-bit<br>Programmable Pulse<br>Generator | 8-bit re                                                                                                                                                                                                                                                                                                                                                                                                | 8-bit reload of eload registers | /10 channels (8<br>counters × 12<br>for L pulse wid<br>for H pulse wid | th $\times$ 12                    | nels<br>8-bit reload (<br>8-bit reload<br>L pulse v<br>8-bit reload | 6-bit)/16 chan-<br>(8-bit)<br>counters $\times$ 16<br>registers for<br>vidth $\times$ 16<br>registers for<br>width $\times$ 16 |  |

| Generator                                   | Supports 8-bit and 16-bit operation modes.<br>A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as<br>8-bit prescaler + 8-bit reload counter.<br>Operation clock frequency : fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> or 128 μs@fosc = 4 MHz<br>(fsys = Machine clock frequency, fosc = Oscillation clock frequency) |                                 |                                                                        |                                   |                                                                     |                                                                                                                                |  |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                         | 1 cha                           | annel                                                                  |                                   | 3 cha                                                               | annels                                                                                                                         |  |

| CAN Interface                               | Conforms to CAN Specification Version 2.0 Part A and B.<br>Automatic re-transmission in case of error<br>Automatic transmission responding to Remote Frame<br>Prioritized 16 message buffers for data and ID<br>Supports multiple messages.<br>Flexible configuration of acceptance filtering :<br>Full bit compare/Full bit mask/Two partial bit masks<br>Supports up to 1 Mbps.                       |                                 |                                                                        |                                   |                                                                     |                                                                                                                                |  |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                         | 8 cha                           | innels                                                                 |                                   | 16 ch                                                               | annels                                                                                                                         |  |

| External Interrupt                          |                                                                                                                                                                                                                                                                                                                                                                                                         | 0 0                             | ng edge, startir<br>ces (El²OS) and                                    | ng up by H/L lev<br>I DMA.        | vel input, extern                                                   | al interrupt,                                                                                                                  |  |

| D/A converter                               |                                                                                                                                                                                                                                                                                                                                                                                                         | -                               | _                                                                      |                                   | 2 cha                                                               | annels                                                                                                                         |  |

| I/O Ports                                   | Virtually all external pins can be used as general purpose I/O port.<br>All push-pull outputs<br>Bit-wise settable as input/output or peripheral module signal<br>Settable as CMOS schmitt trigger/ automotive inputs<br>TTL input level settable for external bus (only for external bus pin)                                                                                                          |                                 |                                                                        |                                   |                                                                     |                                                                                                                                |  |

| Flash Memory                                |                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |                                                                        | _                                 |                                                                     |                                                                                                                                |  |

| Corresponding EVA name                      | MB90V3                                                                                                                                                                                                                                                                                                                                                                                                  | 40A-104                         | MB90V3                                                                 | 40A-103                           | _                                                                   |                                                                                                                                |  |

\*: It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

| Pin No.  |               | Circuit |                                                                                                                                               |  |  |  |  |

|----------|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LQFP64*  | Pin name      | type    | Function                                                                                                                                      |  |  |  |  |

|          | P00 to P07    |         | General purpose I/O ports. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode. |  |  |  |  |

| 24 to 31 | AD00 to AD07  | G       | Input/output pins of external address data bus lower 8 bits. This function is enabled when the external bus is enabled.                       |  |  |  |  |

|          | INT8 to INT15 |         | External interrupt request input pins for INT8 to INT15                                                                                       |  |  |  |  |

|          | P10           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 32       | AD08          | G       | Input/output pin for external bus address data bus bit 8.<br>This function is enabled when external bus is enabled.                           |  |  |  |  |

|          | TIN1          |         | Event input pin for reload timer1                                                                                                             |  |  |  |  |

|          | P11           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 33       | 33 AD09       |         | Input/output pin for external bus address data bus bit 9. This function is enabled when external bus is enabled.                              |  |  |  |  |

|          | TOT1          |         | Output pin for reload timer1                                                                                                                  |  |  |  |  |

|          | P12           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 34       | AD10          | Ν       | Input/output pin for external bus address data bus bit 10. This function is enabled when external bus is enabled.                             |  |  |  |  |

| SIN3     |               |         | Serial data input pin for UART3                                                                                                               |  |  |  |  |

|          | INT11R        |         | External interrupt request input pin for INT11                                                                                                |  |  |  |  |

|          | P13           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 35       |               |         | Input/output pin for external bus address data bus bit 11.<br>This function is enabled when external bus is enabled.                          |  |  |  |  |

|          | SOT3          |         | Serial data output pin for UART3                                                                                                              |  |  |  |  |

|          | P14           |         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 36       | AD12          | G       | Input/output pin for external bus address data bus bit 12.<br>This function is enabled when external bus is enabled.                          |  |  |  |  |

|          | SCK3          |         | Clock input/output pin for UART3                                                                                                              |  |  |  |  |

| 37       | P15           | N       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 37 AD13  |               |         | Input/output pin for external bus address data bus bit 13.<br>This function is enabled when external bus is enabled.                          |  |  |  |  |

| 38       | P16           | G       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.  |  |  |  |  |

| 30       | AD14          | 9       | Input/output pin for external bus address data bus bit 14.<br>This function is enabled when external bus is enabled.                          |  |  |  |  |

### HANDLING DEVICES

### Special care is required for the following when handling the device :

- Preventing latch-up

- Treatment of unused pins

- Using external clock

- Precautions for when not using a sub clock signal

- Notes on during operation of PLL clock mode

- Power supply pins (Vcc/Vss)

- Pull-up/down resistors

- Crystal Oscillator Circuit

- Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

- Connection of Unused Pins of A/D Converter

- Notes on Energization

- Stabilization of power supply voltage

- Initialization

- Port0 to port3 output during Power-on (External-bus mode)

- Notes on using CAN Function

- Flash security Function

- Correspondence with  $T_{A}=~+$  105  $^{\circ}C$  or more

- Low voltage/CPU operation detection reset circuit

- Internal CR oscillation circuit

### 1. Preventing latch-up

CMOS IC chips may suffer latch-up under the following conditions :

- A voltage higher than  $V_{\mbox{\scriptsize CC}}$  or lower than  $V_{\mbox{\scriptsize SS}}$  is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between  $V_{\text{CC}}$  pin and  $V_{\text{SS}}$  pin.

- The AV  $\operatorname{cc}$  power supply is applied before the V  $\operatorname{vcc}$  voltage.

Latch-up may increase the power supply current drastically, causing thermal damage to the device.

In using the devices, take sufficient care to avoid exceeding maximum ratings.

For the same reason, also be careful not to let the analog power-supply voltage (AVcc, AVRH) exceed the digital power-supply voltage.

### 2. Handling unused pins

Leaving unused input pins open may result in misbehavior or latch up and possible permanent damage of the device. Therefore they must be pulled up or pulled down through resistors. In this case those resistors should be more than 2 k $\Omega$ .

Unused I/O pins should be set to the output state and can be left open, or the input state with the above described connection.

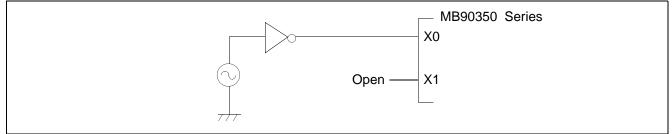

### 3. Using external clock

To use external clock, drive the X0 pin and leave X1 pin open.

### 16. Flash security Function

The security byte is located in the area of the flash memory.

If protection code  $01_{\text{H}}$  is written in the security byte, the flash memory is in the protected state by security. Therefore please do not write  $01_{\text{H}}$  in this address if you do not use the security function. Please refer to following table for the address of the security byte.

|                                                                               | Flash memory size            | Address for security bit |

|-------------------------------------------------------------------------------|------------------------------|--------------------------|

| MB90F352(S)<br>MB90F352A(S)<br>MB90F352TA(S)<br>MB90F357A(S)<br>MB90F357TA(S) | Embedded 1 Mbit Flash Memory | FE0001н                  |

### 17. Correspondence with $T_A = +105 \ ^\circ C$ or more

If used exceeding T<sub>A</sub> = +105 °C, please contact Fujitsu sales representatives for reliability limitations.

#### 18. Low voltage/CPU operation reset circuit

The low voltage detection reset circuit is a function that monitors power supply voltage in order to detect when a voltage drops below a given voltage level. When a low voltage condition is detected, an internal reset signal is generated.

The CPU operation detection reset circuit is a 20-bit counter that uses oscillation as a count clock and generates an internal reset signal if not cleared within a given time after startup.

#### (1) Low voltage detection reset circuit

| Detection voltage             | ÷ |

|-------------------------------|---|

| $4.0~\text{V}\pm0.3~\text{V}$ |   |

When a low voltage condition is detected, the low voltage detection flag (LVRC : LVRF) is set to "1" and an internal reset signal is output.

Because the low voltage detection reset circuit continues to operate even in stop mode, detection of a low voltage condition generates an internal reset and releases stop mode.

During an internal RAM write cycle, low voltage reset is generated after the completion of writing. During the output of this internal reset, the reset output from the low voltage detection reset circuit is suppressed.

#### (2) CPU operation detection reset circuit

The CPU operation detection reset circuit is a counter that prevents program runaway. The counter starts automatically after a power-on reset, and must be continually cleared within a given time. If the given time interval elapses and the counter has not been cleared, a cause such as infinite program looping is assumed and an internal reset signal is generated. The internal reset generated from the CPU operation detection circuit has a width of 5 machine cycles.

| Interval time            |  |  |  |  |

|--------------------------|--|--|--|--|

| 220/Fc (approx. 262 ms*) |  |  |  |  |

\* : This value assumes the interval time at an oscillation clock frequency of 4 MHz. During recovery from standby mode, the detection period is the maximum interval plus 20 μs.

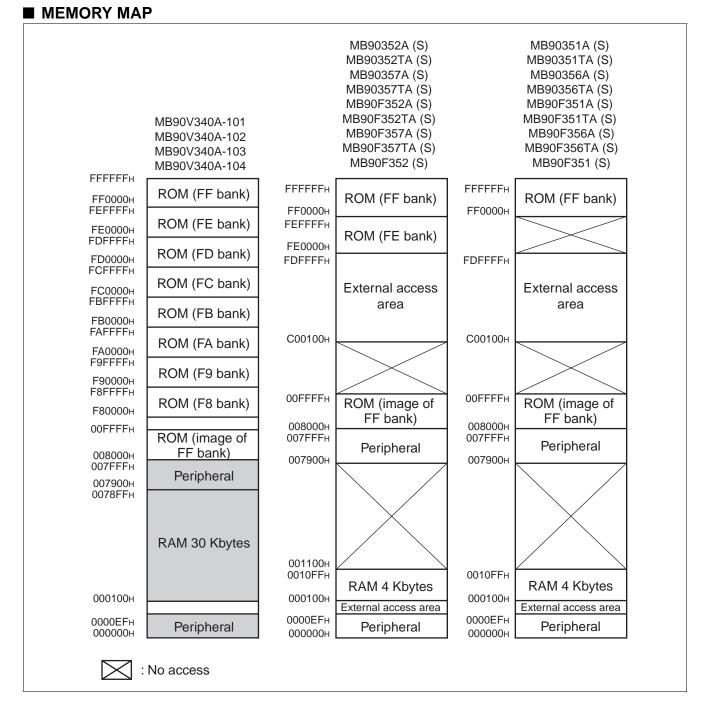

#### • MB90V340A-103/104

Note : The high-order portion of bank 00 gives the image of the FF bank ROM to make the small model of the C compiler effective. Since the low-order 16 bits are the same, the table in ROM can be referenced without using the far specification in the pointer declaration.

For example, an attempt to access 00C000H accesses the value at FFC000H in ROM.

The ROM area in bank FF exceeds 32 Kbytes, and its entire image cannot be shown in bank 00.

The image between FF8000 $\mu$  and FFFFF $\mu$  is visible in bank 00, while the image between FF0000 $\mu$  and FF7FFF $\mu$  is visible only in bank FF.

| Address           | Register                 | Abbrevia-<br>tion | Access | Resource name                | Initial value |

|-------------------|--------------------------|-------------------|--------|------------------------------|---------------|

| <b>7908</b> н     | Reload Register L4       | PRLL4             | R/W    |                              | XXXXXXXXB     |

| <b>7909</b> н     | Reload Register H4       | PRLH4             | R/W    | 16-bit Programmable          | XXXXXXXXB     |

| <b>790А</b> н     | Reload Register L5       | PRLL5             | R/W    | Pulse<br>Generator 4/5       | XXXXXXXXB     |

| <b>7</b> 90Вн     | Reload Register H5       | PRLH5             | R/W    |                              | XXXXXXXXB     |

| <b>790С</b> н     | Reload Register L6       | PRLL6             | R/W    |                              | XXXXXXXXB     |

| <b>790D</b> н     | Reload Register H6       | PRLH6             | R/W    | 16-bit Programmable<br>Pulse | XXXXXXXXB     |

| <b>790Е</b> н     | Reload Register L7       | PRLL7             | R/W    | Generator 6/7                | XXXXXXXXB     |

| <b>790F</b> н     | Reload Register H7       | PRLH7             | R/W    |                              | XXXXXXXXB     |

| <b>7910</b> н     | Reload Register L8       | PRLL8             | R/W    |                              | XXXXXXXAB     |

| <b>7911</b> н     | Reload Register H8       | PRLH8             | R/W    | 16-bit Programmable          | XXXXXXXXB     |

| 7912н             | Reload Register L9       | PRLL9             | R/W    | Pulse<br>Generator 8/9       | XXXXXXXXB     |

| 7913н             | Reload Register H9       | PRLH9             | R/W    |                              | XXXXXXXXB     |

| <b>7914</b> н     | Reload Register LA       | PRLLA             | R/W    |                              | XXXXXXXXB     |

| <b>7915</b> н     | Reload Register HA       | PRLHA             | R/W    | 16-bit Programmable          | XXXXXXXXB     |

| <b>7916</b> н     | Reload Register LB       | PRLLB             | R/W    | Pulse<br>Generator A/B       | XXXXXXXXB     |

| <b>7917</b> н     | Reload Register HB       | PRLHB             | R/W    |                              | XXXXXXXXB     |

| <b>7918</b> н     | Reload Register LC       | PRLLC             | R/W    |                              | XXXXXXXAB     |

| <b>7919</b> н     | Reload Register HC       | PRLHC             | R/W    | 16-bit Programmable          | XXXXXXXXB     |

| <b>791А</b> н     | Reload Register LD       | PRLLD             | R/W    | Pulse<br>Generator C/D       | XXXXXXXXB     |

| <b>791B</b> н     | Reload Register HD       | PRLHD             | R/W    |                              | XXXXXXXXB     |

| <b>791C</b> н     | Reload Register LE       | PRLLE             | R/W    |                              | XXXXXXXXB     |

| <b>791D</b> н     | Reload Register HE       | PRLHE             | R/W    | 16-bit Programmable          | XXXXXXXXB     |

| <b>791Е</b> н     | Reload Register LF       | PRLLF             | R/W    | Pulse<br>Generator E/F       | XXXXXXXXB     |

| 791F⊦             | Reload Register HF       | PRLHF             | R/W    |                              | XXXXXXXXB     |

| <b>7920</b> н     | Input Capture Register 0 | IPCP0             | R      |                              | XXXXXXXXB     |

| <b>7921</b> н     | Input Capture Register 0 | IPCP0             | R      |                              | XXXXXXXXB     |

| <b>7922</b> н     | Input Capture Register 1 | IPCP1             | R      | Input Capture 0/1            | XXXXXXXXB     |

| 7923н             | Input Capture Register 1 | IPCP1             | R      |                              | XXXXXXXXB     |

| 7924н to<br>7927н |                          | Reserv            | red    | 1                            | ł             |

| <b>7928</b> н     | Input Capture Register 4 | IPCP4             | R      |                              | XXXXXXXXB     |

| 7929н             | Input Capture Register 4 | IPCP4             | R      |                              | XXXXXXXXB     |

| <b>792А</b> н     | Input Capture Register 5 | IPCP5             | R      | Input Capture 4/5            | XXXXXXX       |

| <b>7</b> 92Вн     | Input Capture Register 5 | IPCP5             | R      | 1                            | XXXXXXXXB     |

| Address           | Register                             | Abbrevia-<br>tion | Access | Resource name      | Initial value |

|-------------------|--------------------------------------|-------------------|--------|--------------------|---------------|

| <b>792С</b> н     | Input Capture Register 6             | IPCP6             | R      |                    | XXXXXXXX      |

| <b>792D</b> н     | Input Capture Register 6             | IPCP6             | R      | Input Conturo 6/7  | XXXXXXXX      |

| <b>792Е</b> н     | Input Capture Register 7             | IPCP7             | R      | Input Capture 6/7  | XXXXXXXX      |

| <b>792F</b> н     | Input Capture Register 7             | IPCP7             | R      |                    | XXXXXXXX      |

| 7930н to<br>7937н |                                      | Reserve           | ed     |                    |               |

| <b>7938</b> н     | Output Compare Register 4            | OCCP4             | R/W    |                    | XXXXXXXX      |

| <b>7939</b> н     | Output Compare Register 4            | OCCP4             | R/W    | Output Compore 4/5 | XXXXXXXX      |

| 793Ан             | Output Compare Register 5            | OCCP5             | R/W    | Output Compare 4/5 | XXXXXXXX      |

| <b>793В</b> н     | Output Compare Register 5            | OCCP5             | R/W    |                    | XXXXXXXX      |

| 793Сн             | Output Compare Register 6            | OCCP6             | R/W    |                    | XXXXXXXX      |

| <b>793D</b> н     | Output Compare Register 6            | OCCP6             | R/W    | Output Compore 6/7 | XXXXXXXX      |

| <b>793Е</b> н     | Output Compare Register 7            | OCCP7             | R/W    | Output Compare 6/7 | XXXXXXXX      |

| <b>793F</b> н     | Output Compare Register 7            | OCCP7             | R/W    |                    | XXXXXXXX      |

| <b>7940</b> н     | Timer Data Register 0                | TCDT0             | R/W    |                    | 0000000в      |

| <b>7941</b> н     | Timer Data Register 0                | TCDT0             | R/W    | I/O Timer 0        | 0000000в      |

| <b>7942</b> н     | Timer Control Status Register 0      | TCCSL0            | R/W    |                    | 0000000в      |

| 7943н             | Timer Control Status Register 0      | TCCSH0            | R/W    |                    | 0XXXXXXX      |

| <b>7944</b> н     | Timer Data Register 1                | TCDT1             | R/W    |                    | 0000000в      |

| <b>7945</b> н     | Timer Data Register 1                | TCDT1             | R/W    | I/O Timer 1        | 0000000в      |

| <b>7946</b> н     | Timer Control Status Register 1      | TCCSL1            | R/W    |                    | 0000000в      |

| <b>7947</b> н     | Timer Control Status Register 1      | TCCSH1            | R/W    |                    | 0XXXXXXXB     |

| <b>7948</b> н     | Timer Degister 0/Delead Degister 0   | TMR0/             | R/W    | 16-bit Reload      | XXXXXXXX      |

| <b>7949</b> н     | - Timer Register 0/Reload Register 0 | TMRLR0            | R/W    | Timer 0            | XXXXXXXX      |

| 794Ан             | Timer Degister 1/Delead Degister 1   | TMR1/             | R/W    | 16-bit Reload      | XXXXXXXX      |

| <b>794В</b> н     | - Timer Register 1/Reload Register 1 | TMRLR1            | R/W    | Timer 1            | XXXXXXXX      |

| <b>794С</b> н     | Timer Degister 2/Delead Degister 2   | TMR2/             | R/W    | 16-bit Reload      | XXXXXXXX      |

| <b>794D</b> н     | - Timer Register 2/Reload Register 2 | TMRLR2            | R/W    | Timer 2            | XXXXXXXX      |

| <b>794Е</b> н     | Timer Degister 2/Delead Degister 2   | TMR3/             | R/W    | 16-bit Reload      | XXXXXXXX      |

| <b>794F</b> н     | Timer Register 3/Reload Register 3   | TMRLR3            | R/W    | Timer 3            | XXXXXXXX      |

### ■ CAN CONTROLLERS

The CAN controller has the following features :

- Conforms to CAN Specification Version 2.0 Part A and B

- Supports transmission/reception in standard frame and extended frame formats

- · Supports transmitting of data frames by receiving remote frames

- 16 transmitting/receiving message buffers

- 29-bit ID and 8-byte data

- Multi-level message buffer configuration

- Provides full-bit comparison, full-bit mask, acceptance register 0/acceptance register 1 for each message buffer as ID acceptance mask

- Two acceptance mask registers in either standard frame format or extended frame formats

- Bit rate programmable from 10 Kbps to 2 Mbps (when input clock is at 16 MHz)

| Address | Persister                         | Abbreviation                  | Access | Initial Value |  |

|---------|-----------------------------------|-------------------------------|--------|---------------|--|

| CAN1    | Register                          | Appreviation                  | Access |               |  |

| 000080н | Message buffer enable register    | BVALR                         | R/W    | 0000000в      |  |

| 000081н | message builer enable register    | DVALIN                        | 12/ 77 | 0000000в      |  |

| 000082н | Transmit request register         | TREQR                         | R/W    | 0000000в      |  |

| 000083н | Transmit request register         | INEQN                         | 12/00  | 0000000в      |  |

| 000084н | Transmit cancel register          | TCANR                         | W      | 0000000в      |  |

| 000085н | Hansmit cancer register           | TOAIN                         | vv     | 0000000в      |  |

| 000086н | Transmission complete register    | TCR                           | R/W    | 0000000в      |  |

| 000087н | Tansmission complete register     | TOR                           | 10/00  | 0000000в      |  |

| 000088н | Receive complete register         | Receive complete register RCR | R/W    | 0000000в      |  |

| 000089н |                                   | Kok                           |        | 0000000в      |  |

| 00008Ан | Remote request receiving register | RRTRR                         | R/W    | 0000000в      |  |

| 00008Вн | Remote request receiving register |                               |        | 0000000в      |  |

| 00008Сн | Receive overrun register          | ROVRR                         | R/W    | 0000000в      |  |

| 00008Dн | Receive overfull register         | NOVIN                         |        | 0000000в      |  |

| 00008Eн | Reception interrupt               | RIER                          | R/W    | 0000000в      |  |

| 00008Fн | enable register                   |                               | 10,00  | 0000000в      |  |

### List of Control Registers

| Address         | Dogistar        |                  | A       | In Heal Malue                          |  |

|-----------------|-----------------|------------------|---------|----------------------------------------|--|

| CAN1            | Register        | Abbreviation     | Access  | Initial Value                          |  |

| 007С60н         | DLC register 0  | DLCR0            | R/W     | XXXXXXXXB                              |  |

| 007C61н         | DLC register 0  | DLCRU            |         | ллллллв                                |  |

| 007С62н         | DLC register 1  | DLCR1            | R/W     | XXXXXXXXB                              |  |

| <b>007С63</b> н | DEC legister 1  | DEGICI           | 10/00   | ЛЛЛЛЛЛВ                                |  |

| 007C64н         | DLC register 2  | DLCR2            | R/W     | XXXXXXXX <sub>B</sub>                  |  |

| <b>007С65</b> н | DEC legister 2  | DEGIZ            | 10/00   | ЛЛЛЛЛЛВ                                |  |

| <b>007С66</b> н | DLC register 3  | DLCR3            | R/W     | XXXXXXXX <sub>B</sub>                  |  |

| <b>007С67</b> н | DEC legister 5  | DEGRO            | 10/00   | ЛЛЛЛЛЛВ                                |  |

| <b>007С68</b> н | DLC register 4  | DLCR4            | R/W     | XXXXXXXX <sub>B</sub>                  |  |

| 007C69н         | DLC Tegister 4  | DLCR4            |         | ллллллв                                |  |

| 007С6Ан         | DLC register 5  | DLCR5            | R/W     | VVVVVVV <sub>2</sub>                   |  |

| 007C6Bн         | DLC register 5  | DLORG            |         | XXXXXXXXB                              |  |

| 007С6Сн         | DLC register 6  | DLCR6            | R/W     | XXXXXXXXB                              |  |

| 007C6Dн         | DEC legister o  | DEGRO            | 10/00   | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |  |

| 007С6Ен         | DLC register 7  | gister 7 DLCR7 I | R/W     | XXXXXXXX                               |  |

| 007C6Fн         | DLC Tegister 7  | DLCKI            |         | ХХХХХХХХХВ                             |  |

| 007С70н         | DLC register 8  | DLCR8            | R/W     | XXXXXXXX <sub>B</sub>                  |  |

| <b>007C71</b> н | DLC register o  | DLCRO            |         | ллллллв                                |  |

| 007С72н         | DLC register 9  | DLCR9            | R/W     | XXXXXXXXB                              |  |

| 007С73н         | DLC register 9  | DLONG            | 10/00   | АЛАЛАЛАВ                               |  |

| 007C74н         | DLC register 10 | DLCR10           | R/W     | XXXXXXXXB                              |  |

| 007C75н         | DEC legister 10 | DECKIO           |         | <b>VVVVVVV</b> R                       |  |

| 007С76н         | DLC register 11 | DLCR11           | R/W     | XXXXXXXX                               |  |

| <b>007С77</b> н | DLC register 11 | DLOKTI           |         | <b>VVVVVVV</b> R                       |  |

| 007С78н         | DLC register 12 | DLCR12           | R/W     | XXXXXXXXB                              |  |

| <b>007С79</b> н | DEC register 12 | DEGITZ           | 10/00   | лллллллв                               |  |

| 007С7Ан         | DLC register 13 | DLCR13           | R/W     | XXXXXXXXB                              |  |

| 007С7Вн         |                 | DEGRIS           |         | AAAAAAAAB                              |  |

| 007С7Сн         | DLC register 14 | DLCR14           | R/W     | XXXXXXXXB                              |  |

| 007C7Dн         | DEC TEGISIEL 14 | DLGR14           | FX/ V V | лллллллв                               |  |

| 007С7Ен         | DLC register 15 |                  | R/W     | YYYYYYYY <sub>2</sub>                  |  |

| 007C7Fн         | DLC register 15 | DLCR15           | r./ VV  | XXXXXXXXB                              |  |

## List of Message Buffers (DLC Registers and Data Registers)

### (Continued)

| Interrupt cause   | El <sup>2</sup> OS<br>corre-<br>DMA ch |        | Interrupt vector |         | Interrupt control register |         |

|-------------------|----------------------------------------|--------|------------------|---------|----------------------------|---------|

|                   | sponding                               | number | Number           | Address | Number                     | Address |

| UART 2 RX         | Y2                                     | 14     | #39              | FFFF60⊦ | ICR14                      | 0000BEH |

| UART 2 TX         | Y1                                     | 15     | #40              | FFFF5CH |                            | UUUUDEH |

| Flash Memory      | N                                      |        | #41              | FFFF58⊦ | ICR15                      | 0000BFн |

| Delayed interrupt | N                                      |        | #42              | FFFF54⊦ | 10115                      | UUUUDFH |

Y1 : Usable

Y2 : Usable, with EI2OS stop function

N : Unusable

Notes : • The peripheral resources sharing the ICR register have the same interrupt level.

- When two peripheral resources share the ICR register, only one can use El<sup>2</sup>OSat a time.

- When either of the two peripheral resources sharing the ICR register specifies EI<sup>2</sup>OS, the other one cannot use interrupts.

### 4. AC Characteristics

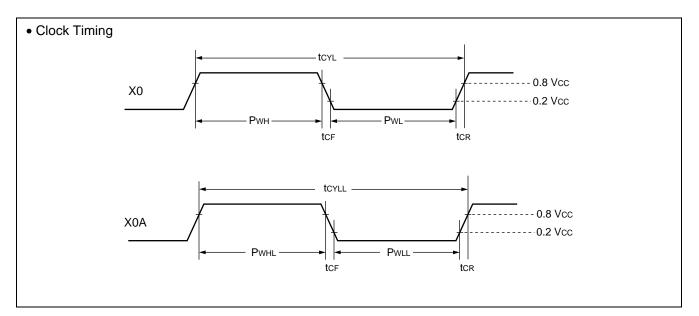

### (1) Clock Timing

| (MB90F352(S)/N                 | /IB90F351(    | Ś): T <sub>A</sub> = −40 | °C to + | 125 °C, ∖ | /cc = 5.0 | $V \pm 10^{\circ}$ | %, fcP ≤ 24 MHZ, Vss = AVss = 0 V<br>%, fcP ≤ 16 MHZ, Vss = AVss = 0 V<br>%, fcP ≤ 24 MHZ, Vss = AVss = 0 V |  |

|--------------------------------|---------------|--------------------------|---------|-----------|-----------|--------------------|-------------------------------------------------------------------------------------------------------------|--|

|                                |               |                          | Value   |           |           |                    |                                                                                                             |  |

| Parameter                      | Symbol        | Pin                      | Min     | Тур       | Мах       | Unit               | Remarks                                                                                                     |  |

|                                |               |                          | 3       |           | 16        | MHz                | 1/2 (at PLL stop)<br>When using an oscillation circuit                                                      |  |

|                                |               |                          | 4       |           | 16        | MHz                | 1 multiplied PLL<br>When using an oscillation circuit                                                       |  |

|                                |               | X0, X1                   | 4       |           | 12        | MHz                | 2 multiplied PLL<br>When using an oscillation circuit                                                       |  |

|                                |               | λ0, λ1                   | 4       |           | 8         | MHz                | 3 multiplied PLL<br>When using an oscillation circuit                                                       |  |

|                                |               |                          | 4       |           | 6         | MHz                | 4 multiplied PLL<br>When using an oscillation circuit                                                       |  |

|                                | fc            |                          |         |           | 4         | MHz                | 6 multiplied PLL<br>When using an oscillation circuit                                                       |  |

| Clock frequency                |               | XO                       | 3       |           | 24        | MHz                | 1/2 (at PLL stop),<br>When using an external clock                                                          |  |

|                                |               |                          | 4       |           | 24        | MHz                | 1 multiplied PLL<br>When using an external clock                                                            |  |

|                                |               |                          | 4       |           | 12        | MHz                | 2 multiplied PLL<br>When using an external clock                                                            |  |

|                                |               |                          | 4       |           | 8         | MHz                | 3 multiplied PLL<br>When using an external clock                                                            |  |

|                                |               |                          | 4       | _         | 6         | MHz                | 4 multiplied PLL<br>When using an external clock                                                            |  |

|                                |               |                          |         |           | 4         | MHz                | 6 multiplied PLL<br>When using an external clock                                                            |  |

|                                | fc∟           | X0A, X1A                 |         | 32.768    | 100       | kHz                |                                                                                                             |  |

|                                | tcy∟          | X0, X1                   | 62.5    |           | 333       | ns                 | When using an oscillation circuit                                                                           |  |

| Clock cycle time               | LOTL          | X0                       | 41.67   | —         | 333       | ns                 | When using an external clock                                                                                |  |

|                                | <b>t</b> CYLL | X0A, X1A                 | 10      | 30.5      |           | μs                 |                                                                                                             |  |

| Input clock pulse width        | Pwh, Pwl      | X0                       | 10      |           |           | ns                 | Duty ratio is about 30% to 70%.                                                                             |  |

|                                | PWHL, PWLL    | X0A                      | 5       | 15.2      |           | μs                 |                                                                                                             |  |

| Input clock rise and fall time | tcr, tcr      | X0                       |         |           | 5         | ns                 | When using an external clock                                                                                |  |

|                                |               |                          |         |           |           |                    | (Continued                                                                                                  |  |

$(MB90F352(S)/MB90F351(S): T_A = -40 \text{ °C to } +105 \text{ °C}, V_{CC} = 5.0 \text{ V} \pm 10\%, f_{CP} \le 24 \text{ MHz}, V_{SS} = AV_{SS} = 0 \text{ V})$

(Continued)

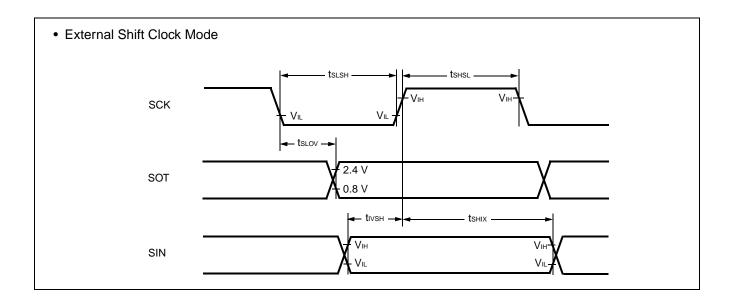

$\begin{array}{l} (MB90F352(S)/MB90F351(S): T_{A} = -40 \ ^{\circ}C \ to +105 \ ^{\circ}C, \ V_{Cc} = 5.0 \ V \pm 10\%, \ f_{CP} \leq 24 \ MHz, \ V_{SS} = AV_{SS} = 0 \ V) \\ (MB90F352(S)/MB90F351(S): T_{A} = -40 \ ^{\circ}C \ to +125 \ ^{\circ}C, \ V_{Cc} = 5.0 \ V \pm 10\%, \ f_{CP} \leq 16 \ MHz, \ V_{SS} = AV_{SS} = 0 \ V) \\ (Device \ other \ than \ above: T_{A} = -40 \ ^{\circ}C \ to +125 \ ^{\circ}C, \ V_{Cc} = 5.0 \ V \pm 10\%, \ f_{CP} \leq 24 \ MHz, \ V_{SS} = AV_{SS} = 0 \ V) \\ \end{array}$

| Parameter                                                 | Symbol       | Pin   |       | Value |     | Unit | Remarks                                                                                                                |

|-----------------------------------------------------------|--------------|-------|-------|-------|-----|------|------------------------------------------------------------------------------------------------------------------------|

| Farameter                                                 | Symbol       | E III | Min   | Тур   | Мах | Unit | iteliidi kõ                                                                                                            |

|                                                           |              |       | 1.5   |       | 24  | MHz  | $\begin{array}{l} MB90F352/(S), \ MB90F351/(S)\\ When \ using \ main \ clock\\ (T_A \leq +105 \ ^\circ C) \end{array}$ |

| Internal operating<br>clock frequency<br>(machine clock)  | fср          |       | 1.5   |       | 16  |      | $\begin{array}{l} MB90F352/(S),\ MB90F351/(S)\\ When using main clock\\ (T_{A}\leq +125\ ^{\circ}C) \end{array}$       |

|                                                           |              |       | 1.5   |       | 24  | MHz  | Device other than above,<br>When using main clock                                                                      |

|                                                           | fcpl         |       |       | 8.192 | 50  | kHz  | When using sub clock                                                                                                   |

| Internal operating<br>clock cycle time<br>(machine clock) | tcp          |       | 41.67 | 66    | 666 | ns   | $\begin{array}{l} MB90F352/(S),\ MB90F351/(S)\\ When\ using\ main\ clock\\ (T_A \leq +105\ ^{\circ}C) \end{array}$     |

|                                                           |              |       | 62.5  |       | 000 | 115  | $\begin{array}{l} MB90F352/(S),\ MB90F351/(S)\\ When\ using\ main\ clock\\ (T_A \leq +125\ ^{\circ}C) \end{array}$     |

|                                                           |              |       | 41.67 |       | 666 | ns   | Device other than above,<br>When using main clock                                                                      |

|                                                           | <b>t</b> CPL |       | 20    | 122.1 | —   | μs   | When using sub clock                                                                                                   |

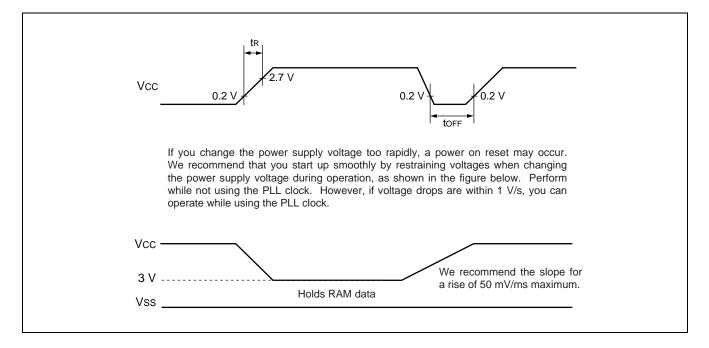

### (3) Power On Reset

$\begin{array}{l} (MB90F352(S)/MB90F351(S): \ T_{A} = -40 \ ^{\circ}C \ to \ +105 \ ^{\circ}C, \ V_{CC} = 5.0 \ V \pm 10\%, \ f_{CP} \leq 24 \ MHz, \ V_{SS} = AV_{SS} = 0 \ V) \\ (MB90F352(S)/MB90F351(S): \ T_{A} = -40 \ ^{\circ}C \ to \ +125 \ ^{\circ}C, \ V_{CC} = 5.0 \ V \pm 10\%, \ f_{CP} \leq 16 \ MHz, \ V_{SS} = AV_{SS} = 0 \ V) \\ (Device \ other \ than \ above: \ T_{A} = -40 \ ^{\circ}C \ to \ +125 \ ^{\circ}C, \ V_{CC} = 5.0 \ V \pm 10\%, \ f_{CP} \leq 24 \ MHz, \ V_{SS} = AV_{SS} = 0 \ V) \\ \end{array}$

| Parameter          | Symbol Pin |      | Condition | Va   | lue | Unit | Remarks                     |  |

|--------------------|------------|------|-----------|------|-----|------|-----------------------------|--|

| Farameter          | Symbol     | EIII | Condition | Min  | Max | Unit | iveingi ka                  |  |

| Power on rise time | tR         | Vcc  |           | 0.05 | 30  | ms   |                             |  |

| Power off time     | toff       | Vcc  |           | 1    |     | ms   | Due to repetitive operation |  |

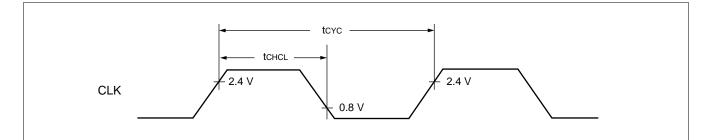

(4) Clock Output Timing

$(T_A = -40 \text{ °C to } +105 \text{ °C}, V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ Vss} = 0.0 \text{ V}, f_{CP} \le 24 \text{ MHz})$

| Parameter                                     | Symbol | Pin | Condition | Value |     | Unit | Remarks      |

|-----------------------------------------------|--------|-----|-----------|-------|-----|------|--------------|

| Farameter                                     | Symbol |     |           | Min   | Max | Onit | itemarks     |

| Cycle time                                    |        | CLK | _         | 62.5  | _   | ns   | fcp = 16 MHz |

| Cycle time tcyc                               | LCYC   |     |           | 41.76 | _   | ns   | fcp = 24 MHz |

| $CLK \uparrow \rightarrow CLK \downarrow$ top | touo   | CLK |           | 20    | _   | ns   | fcp = 16 MHz |

|                                               | ICHCL  | OLK |           | 13    |     | ns   | fcp = 24 MHz |

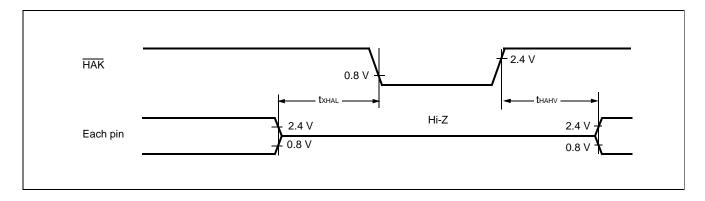

### (8) Hold Timing

(T\_A = -40°C to +105°C, V\_{\rm CC} = 5.0 V  $\pm$  10 %, V\_{\rm SS} = 0.0 V, f\_{\rm CP} \leq 24 MHz)

| Parameter                                                                          | Symbol Pin    |     | Condition | Va          | lue   | Units | Remarks |

|------------------------------------------------------------------------------------|---------------|-----|-----------|-------------|-------|-------|---------|

| Farameter                                                                          | Symbol        | ГШ  | Condition | Min         | Мах   | Units | Remarks |

| Pin floating $\Rightarrow \overline{\text{HAK}} \downarrow$ time                   | <b>t</b> xhal | HAK |           | 30          | tcp   | ns    |         |

| $\frac{\text{HAK}}{\text{time}} \uparrow \text{time} \Rightarrow \text{Pin valid}$ | <b>t</b> hah∨ | HAK |           | <b>t</b> CP | 2 tcp | ns    |         |

Note : There is more than 1 machine cycle from when HRQ pin reads in until the  $\overline{HAK}$  is changed.

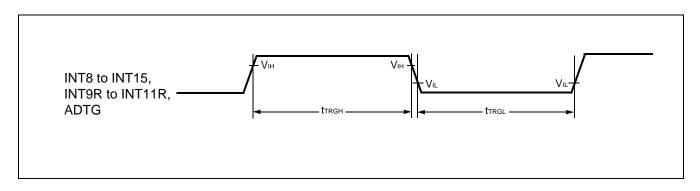

#### (10) Trigger Input Timing

$\begin{array}{l} (MB90F352(S)/MB90F351(S): T_{A} = -40 \ ^{\circ}C \ to \ +105 \ ^{\circ}C, \ Vcc = 5.0 \ V \pm 10\%, \ f_{CP} \leq 24 \ MHz, \ Vss = AV_{SS} = 0 \ V) \\ (MB90F352(S)/MB90F351(S): T_{A} = -40 \ ^{\circ}C \ to \ +125 \ ^{\circ}C, \ Vcc = 5.0 \ V \pm 10\%, \ f_{CP} \leq 16 \ MHz, \ Vss = AV_{SS} = 0 \ V) \\ (Device \ other \ than \ above: T_{A} = -40 \ ^{\circ}C \ to \ +125 \ ^{\circ}C, \ Vcc = 5.0 \ V \pm 10\%, \ f_{CP} \leq 24 \ MHz, \ Vss = AV_{SS} = 0 \ V) \\ \end{array}$

| Parameter         | Symbol Pin     |                                            | Condition | Val   | ue  | Unit | Remarks  |

|-------------------|----------------|--------------------------------------------|-----------|-------|-----|------|----------|

| Farameter         | Symbol         | FIII                                       | Condition |       | Max | Unit | itema ka |

| Input pulse width | ttrgh<br>ttrgl | INT8 to INT15,<br>INT9R to INT11R,<br>ADTG | _         | 5 tcp |     | ns   |          |

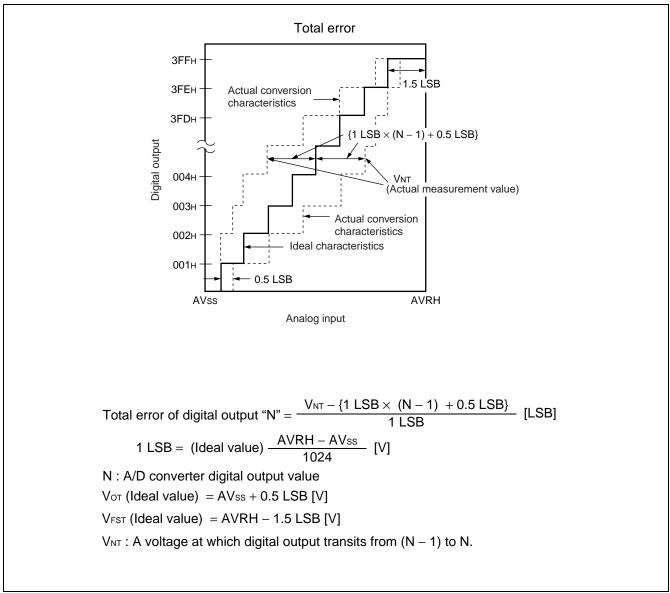

### 6. Definition of A/D Converter Terms

| Resolution                      | : Analog variation that is recognized by an A/D converter.                                                                                                                                                                                         |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non linearity<br>error          | : Deviation between a line across zero-transition line ( "00 0000 0000" $\leftarrow \rightarrow$ "00 0000 0001" ) and full-scale transition line ( "11 1111 1110" $\leftarrow \rightarrow$ "11 1111 1111" ) and actual conversion characteristics. |

| Differential<br>linearity error | : Deviation of input voltage, which is required for changing output code by 1 LSB, from an ideal value.                                                                                                                                            |

| Total error                     | : Difference between an actual value and a theoretical value. A total error includes zero tran-<br>sition error, full-scale transition error, and linear error.                                                                                    |

### 7. Flash Memory Program/Erase Characteristics

Flash Memory

| Parameter                               | Conditions                                                                                         |        | Value |       | Unit  | Remarks                                          |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|--------|-------|-------|-------|--------------------------------------------------|--|

| Falailletei                             | Conditions                                                                                         | Min    | Тур   | Max   | Onit  | Remarks                                          |  |

| Sector erase time                       |                                                                                                    | _      | 1     | 15    | S     | Excludes programming prior to erasure            |  |

| Chip erase time                         | $\begin{array}{l} T_{\text{A}}=+25 \ ^{\circ}\text{C} \\ V_{\text{CC}}=5.0 \ \text{V} \end{array}$ | _      | 9     | —     | S     | Excludes programming prior to erasure            |  |

| Word (16-bit width)<br>programming time |                                                                                                    | _      | 16    | 3,600 | μs    | Except for the overhead time of the system level |  |

| Program/Erase cycle                     |                                                                                                    | 10,000 | _     |       | cycle |                                                  |  |

| Flash Memory Data<br>Retention Time     | Average<br>T <sub>A</sub> = +85 °C                                                                 | 20     |       |       | year  | *                                                |  |

\* : This value comes from the technology qualification. (Using Arrhenius equation to translate high temperature measurements into normalized value at +85 °C)

**Dual Operation Flash Memory**

| Parameter                               | Conditions                         |        | Value |       | Unit  | Remarks                                          |  |

|-----------------------------------------|------------------------------------|--------|-------|-------|-------|--------------------------------------------------|--|

| raiaineter                              | Conditions                         | Min    | Тур   | Max   | Onit  | Reliidiks                                        |  |

| Sector erase time<br>(4 Kbytes sector)  |                                    | _      | 0.2   | 0.5   | S     | Excludes programming prior to erasure            |  |

| Sector erase time<br>(16 Kbytes sector) | T <sub>A</sub> = +25 °C            | _      | 0.5   | 7.5   | S     | Excludes programming prior to erasure            |  |

| Chip erase time                         | Vcc = 5.0 V                        | _      | 4.6   |       | S     | Excludes programming prior to erasure            |  |

| Word (16-bit width)<br>programming time |                                    | _      | 64    | 3,600 | μs    | Except for the overhead time of the system level |  |

| Program/Erase cycle                     |                                    | 10,000 |       |       | cycle |                                                  |  |

| Flash Memory Data<br>Retention Time     | Average<br>T <sub>A</sub> = +85 °C | 20     |       |       | year  | *                                                |  |

\* : This value comes from the technology qualification.

(Using Arrhenius equation to translate high temperature measurements into normalized value at +85 °C)