Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 147456                                                         |

| Number of I/O                  | 154                                                            |

| Number of Gates                | 1000000                                                        |

| Voltage - Supply               | 1.14V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                |

| Package / Case                 | 208-BFQFP                                                      |

| Supplier Device Package        | 208-PQFP (28x28)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p1000l-1pq208 |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

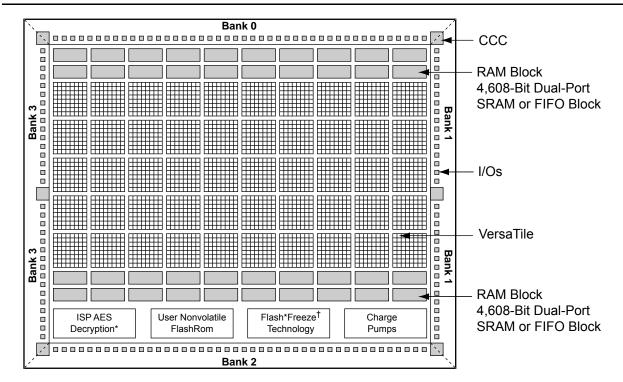

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

Note: \* AGLP030 does not contain a PLL or support AES security.

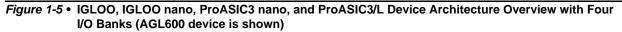

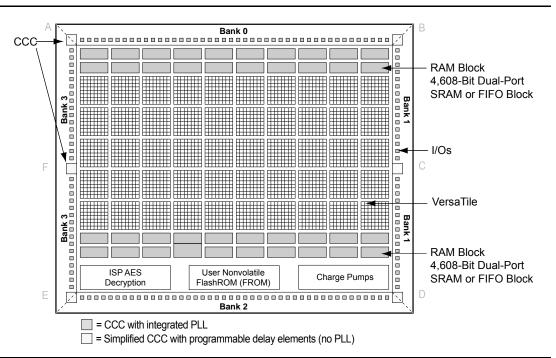

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

| /О Туре      | Beginning of I/O Name | Notes                                                    |

|--------------|-----------------------|----------------------------------------------------------|

| Single-Ended | GAAO/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAA1/IOuxwByVz        | quadrant global at a time                                |

|              | GAA2/IOuxwByVz        |                                                          |

|              | GABO/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAB1/IOuxwByVz        | quadrant global at a time.                               |

|              | GAB2/IOuxwByVz        |                                                          |

|              | GAC0/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAC1/IOuxwByVz        | quadrant global at a time.                               |

|              | GAC2/IOuxwByVz        |                                                          |

|              | GBAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBA1/IOuxwByVz        | at a time.                                               |

|              | GBA2/IOuxwByVz        |                                                          |

|              | GBBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBB1/IOuxwByVz        | at a time.                                               |

|              | GBB2/IOuxwByVz        |                                                          |

|              | GBC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBC1/IOuxwByVz        | at a time.                                               |

|              | GBC2/IOuxwByVz        |                                                          |

|              | GDAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDA1/IOuxwByVz        | at a time.                                               |

|              | GDA2/IOuxwByVz        |                                                          |

|              | GDBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDB1/IOuxwByVz        | at a time.                                               |

|              | GDB2/IOuxwByVz        |                                                          |

|              | GDC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDC1/IOuxwByVz        | at a time.                                               |

|              | GDC2/IOuxwByVz        |                                                          |

|              | GEAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEA1/IOuxwByVz        | at a time.                                               |

|              | GEA2/IOuxwByVz        |                                                          |

|              | GEBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEB1/IOuxwByVz        | at a time.                                               |

|              | GEB2/IOuxwByVz        |                                                          |

|              | GEC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEC1/IOuxwByVz        | at a time.                                               |

|              | GEC2/IOuxwByVz        |                                                          |

### Table 3-3 • Quadrant Global Pin Name

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

# **CCC Support in Microsemi's Flash Devices**

The flash FPGAs listed in Table 4-1 support the CCC feature and the functions described in this document.

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                       |  |

|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                 |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                             |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                        |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                               |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                           |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                          |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                               |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                             |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                       |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                             |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                              |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flash memory into a monolithic device |  |

### Table 4-1 • Flash-Based FPGAs

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Notes:

- 1. For INBUF\* driving a PLL macro or CLKDLY macro, the I/O will be hard-routed to the CCC; i.e., will be placed by software to a dedicated Global I/O.

- 2. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

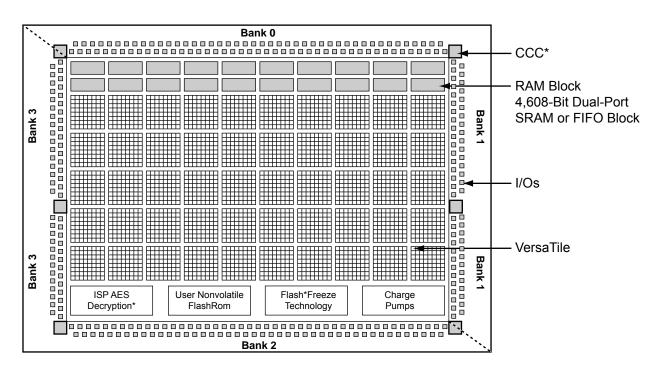

### Figure 4-3 • CCC Options: Global Buffers with Programmable Delay

The CLKDLY macro is a pass-through clock source that does not use the PLL, but provides the ability to delay the clock input using a programmable delay. The CLKDLY macro takes the selected clock input and adds a user-defined delay element. This macro generates an output clock phase shift from the input clock.

The CLKDLY macro can be driven by an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the software will automatically place the dedicated global I/O in the appropriate locations. Many specific INBUF macros support the wide variety of single-ended and differential I/O standards supported by the low power flash family. The available INBUF macros are described in the *IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.*

The CLKDLY macro can be driven directly from the FPGA core. The CLKDLY macro can also be driven from an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate the clock input driven by the hardwired I/O connection.

The visual CLKDLY configuration in the SmartGen area of the Microsemi Libero System-on-Chip (SoC) and Designer tools allows the user to select the desired amount of delay and configures the delay elements appropriately. SmartGen also allows the user to select the input clock source. SmartGen will automatically instantiate the special macro, PLLINT, when needed.

## **CLKDLY Macro Signal Descriptions**

The CLKDLY macro supports one input and one output. Each signal is described in Table 4-2.

Table 4-2 • Input and Output Description of the CLKDLY Macro

| Signal | Name            | I/O    | Description                                                       |

|--------|-----------------|--------|-------------------------------------------------------------------|

| CLK    | Reference Clock | Input  | Reference clock input                                             |

| GL     | Global Output   | Output | Primary output clock to respective global/quadrant clock networks |

## **Fusion CCC Locations**

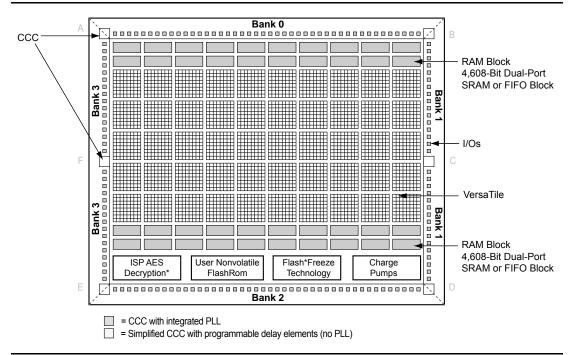

Fusion devices have six CCCs: one in each of the four corners and one each in the middle of the east and west sides of the device (Figure 4-17 and Figure 4-18). The device can have one integrated PLL in the middle of the west side of the device or two integrated PLLs in the middle of the east and west sides of the device (middle right and middle left).

*Figure 4-17* • CCC Locations in Fusion Family Devices (AFS090, AFS250, M1AFS250)

Figure 4-18 • CCC Locations in Fusion Family Devices (except AFS090, AFS250, M1AFS250)

## Phase Adjustment

The four phases available (0, 90, 180, 270) are phases with respect to VCO (PLL output). The VCO is divided to achieve the user's CCC required output frequency (GLA, YB/GLB, YC/GLC). The division happens after the selection of the VCO phase. The effective phase shift is actually the VCO phase shift divided by the output divider. This is why the visual CCC shows both the actual achievable phase and more importantly the actual delay that is equivalent to the phase shift that can be achieved.

## **Dynamic PLL Configuration**

The CCCs can be configured both statically and dynamically.

In addition to the ports available in the Static CCC, the Dynamic CCC has the dynamic shift register signals that enable dynamic reconfiguration of the CCC. With the Dynamic CCC, the ports CLKB and CLKC are also exposed. All three clocks (CLKA, CLKB, and CLKC) can be configured independently.

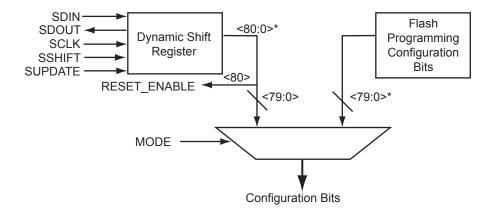

The CCC block is fully configurable. The following two sources can act as the CCC configuration bits.

### Flash Configuration Bits

The flash configuration bits are the configuration bits associated with programmed flash switches. These bits are used when the CCC is in static configuration mode. Once the device is programmed, these bits cannot be modified. They provide the default operating state of the CCC.

### **Dynamic Shift Register Outputs**

This source does not require core reprogramming and allows core-driven dynamic CCC reconfiguration. When the dynamic register drives the configuration bits, the user-defined core circuit takes full control over SDIN, SDOUT, SCLK, SSHIFT, and SUPDATE. The configuration bits can consequently be dynamically changed through shift and update operations in the serial register interface. Access to the logic core is accomplished via the dynamic bits in the specific tiles assigned to the PLLs.

Figure 4-21 illustrates a simplified block diagram of the MUX architecture in the CCCs.

Note: \*For Fusion, bit <88:81> is also needed.

The selection between the flash configuration bits and the bits from the configuration register is made using the MODE signal shown in Figure 4-21. If the MODE signal is logic HIGH, the dynamic shift register configuration bits are selected. There are 81 control bits to configure the different functions of the CCC.

Figure 4-21 • The CCC Configuration MUX Architecture

FlashROM in Microsemi's Low Power Flash Devices

# FlashROM Support in Flash-Based Devices

The flash FPGAs listed in Table 5-1 support the FlashROM feature and the functions described in this document.

### Table 5-1 • Flash-Based FPGAs

| Series      | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO IGLOO |                      | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|             | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|             | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|             | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3    | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|             | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|             | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|             | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|             | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|             | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|             | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion      | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Notes:

- Automotive ProASIC3 devices restrict RAM4K9 to a single port or to dual ports with the same clock 180° out of phase (inverted) between clock pins. In single-port mode, inputs to port B should be tied to ground to prevent errors during compile. This warning applies only to automotive ProASIC3 parts of certain revisions and earlier. Contact Technical Support at soc\_tech@microsemi.com for information on the revision number for a particular lot and date code.

- 2. For FIFO4K18, the same clock 180° out of phase (inverted) between clock pins should be used.

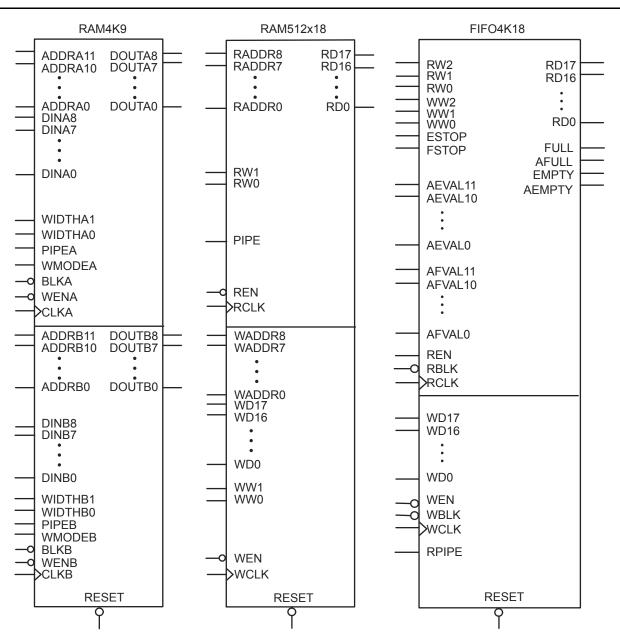

Figure 6-3 • Supported Basic RAM Macros

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

• Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

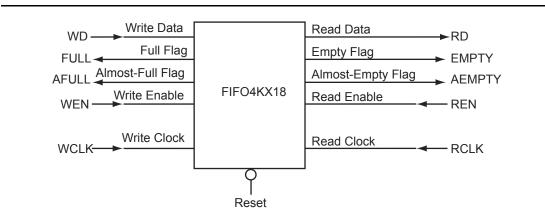

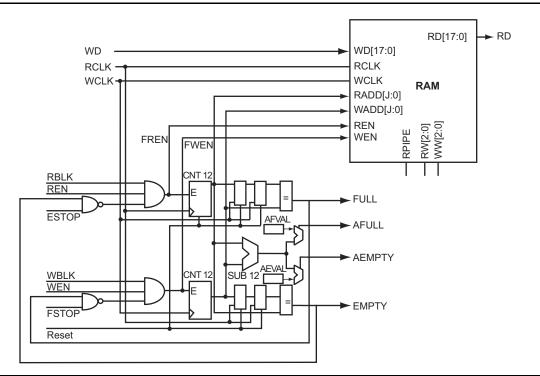

Figure 6-7 • RAM Block with Embedded FIFO Controller

The FIFOs maintain a separate read and write address. Whenever the difference between the write address and the read address is greater than or equal to the almost-full value (AFVAL), the Almost-Full flag is asserted. Similarly, the Almost-Empty flag is asserted whenever the difference between the write address and read address is less than or equal to the almost-empty value (AEVAL).

Due to synchronization between the read and write clocks, the Empty flag will deassert after the second read clock edge from the point that the write enable asserts. However, since the Empty flag is synchronized to the read clock, it will assert after the read clock reads the last data in the FIFO. Also, since the Full flag is dependent on the actual hardware configuration, it will assert when the actual physical implementation of the FIFO is full.

For example, when a user configures a 128×18 FIFO, the actual physical implementation will be a 256×18 FIFO element. Since the actual implementation is 256×18, the Full flag will not trigger until the

ProASIC3L FPGA Fabric User's Guide

| Date                     | Change                                                                                                                                                                                                                                          | Page |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| June 2011<br>(continued) | The following sentence was removed from the "LVCMOS (Low-Voltage CMOS)" section (SAR 22634): "All these versions use a 3.3 V–tolerant CMOS input buffer and a push-pull output buffer."                                                         | 184  |

|                          | Hot-insertion was changed to "No" for other IGLOO and all ProASIC3 devices in Table 7-12 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in IGLOO and ProASIC3 Devices (SAR 24526).                                                         | 193  |

|                          | The "Electrostatic Discharge Protection" section was revised to remove references to tolerances (refer to the <i>Reliability Report</i> for tolerances). The Machine Model (MM) is not supported and was deleted from this section (SAR 24385). | 192  |

|                          | The "I/O Interfacing" section was revised to state that low power flash devices are 5 V–input– and 5 V–output–tolerant if certain I/O standards are selected, removing "without adding any extra circuitry," which was incorrect (SAR 21404).   | 208  |

| July 2010                | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                       | N/A  |

| v1.4<br>(December 2008)  | The terminology in the "Low Power Flash Device I/O Support" section was revised.                                                                                                                                                                | 176  |

| v1.3<br>(October 2008)   | The "Low Power Flash Device I/O Support" section was revised to include new families and make the information more concise.                                                                                                                     | 176  |

| v1.2<br>(June 2008)      | <ul> <li>The following changes were made to the family descriptions in Table 7-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul>       | 176  |

| v1.1<br>(March 2008)     | Originally, this document contained information on all IGLOO and ProASIC3 families. With the addition of new families and to highlight the differences between the features, the document has been separated into 3 documents:                  | N/A  |

|                          | This document contains information specific to IGLOO, ProASIC3, and ProASIC3L.                                                                                                                                                                  |      |

|                          | "I/O Structures in IGLOOe and ProASIC3E Devices" in the <i>ProASIC3E FPGA Fabric User's Guide</i> contains information specific to IGLOOe, ProASIC3E, and ProASIC3EL I/O features.                                                              |      |

|                          | "I/O Structures in IGLOO PLUS Devices" in the <i>IGLOO PLUS FPGA Fabric User's Guide</i> contains information specific to IGLOO PLUS I/O features.                                                                                              |      |

I/O Structures in IGLOOe and ProASIC3E Devices

## 5 V Output Tolerance

IGLOO and ProASIC3 I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

## **Schmitt Trigger**

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

ProASIC3E devices have Schmitt triggers built into their I/O circuitry. The Schmitt trigger is available for the LVTTL, LVCMOS, and 3.3 V PCI I/O standards.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

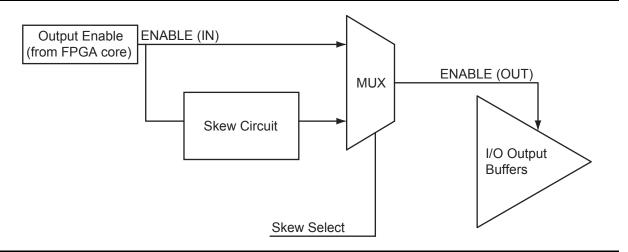

## Selectable Skew between Output Buffer Enable and Disable Times

Low power flash devices have a configurable skew block in the output buffer circuitry that can be enabled to delay output buffer assertion without affecting deassertion time. Since this skew block is only available for the OE signal, the feature can be used in tristate and bidirectional buffers. A typical 1.2 ns delay is added to the OE signal to prevent potential bus contention. Refer to the appropriate family datasheet for detailed timing diagrams and descriptions.

The Skew feature is available for all I/O standards.

This feature can be implemented by using a PDC command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

The configurable skew block is used to delay output buffer assertion (enable) without affecting deassertion (disable) time.

# **User I/O Naming Convention**

## IGLOOe and ProASIC3E

Due to the comprehensive and flexible nature of IGLOOe and ProASIC3E device user I/Os, a naming scheme is used to show the details of each I/O (Figure 8-20 on page 246). The name identifies to which I/O bank it belongs, as well as the pairing and pin polarity for differential I/Os.

I/O Nomenclature = FF/Gmn/IOuxwByVz

Gmn is only used for I/Os that also have CCC access—i.e., global pins.

- FF = Indicates the I/O dedicated for the Flash\*Freeze mode activation pin in IGLOOe only

- G = Global

- m = Global pin location associated with each CCC on the device: A (northwest corner), B (northeast corner), C (east middle), D (southeast corner), E (southwest corner), and F (west middle)

- n = Global input MUX and pin number of the associated Global location m, either A0, A1, A2, B0, B1, B2, C0, C1, or C2. Refer to the "Global Resources in Low Power Flash Devices" section on page 47 for information about the three input pins per clock source MUX at CCC location m.

- u = I/O pair number in the bank, starting at 00 from the northwest I/O bank and proceeding in a clockwise direction

- x = P (Positive) or N (Negative) for differential pairs, or R (Regular—single-ended) for the I/Os that support single-ended and voltage-referenced I/O standards only

- w = D (Differential Pair), P (Pair), or S (Single-Ended). D (Differential Pair) if both members of the pair are bonded out to adjacent pins or are separated only by one GND or NC pin; P (Pair) if both members of the pair are bonded out but do not meet the adjacency requirement; or S (Single-Ended) if the I/O pair is not bonded out. For Differential (D) pairs, adjacency for ball grid packages means only vertical or horizontal. Diagonal adjacency does not meet the requirements for a true differential pair.

- B = Bank

- y = Bank number (0–7). The bank number starts at 0 from the northwest I/O bank and proceeds in a clockwise direction.

- $V = V_{REF}$

- z = V<sub>REF</sub> minibank number (0–4). A given voltage-referenced signal spans 16 pins (typically) in an I/O bank. Voltage banks may have multiple V<sub>REF</sub> minibanks.

I/O Software Control in Low Power Flash Devices

### **Output Buffers**

There are two variations: Regular and Special.

If the **Regular** variation is selected, only the Width (1 to 128) needs to be entered. The default value for Width is 1.

The Special variation has Width, Technology, Output Drive, and Slew Rate options.

### **Bidirectional Buffers**

There are two variations: Regular and Special.

The Regular variation has Enable Polarity (Active High, Active Low) in addition to the Width option.

The **Special** variation has Width, Technology, Output Drive, Slew Rate, and Resistor Pull-Up/-Down options.

### **Tristate Buffers**

Same as Bidirectional Buffers.

### DDR

There are eight variations: DDR with Regular Input Buffers, Special Input Buffers, Regular Output Buffers, Special Output Buffers, Regular Tristate Buffers, Special Tristate Buffers, Regular Bidirectional Buffers, and Special Bidirectional Buffers.

These variations resemble the options of the previous I/O macro. For example, the Special Input Buffers variation has Width, Technology, Voltage Level, and Resistor Pull-Up/-Down options. DDR is not available on IGLOO PLUS devices.

- 4. Once the desired configuration is selected, click the **Generate** button. The Generate Core window opens (Figure 9-4).

- 5. Enter a name for the macro. Click **OK**. The core will be generated and saved to the appropriate location within the project files (Figure 9-5 on page 257).

Figure 9-4 • Generate Core Window

6. Instantiate the I/O macro in the top-level code.

The user must instantiate the DDR\_REG or DDR\_OUT macro in the design. Use SmartGen to generate both these macros and then instantiate them in your top level. To combine the DDR macros with the I/O, the following rules must be met:

### Rules for the DDR I/O Function

- The fanout between an I/O pin (D or Y) and a DDR (DDR\_REG or DDR\_OUT) macro must be equal to one for the combining to happen on that pin.

- If a DDR\_REG macro and a DDR\_OUT macro are combined on the same bidirectional I/O, they must share the same clear signal.

- Registers will not be combined in an I/O in the presence of DDR combining on the same I/O.

### Using the I/O Buffer Schematic Cell

Libero SoC software includes the ViewDraw schematic entry tool. Using ViewDraw, the user can insert any supported I/O buffer cell in the top-level schematic. Figure 9-5 shows a top-level schematic with different I/O buffer cells. When synthesized, the netlist will contain the same I/O macro.

Figure 9-5 • I/O Buffer Schematic Cell Usage

I/O Software Control in Low Power Flash Devices

# **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Date                    | Changes                                                                                                                                                                         | Page |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| August 2012             | The notes in Table 9-2 • Designer State (resulting from I/O attribute modification) were revised to clarify which device families support programmable input delay (SAR 39666). | 253  |

| June 2011               | Figure 9-2 • SmartGen Catalog was updated (SAR 24310). Figure 8-3 • Expanded I/O Section and the step associated with it were deleted to reflect changes in the software.       | 254  |

|                         | The following rule was added to the "VREF Rules for the Implementation of Voltage-Referenced I/O Standards" section:                                                            | 265  |

|                         | Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os (SAR 24310).                    |      |

| July 2010               | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                       | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 9-1 • Flash-Based FPGAs.                                                                                               | 252  |

|                         | The notes for Table 9-2 • Designer State (resulting from I/O attribute modification) were revised to indicate that skew control and input delay do not apply to nano devices.   | 253  |

| v1.3<br>(October 2008)  | The "Flash FPGAs I/O Support" section was revised to include new families and make the information more concise.                                                                | 252  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 9-1 • Flash-<br>Based FPGAs:                                                                                | 252  |

|                         | ProASIC3L was updated to include 1.5 V.                                                                                                                                         |      |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                  |      |

| v1.1<br>(March 2008)    | This document was previously part of the I/O Structures in IGLOO and ProASIC3 Devices document. The content was separated and made into a new document.                         | N/A  |

|                         | Table 9-2 • Designer State (resulting from I/O attribute modification) was updated to include note 2 for IGLOO PLUS.                                                            | 253  |

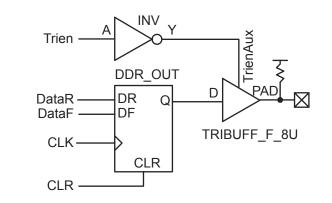

## **DDR Tristate Output Register**

#### Figure 10-7 • DDR Tristate Output Register, LOW Enable, 8 mA, Pull-Up (LVTTL)

### Verilog

module DDR\_TriStateBuf\_LVTTL\_8mA\_HighSlew\_LowEnb\_PullUp(DataR, DataF, CLR, CLK, Trien, PAD);

input DataR, DataF, CLR, CLK, Trien; output PAD;

wire TrienAux, Q;

```

INV Inv_Tri(.A(Trien),.Y(TrienAux));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

TRIBUFF_F_8U TRIBUFF_F_8U_0_inst(.D(Q),.E(TrienAux),.PAD(PAD));

```

endmodule

### VHDL

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

```

```

entity DDR_TriStateBuf_LVTTL_8mA_HighSlew_LowEnb_PullUp is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; PAD : out std_logic);

end DDR_TriStateBuf_LVTTL_8mA_HighSlew_LowEnb_PullUp;

```

architecture DEF\_ARCH of DDR\_TriStateBuf\_LVTTL\_8mA\_HighSlew\_LowEnb\_PullUp is

```

component INV

port(A : in std_logic := 'U'; Y : out std_logic);

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component TRIBUFF_F_8U

port(D, E : in std_logic := 'U'; PAD : out std_logic);

end component;

signal TrienAux, Q : std_logic ;

begin

```

Inv\_Tri : INV

port map(A => Trien, Y => TrienAux);

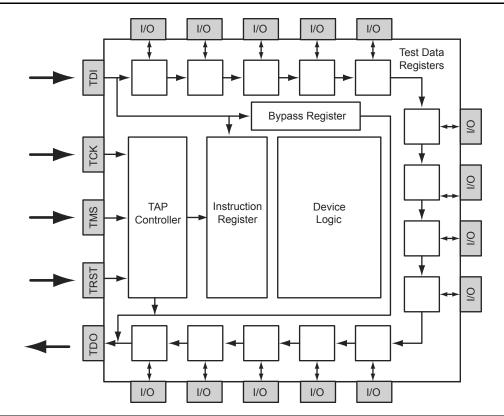

Boundary Scan in Low Power Flash Devices

Figure 16-2 • Boundary Scan Chain

# **Board-Level Recommendations**

Table 16-3 gives pull-down recommendations for the TRST and TCK pins.

### Table 16-3 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance* |

|----------------|---------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ       |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ       |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.2 V | TBD                 |

Note: Equivalent parallel resistance if more than one device is on JTAG chain (Figure 16-3)

# **Power-Up/-Down Sequence and Transient Current**

Microsemi's low power flash devices use the following main voltage pins during normal operation:<sup>2</sup>

- VCCPLX

- VJTAG

- VCC: Voltage supply to the FPGA core

- VCC is 1.5 V ± 0.075 V for IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3 devices operating at 1.5 V.

- VCC is 1.2 V ± 0.06 V for IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices operating at 1.2 V.

- V5 devices will require a 1.5 V VCC supply, whereas V2 devices can utilize either a 1.2 V or 1.5 V VCC.

- VCCIBx: Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number.

- VMVx: Quiet supply voltage to the input buffers of each I/O bank. x is the bank number. (Note: IGLOO nano, IGLOO PLUS, and ProASIC3 nano devices do not have VMVx supply pins.)

The I/O bank VMV pin must be tied to the VCCI pin within the same bank. Therefore, the supplies that need to be powered up/down during normal operation are VCC and VCCI. These power supplies can be powered up/down in any sequence during normal operation of IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, ProASIC3, and ProASIC3 nano FPGAs. During power-up, I/Os in each bank will remain tristated until the last supply (either VCCIBx or VCC) reaches its functional activation voltage. Similarly, during power-down, I/Os of each bank are tristated once the first supply reaches its brownout deactivation voltage.

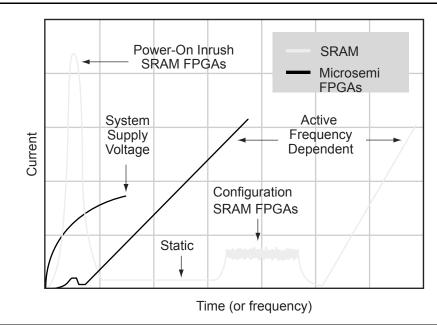

Although Microsemi's low power flash devices have no power-up or power-down sequencing requirements, Microsemi identifies the following power conditions that will result in higher than normal transient current. Use this information to help maximize power savings:

Microsemi recommends tying VCCPLX to VCC and using proper filtering circuits to decouple VCC noise from the PLL.

a. If VCCPLX is powered up before VCC, a static current of up to 5 mA (typical) per PLL may be measured on VCCPLX.

The current vanishes as soon as VCC reaches the VCCPLX voltage level.

The same current is observed at power-down (VCC before VCCPLX).

- b. If VCCPLX is powered up simultaneously or after VCC:

- Microsemi's low power flash devices exhibit very low transient current on VCC. For ProASIC3 devices, the maximum transient current on V<sub>CC</sub> does not exceed the maximum standby current specified in the device datasheet.

The source of transient current, also known as inrush current, varies depending on the FPGA technology. Due to their volatile technology, the internal registers in SRAM FPGAs must be initialized before configuration can start. This initialization is the source of significant inrush current in SRAM FPGAs during power-up. Due to the nonvolatile nature of flash technology, low power flash devices do not require any initialization at power-up, and there is very little or no crossbar current through PMOS and NMOS devices. Therefore, the transient current at power-up is significantly less than for SRAM FPGAs. Figure 18-1 on page 376 illustrates the types of power consumption by SRAM FPGAs compared to Microsemi's antifuse and flash FPGAs.

For more information on Microsemi FPGA voltage supplies, refer to the appropriate datasheet located at http://www.microsemi.com/soc/techdocs/ds.

Power-Up/-Down Behavior of Low Power Flash Devices

## **Transient Current on VCC**

The characterization of the transient current on VCC is performed on nearly all devices within the IGLOO, ProASIC3L, and ProASIC3 families. A sample size of five units is used from each device family member. All the device I/Os are internally pulled down while the transient current measurements are performed. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCC, when the power supply is powered at ramp-rates ranging from 15 V/ms to 0.15 V/ms, does not exceed the maximum standby current specified in the device datasheets. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCC. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCC is typically in the range of 1–5 mA.

## **Transient Current on VCCI**

The characterization of the transient current on VCCI is performed on devices within the IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, ProASIC3 nano, and ProASIC3L groups of devices, similarly to VCC transient current measurements. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCCI, when the power supply is powered at ramp-rates ranging from 33 V/ms to 0.33 V/ms, does not exceed the maximum standby current specified in the device datasheet. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCCI. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCCI is typically in the range of 1–2 mA.