Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells |                                                                 |

| Total RAM Bits                 | 147456                                                          |

| Number of I/O                  | 300                                                             |

| Number of Gates                | 100000                                                          |

| Voltage - Supply               | 1.14V ~ 1.575V                                                  |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                              |

| Package / Case                 | 484-BGA                                                         |

| Supplier Device Package        | 484-FPBGA (23x23)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p1000l-fgg484i |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

## Flash\*Freeze Mode Device Behavior

### Entering Flash\*Freeze Mode

- IGLOO, IGLOO nano, IGLOO PLUS, ProASCI3L, and RT ProASIC3 devices are designed and optimized to enter Flash\*Freeze mode only when power supplies are stable. If the device is being powered up while the FF pin is asserted (Flash\*Freeze mode type 1), or while both FF pin and LSICC signal are asserted (Flash\*Freeze mode type 2), the device is expected to enter Flash\*Freeze mode within 5 µs after the I/Os and FPGA core have reached their activation levels.

- If the device is already powered up when the FF pin is asserted, the device will enter Flash\*Freeze mode within 1 µs (type 1). In Flash\*Freeze mode type 2 operation, entering Flash\*Freeze mode is completed within 1 µs after both FF pin and LSICC signal are asserted. Exiting Flash\*Freeze mode is completed within 1 µs after deasserting the FF pin only.

#### PLLs

- If an embedded PLL is used, entering Flash\*Freeze mode will automatically power down the PLL.

- The PLL output clocks will stop toggling within 1 µs after the assertion of the FF pin in type 1, or after both FF pin and LSICC signal are asserted in type 2. At the same time, I/Os will transition into the state specified in Table 2-6 on page 29. The user design must ensure it is safe to enter Flash\*Freeze mode.

### I/Os and Globals

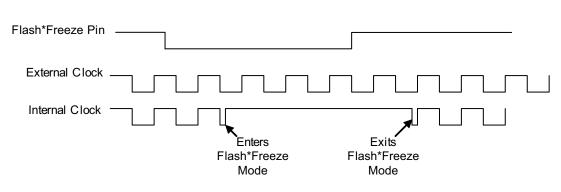

• While entering Flash\*Freeze mode, inputs, globals, and PLLs will enter their Flash\*Freeze state asynchronously to each other. As a result, clock and data glitches and narrow pulses may be generated while entering Flash\*Freeze mode, as shown in Figure 2-5.

Figure 2-5 • Narrow Clock Pulses During Flash\*Freeze Entrance and Exit

- I/O banks are not all deactivated simultaneously when entering Flash\*Freeze mode. This can cause clocks and inputs to become disabled at different times, resulting in unexpected data being captured.

- Upon entering Flash\*Freeze mode, all inputs and globals become tied High internally (except when an input hold state is used on IGLOO nano or IGLOO PLUS devices). If any of these signals are driven Low or tied Low externally, they will experience a Low to High transition internally when entering Flash\*Freeze mode.

- Upon entering type 2 Flash\*Freeze mode, ensure the LSICC signal (active High) does not deassert. This can prevent the device from entering Flash\*Freeze mode.

- Asynchronous input to output paths may experience output glitches. For example, on a direct into-out path, if the current state is '0' and the input bank turns off first, the input and then the output will transition to '1' before the output enters its Flash\*Freeze state. This can be prevented by using latches in asynchronous in-to-out paths.

- The above situations can cause glitches or invalid data to be clocked into and preserved in the device. Refer to the "Flash\*Freeze Design Guide" section on page 34 for solutions.

Flash\*Freeze Technology and Low Power Modes

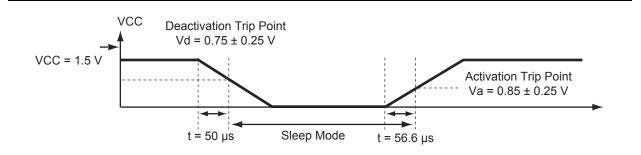

power supply and board-level configurations, the user can easily calculate how long it will take for the core to become inactive or active. For more information, refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373.

Figure 2-8 • Entering and Exiting Sleep Mode, Typical Timing Diagram

### **Context Save and Restore in Sleep or Shutdown Mode**

In Sleep mode or Shutdown mode, the contents of the SRAM, state of the I/Os, and state of the registers are lost when the device is powered off, if no other measure is taken. A low-cost external serial EEPROM can be used to save and restore the contents of the device when entering and exiting Sleep mode or Shutdown mode. In the *Embedded SRAM Initialization Using External Serial EEPROM* application note, detailed information and a reference design are provided for initializing the embedded SRAM using an external serial EEPROM. The user can easily customize the reference design to save and restore the FPGA state when entering and exiting Sleep mode or Shutdown mode. The microcontroller will need to manage this activity; hence, before powering down  $V_{CC}$ , the data will be read from the FPGA and stored externally. In a similar way, after the FPGA is powered up, the microcontroller will allow the FPGA to load the data from external memory and restore its original state.

## Flash\*Freeze Design Guide

This section describes how designers can create reliable designs that use ultra-low power Flash\*Freeze modes optimally. The section below provides guidance on how to select the best Flash\*Freeze mode for any application. The "Design Solutions" section on page 35 gives specific recommendations on how to design and configure clocks, set/reset signals, and I/Os. This section also gives an overview of the design flow and provides details concerning Microsemi's Flash\*Freeze Management IP, which enables clean clock gating and housekeeping. The "Additional Power Conservation Techniques" section on page 41 describes board-level considerations for entering and exiting Flash\*Freeze mode.

## Selecting the Right Flash\*Freeze Mode

Both Flash\*Freeze modes will bring an FPGA into an ultra-low power static mode that retains register and SRAM content and sets I/Os to a predetermined configuration. There are two primary differences that distinguish type 2 mode from type 1, and they must be considered when creating a design using Flash\*Freeze technology.

First, with type 2 mode, the device has an opportunity to wait for a second signal to enable activation of Flash\*Freeze mode. This allows processes to complete prior to deactivating the device, and can be useful to control task completion, data preservation, accidental Flash\*Freeze activation, system shutdown, or any other housekeeping function. The second signal may be derived from an external or into-out internal source. The second difference between type 1 and type 2 modes is that a design for type 2 mode has an opportunity to cleanly manage clocks and data activity before entering and exiting Flash\*Freeze mode. This is particularly important when data preservation is needed, as it ensures valid data is stored prior to entering, and upon exiting, Flash\*Freeze mode.

Type 1 Flash\*Freeze mode is ideally suited for applications with the following design criteria:

- Entering Flash\*Freeze mode is not dependent on any signal other than the external FF pin.

- Internal housekeeping is not required prior to entering Flash\*Freeze.

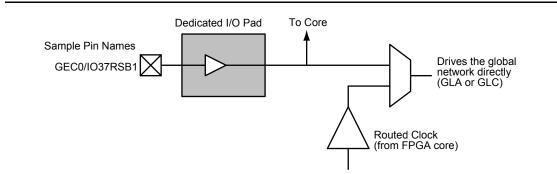

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

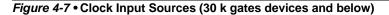

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Notes:

- Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Conventions in I/O Structures" chapter of the appropriate device user's guide.

- 2. Instantiate the routed clock source input as follows:

- a) Connect the output of a logic element to the clock input of a PLL, CLKDLY, or CLKINT macro.

- b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS/B-LVDS/M-LVDS/DDR) in a relevant global pin location.

- 3. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

Figure 4-8 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT (60 k gates devices and above)

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

Dividers n and m (the input divider and feedback divider, respectively) provide integer frequency division factors from 1 to 128. The output dividers u, v, and w provide integer division factors from 1 to 32. Frequency scaling of the reference clock CLKA is performed according to the following formulas:

$$f_{GLA} = f_{CLKA} \times m / (n \times u) - GLA Primary PLL Output Clock$$

$$EQ 4-1$$

$$f_{GLB} = f_{YB} = f_{CLKA} \times m / (n \times v) - GLB Secondary 1 PLL Output Clock(s)$$

$$EQ 4-2$$

$$f_{GLC} = f_{YC} = f_{CLKA} \times m / (n \times w) - GLC$$

Secondary 2 PLL Output Clock(s)

EQ 4-3

SmartGen provides a user-friendly method of generating the configured PLL netlist, which includes automatically setting the division factors to achieve the closest possible match to the requested frequencies. Since the five output clocks share the *n* and *m* dividers, the achievable output frequencies are interdependent and related according to the following formula:

$$f_{GLA} = f_{GLB} \times (v / u) = f_{GLC} \times (w / u)$$

EQ 4-4

## **Clock Delay Adjustment**

There are a total of seven configurable delay elements implemented in the PLL architecture.

Two of the delays are located in the feedback path, entitled System Delay and Feedback Delay. System Delay provides a fixed delay of 2 ns (typical), and Feedback Delay provides selectable delay values from 0.6 ns to 5.56 ns in 160 ps increments (typical). For PLLs, delays in the feedback path will effectively advance the output signal from the PLL core with respect to the reference clock. Thus, the System and Feedback delays generate negative delay on the output clock. Additionally, each of these delays can be independently bypassed if necessary.

The remaining five delays perform traditional time delay and are located at each of the outputs of the PLL. Besides the fixed global driver delay of 0.755 ns for each of the global networks, the global multiplexer outputs (GLA, GLB, and GLC) each feature an additional selectable delay value, as given in Table 4-7.

| Device                | Typical | Starting Values | Increments | Ending Value |  |

|-----------------------|---------|-----------------|------------|--------------|--|

| ProASIC3              | 200 ps  | 0 to 735 ps     | 200 ps     | 6.735 ns     |  |

| IGLOO/ProASIC3L 1.5 V | 360 ps  | 0 to 1.610 ns   | 360 ps     | 12.410 ns    |  |

| IGLOO/ProASIC3L 1.2 V | 580 ps  | 0 to 2.880 ns   | 580 ps     | 20.280 ns    |  |

Table 4-7 • Delay Values in Libero SoC Software per Device Family

The additional YB and YC signals have access to a selectable delay from 0.6 ns to 5.56 ns in 160 ps increments (typical). This is the same delay value as the CLKDLY macro. It is similar to CLKDLY, which bypasses the PLL core just to take advantage of the phase adjustment option with the delay value.

The following parameters must be taken into consideration to achieve minimum delay at the outputs (GLA, GLB, GLC, YB, and YC) relative to the reference clock: routing delays from the PLL core to CCC outputs, core outputs and global network output delays, and the feedback path delay. The feedback path delay acts as a time advance of the input clock and will offset any delays introduced beyond the PLL core output. The routing delays are determined from back-annotated simulation and are configuration-dependent.

| OADIVHALF /<br>OBDIVHALF /<br>OCDIVHALF | OADIV<4:0> /<br>OBDIV<4:0> /<br>OCDIV<4:0><br>(in decimal) | Divider Factor | Input Clock<br>Frequency | Output Clock<br>Frequency (MHz)   |

|-----------------------------------------|------------------------------------------------------------|----------------|--------------------------|-----------------------------------|

| 1                                       | 2                                                          | 1.5            | 100 MHz RC               | 66.7                              |

|                                         | 4                                                          | 2.5            | Oscillator               | 40.0                              |

|                                         | 6                                                          | 3.5            |                          | 28.6                              |

|                                         | 8                                                          | 4.5            |                          | 22.2                              |

|                                         | 10                                                         | 5.5            |                          | 18.2                              |

|                                         | 12                                                         | 6.5            |                          | 15.4                              |

|                                         | 14                                                         | 7.5            |                          | 13.3                              |

|                                         | 16                                                         | 8.5            |                          | 11.8                              |

|                                         | 18                                                         | 9.5            |                          | 10.5                              |

|                                         | 20                                                         | 10.5           |                          | 9.5                               |

|                                         | 22                                                         | 11.5           |                          | 8.7                               |

|                                         | 24                                                         | 12.5           |                          | 8.0                               |

|                                         | 26                                                         | 13.5           |                          | 7.4                               |

|                                         | 28                                                         | 14.5           | 1                        | 6.9                               |

| 0                                       | 0–31                                                       | 1–32           | Other Clock Sources      | Depends on other divider settings |

### Table 4-18 • Fusion Dynamic CCC Division by Half Configuration

### Table 4-19 • Configuration Bit <76:75> / VCOSEL<2:1> Selection for All Families

|                   |               |               |               | VCOS          | EL[2:1]       |               |               |               |

|-------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

|                   | (             | 0             | 0             | )1            | 1             | 0             | 11            |               |

| Voltage           | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) |

| IGLOO and IGLOO   | PLUS          |               |               |               | •             |               |               |               |

| 1.2 V ± 5%        | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 160           |

| 1.5 V ± 5%        | 24            | 43.75         | 30            | 87.5          | 60            | 175           | 135           | 250           |

| ProASIC3L, RT Pro | ASIC3, and    | Military Pro  | ASIC3/L       | •             | •             |               |               |               |

| 1.2 V ± 5%        | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 250           |

| 1.5 V ± 5%        | 24            | 43.75         | 30            | 70            | 60            | 175           | 135           | 350           |

| ProASIC3 and Fusi | ion           | •             |               | •             | •             | •             |               |               |

| 1.5 V ± 5%        | 24            | 43.75         | 33.75         | 87.5          | 67.5          | 175           | 135           | 350           |

### Table 4-20 • Configuration Bit <74> / VCOSEL<0> Selection for All Families

| VCOSEL[0] | Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0         | Fast PLL lock acquisition time with high tracking jitter. Refer to the corresponding datasheet for specific value and definition. |

| 1         | Slow PLL lock acquisition time with low tracking jitter. Refer to the corresponding datasheet for specific value and definition.  |

FlashROM in Microsemi's Low Power Flash Devices

# **FlashROM Applications**

The SmartGen core generator is used to configure FlashROM content. You can configure each page independently. SmartGen enables you to create and modify regions within a page; these regions can be 1 to 16 bytes long (Figure 5-4).

|          |   |    | Byte Number in Page |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------|---|----|---------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|          |   | 15 | 14                  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|          | 7 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| <u> </u> | 6 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| he       | 5 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Numb     | 4 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| ۵<br>ا   | 3 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Pag      | 2 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| а.       | 1 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|          | 0 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

#### Figure 5-4 • FlashROM Configuration

The FlashROM content can be changed independently of the FPGA core content. It can be easily accessed and programmed via JTAG, depending on the security settings of the device. The SmartGen core generator enables each region to be independently updated (described in the "Programming and Accessing FlashROM" section on page 138). This enables you to change the FlashROM content on a per-part basis while keeping some regions "constant" for all parts. These features allow the FlashROM to be used in diverse system applications. Consider the following possible uses of FlashROM:

- Internet protocol (IP) addressing (wireless or fixed)

- System calibration settings

- Restoring configuration after unpredictable system power-down

- · Device serialization and/or inventory control

- Subscription-based business models (e.g., set-top boxes)

- Secure key storage

- Asset management tracking

- Date stamping

- Version management

I/O Structures in IGLOO and ProASIC3 Devices

| Solution | Board Components                                                                                                                                                                 | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Two resistors                                                                                                                                                                    | Low to High <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2        | Resistor and Zener 3.3 V                                                                                                                                                         | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3        | Bus switch                                                                                                                                                                       | High                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4        | Minimum resistor value <sup>2,3,4,5</sup><br>R = 47 $\Omega$ at T <sub>J</sub> = 70°C<br>R = 150 $\Omega$ at T <sub>J</sub> = 85°C<br>R = 420 $\Omega$ at T <sub>J</sub> = 100°C | Medium                   | Maximum diode current at 100% duty cycle, signal constantly at 1<br>52.7 mA at $T_J = 70^{\circ}$ C / 10-year lifetime<br>16.5 mA at $T_J = 85^{\circ}$ C / 10-year lifetime<br>5.9 mA at $T_J = 100^{\circ}$ C / 10-year lifetime<br>For duty cycles other than 100%, the currents can be<br>increased by a factor of 1 / (duty cycle).<br>Example: 20% duty cycle at 70°C<br>Maximum current = (1 / 0.2) × 52.7 mA = 5 × 52.7 mA =<br>263.5 mA |

#### Table 7-13 • Comparison Table for 5 V–Compliant Receiver Solutions

Notes:

- 1. Speed and current consumption increase as the board resistance values decrease.

- 2. Resistor values ensure I/O diode long-term reliability.

- 3. At 70°C, customers could still use 420  $\Omega$  on every I/O.

- 4. At 85°C, a 5 V solution on every other I/O is permitted, since the resistance is lower (150  $\Omega$ ) and the current is higher. Also, the designer can still use 420  $\Omega$  and use the solution on every I/O.

- 5. At 100°C, the 5 V solution on every I/O is permitted, since 420  $\Omega$  are used to limit the current to 5.9 mA.

### 5 V Output Tolerance

IGLOO and ProASIC3 I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

## Schmitt Trigger

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

The Schmitt trigger is available for the LVTTL, LVCMOS, and 3.3 V PCI I/O standards.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 7-5 on page 179) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

IGLOO and ProASIC3 devices support output slew rate control: high and low. Microsemi recommends the high slew rate option to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected.

### **Output Drive**

The output buffers of IGLOO and ProASIC3 devices can provide multiple drive strengths to meet signal integrity requirements. The LVTTL and LVCMOS (except 1.2 V LVCMOS) standards have selectable drive strengths. Other standards have a preset value.

Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 2.5 V, 5.0 V input, LVCMOS 1.8 V, and LVCMOS 1.5 V. All other I/O standards have a high output slew rate by default.

For 30 k gate devices, refer to Table 7-14. For other ProASIC3 and IGLOO devices, refer to Table 7-15 through Table 7-16 on page 203 for more information about the slew rate and drive strength specification. Refer to Table 7-4 on page 178 for I/O bank type definitions.

There will be a difference in timing between the Standard Plus I/O banks and the Advanced I/O banks. Refer to the I/O timing tables in the datasheet for the standards supported by each device.

Table 7-14 • IGLOO and ProASIC3 Output Drive and Slew for Standard I/O Bank Type (for 30 k gate devices)

| I/O Standards      | 2 mA | 4 mA | 6 mA | 8 mA | SI   | ew  |

|--------------------|------|------|------|------|------|-----|

| LVTTL/LVCMOS 3.3 V | 1    | 1    | 1    | 1    | High | Low |

| LVCMOS 2.5 V       | 1    | 1    | 1    | 1    | High | Low |

| LVCMOS 1.8 V       | 1    | 1    | -    | -    | High | Low |

| LVCMOS 1.5 V       | 1    | _    | -    | _    | High | Low |

| I/O Standards | 2 mA | 4 mA | 6 mA | 8 mA       | 12 mA    | 16 mA | S    | lew |

|---------------|------|------|------|------------|----------|-------|------|-----|

| LVTTL         | 1    | ~    | 1    | 1          | 1        | 1     | High | Low |

| LVCMOS 3.3 V  | 1    | 1    | ~    | ~          | <i>✓</i> | 1     | High | Low |

| LVCMOS 2.5 V  | 1    | ✓ *  | 1    | <b>√</b> * | 1        | -     | High | Low |

| LVCMOS 1.8 V  | 1    | ✓    | 1    | 1          | -        | -     | High | Low |

| LVCMOS 1.5 V  | ~    | ✓    | -    | _          | -        | -     | High | Low |

Table 7-15 • IGLOO and ProASIC3 Output Drive and Slew for Standard Plus I/O Bank Type

Note: \*Not available in Automotive devices.

| I/O Standards    | 2 mA | 4 mA       | 6 mA | 8 mA       | 12 mA    | 16 mA | 24 mA | S    | ew  |

|------------------|------|------------|------|------------|----------|-------|-------|------|-----|

| LVTTL            | 1    | ✓          | ✓    | ✓          | <i>✓</i> | 1     | 1     | High | Low |

| LVCMOS 3.3 V     | ✓    | ✓          | ✓    | ✓          | 1        | 1     | 1     | High | Low |

| LVCMOS 2.5 V     | 1    | ✓ *        | ✓    | ✓ *        | 1        | 1     | 1     | High | Low |

| LVCMOS 2.5/5.0 V | 1    | <b>√</b> * | ✓    | <b>√</b> * | 1        | 1     | 1     | High | Low |

| LVCMOS 1.8 V     | 1    | ✓          | ✓    | ✓          | 1        | 1     | -     | High | Low |

| LVCMOS 1.5 V     | 1    | ✓          | ✓    | ✓          | ✓        | -     | -     | High | Low |

Note: Not available in Automotive devices.

# I/O Software Support

In Microsemi's Libero software, default settings have been defined for the various I/O standards supported. Changes can be made to the default settings via the use of attributes; however, not all I/O attributes are applicable for all I/O standards. Table 7-17 list the valid I/O attributes that can be manipulated by the user for each I/O standard.

Single-ended I/O standards in low power flash devices support up to five different drive strengths.

| I/O Standard         | SLEW<br>(output<br>only) | OUT_DRIVE<br>(output only) | SKEW<br>(all macros<br>with OE) | RES_PULL | OUT_LOAD<br>(output only) | COMBINE_REGISTER |

|----------------------|--------------------------|----------------------------|---------------------------------|----------|---------------------------|------------------|

| LVTTL/LVCMOS 3.3 V   | 1                        | ✓                          | 1                               | ✓        | ✓                         | 1                |

| LVCMOS 2.5 V         | 1                        | ✓                          | 1                               | <i>✓</i> | ✓                         | 1                |

| LVCMOS 2.5/5.0 V     | 1                        | 1                          | 1                               | 1        | ✓                         | ✓                |

| LVCMOS 1.8 V         | 1                        | 1                          | 1                               | 1        | ✓                         | 1                |

| LVCMOS 1.5 V         | 1                        | 1                          | 1                               | 1        | 1                         | ✓                |

| PCI (3.3 V)          |                          |                            | 1                               |          | 1                         | ✓                |

| PCI-X (3.3 V)        | 1                        |                            | 1                               |          | ✓                         | ✓                |

| LVDS, B-LVDS, M-LVDS |                          |                            | 1                               |          |                           | 1                |

| LVPECL               |                          |                            |                                 |          |                           | ✓                |

Table 7-17 • IGLOO and ProASIC3 I/O Attributes vs. I/O Standard Applications

Note: Applies to all 30 k gate devices.

Table 7-18 lists the default values for the above selectable I/O attributes as well as those that are preset for that I/O standard. See Table 7-14 on page 203 to Table 7-16 on page 203 for SLEW and OUT\_DRIVE settings.

| Table 7-18 • IGLOO and ProASIC3 I/O Default Attributes | 5 |

|--------------------------------------------------------|---|

|--------------------------------------------------------|---|

| I/O Standards           | SLEW<br>(output only) | OUT_DRIVE<br>(output only) | SKEW<br>(tribuf and<br>bibuf<br>only) | RES_PULL | OUT_LOAD<br>(output<br>only) | COMBINE_REGISTER |

|-------------------------|-----------------------|----------------------------|---------------------------------------|----------|------------------------------|------------------|

| LVTTL/LVCMOS 3.3 V      |                       | on page 203 to             | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 2.5 V            |                       |                            | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 2.5/5.0 V        | page 203.             | page 203.                  | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 1.8 V            | 1-0                   | 1.0                        | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 1.5 V            |                       |                            | Off                                   | None     | 35 pF                        | -                |

| PCI (3.3 V)             |                       |                            | Off                                   | None     | 10 pF                        | -                |

| PCI-X (3.3 V)           |                       |                            | Off                                   | None     | 10 pF                        | -                |

| LVDS, B-LVDS,<br>M-LVDS |                       |                            | Off                                   | None     | 0 pF                         | -                |

| LVPECL                  | 1                     |                            | Off                                   | None     | 0 pF                         | -                |

I/O Software Control in Low Power Flash Devices

### I/O Function

Figure 9-8 shows an example of the I/O Function table included in the I/O bank report:

### Figure 9-8 • I/O Function Table

This table lists the number of input I/Os, output I/Os, bidirectional I/Os, and differential input and output I/O pairs that use I/O and DDR registers.

Note: IGLOO nano and ProASIC3 nano devices do not support differential inputs.

Certain rules must be met to implement registered and DDR I/O functions (refer to the I/O Structures section of the handbook for the device you are using and the "DDR" section on page 256).

### I/O Technology

The I/O Technology table (shown in Figure 9-9) gives the values of VCCI and VREF (reference voltage) for all the I/O standards used in the design. The user should assign these voltages appropriately.

Figure 9-9 • I/O Technology Table

DDR for Microsemi's Low Power Flash Devices

# **Instantiating DDR Registers**

Using SmartGen is the simplest way to generate the appropriate RTL files for use in the design. Figure 10-4 shows an example of using SmartGen to generate a DDR SSTL2 Class I input register. SmartGen provides the capability to generate all of the DDR I/O cells as described. The user, through the graphical user interface, can select from among the many supported I/O standards. The output formats supported are Verilog, VHDL, and EDIF.

Figure 10-5 on page 277 through Figure 10-8 on page 280 show the I/O cell configured for DDR using SSTL2 Class I technology. For each I/O standard, the I/O pad is buffered by a special primitive that indicates the I/O standard type.

Figure 10-4 • Example of Using SmartGen to Generate a DDR SSTL2 Class I Input Register

Programming Flash Devices

# List of Changes

| Date      | Changes                                                                                                                                                                                                                                                                                                         | Page |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| July 2010 | FlashPro4 is a replacement for FlashPro3 and has been added to this chapter.<br>FlashPro is no longer available.                                                                                                                                                                                                | N/A  |  |  |

|           | The chapter was updated to include SmartFusion devices.                                                                                                                                                                                                                                                         | N/A  |  |  |

|           | The following were deleted:                                                                                                                                                                                                                                                                                     | N/A  |  |  |

|           | "Live at Power-Up (LAPU) or Boot PROM" section                                                                                                                                                                                                                                                                  |      |  |  |

|           | "Design Security" section                                                                                                                                                                                                                                                                                       |      |  |  |

|           | Table 14-2 • Programming Features for Actel Devices and much of the text in the "Programming Features for Microsemi Devices" section                                                                                                                                                                            |      |  |  |

|           | "Programming Flash FPGAs" section                                                                                                                                                                                                                                                                               |      |  |  |

|           | "Return Material Authorization (RMA) Policies" section                                                                                                                                                                                                                                                          |      |  |  |

|           | The "Device Programmers" section was revised.                                                                                                                                                                                                                                                                   | 291  |  |  |

|           | The Independent Programming Centers information was removed from the "Volume Programming Services" section.                                                                                                                                                                                                     | 292  |  |  |

|           | Table 11-3 • Programming Solutions was revised to add FlashPro4 and note that FlashPro is discontinued. A note was added for FlashPro Lite regarding power supply requirements.                                                                                                                                 |      |  |  |

|           | Most items were removed from Table 11-4 • Programming Ordering Codes, including FlashPro3 and FlashPro.                                                                                                                                                                                                         | 294  |  |  |

|           | The "Programmer Device Support" section was deleted and replaced with a reference to the Microsemi SoC Products Group website for the latest information.                                                                                                                                                       | 294  |  |  |

|           | The "Certified Programming Solutions" section was revised to add FlashPro4 and remove Silicon Sculptor I and Silicon Sculptor 6X. Reference to <i>Programming and Functional Failure Guidelines</i> was added.                                                                                                  | 294  |  |  |

|           | The file type *.pdb was added to the "Use the Latest Version of the Designer Software to Generate Your Programming File (recommended)" section.                                                                                                                                                                 | 295  |  |  |

|           | Instructions on cleaning and careful insertion were added to the "Perform Routine<br>Hardware Self-Diagnostic Test" section. Information was added regarding testing<br>Silicon Sculptor programmers with an adapter module installed before every<br>programming session verifying their calibration annually. | 295  |  |  |

|           | The "Signal Integrity While Using ISP" section is new.                                                                                                                                                                                                                                                          | 296  |  |  |

|           | The "Programming Failure Allowances" section was revised.                                                                                                                                                                                                                                                       | 296  |  |  |

The following table lists critical changes that were made in each revision of the chapter.

ProASIC3L FPGA Fabric User's Guide

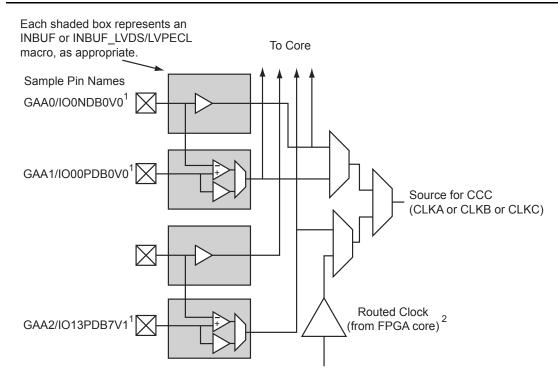

Figure 12-5 • Example Application Scenario Using AES in Fusion Devices

### FlashLock

### Additional Options for IGLOO and ProASIC3 Devices

The user also has the option of prohibiting Write operations to the FPGA array but allowing Verify operations on the FPGA array and/or Read operations on the FlashROM without the use of the FlashLock Pass Key. This option provides the user the freedom of verifying the FPGA array and/or reading the FlashROM contents after the device is programmed, without having to provide the FlashLock Pass Key. The user can incorporate AES encryption on the programming files to better enhance the level of security used.

## **Permanent Security Setting Options**

In applications where a permanent lock is not desired, yet the security settings should not be modifiable, IGLOO and ProASIC3 devices can accommodate this requirement.

This application is particularly useful in cases where a device is located at a remote location and must be reprogrammed with a design or data update. Refer to the "Application 3: Nontrusted Environment—Field Updates/Upgrades" section on page 310 for further discussion and examples of how this can be achieved.

The user must be careful when considering the Permanent FlashLock or Permanent Security Settings option. Once the design is programmed with the permanent settings, it is not possible to reconfigure the security settings already employed on the device. Therefore, exercise careful consideration before programming permanent settings.

### Permanent FlashLock

The purpose of the permanent lock feature is to provide the benefits of the highest level of security to IGLOO and ProASIC3 devices. If selected, the permanent FlashLock feature will create a permanent barrier, preventing any access to the contents of the device. This is achieved by permanently disabling Write and Verify access to the array, and Write and Read access to the FlashROM. After permanently locking the device, it has been effectively rendered one-time-programmable. This feature is useful if the intended applications do not require design or system updates to the device.

# 13 – In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

## Introduction

Microsemi's low power flash devices are all in-system programmable. This document describes the general requirements for programming a device and specific requirements for the FlashPro4/3/3X programmers<sup>1</sup>.

IGLOO, ProASIC3, SmartFusion, and Fusion devices offer a low power, single-chip, live-at-power-up solution with the ASIC advantages of security and low unit cost through nonvolatile flash technology. Each device contains 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications such as Internet Protocol (IP) addressing, user system preference storage, device serialization, or subscription-based business models. IGLOO, ProASIC3, SmartFusion, and Fusion devices offer the best in-system programming (ISP) solution, FlashLock<sup>®</sup> security features, and AES-decryption-based ISP.

## **ISP** Architecture

Low power flash devices support ISP via JTAG and require a single VPUMP voltage of 3.3 V during programming. In addition, programming via a microcontroller in a target system is also supported.

Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide.

Family-specific support:

- ProASIC3, ProASIC3E, SmartFusion, and Fusion devices support ISP.

- ProASIC3L devices operate using a 1.2 V core voltage; however, programming can be done only at 1.5 V. Voltage switching is required in-system to switch from a 1.2 V core to 1.5 V core for programming.

- IGLOO and IGLOOe V5 devices can be programmed in-system when the device is using a 1.5 V supply voltage to the FPGA core.

- IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only) or 1.5 V. IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V. Voltage switching is required in-system to switch from a 1.2 V supply (VCC,VCCI, and VJTAG) to 1.5 V for programming. The exception is that V2 devices can be programmed at 1.2 V VCC with FlashPro4.

IGLOO devices cannot be programmed in-system when the device is in Flash\*Freeze mode. The device should exit Flash\*Freeze mode and be in normal operation for programming to start. Programming operations in IGLOO devices can be achieved when the device is in normal operating mode and a 1.5 V core voltage is used.

## **JTAG 1532**

IGLOO, ProASIC3, SmartFusion, and Fusion devices support the JTAG-based IEEE 1532 standard for ISP. To start JTAG operations, the IGLOO device must exit Flash\*Freeze mode and be in normal operation before starting to send JTAG commands to the device. As part of this support, when a device is in an unprogrammed state, all user I/O pins are disabled. This is achieved by keeping the global IO\_EN

FlashPro4 replaced FlashPro3/3X in 2010 and is backward compatible with FlashPro3/3X as long as there is no connection to pin 4 on the JTAG header on the board. On FlashPro3/3X, there is no connection to pin 4 on the JTAG header; however, pin 4 is used for programming mode (Prog\_Mode) on FlashPro4. When converting from FlashPro3/3X to FlashPro4, users should make sure that JTAG connectors on system boards do not have any connection to pin 4. FlashPro3X supports discrete TCK toggling that is needed to support non-JTAG compliant devices in the chain. This feature is included in FlashPro4.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

# IEEE 1532 (JTAG) Interface

The supported industry-standard IEEE 1532 programming interface builds on the IEEE 1149.1 (JTAG) standard. IEEE 1532 defines the standardized process and methodology for ISP. Both silicon and software issues are addressed in IEEE 1532 to create a simplified ISP environment. Any IEEE 1532 compliant programmer can be used to program low power flash devices. Device serialization is not supported when using the IEEE1532 standard. Refer to the standard for detailed information about IEEE 1532.

# Security

Unlike SRAM-based FPGAs that require loading at power-up from an external source such as a microcontroller or boot PROM, Microsemi nonvolatile devices are live at power-up, and there is no bitstream required to load the device when power is applied. The unique flash-based architecture prevents reverse engineering of the programmed code on the device, because the programmed data is stored in nonvolatile memory cells. Each nonvolatile memory cell is made up of small capacitors and any physical deconstruction of the device will disrupt stored electrical charges.

Each low power flash device has a built-in 128-bit Advanced Encryption Standard (AES) decryption core, except for the 30 k gate devices and smaller. Any FPGA core or FlashROM content loaded into the device can optionally be sent as encrypted bitstream and decrypted as it is loaded. This is particularly suitable for applications where device updates must be transmitted over an unsecured network such as the Internet. The embedded AES decryption core can prevent sensitive data from being intercepted (Figure 13-1 on page 331). A single 128-bit AES Key (32 hex characters) is used to encrypt FPGA core programming data and/or FlashROM programming data in the Microsemi tools. The low power flash devices also decrypt with a single 128-bit AES Key. In addition, low power flash devices support a Message Authentication Code (MAC) for authentication of the encrypted bitstream on-chip. This allows the encrypted bitstream to be authenticated and prevents erroneous data from being programmed into the device. The FPGA core, FlashROM, and Flash Memory Blocks (FBs), in Fusion only, can be updated independently using a programming file that is AES-encrypted (cipher text) or uses plain text.

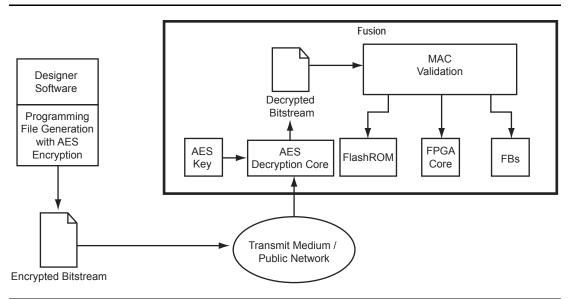

## STAPL vs. DirectC

Programming the low power flash devices is performed using DirectC or the STAPL player. Both tools use the STAPL file as an input. DirectC is a compiled language, whereas STAPL is an interpreted language. Microprocessors will be able to load the FPGA using DirectC much more quickly than STAPL. This speed advantage becomes more apparent when lower clock speeds of 8- or 16-bit microprocessors are used. DirectC also requires less memory than STAPL, since the programming algorithm is directly implemented. STAPL does have one advantage over DirectC—the ability to upgrade. When a new programming algorithm is required, the STAPL user simply needs to regenerate a STAPL file using the latest version of the Designer software and download it to the system. The DirectC user must download the latest version of DirectC from Microsemi, compile everything, and download the result into the system (Figure 15-4).

Figure 15-4 • STAPL vs. DirectC

# 17 – UJTAG Applications in Microsemi's Low Power Flash Devices

# Introduction

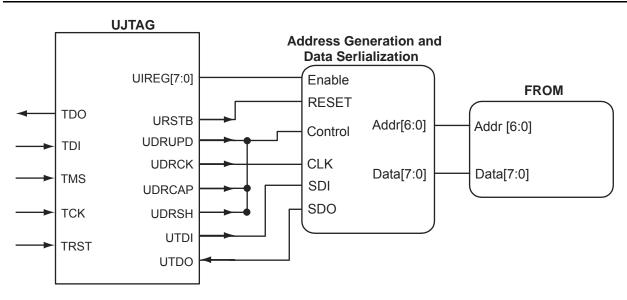

In Fusion, IGLOO, and ProASIC3 devices, there is bidirectional access from the JTAG port to the core VersaTiles during normal operation of the device (Figure 17-1). User JTAG (UJTAG) is the ability for the design to use the JTAG ports for access to the device for updates, etc. While regular JTAG is used, the UJTAG tiles, located at the southeast area of the die, are directly connected to the JTAG Test Access Port (TAP) Controller in normal operating mode. As a result, all the functional blocks of the device, such as Clock Conditioning Circuits (CCCs) with PLLs, SRAM blocks, embedded FlashROM, flash memory blocks, and I/O tiles, can be reached via the JTAG ports. The UJTAG functionality is available by instantiating the UJTAG macro directly in the source code of a design. Access to the FPGA core VersaTiles from the JTAG ports enables users to implement different applications using the TAP Controller (JTAG port). This document introduces the UJTAG tile functionality and discusses a few application examples. However, the possible applications are not limited to what is presented in this document. UJTAG can serve different purposes in many designs as an elementary or auxiliary part of the design. For detailed usage information, refer to the "Boundary Scan in Low Power Flash Devices" section on page 357.

Figure 17-1 • Block Diagram of Using UJTAG to Read FlashROM Contents

Power-Up/-Down Behavior of Low Power Flash Devices

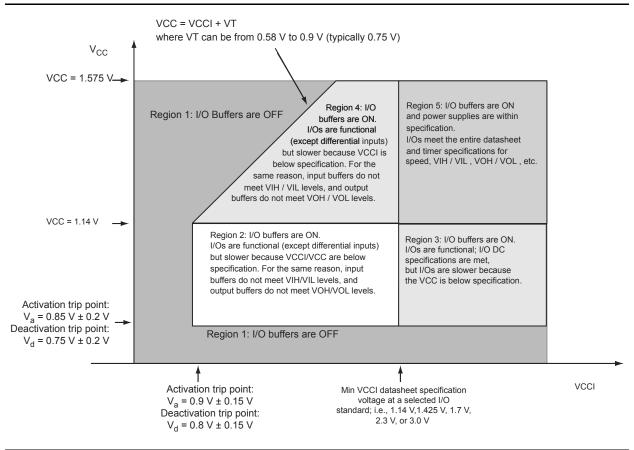

Figure 18-5 • I/O State as a Function of VCCI and VCC Voltage Levels for IGLOO V2, IGLOO nano V2, IGLOO PLUS V2, and ProASIC3L Devices Running at VCC = 1.2 V ± 0.06 V

# **B** – **Product Support**

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

## **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 650.318.8044

# **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

Visit the Customer Support website (www.microsemi.com/soc/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

## Website

You can browse a variety of technical and non-technical information on the SoC home page, at www.microsemi.com/soc.

## **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

### Email

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.

Product Support

### **My Cases**

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

### Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (soc\_tech@microsemi.com) or contact a local sales office. Sales office listings can be found at www.microsemi.com/soc/company/contact/default.aspx.

## **ITAR Technical Support**

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via soc\_tech\_itar@microsemi.com. Alternatively, within My Cases, select **Yes** in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.