Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | -                                                               |

| Total RAM Bits                 | 147456                                                          |

| Number of I/O                  | 154                                                             |

| Number of Gates                | 1000000                                                         |

| Voltage - Supply               | 1.14V ~ 1.575V                                                  |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                              |

| Package / Case                 | 208-BFQFP                                                       |

| Supplier Device Package        | 208-PQFP (28x28)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p1000l-pqg208i |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Microsemi

Flash\*Freeze Technology and Low Power Modes

# Flash Families Support the Flash\*Freeze Feature

The low power flash FPGAs listed in Table 2-1 support the Flash\*Freeze feature and the functions described in this document.

#### Table 2-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

# 3 – Global Resources in Low Power Flash Devices

## Introduction

IGLOO, Fusion, and ProASIC3 FPGA devices offer a powerful, low-delay VersaNet global network scheme and have extensive support for multiple clock domains. In addition to the Clock Conditioning Circuits (CCCs) and phase-locked loops (PLLs), there is a comprehensive global clock distribution network called a VersaNet global network. Each logical element (VersaTile) input and output port has access to these global networks. The VersaNet global networks can be used to distribute low-skew clock signals or high-fanout nets. In addition, these highly segmented VersaNet global networks contain spines (the vertical branches of the global network tree) and ribs that can reach all the VersaTiles inside their region. This allows users the flexibility to create low-skew local clock networks using spines. This document describes VersaNet global networks and discusses how to assign signals to these global networks and spines in a design flow. Details concerning low power flash device PLLs are described in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" section on page 77. This chapter describes the low power flash devices' global architecture and uses of these global networks in designs.

### **Global Architecture**

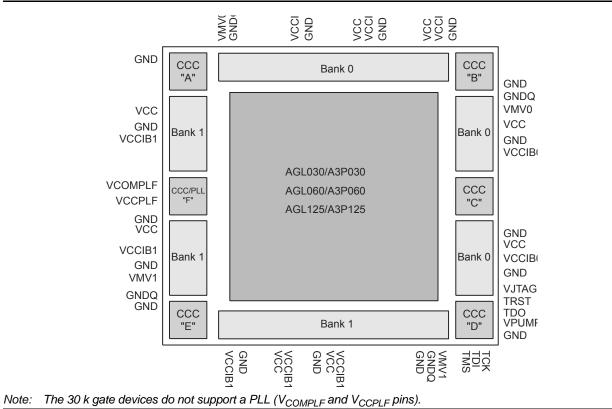

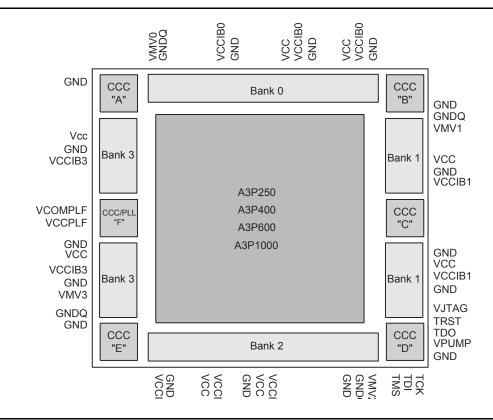

Low power flash devices offer powerful and flexible control of circuit timing through the use of global circuitry. Each chip has up to six CCCs, some with PLLs.

- In IGLOOe, ProASIC3EL, and ProASIC3E devices, all CCCs have PLLs—hence, 6 PLLs per device (except the PQ208 package, which has only 2 PLLs).

- In IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, and ProASIC3L devices, the west CCC contains a PLL core (except in 10 k through 30 k devices).

- In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.

Refer to Table 4-6 on page 100 for details. Each PLL includes delay lines, a phase shifter (0°, 90°, 180°, 270°), and clock multipliers/dividers. Each CCC has all the circuitry needed for the selection and interconnection of inputs to the VersaNet global network. The east and west CCCs each have access to three chip global lines on each side of the chip (six chip global lines total). The CCCs at the four corners each have access to three quadrant global lines in each quadrant of the chip (except in 10 k through 30 k gate devices).

The nano 10 k, 15 k, and 20 k devices support four VersaNet global resources, and 30 k devices support six global resources. The 10 k through 30 k devices have simplified CCCs called CCC-GLs.

The flexible use of the VersaNet global network allows the designer to address several design requirements. User applications that are clock-resource-intensive can easily route external or gated internal clocks using VersaNet global routing networks. Designers can also drastically reduce delay penalties and minimize resource usage by mapping critical, high-fanout nets to the VersaNet global network.

Note: Microsemi recommends that you choose the appropriate global pin and use the appropriate global resource so you can realize these benefits.

The following sections give an overview of the VersaNet global network, the structure of the global network, access point for the global networks, and the clock aggregation feature that enables a design to have very low clock skew using spines.

Global Resources in Low Power Flash Devices

#### Figure 3-18 • Globals Management GUI in Designer

- 3. Occasionally, the synthesis tool assigns a global macro to clock nets, even though the fanout is significantly less than other asynchronous signals. Select **Demote global nets whose fanout is less than** and enter a reasonable value for fanouts. This frees up some global networks from the signals that have very low fanouts. This can also be done using PDC.

- 4. Use a local clock network for the signals that do not need to go to the whole chip but should have low skew. This local clock network assignment can only be done using PDC.

- 5. Assign the I/O buffer using MVN if you have fixed I/O assignment. As shown in Figure 3-10 on page 61, there are three sets of global pins that have a hardwired connection to each global network. Do not try to put multiple CLKBUF macros in these three sets of global pins. For example, do not assign two CLKBUFs to GAA0x and GAA2x pins.

- 6. You must click **Commit** at the end of MVN assignment. This runs the pre-layout checker and checks the validity of global assignment.

- 7. Always run Compile with the **Keep existing physical constraints** option on. This uses the quadrant clock network assignment in the MVN assignment and checks if you have the desired signals on the global networks.

- 8. Run Layout and check the timing.

### Available I/O Standards

| CLKBUF_LVCMOS5                 |

|--------------------------------|

| CLKBUF_LVCMOS33 <sup>1</sup>   |

| CLKBUF_LVCMOS25 <sup>2</sup>   |

| CLKBUF_LVCMOS18                |

| CLKBUF_LVCMOS15                |

| CLKBUF_PCI                     |

| CLKBUF_PCIX <sup>3</sup>       |

| CLKBUF_GTL25 <sup>2,3</sup>    |

| CLKBUF_GTL33 <sup>2,3</sup>    |

| CLKBUF_GTLP25 <sup>2,3</sup>   |

| CLKBUF_GTLP33 <sup>2,3</sup>   |

| CLKBUF_HSTL_I <sup>2,3</sup>   |

| CLKBUF_HSTL_II <sup>2,3</sup>  |

| CLKBUF_SSTL3_I <sup>2,3</sup>  |

| CLKBUF_SSTL3_II <sup>2,3</sup> |

| CLKBUF_SSTL2_I <sup>2,3</sup>  |

| CLKBUF_SSTL2_II <sup>2,3</sup> |

| CLKBUF_LVDS <sup>4,5</sup>     |

| CLKBUF_LVPECL <sup>5</sup>     |

|                                |

Notes:

- 1. By default, the CLKBUF macro uses 3.3 V LVTTL I/O technology. For more details, refer to the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.

- 2. I/O standards only supported in ProASIC3E and IGLOOe families.

- 3. I/O standards only supported in the following Fusion devices: AFS600 and AFS1500.

- 4. B-LVDS and M-LVDS standards are supported by CLKBUF\_LVDS.

- 5. Not supported for IGLOO nano and ProASIC3 nano devices.

### **Global Synthesis Constraints**

The Synplify<sup>®</sup> synthesis tool, by default, allows six clocks in a design for Fusion, IGLOO, and ProASIC3. When more than six clocks are needed in the design, a user synthesis constraint attribute, syn\_global\_buffers, can be used to control the maximum number of clocks (up to 18) that can be inferred by the synthesis engine.

High-fanout nets will be inferred with clock buffers and/or internal clock buffers. If the design consists of CCC global buffers, they are included in the count of clocks in the design.

The subsections below discuss the clock input source (global buffers with no programmable delays) and the clock conditioning functional block (global buffers with programmable delays and/or PLL function) in detail.

### Microsemi

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

Dividers n and m (the input divider and feedback divider, respectively) provide integer frequency division factors from 1 to 128. The output dividers u, v, and w provide integer division factors from 1 to 32. Frequency scaling of the reference clock CLKA is performed according to the following formulas:

$$f_{GLA} = f_{CLKA} \times m / (n \times u) - GLA Primary PLL Output Clock$$

$$EQ 4-1$$

$$f_{GLB} = f_{YB} = f_{CLKA} \times m / (n \times v) - GLB Secondary 1 PLL Output Clock(s)$$

$$EQ 4-2$$

$$f_{GLC} = f_{YC} = f_{CLKA} \times m / (n \times w) - GLC$$

Secondary 2 PLL Output Clock(s)

EQ 4-3

SmartGen provides a user-friendly method of generating the configured PLL netlist, which includes automatically setting the division factors to achieve the closest possible match to the requested frequencies. Since the five output clocks share the *n* and *m* dividers, the achievable output frequencies are interdependent and related according to the following formula:

$$f_{GLA} = f_{GLB} \times (v / u) = f_{GLC} \times (w / u)$$

EQ 4-4

### **Clock Delay Adjustment**

There are a total of seven configurable delay elements implemented in the PLL architecture.

Two of the delays are located in the feedback path, entitled System Delay and Feedback Delay. System Delay provides a fixed delay of 2 ns (typical), and Feedback Delay provides selectable delay values from 0.6 ns to 5.56 ns in 160 ps increments (typical). For PLLs, delays in the feedback path will effectively advance the output signal from the PLL core with respect to the reference clock. Thus, the System and Feedback delays generate negative delay on the output clock. Additionally, each of these delays can be independently bypassed if necessary.

The remaining five delays perform traditional time delay and are located at each of the outputs of the PLL. Besides the fixed global driver delay of 0.755 ns for each of the global networks, the global multiplexer outputs (GLA, GLB, and GLC) each feature an additional selectable delay value, as given in Table 4-7.

| Device                | Typical | Starting Values | Increments | Ending Value |

|-----------------------|---------|-----------------|------------|--------------|

| ProASIC3              | 200 ps  | 0 to 735 ps     | 200 ps     | 6.735 ns     |

| IGLOO/ProASIC3L 1.5 V | 360 ps  | 0 to 1.610 ns   | 360 ps     | 12.410 ns    |

| IGLOO/ProASIC3L 1.2 V | 580 ps  | 0 to 2.880 ns   | 580 ps     | 20.280 ns    |

Table 4-7 • Delay Values in Libero SoC Software per Device Family

The additional YB and YC signals have access to a selectable delay from 0.6 ns to 5.56 ns in 160 ps increments (typical). This is the same delay value as the CLKDLY macro. It is similar to CLKDLY, which bypasses the PLL core just to take advantage of the phase adjustment option with the delay value.

The following parameters must be taken into consideration to achieve minimum delay at the outputs (GLA, GLB, GLC, YB, and YC) relative to the reference clock: routing delays from the PLL core to CCC outputs, core outputs and global network output delays, and the feedback path delay. The feedback path delay acts as a time advance of the input clock and will offset any delays introduced beyond the PLL core output. The routing delays are determined from back-annotated simulation and are configuration-dependent.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

#### **External Feedback Configuration**

For certain applications, such as those requiring generation of PCB clocks that must be matched with existing board delays, it is useful to implement an external feedback, EXTFB. The Phase Detector of the PLL core will receive CLKA and EXTFB as inputs. EXTFB may be processed by the fixed System Delay element as well as the *M* divider element. The EXTFB option is currently not supported.

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

| Name                                          | : test_pll            |

|-----------------------------------------------|-----------------------|

| Family                                        | : ProASIC3E           |

| Output Format                                 | : VHDL                |

| Type                                          | : Static PLL          |

| Input Freq(MHz)                               | : 10.000              |

| CLKA Source                                   | : Hardwired I/O       |

| Feedback Delay Value Index                    | : 1                   |

| Feedback Mux Select                           | : 2                   |

| XDLY Mux Select                               | -<br>: No             |

| Primary Freq(MHz)                             | : 33.000              |

| Primary PhaseShift                            | : 0                   |

| Primary Delay Value Index                     | : 1                   |

| Primary Mux Select                            | : 4                   |

| Secondary1 Freq(MHz)                          | : 66.000              |

| Use GLB                                       | : YES                 |

| Use YB                                        | : YES                 |

| GLB Delay Value Index                         | : 1                   |

| YB Delay Value Index                          | · 1                   |

| Secondaryl PhaseShift                         | : 0                   |

| Secondary1 Mux Select                         | : 4                   |

| Secondary1 Mux Select<br>Secondary2 Freq(MHz) | : 101.000             |

| Use GLC                                       | : YES                 |

| Use YC                                        | : NO                  |

| GLC Delay Value Index                         | : NO<br>: 1           |

| YC Delay Value Index                          | · 1                   |

| _                                             | : 0                   |

| Secondary2 PhaseShift                         | : 4                   |

| Secondary2 Mux Select                         | • 4                   |

|                                               |                       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

| Primary Clock frequency 33.333                |                       |

| Primary Clock Phase Shift 0.000               |                       |

| Primary Clock Output Delay from               | n CLKA U.180          |

|                                               |                       |

| Secondaryl Clock frequency 66.6               |                       |

| Secondaryl Clock Phase Shift 0.               |                       |

| Secondaryl Clock Global Output                |                       |

| Secondaryl Clock Core Output De               | elay from CLKA 0.625  |

|                                               | 000                   |

| Secondary2 Clock frequency 100.               |                       |

| Secondary2 Clock Phase Shift 0.               |                       |

| Secondary2 Clock Global Output                | Delay from CLKA 0.180 |

|                                               |                       |

Below is an example Verilog HDL description of a legal PLL core configuration generated by SmartGen:

module test\_pll(POWERDOWN,CLKA,LOCK,GLA); input POWERDOWN, CLKA; output LOCK,GLA;

FlashROM in Microsemi's Low Power Flash Devices

# **Programming and Accessing FlashROM**

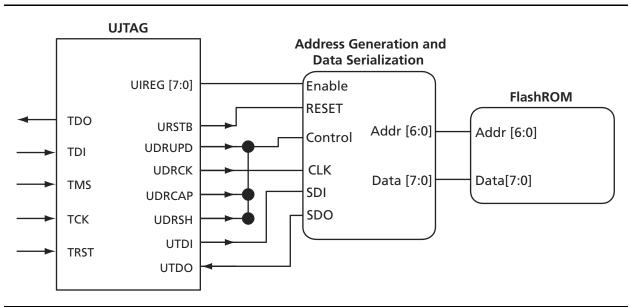

The FlashROM content can only be programmed via JTAG, but it can be read back selectively through the JTAG programming interface, the UJTAG interface, or via direct FPGA core addressing. The pages of the FlashROM can be made secure to prevent read-back via JTAG. In that case, read-back on these secured pages is only possible by the FPGA core fabric or via UJTAG.

A 7-bit address from the FPGA core defines which of the eight pages (three MSBs) is being read, and which of the 16 bytes within the selected page (four LSBs) are being read. The FlashROM content can be read on a random basis; the access time is 10 ns for a device supporting commercial specifications. The FPGA core will be powered down during writing of the FlashROM content. FPGA power-down during FlashROM programming is managed on-chip, and FPGA core functionality is not available during programming of the FlashROM. Table 5-2 summarizes various FlashROM access scenarios.

| Access Mode | FlashROM Read | FlashROM Write |

|-------------|---------------|----------------|

| JTAG        | Yes           | Yes            |

| UJTAG       | Yes           | No             |

| FPGA core   | Yes           | No             |

Figure 5-6 shows the accessing of the FlashROM using the UJTAG macro. This is similar to FPGA core access, where the 7-bit address defines which of the eight pages (three MSBs) is being read and which of the 16 bytes within the selected page (four LSBs) are being read. Refer to the "UJTAG Applications in Microsemi's Low Power Flash Devices" section on page 363 for details on using the UJTAG macro to read the FlashROM.

Figure 5-7 on page 139 and Figure 5-8 on page 139 show the FlashROM access from the JTAG port. The FlashROM content can be read on a random basis. The three-bit address defines which page is being read or updated.

Figure 5-6 • Block Diagram of Using UJTAG to Read FlashROM Contents

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## Software Support

The SmartGen core generator is the easiest way to select and configure the memory blocks (Figure 6-12). SmartGen automatically selects the proper memory block type and aspect ratio, and cascades the memory blocks based on the user's selection. SmartGen also configures any additional signals that may require tie-off.

SmartGen will attempt to use the minimum number of blocks required to implement the desired memory. When cascading, SmartGen will configure the memory for width before configuring for depth. For example, if the user requests a 256×8 FIFO, SmartGen will use a 512×9 FIFO configuration, not 256×18.

Figure 6-12 • SmartGen Core Generator Interface

ProASIC3L FPGA Fabric User's Guide

Figure 7-20 • Naming Conventions of IGLOO and ProASIC3 Devices with Four I/O Banks – Top View

**Revision** 4

### GTL 2.5 V (Gunning Transceiver Logic 2.5 V)

This is a low power standard (JESD 8-3) for electrical signals used in CMOS circuits that allows for low electromagnetic interference at high transfer speeds. It has a voltage swing between 0.4 V and 1.2 V and typically operates at speeds of between 20 and 40 MHz. VCCI must be connected to 2.5 V. The reference voltage (VREF) is 0.8 V.

### GTL 3.3 V (Gunning Transceiver Logic 3.3 V)

This is the same as GTL 2.5 V above, except VCCI must be connected to 3.3 V.

#### GTL+ (Gunning Transceiver Logic Plus)

This is an enhanced version of GTL that has defined slew rates and higher voltage levels. It requires a differential amplifier input buffer and an open-drain output buffer. Even though the output is open-drain, VCCI must be connected to either 2.5 V or 3.3 V. The reference voltage (VREF) is 1 V.

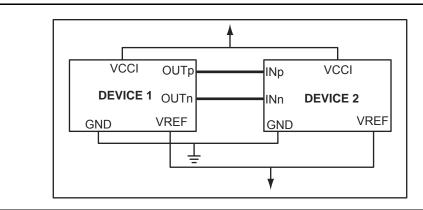

### **Differential Standards**

These standards require two I/Os per signal (called a "signal pair"). Logic values are determined by the potential difference between the lines, not with respect to ground. This is why differential drivers and receivers have much better noise immunity than single-ended standards. The differential interface standards offer higher performance and lower power consumption than their single-ended counterparts. Two I/O pins are used for each data transfer channel. Both differential standards require resistor termination.

Figure 8-8 • Differential Topology

### LVPECL (Low-Voltage Positive Emitter Coupled Logic)

LVPECL requires that one data bit be carried through two signal lines; therefore, two pins are needed per input or output. It also requires external resistor termination. The voltage swing between the two signal lines is approximately 850 mV. When the power supply is +3.3 V, it is commonly referred to as Low-Voltage PECL (LVPECL). Refer to the device datasheet for the full implementation of the LVPECL transmitter and receiver.

### LVDS (Low-Voltage Differential Signal)

LVDS is a moderate-speed differential signaling system, in which the transmitter generates two different voltages that are compared at the receiver. LVDS uses a differential driver connected to a terminated receiver through a constant-impedance transmission line. It requires that one data bit be carried through two signal lines; therefore, the user will need two pins per input or output. It also requires external resistor termination. The voltage swing between the two signal lines is approximately 350 mV.  $V_{CCI}$  is 2.5 V. Low power flash devices contain dedicated circuitry supporting a high-speed LVDS standard that has its own user specification. Refer to the device datasheet for the full implementation of the LVDS transmitter and receiver.

I/O Software Control in Low Power Flash Devices

## Implementing I/Os in Microsemi Software

Microsemi Libero SoC software is integrated with design entry tools such as the SmartGen macro builder, the ViewDraw schematic entry tool, and an HDL editor. It is also integrated with the synthesis and Designer tools. In this section, all necessary steps to implement the I/Os are discussed.

### **Design Entry**

There are three ways to implement I/Os in a design:

- 1. Use the SmartGen macro builder to configure I/Os by generating specific I/O library macros and then instantiating them in top-level code. This is especially useful when creating I/O bus structures.

- 2. Use an I/O buffer cell in a schematic design.

- 3. Manually instantiate specific I/O macros in the top-level code.

If technology-specific macros, such as INBUF\_LVCMOS33 and OUTBUF\_PCI, are used in the HDL code or schematic, the user will not be able to change the I/O standard later on in Designer. If generic I/O macros are used, such as INBUF, OUTBUF, TRIBUF, CLKBUF, and BIBUF, the user can change the I/O standard using the Designer I/O Attribute Editor tool.

#### Using SmartGen for I/O Configuration

The SmartGen tool in Libero SoC provides a GUI-based method of configuring the I/O attributes. The user can select certain I/O attributes while configuring the I/O macro in SmartGen. The steps to configure an I/O macro with specific I/O attributes are as follows:

- 1. Open Libero SoC.

- 2. On the left-hand side of the Catalog View, select I/O, as shown in Figure 9-2.

Figure 9-2 • SmartGen Catalog

## **Programming Support in Flash Devices**

The flash FPGAs listed in Table 11-1 support flash in-system programming and the functions described in this document.

| Series      | Family <sup>*</sup>     | Description                                                                                                                                                                                                   |  |

|-------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO IGLOO |                         | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                                             |  |

|             | IGLOOe                  | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                                         |  |

| IGLOO nano  |                         | The industry's lowest-power, smallest-size solution, supporting 1.2 V to 1.5 V core voltage with Flash*Freeze technology                                                                                      |  |

|             | IGLOO PLUS              | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                                    |  |

| ProASIC3    | ProASIC3                | Low power, high-performance 1.5 V FPGAs                                                                                                                                                                       |  |

|             | ProASIC3E               | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                                      |  |

|             | ProASIC3 nano           | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                                           |  |

|             | ProASIC3L               | ProASIC3 FPGAs supporting 1.2 V to 1.5 V core voltage with Flash*Freeze technology                                                                                                                            |  |

|             | RT ProASIC3             | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                                   |  |

|             | Military ProASIC3/EL    | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                                         |  |

|             | Automotive ProASIC3     | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                                          |  |

| SmartFusion | SmartFusion             | Mixed-signal FPGA integrating FPGA fabric, programmable microcontroller subsystem (MSS), including programmable analog and ARM <sup>®</sup> Cortex™-M3 hard processor and flash memory in a monolithic device |  |

| Fusion      | Fusion                  | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device                |  |

| ProASIC     | ProASIC                 | First generation ProASIC devices                                                                                                                                                                              |  |

|             | ProASIC <sup>PLUS</sup> | Second generation ProASIC devices                                                                                                                                                                             |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 11-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 11-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

### **Programming File Header Definition**

In each STAPL programming file generated, there will be information about how the AES key and FlashLock Pass Key are configured. Table 12-8 shows the header definitions in STAPL programming files for different security levels.

| Security Level                                                     | STAPL File Header Definition          |

|--------------------------------------------------------------------|---------------------------------------|

| No security (no FlashLock Pass Key or AES key)                     | NOTE "SECURITY" "Disable";            |

| FlashLock Pass Key with no AES key                                 | NOTE "SECURITY" "KEYED ";             |

| FlashLock Pass Key with AES key                                    | NOTE "SECURITY" "KEYED ENCRYPT ";     |

| Permanent Security Settings option enabled                         | NOTE "SECURITY" "PERMLOCK ENCRYPT ";  |

| AES-encrypted FPGA array (for programming updates)                 | NOTE "SECURITY" "ENCRYPT CORE ";      |

| AES-encrypted FlashROM (for programming updates)                   | NOTE "SECURITY" "ENCRYPT FROM ";      |

| AES-encrypted FPGA array and FlashROM (for<br>programming updates) | NOTE "SECURITY" "ENCRYPT FROM CORE "; |

### **Example File Headers**

STAPL Files Generated with FlashLock Key and AES Key Containing Key Information

- FlashLock Key / AES key indicated in STAPL file header definition

- · Intended ONLY for secured/trusted environment programming applications

```

_____

NOTE "CREATOR" "Designer Version: 6.1.1.108";

NOTE "DEVICE" "A3PE600";

NOTE "PACKAGE" "208 PQFP";

NOTE "DATE" "2005/04/08";

NOTE "STAPL_VERSION" "JESD71";

NOTE "IDCODE" "$123261CF";

NOTE "DESIGN" "counter32";

NOTE "CHECKSUM" "$EDB9";

NOTE "SAVE_DATA" "FRomStream";

NOTE "SECURITY" "KEYED ENCRYPT ";

NOTE "ALG_VERSION" "1";

NOTE "MAX FREO" "20000000";

NOTE "SILSIG" "$0000000";

NOTE "PASS_KEY" "$00123456789012345678901234567890";

NOTE "AES_KEY" "$ABCDEFABCDEFABCDEFABCDEFABCDEFAB;

_____

```

## **Related Documents**

### **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                    |     |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                  |     |

| v1.5<br>(August 2009)   | The "CoreMP7 Device Security" section was removed from "Security in ARM-<br>Enabled Low Power Flash Devices", since M7-enabled devices are no longer<br>supported.                                                                         |     |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs.                                                                                                                                                         |     |

| v1.3<br>(October 2008)  | The "Security Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                           |     |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> |     |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                                                      | N/A |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 302 |

# List of Changes

| Date                   | Changes                                                                                                                                               |     |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| July 2010              | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.             |     |

| v1.1<br>(October 2008) | The "Introduction" was revised to include information about the core supply voltage range of operation in V2 devices.                                 |     |

|                        | IGLOO nano device support was added to Table 14-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit.                                           | 342 |

|                        | The "Circuit Description" section was updated to include IGLOO PLUS core operation from 1.2 V to 1.5 V in 50 mV increments.                           | 343 |

| v1.0<br>(August 2008)  | The "Microsemi's Flash Families Support Voltage Switching Circuit" section was revised to include new families and make the information more concise. |     |

The following table lists critical changes that were made in each revision of the chapter.

# Microsemi

Microprocessor Programming of Microsemi's Low Power Flash Devices

# List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                    |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| September 2012          | The "Security" section was modified to clarify that Microsemi does not support read-back of FPGA core-programmed data (SAR 41235).                                                                                                         |  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                  |  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 15-1 • Flash-Based FPGAs.                                                                                                                                                         |  |

| v1.3<br>(October 2008)  | The "Microprocessor Programming Support in Flash Devices" section was revised to include new families and make the information more concise.                                                                                               |  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 15-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> |  |

| v1.1<br>(March 2008)    |                                                                                                                                                                                                                                            |  |

## **UJTAG Macro**

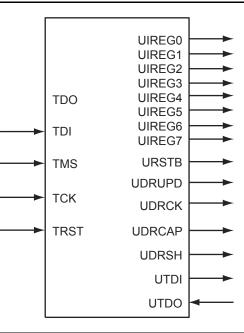

The UJTAG tiles can be instantiated in a design using the UJTAG macro from the Fusion, IGLOO, or ProASIC3 macro library. Note that "UJTAG" is a reserved name and cannot be used for any other userdefined blocks. A block symbol of the UJTAG tile macro is presented in Figure 17-2. In this figure, the ports on the left side of the block are connected to the JTAG TAP Controller, and the right-side ports are accessible by the FPGA core VersaTiles. The TDI, TMS, TDO, TCK, and TRST ports of UJTAG are only provided for design simulation purposes and should be treated as external signals in the design netlist. However, these ports must NOT be connected to any I/O buffer in the netlist. Figure 17-3 on page 366 illustrates the correct connection of the UJTAG macro to the user design netlist. Microsemi Designer software will automatically connect these ports to the TAP during place-and-route. Table 17-2 gives the port descriptions for the rest of the UJTAG ports:

| Port        | Description                                                                                                                                                                                                                                                                                |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| UIREG [7:0] | This 8-bit bus carries the contents of the JTAG Instruction Register of each device. Instruction Register values 16 to 127 are not reserved and can be employed as user-defined instructions.                                                                                              |  |  |

| URSTB       | URSTB is an active-low signal and will be asserted when the TAP Controller is in Test-Logic-Rese<br>mode. URSTB is asserted at power-up, and a power-on reset signal resets the TAP Controller. URSTI<br>will stay asserted until an external TAP access changes the TAP Controller state. |  |  |

| UTDI        | This port is directly connected to the TAP's TDI signal.                                                                                                                                                                                                                                   |  |  |

| UTDO        | This port is the user TDO output. Inputs to the UTDO port are sent to the TAP TDO output MUX when the IR address is in user range.                                                                                                                                                         |  |  |

| UDRSH       | Active-high signal enabled in the ShiftDR TAP state                                                                                                                                                                                                                                        |  |  |

| UDRCAP      | Active-high signal enabled in the CaptureDR TAP state                                                                                                                                                                                                                                      |  |  |

| UDRCK       | This port is directly connected to the TAP's TCK signal.                                                                                                                                                                                                                                   |  |  |

| UDRUPD      | Active-high signal enabled in the UpdateDR TAP state                                                                                                                                                                                                                                       |  |  |

Table 17-2 • UJTAG Port Descriptions

Figure 17-2 • UJTAG Tile Block Symbol

Power-Up/-Down Behavior of Low Power Flash Devices

#### Figure 18-3 • I/O State when VCCI Is Powered before VCC

#### **Power-Up to Functional Time**

At power-up, device I/Os exit the tristate mode and become functional once the last voltage supply in the power-up sequence (VCCI or VCC) reaches its functional activation level. The power-up–to–functional time is the time it takes for the last supply to power up from zero to its functional level. Note that the functional level of the power supply during power-up may vary slightly within the specification at different ramp-rates. Refer to Table 18-2 for the functional level of the voltage supplies at power-up.

Typical I/O behavior during power-up-to-functional time is illustrated in Figure 18-2 on page 377 and Figure 18-3.

| Device                                                                                                      | VCC Functional<br>Activation Level (V) | VCCI Functional<br>Activation Level (V) |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano,<br>IGLOO PLUS, and ProASIC3L devices running at<br>VCC = 1.5 V* | 0.85 V ± 0.25 V                        | 0.9 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and<br>ProASIC3L devices running at VCC = 1.2 V*                             | 0.85 V ± 0.2 V                         | 0.9 V ± 0.15 V                          |

#### Table 18-2 • Power-Up Functional Activation Levels for VCC and VCCI

Note: \*V5 devices will require a 1.5 V VCC supply, whereas V2 devices can utilize either a 1.2 V or 1.5 V VCC.

Microsemi's low power flash devices meet Level 0 LAPU; that is, they can be functional prior to  $V_{CC}$  reaching the regulated voltage required. This important advantage distinguishes low power flash devices from their SRAM-based counterparts. SRAM-based FPGAs, due to their volatile technology, require hundreds of milliseconds after power-up to configure the design bitstream before they become functional. Refer to Figure 18-4 on page 379 and Figure 18-5 on page 380 for more information.