ĿХF

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 36864                                                          |

| Number of I/O                  | 97                                                             |

| Number of Gates                | 250000                                                         |

| Voltage - Supply               | 1.14V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                |

| Package / Case                 | 144-LBGA                                                       |

| Supplier Device Package        | 144-FPBGA (13x13)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p250l-1fgg144 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ProASIC3L FPGA Fabric User's Guide

|   | Device-Specific Layout                                                   | . 94 |

|---|--------------------------------------------------------------------------|------|

|   | PLL Core Specifications                                                  | 100  |

|   | Functional Description                                                   | 101  |

|   | Software Configuration                                                   | 112  |

|   | Detailed Usage Information                                               | 120  |

|   | Recommended Board-Level Considerations                                   | 128  |

|   | Conclusion                                                               | 129  |

|   | Related Documents                                                        | 129  |

|   | List of Changes                                                          | 129  |

|   |                                                                          |      |

| 5 | FlashROM in Microsemi's Low Power Flash Devices                          |      |

|   | Introduction                                                             | 133  |

|   | Architecture of User Nonvolatile FlashROM                                | 133  |

|   | FlashROM Support in Flash-Based Devices                                  | 134  |

|   | FlashROM Applications                                                    | 136  |

|   | FlashROM Security                                                        | 137  |

|   | Programming and Accessing FlashROM                                       | 138  |

|   | FlashROM Design Flow                                                     |      |

|   | Custom Serialization Using FlashROM                                      |      |

|   | Conclusion                                                               |      |

|   | Related Documents                                                        |      |

|   | List of Changes                                                          |      |

|   |                                                                          | 110  |

| 6 | SRAM and FIFO Memories in Microsemi's Low Power Flash Devices            | 147  |

|   | Introduction                                                             | 147  |

|   | Device Architecture                                                      | 147  |

|   | SRAM/FIFO Support in Flash-Based Devices                                 |      |

|   | SRAM and FIFO Architecture                                               |      |

|   | Memory Blocks and Macros                                                 |      |

|   | Initializing the RAM/FIFO                                                |      |

|   | Software Support                                                         |      |

|   |                                                                          |      |

|   | List of Changes                                                          |      |

|   |                                                                          | 175  |

| 7 | I/O Structures in IGLOO and ProASIC3 Devices                             | 175  |

|   |                                                                          |      |

|   | Low Power Flash Device I/O Support                                       |      |

|   | Advanced I/Os—IGLOO, ProASIC3L, and ProASIC3                             |      |

|   |                                                                          |      |

|   | I/O Standards                                                            |      |

|   | I/O Features                                                             |      |

|   | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout |      |

|   | I/O Software Support                                                     |      |

|   |                                                                          |      |

|   | User I/O Naming Convention                                               |      |

|   | Board-Level Considerations                                               |      |

|   |                                                                          |      |

|   | Related Documents                                                        |      |

|   | List of Changes                                                          | 210  |

| 8 | I/O Structures in IGLOOe and ProASIC3E Devices                           | 213  |

| - |                                                                          |      |

Flash\*Freeze Technology and Low Power Modes

# **Sleep and Shutdown Modes**

### **Sleep Mode**

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs support Sleep mode when device functionality is not required. In Sleep mode,  $V_{CC}$  (core voltage),  $V_{JTAG}$  (JTAG DC voltage), and VPUMP (programming voltage) are grounded, resulting in the FPGA core being turned off to reduce power consumption. While the device is in Sleep mode, the rest of the system can still be operating and driving the input buffers of the device. The driven inputs do not pull up the internal power planes, and the current draw is limited to minimal leakage current.

Table 2-7 shows the power supply status in Sleep mode.

#### Table 2-7 • Sleep Mode—Power Supply Requirement for IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 Devices

| Power Supplies | Power Supply State |

|----------------|--------------------|

| VCC            | Powered off        |

| VCCI = VMV     | Powered on         |

| VJTAG          | Powered off        |

| VPUMP          | Powered off        |

Refer to the "Power-Up/-Down Behavior" section on page 33 for more information about I/O states during Sleep mode and the timing diagram for entering and exiting Sleep mode.

## Shutdown Mode

Shutdown mode is supported for all IGLOO nano and IGLOO PLUS devices as well the following IGLOO/e devices: AGL015, AGL030, AGLE600, AGLE3000, and A3PE3000L. Shutdown mode can be used by turning off all power supplies when the device function is not needed. Cold-sparing and hot-insertion features enable these devices to be powered down without turning off the entire system. When power returns, the live-at-power-up feature enables operation of the device after reaching the voltage activation point.

- · The device is reset upon exiting Flash\*Freeze mode or internal state saving is not required.

- State saving is required, but data and clock management is performed external to the FPGA. In other words, incoming data is externally guaranteed and held valid prior to entering Flash\*Freeze mode.

Type 2 Flash\*Freeze mode is ideally suited for applications with the following design criteria:

- Entering Flash\*Freeze mode is dependent on an internal or external signal in addition to the external FF pin.

- State saving is required and incoming data is not externally guaranteed valid.

- The designer wants to use his/her own Flash\*Freeze management IP for clock and data management.

- The designer wants to use his/her own Flash\*Freeze management logic for clock and data management.

- Internal housekeeping is required prior to entering Flash\*Freeze mode. Housekeeping activities

may include loading data to SRAM, system shutdown, completion of current task, or ensuring

valid Flash\*Freeze pin assertion.

There is no downside to type 2 mode, and Microsemi's Flash\*Freeze management IP offers a very low tile count clock and data management solution. Microsemi's recommendation for most designs is to use type 2 Flash\*Freeze mode with Flash\*Freeze management IP.

### **Design Solutions**

#### Clocks

- Microsemi recommends using a completely synchronous design in Type 2 mode with Flash\*Freeze management IP cleanly gating all internal and external clocks. This will prevent narrow pulses upon entrance and exit from Flash\*Freeze mode (Figure 2-5 on page 30).

- Upon entering Flash\*Freeze mode, external clocks become tied off High, internal to the clock pin (unless hold state is used on IGLOO nano or IGLOO PLUS), and PLLs are turned off. Any clock that is externally Low will realize a Low to High transition internal to the device while entering Flash\*Freeze. If clocks will float during Flash\*Freeze mode, Microsemi recommends using the weak pull-up feature. If clocks will continue to drive the device during Flash\*Freeze mode, the clock gating (filter) available in Flash\*Freeze management IP can help to filter unwanted narrow clock pulses upon Flash\*Freeze mode entry and exit.

- Clocks may continue to drive FPGA pins while the device is in Flash\*Freeze mode, with virtually

no power consumption. The weak pull-up/-down configuration will result in unnecessary power

consumption if used in this scenario.

- Floating clocks can cause totem pole currents on the input I/O circuitry when the device is in

active mode. If clocks are externally gated prior to entering Flash\*Freeze mode, Microsemi

recommends gating them to a known value (preferably '1', to avoid a possible narrow pulse upon

Flash\*Freeze mode exit), and not leaving them floating. However, during Flash\*Freeze mode, all

inputs and clocks are internally tied off to prevent totem pole currents, so they can be left floating.

- Upon exiting Flash\*Freeze mode, the design must allow maximum acquisition time for the PLL to acquire the lock signal, and for a PLL clock to become active. If a PLL output clock is used as the primary clock for Flash\*Freeze management IP, it is important to note that the clock gating circuit will only release other clocks after the primary PLL output clock becomes available.

## Spine Access

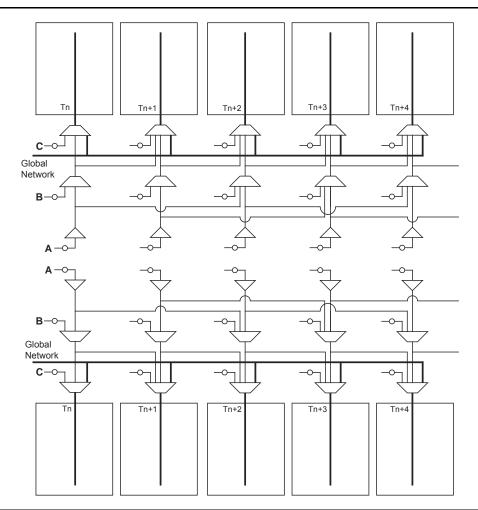

The physical location of each spine is identified by the letter T (top) or B (bottom) and an accompanying number (T*n* or B*n*). The number *n* indicates the horizontal location of the spine; 1 refers to the first spine on the left side of the die. Since there are six chip spines in each spine tree, there are up to six spines available for each combination of T (or B) and *n* (for example, six T1 spines). Similarly, there are three quadrant spines available for each combination of T (or B) and *n* (for example, four T1 spines), as shown in Figure 3-7.

Figure 3-7 • Chip Global Aggregation

A spine is also called a local clock network, and is accessed by the dedicated global MUX architecture. These MUXes define how a particular spine is driven. Refer to Figure 3-8 on page 60 for the global MUX architecture. The MUXes for each chip global spine are located in the middle of the die. Access to the top and bottom chip global spine is available from the middle of the die. There is no control dependency between the top and bottom spines. If a top spine, T1, of a chip global network is assigned to a net, B1 is not wasted and can be used by the global clock network. The signal assigned only to the top or bottom spine cannot access the middle two rows of the architecture. However, if a spine is using the top and bottom at the same time (T1 and B1, for instance), the previous restriction is lifted.

The MUXes for each quadrant global spine are located in the north and south sides of the die. Access to the top and bottom quadrant global spines is available from the north and south sides of the die. Since the MUXes for quadrant spines are located in the north and south sides of the die, you should not try to drive T1 and B1 quadrant spines from the same signal.

Global Resources in Low Power Flash Devices

### **Global Macro and Placement Selections**

Low power flash devices provide the flexibility of choosing one of the three global input pad locations available to connect to a global / quadrant global network. For 60K gate devices and above, if the single-ended I/O standard is chosen, there is flexibility to choose one of the global input pads (the first, second, and fourth input). Once chosen, the other I/O locations are used as regular I/Os. If the differential I/O standard is chosen, the first and second inputs are considered as paired, and the third input is paired with a regular I/O. The user then has the choice of selecting one of the two sets to be used as the global input source. There is also the option to allow an internal clock signal to feed the global network. A multiplexer tree selects the appropriate global input for routing to the desired location. Note that the global I/O pads do not need to feed the global network; they can also be used as regular I/O pads.

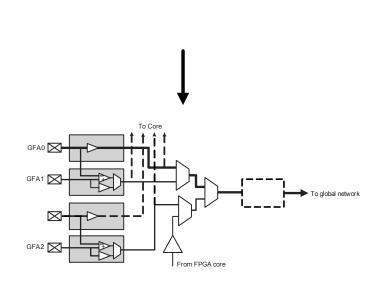

### Hardwired I/O Clock Source

Hardwired I/O refers to global input pins that are hardwired to the multiplexer tree, which directly accesses the global network. These global input pins have designated pin locations and are indicated with the I/O naming convention Gmn (m refers to any one of the positions where the global buffers is available, and n refers to any one of the three global input MUXes and the pin number of the associated global location, m). Choosing this option provides the benefit of directly connecting to the global buffers, which provides less delay. See Figure 3-11 for an example illustration of the connections, shown in red. If a CLKBUF macro is initiated, the clock input can be placed at one of nine dedicated global input pin locations: GmA0, GmA1, GmA2, GmB0, GmB1, GmB2, GmC0, GmC1, or GmC2. Note that the placement of the global will determine whether you are using chip global or quadrant global. For example, if the CLKBIF is placed in one of the GF pin locations, it will use the chip global network; if the CLKBIF is placed in one of the GA pin locations, it will use the chip global network. This is shown in Figure 3-12 on page 65 and Figure 3-13 on page 65.

Figure 3-11 • CLKBUF Macro

ProASIC3L FPGA Fabric User's Guide

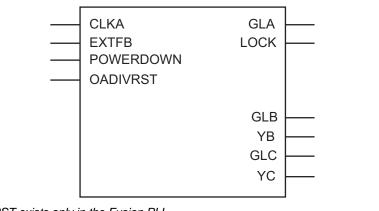

Note: OAVDIVRST exists only in the Fusion PLL.

#### Figure 3-15 • PLLs in Low Power Flash Devices

You can use the syn\_global\_buffers attribute in Synplify to specify a maximum number of global macros to be inserted in the netlist. This can also be used to restrict the number of global buffers inserted. In the Synplicity 8.1 version or newer, a new attribute, syn\_global\_minfanout, has been added for low power flash devices. This enables you to promote only the high-fanout signal to global. However, be aware that you can only have six signals assigned to chip global networks, and the rest of the global signals should be assigned to quadrant global networks. So, if the netlist has 18 global macros, the remaining 12 global macros should have fanout that allows the instances driven by these globals to be placed inside a quadrant.

### **Global Promotion and Demotion Using PDC**

The HDL source file or schematic is the preferred place for defining which signals should be assigned to a clock network using clock macro instantiation. This method is preferred because it is guaranteed to be honored by the synthesis tools and Designer software and stop any replication on this net by the synthesis tool. Note that a signal with fanout may have logic replication if it is not promoted to global during synthesis. In that case, the user cannot promote that signal to global using PDC. See Synplicity Help for details on using this attribute. To help you with global management, Designer allows you to promote a signal to a global network or demote a global macro to a regular macro from the user netlist using the compile options and/or PDC commands.

The following are the PDC constraints you can use to promote a signal to a global network:

1. PDC syntax to promote a regular net to a chip global clock:

assign\_global\_clock -net netname

The following will happen during promotion of a regular signal to a global network:

- If the net is external, the net will be driven by a CLKINT inserted automatically by Compile.

- The I/O macro will not be changed to CLKBUF macros.

- If the net is an internal net, the net will be driven by a CLKINT inserted automatically by Compile.

- 2. PDC syntax to promote a net to a quadrant clock:

assign\_local\_clock -net netname -type quadrant UR|UL|LR|LL

This follows the same rule as the chip global clock network.

The following PDC command demotes the clock nets to regular nets.

unassign\_global\_clock -net netname

# 5 – FlashROM in Microsemi's Low Power Flash Devices

## Introduction

The Fusion, IGLOO, and ProASIC3 families of low power flash-based devices have a dedicated nonvolatile FlashROM memory of 1,024 bits, which provides a unique feature in the FPGA market. The FlashROM can be read, modified, and written using the JTAG (or UJTAG) interface. It can be read but not modified from the FPGA core. Only low power flash devices contain on-chip user nonvolatile memory (NVM).

## Architecture of User Nonvolatile FlashROM

Low power flash devices have 1 kbit of user-accessible nonvolatile flash memory on-chip that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits (16 bytes) during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core. Figure 5-1 shows the FlashROM logical structure.

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports synchronous read. The address is latched on the rising edge of the clock, and the new output data is stable after the falling edge of the same clock cycle. For more information, refer to the timing diagrams in the DC and Switching Characteristics chapter of the appropriate datasheet. The FlashROM can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

|                                 |   | Byte Number in Bank |    |    |    |    |    | 4 LSB of ADDR (READ) |   |   |   |   |   |   |   |   |   |

|---------------------------------|---|---------------------|----|----|----|----|----|----------------------|---|---|---|---|---|---|---|---|---|

|                                 |   | 15                  | 14 | 13 | 12 | 11 | 10 | 9                    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| of                              | 7 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| 3 MSB of<br>EAD)                | 6 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| ΑD                              | 5 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| RE C                            | 4 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| dr (                            | 3 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| NU                              | 2 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| Bank Number 3 MS<br>ADDR (READ) | 1 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| ä                               | 0 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

Figure 5-1 • FlashROM Architecture

FlashROM in Microsemi's Low Power Flash Devices

# **Programming and Accessing FlashROM**

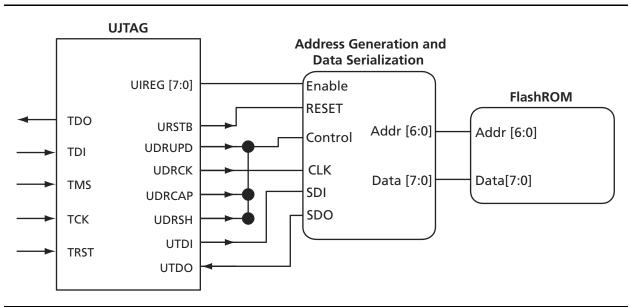

The FlashROM content can only be programmed via JTAG, but it can be read back selectively through the JTAG programming interface, the UJTAG interface, or via direct FPGA core addressing. The pages of the FlashROM can be made secure to prevent read-back via JTAG. In that case, read-back on these secured pages is only possible by the FPGA core fabric or via UJTAG.

A 7-bit address from the FPGA core defines which of the eight pages (three MSBs) is being read, and which of the 16 bytes within the selected page (four LSBs) are being read. The FlashROM content can be read on a random basis; the access time is 10 ns for a device supporting commercial specifications. The FPGA core will be powered down during writing of the FlashROM content. FPGA power-down during FlashROM programming is managed on-chip, and FPGA core functionality is not available during programming of the FlashROM. Table 5-2 summarizes various FlashROM access scenarios.

| Access Mode | FlashROM Read | FlashROM Write |

|-------------|---------------|----------------|

| JTAG        | Yes           | Yes            |

| UJTAG       | Yes           | No             |

| FPGA core   | Yes           | No             |

Figure 5-6 shows the accessing of the FlashROM using the UJTAG macro. This is similar to FPGA core access, where the 7-bit address defines which of the eight pages (three MSBs) is being read and which of the 16 bytes within the selected page (four LSBs) are being read. Refer to the "UJTAG Applications in Microsemi's Low Power Flash Devices" section on page 363 for details on using the UJTAG macro to read the FlashROM.

Figure 5-7 on page 139 and Figure 5-8 on page 139 show the FlashROM access from the JTAG port. The FlashROM content can be read on a random basis. The three-bit address defines which page is being read or updated.

Figure 5-6 • Block Diagram of Using UJTAG to Read FlashROM Contents

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

# **SRAM/FIFO Support in Flash-Based Devices**

The flash FPGAs listed in Table 6-1 support SRAM and FIFO blocks and the functions described in this document.

#### Table 6-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 6-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 6-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

I/O Structures in IGLOO and ProASIC3 Devices

# Low Power Flash Device I/O Support

The low power flash FPGAs listed in Table 7-1 support I/Os and the functions described in this document.

#### Table 7-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                       |

|----------|----------------------|-------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L             |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                       |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

ProASIC3L FPGA Fabric User's Guide

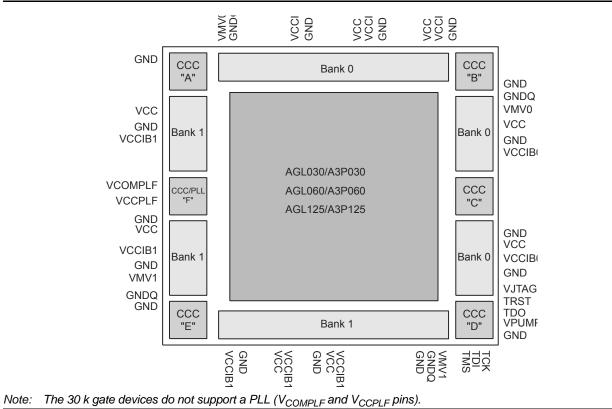

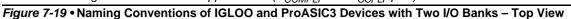

Figure 7-20 • Naming Conventions of IGLOO and ProASIC3 Devices with Four I/O Banks – Top View

**Revision 4**

I/O Structures in IGLOOe and ProASIC3E Devices

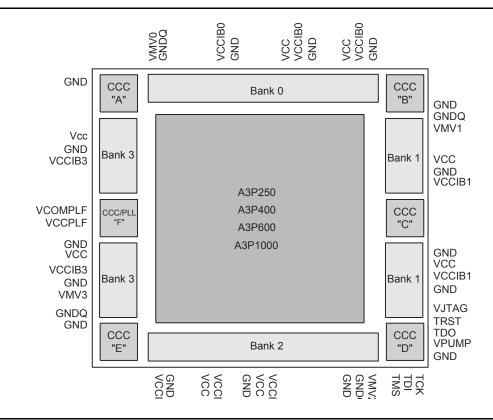

#### Notes:

- 1. All NMOS transistors connected to the I/O pad serve as ESD protection.

- 2. See Table 8-2 on page 215 for available I/O standards.

- 3. Programmable input delay is applicable only to ProASIC3E, IGLOOe, ProASIC3EL, and RT ProASIC3 devices.

Figure 8-5 • Simplified I/O Buffer Circuitry

### I/O Registers

Each I/O module contains several input, output, and enable registers. Refer to Figure 8-5 for a simplified representation of the I/O block. The number of input registers is selected by a set of switches (not shown in Figure 8-3 on page 220) between registers to implement single-ended or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user. A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input Register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy certain rules.

#### Table 8-11 • Hot-Swap Level 3

| Description                              | Hot-swap while bus idle                                                                                                                                                                                       |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                                                                           |

| Bus State                                | Held idle (no ongoing I/O processes during insertion/removal)                                                                                                                                                 |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                                                                |

| Device Circuitry Connected to Bus Pins   | Must remain glitch-free during power-up or power-<br>down                                                                                                                                                     |

| Example Application                      | Board bus shared with card bus is "frozen," and<br>there is no toggling activity on the bus. It is critical<br>that the logic states set on the bus signal not be<br>disturbed during card insertion/removal. |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E<br>devices: Compliant with two levels of staging (first:<br>GND; second: all other pins)                                                                              |

|                                          | Other IGLOO/ProASIC3 devices: Compliant:                                                                                                                                                                      |

|                                          | Option A – Two levels of staging (first: GND; second: all other pins) together with bus switch on the I/Os                                                                                                    |

|                                          | Option B – Three levels of staging (first: GND; second: supplies; third: all other pins)                                                                                                                      |

### Table 8-12 • Hot-Swap Level 4

| Description                              | Hot-swap on an active bus                                                                                                                           |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                 |

| Bus State                                | Bus may have active I/O processes ongoing, but device being inserted or removed must be idle.                                                       |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                      |

| Device Circuitry Connected to Bus Pins   | Must remain glitch-free during power-up or power-<br>down                                                                                           |

| Example Application                      | There is activity on the system bus, and it is critical that the logic states set on the bus signal not be disturbed during card insertion/removal. |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E<br>devices: Compliant with two levels of staging (first:<br>GND; second: all other pins)                    |

|                                          | Other IGLOO/ProASIC3 devices: Compliant:                                                                                                            |

|                                          | Option A – Two levels of staging (first: GND;<br>second: all other pins) together with bus switch on<br>the I/Os                                    |

|                                          | Option B – Three levels of staging (first: GND; second: supplies; third: all other pins)                                                            |

I/O Structures in IGLOOe and ProASIC3E Devices

### IGLOOe and ProASIC3E

For devices requiring Level 3 and/or Level 4 compliance, the board drivers connected to the I/Os must have 10 k $\Omega$  (or lower) output drive resistance at hot insertion, and 1 k $\Omega$  (or lower) output drive resistance at hot removal. This resistance is the transmitter resistance sending a signal toward the I/O, and no additional resistance is needed on the board. If that cannot be assured, three levels of staging can be used to achieve Level 3 and/or Level 4 compliance. Cards with two levels of staging should have the following sequence:

- Grounds

- · Powers, I/Os, and other pins

## **Cold-Sparing Support**

*Cold-sparing* refers to the ability of a device to leave system data undisturbed when the system is powered up, while the component itself is powered down, or when power supplies are floating.

Cold-sparing is supported on ProASIC3E devices only when the user provides resistors from each power supply to ground. The resistor value is calculated based on the decoupling capacitance on a given power supply. The RC constant should be greater than 3  $\mu$ s.

To remove resistor current during operation, it is suggested that the resistor be disconnected (e.g., with an NMOS switch) from the power supply after the supply has reached its final value. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373 for details on cold-sparing.

Cold-sparing means that a subsystem with no power applied (usually a circuit board) is electrically connected to the system that is in operation. This means that all input buffers of the subsystem must present very high input impedance with no power applied so as not to disturb the operating portion of the system.

The 30 k gate devices fully support cold-sparing, since the I/O clamp diode is always off (see Table 8-13 on page 231). If the 30 k gate device is used in applications requiring cold-sparing, a discharge path from the power supply to ground should be provided. This can be done with a discharge resistor or a switched resistor. This is necessary because the 30 k gate devices do not have built-in I/O clamp diodes.

For other IGLOOe and ProASIC3E devices, since the I/O clamp diode is always active, cold-sparing can be accomplished either by employing a bus switch to isolate the device I/Os from the rest of the system or by driving each I/O pin to 0 V. If the resistor is chosen, the resistor value must be calculated based on decoupling capacitance on a given power supply on the board (this decoupling capacitance is in parallel with the resistor). The RC time constant should ensure full discharge of supplies before cold-sparing functionality is required. The resistor is necessary to ensure that the power pins are discharged to ground every time there is an interruption of power to the device.

IGLOOe and ProASIC3E devices support cold-sparing for all I/O configurations. Standards, such as PCI, that require I/O clamp diodes can also achieve cold-sparing compliance, since clamp diodes get disconnected internally when the supplies are at 0 V.

When targeting low power applications, I/O cold-sparing may add additional current if a pin is configured with either a pull-up or pull-down resistor and driven in the opposite direction. A small static current is induced on each I/O pin when the pin is driven to a voltage opposite to the weak pull resistor. The current is equal to the voltage drop across the input pin divided by the pull resistor. Refer to the "Detailed I/O DC Characteristics" section of the appropriate family datasheet for the specific pull resistor value for the corresponding I/O standard.

For example, assuming an LVTTL 3.3 V input pin is configured with a weak pull-up resistor, a current will flow through the pull-up resistor if the input pin is driven LOW. For LVTTL 3.3 V, the pull-up resistor is ~45 k $\Omega$ , and the resulting current is equal to 3.3 V / 45 k $\Omega$  = 73 µA for the I/O pin. This is true also when a weak pull-down is chosen and the input pin is driven High. This current can be avoided by driving the input Low when a weak pull-down resistor is used and driving it High when a weak pull-up resistor is used.

This current draw can occur in the following cases:

- In Active and Static modes:

- Input buffers with pull-up, driven Low

- Input buffers with pull-down, driven High

- Bidirectional buffers with pull-up, driven Low

- Bidirectional buffers with pull-down, driven High

- Output buffers with pull-up, driven Low

- Output buffers with pull-down, driven High

- Tristate buffers with pull-up, driven Low

- Tristate buffers with pull-down, driven High

- In Flash\*Freeze mode:

- Input buffers with pull-up, driven Low

- Input buffers with pull-down, driven High

- Bidirectional buffers with pull-up, driven Low

- Bidirectional buffers with pull-down, driven High

### **Electrostatic Discharge Protection**

Low power flash devices are tested per JEDEC Standard JESD22-A114-B.

These devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

All IGLOO and ProASIC3 devices are tested to the Human Body Model (HBM) and the Charged Device Model (CDM).

Each I/O has two clamp diodes. One diode has its positive (P) side connected to the pad and its negative (N) side connected to VCCI. The second diode has its P side connected to GND and its N side connected to the pad. During operation, these diodes are normally biased in the off state, except when transient voltage is significantly above VCCI or below GND levels.

In 30 k gate devices, the first diode is always off. In other devices, the clamp diode is always on and cannot be switched off.

By selecting the appropriate I/O configuration, the diode is turned on or off. Refer to Table 8-13 for more information about the I/O standards and the clamp diode.

The second diode is always connected to the pad, regardless of the I/O configuration selected.

| I/O Assignment                          | Clamp<br>Diode | Hot<br>Insertion | 5 V Input<br>Tolerance | Input<br>Buffer | Output<br>Buffer |

|-----------------------------------------|----------------|------------------|------------------------|-----------------|------------------|

| 3.3 V LVTTL/LVCMOS                      | No             | Yes              | Yes <sup>1</sup>       | Enabled         | /Disabled        |

| 3.3 V PCI, 3.3 V PCI-X                  | Yes            | No               | Yes <sup>1</sup>       | Enabled         | /Disabled        |

| LVCMOS 2.5 V <sup>2</sup>               | No             | Yes              | No                     | Enabled         | /Disabled        |

| LVCMOS 2.5 V / 5.0 V <sup>2</sup>       | Yes            | No               | Yes <sup>3</sup>       | Enabled         | /Disabled        |

| LVCMOS 1.8 V                            | No             | Yes              | No                     | Enabled         | /Disabled        |

| LVCMOS 1.5 V                            | No             | Yes              | No                     | Enabled         | /Disabled        |

| Voltage-Referenced Input Buffer         | No             | Yes              | No                     | Enabled         | /Disabled        |

| Differential, LVDS/B-LVDS/M-LVDS/LVPECL | No             | Yes              | No                     | Enabled         | /Disabled        |

#### Table 8-13 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in IGLOOe and ProASIC3E Devices

Notes:

1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- In the SmartGen Core Reference Guide, select the LVCMOS5 macro for the LVCMOS 2.5 V / 5.0 V I/O standard or the LVCMOS25 macro for the LVCMOS 2.5 V I/O standard.

- 3. Can be implemented with an external resistor and an internal clamp diode.

I/O Structures in IGLOOe and ProASIC3E Devices

## Conclusion

IGLOOe and ProASIC3E support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The IGLOOe and ProASIC3E device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

## **Related Documents**

## **Application Notes**

Board-Level Considerations http://www.microsemi.com/soc/documents/ALL\_AC276\_AN.pdf

### **User's Guides**

ProASIC3 FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3\_UG.pdf ProASIC3E FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3E\_UG.pdf IGLOOe FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/IGLOOe\_UG.pdf Libero SoC User's Guide http://www.microsemi.com/soc/documents/libero\_ug.pdf IGLOO, Fusion, and ProASIC3 Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen Core Reference Guide http://www.microsemi.com/soc/documents/genguide\_ug.pdf

ProASIC3L FPGA Fabric User's Guide

| Date                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| v1.3<br>(December 2008) | The "Programming Support in Flash Devices" section was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                                                                                                                                                                       | 288      |

|                         | The "Flash Devices" section was updated to include information for IGLOO nano devices. The following sentence was added: IGLOO PLUS devices can also be operated at any voltage between 1.2 V and 1.5 V; the Designer software allows 50 mV increments in the voltage.                                                                                                                                                                                                                | 289      |

|                         | Table 11-4 · Programming Ordering Codes was updated to replace FP3-26PIN-<br>ADAPTER with FP3-10PIN-ADAPTER-KIT.                                                                                                                                                                                                                                                                                                                                                                      | 294      |

|                         | Table 14-6 $\cdot$ Programmer Device Support was updated to add IGLOO nano and ProASIC3 nano devices. AGL400 was added to the IGLOO portion of the table.                                                                                                                                                                                                                                                                                                                             | 317      |

| v1.2<br>(October 2008)  | The "Programming Support in Flash Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                                                                                                         | 288      |

|                         | Figure 11-1 · FlashPro Programming Setup and the "Programming Support in Flash Devices" section are new.                                                                                                                                                                                                                                                                                                                                                                              | 287, 288 |

|                         | Table 14-6 $\cdot$ Programmer Device Support was updated to include A3PE600L with the other ProASIC3L devices, and the RT ProASIC3 family was added.                                                                                                                                                                                                                                                                                                                                  | 317      |

| v1.1<br>(March 2008)    | The "Flash Devices" section was updated to include the IGLOO PLUS family. The text, "Voltage switching is required in-system to switch from a 1.2 V core to 1.5 V core for programming," was revised to state, "Although the device can operate at 1.2 V core voltage, the device can only be reprogrammed when the core voltage is 1.5 V. Voltage switching is required in-system to switch from a 1.2 V supply ( $V_{CC}$ , $V_{CCI}$ , and $V_{JTAG}$ ) to 1.5 V for programming." | 289      |

|                         | The ProASIC3L family was added to Table 14-6 $\cdot$ Programmer Device Support as a separate set of rows rather than combined with ProASIC3 and ProASIC3E devices. The IGLOO PLUS family was included, and AGL015 and A3P015 were added.                                                                                                                                                                                                                                              | 317      |

2. VCC rises to 1.5 V before programming begins.

#### Figure 14-3 • Programming Algorithm

The oscilloscope plot in Figure 14-3 shows a wider time interval for the programming algorithm and includes the TDI and TMS signals from the FlashPro3. These signals carry the programming information that is programmed into the device and should only start toggling after the  $V_{CC}$  core voltage reaches 1.5 V. Again, TRST from FlashPro3 and the  $V_{CC}$  core voltage of the IGLOO device are labeled. As shown in Figure 14-3, TDI and TMS are floating initially, and the core voltage is 1.2 V. When a programming command on the FlashPro3 is executed, TRST is driven HIGH and TDI is momentarily driven to ground. In response to the HIGH TRST signal, the circuit responds and pulls the core voltage to 1.5 V. After 100 ms, TRST is briefly driven LOW by the FlashPro software. This is expected behavior that ensures the device JTAG state machine is in Reset prior to programming. TRST remains HIGH for the duration of the programming. It can be seen in Figure 14-3 that the VCC core voltage signal remains at 1.5 V for approximately 50 ms before information starts passing through on TDI and TMS. This confirms that the voltage switching circuit drives the VCC core supply voltage to 1.5 V prior to programming.

Microprocessor Programming of Microsemi's Low Power Flash Devices

# **Microprocessor Programming Support in Flash Devices**

The flash-based FPGAs listed in Table 15-1 support programming with a microprocessor and the functions described in this document.

#### Table 15-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 15-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 15-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Power-Up/-Down Behavior of Low Power Flash Devices

# Flash Devices Support Power-Up Behavior

The flash FPGAs listed in Table 18-1 support power-up behavior and the functions described in this document.

#### Table 18-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                              |

|----------|----------------------|--------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology        |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                      |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                               |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                      |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                     |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 18-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 18-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.