Welcome to E-XFL.COM

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | -                                                            |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | 36864                                                        |

| Number of I/O                  | 97                                                           |

| Number of Gates                | 250000                                                       |

| Voltage - Supply               | 1.14V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 144-LBGA                                                     |

| Supplier Device Package        | 144-FPBGA (13x13)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p250l-fg144 |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Microsemi

|    | Introduction                                                             | . 213 |

|----|--------------------------------------------------------------------------|-------|

|    | Low Power Flash Device I/O Support                                       | . 214 |

|    | Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E                               | . 215 |

|    | I/O Architecture                                                         | . 220 |

|    | I/O Standards                                                            | . 223 |

|    | I/O Features                                                             | . 227 |

|    | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout | . 241 |

|    | I/O Software Support                                                     | . 242 |

|    | User I/O Naming Convention                                               | . 245 |

|    | Board-Level Considerations                                               | . 246 |

|    | Conclusion                                                               | . 248 |

|    | Related Documents                                                        | . 248 |

|    | List of Changes                                                          | . 249 |

| ~  |                                                                          |       |

| 9  | I/O Software Control in Low Power Flash Devices.                         |       |

|    | Flash FPGAs I/O Support                                                  |       |

|    | Software-Controlled I/O Attributes                                       |       |

|    | Implementing I/Os in Microsemi Software                                  |       |

|    | Assigning Technologies and VREF to I/O Banks                             |       |

|    | Conclusion                                                               |       |

|    | Related Documents                                                        |       |

|    | List of Changes                                                          | . 270 |

| 10 | DDR for Microsemi's Low Power Flash Devices                              | 271   |

|    | Introduction                                                             |       |

|    | Double Data Rate (DDR) Architecture                                      |       |

|    | DDR Support in Flash-Based Devices                                       |       |

|    | I/O Cell Architecture                                                    |       |

|    | Input Support for DDR                                                    |       |

|    | Output Support for DDR                                                   |       |

|    | Instantiating DDR Registers                                              |       |

|    | Design Example                                                           |       |

|    | Conclusion                                                               |       |

|    | List of Changes                                                          |       |

|    |                                                                          |       |

| 11 | Programming Flash Devices                                                | 287   |

|    | Introduction                                                             | . 287 |

|    | Summary of Programming Support                                           |       |

|    | Programming Support in Flash Devices                                     | . 288 |

|    | General Flash Programming Information                                    |       |

|    | Important Programming Guidelines                                         | . 295 |

|    | Related Documents                                                        | . 297 |

|    | List of Changes                                                          | . 298 |

| 12 | Security in Low Power Flash Devices                                      | 301   |

|    | Security in Programmable Logic                                           |       |

|    | Security Support in Flash-Based Devices                                  |       |

|    | Security Architecture                                                    |       |

|    | Security Features                                                        |       |

|    | Security in Action                                                       |       |

|    | •                                                                        | -     |

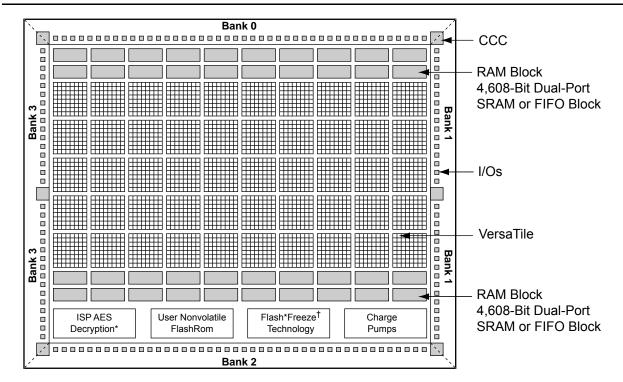

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

Note: \* AGLP030 does not contain a PLL or support AES security.

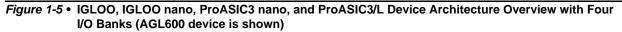

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

ProASIC3L FPGA Fabric User's Guide

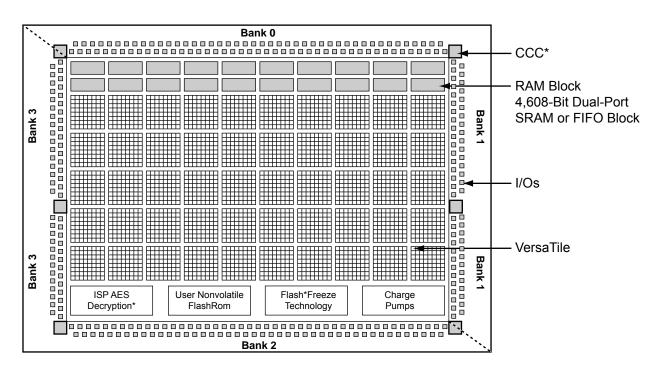

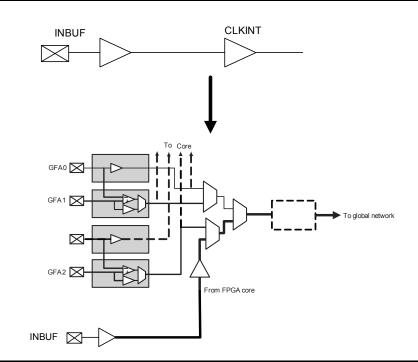

Figure 3-6 shows all nine global inputs for the location A connected to the top left quadrant global network via CCC.

Figure 3-6 • Global Inputs

Since each bank can have a different I/O standard, the user should be careful to choose the correct global I/O for the design. There are 54 global pins available to access 18 global networks. For the single-ended and voltage-referenced I/O standards, you can use any of these three available I/Os to access the global network. For differential I/O standards such as LVDS and LVPECL, the I/O macro needs to be placed on (A0, A1), (B0, B1), (C0, C1), or a similar location. The unassigned global I/Os can be used as regular I/Os. Note that pin names starting with GF and GC are associated with the chip global networks, and GA, GB, GD, and GE are used for quadrant global networks. Table 3-2 on page 54 and Table 3-3 on page 55 show the general chip and quadrant global pin names.

Global Resources in Low Power Flash Devices

### External I/O or Local signal as Clock Source

External I/O refers to regular I/O pins are labeled with the I/O convention IOuxwByVz. You can allow the external I/O or internal signal to access the global. To allow the external I/O or internal signal to access the global network, you need to instantiate the CLKINT macro. Refer to Figure 3-4 on page 51 for an example illustration of the connections. Instead of using CLKINT, you can also use PDC to promote signals from external I/O or internal signal to the global network. However, it may cause layout issues because of synthesis logic replication. Refer to the "Global Promotion and Demotion Using PDC" section on page 67 for details.

Figure 3-14 • CLKINT Macro

### Using Global Macros in Synplicity

The Synplify<sup>®</sup> synthesis tool automatically inserts global buffers for nets with high fanout during synthesis. By default, Synplicity<sup>®</sup> puts six global macros (CLKBUF or CLKINT) in the netlist, including any global instantiation or PLL macro. Synplify always honors your global macro instantiation. If you have a PLL (only primary output is used) in the design, Synplify adds five more global buffers in the netlist. Synplify uses the following global counting rule to add global macros in the netlist:

- 1. CLKBUF: 1 global buffer

- 2. CLKINT: 1 global buffer

- 3. CLKDLY: 1 global buffer

- 4. PLL: 1 to 3 global buffers

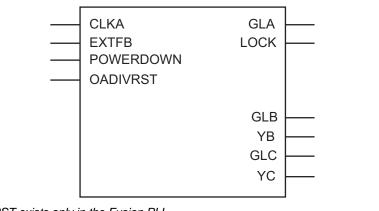

- GLA, GLB, GLC, YB, and YC are counted as 1 buffer.

- GLB or YB is used or both are counted as 1 buffer.

- GLC or YC is used or both are counted as 1 buffer.

ProASIC3L FPGA Fabric User's Guide

Note: OAVDIVRST exists only in the Fusion PLL.

#### Figure 3-15 • PLLs in Low Power Flash Devices

You can use the syn\_global\_buffers attribute in Synplify to specify a maximum number of global macros to be inserted in the netlist. This can also be used to restrict the number of global buffers inserted. In the Synplicity 8.1 version or newer, a new attribute, syn\_global\_minfanout, has been added for low power flash devices. This enables you to promote only the high-fanout signal to global. However, be aware that you can only have six signals assigned to chip global networks, and the rest of the global signals should be assigned to quadrant global networks. So, if the netlist has 18 global macros, the remaining 12 global macros should have fanout that allows the instances driven by these globals to be placed inside a quadrant.

### **Global Promotion and Demotion Using PDC**

The HDL source file or schematic is the preferred place for defining which signals should be assigned to a clock network using clock macro instantiation. This method is preferred because it is guaranteed to be honored by the synthesis tools and Designer software and stop any replication on this net by the synthesis tool. Note that a signal with fanout may have logic replication if it is not promoted to global during synthesis. In that case, the user cannot promote that signal to global using PDC. See Synplicity Help for details on using this attribute. To help you with global management, Designer allows you to promote a signal to a global network or demote a global macro to a regular macro from the user netlist using the compile options and/or PDC commands.

The following are the PDC constraints you can use to promote a signal to a global network:

1. PDC syntax to promote a regular net to a chip global clock:

assign\_global\_clock -net netname

The following will happen during promotion of a regular signal to a global network:

- If the net is external, the net will be driven by a CLKINT inserted automatically by Compile.

- The I/O macro will not be changed to CLKBUF macros.

- If the net is an internal net, the net will be driven by a CLKINT inserted automatically by Compile.

- 2. PDC syntax to promote a net to a quadrant clock:

assign\_local\_clock -net netname -type quadrant UR|UL|LR|LL

This follows the same rule as the chip global clock network.

The following PDC command demotes the clock nets to regular nets.

unassign\_global\_clock -net netname

```

wire VCC, GND;

VCC VCC_1_net(.Y(VCC));

GND GND_1_net(.Y(GND));

PLL Core(.CLKA(CLKA), .EXTFB(GND), .POWERDOWN(POWERDOWN),

.GLA(GLA), .LOCK(LOCK), .GLB(), .YB(), .GLC(), .YC(),

.OADIV0(GND), .OADIV1(GND), .OADIV2(GND), .OADIV3(GND),

.OADIV4(GND), .OAMUX0(GND), .OAMUX1(GND), .OAMUX2(VCC),

.DLYGLA0(GND), .DLYGLA1(GND), .DLYGLA2(GND), .DLYGLA3(GND)

, .DLYGLA4(GND), .OBDIV0(GND), .OBDIV1(GND), .OBDIV2(GND),

.OBDIV3(GND), .OBDIV4(GND), .OBMUX0(GND), .OBMUX1(GND),

.OBMUX2(GND), .DLYYB0(GND), .DLYYB1(GND), .DLYYB2(GND),

.DLYYB3(GND), .DLYYB4(GND), .DLYGLB0(GND), .DLYGLB1(GND),

.DLYGLB2(GND), .DLYGLB3(GND), .DLYGLB4(GND), .OCDIV0(GND),

.OCDIV1(GND), .OCDIV2(GND), .OCDIV3(GND), .OCDIV4(GND),

.OCMUX0(GND), .OCMUX1(GND), .OCMUX2(GND), .DLYYC0(GND),

.DLYYC1(GND), .DLYYC2(GND), .DLYYC3(GND), .DLYYC4(GND),

.DLYGLC0(GND), .DLYGLC1(GND), .DLYGLC2(GND), .DLYGLC3(GND)

, .DLYGLC4(GND), .FINDIV0(VCC), .FINDIV1(GND), .FINDIV2(

VCC), .FINDIV3(GND), .FINDIV4(GND), .FINDIV5(GND),

.FINDIV6(GND), .FBDIV0(VCC), .FBDIV1(GND), .FBDIV2(VCC),

.FBDIV3(GND), .FBDIV4(GND), .FBDIV5(GND), .FBDIV6(GND),

.FBDLY0(GND), .FBDLY1(GND), .FBDLY2(GND), .FBDLY3(GND),

.FBDLY4(GND), .FBSEL0(VCC), .FBSEL1(GND), .XDLYSEL(GND),

.VCOSEL0(GND), .VCOSEL1(GND), .VCOSEL2(GND));

defparam Core.VCOFREQUENCY = 33.000;

endmodule

```

The "PLL Configuration Bits Description" section on page 106 provides descriptions of the PLL configuration bits for completeness. The configuration bits are shown as busses only for purposes of illustration. They will actually be broken up into individual pins in compilation libraries and all simulation models. For example, the FBSEL[1:0] bus will actually appear as pins FBSEL1 and FBSEL0. The setting of these select lines for the static PLL configuration is performed by the software and is completely transparent to the user.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

```

DLYGLC[4:0] 00000

DLYYB[4:0] 00000

DLYYC[4:0] 00000

VCOSEL[2:0] 100

```

Primary Clock Frequency 33.000 Primary Clock Phase Shift 0.000 Primary Clock Output Delay from CLKA 1.695

Secondaryl Clock Frequency 40.000 Secondaryl Clock Phase Shift 0.000 Secondaryl Clock Global Output Delay from CLKB 0.200

Secondary2 Clock Frequency 50.000 Secondary2 Clock Phase Shift 0.000 Secondary2 Clock Global Output Delay from CLKC 0.200

\*\*\*\*\*

| NAME     | SDIN    | VALUE   | TYPE     |

|----------|---------|---------|----------|

| FINDIV   | [6:0]   | 0000101 | EDIT     |

| FBDIV    | [13:7]  | 0100000 | EDIT     |

| OADIV    | [18:14] | 00100   | EDIT     |

| OBDIV    | [23:19] | 00000   | EDIT     |

| OCDIV    | [28:24] | 00000   | EDIT     |

| OAMUX    | [31:29] | 100     | EDIT     |

| OBMUX    | [34:32] | 000     | EDIT     |

| OCMUX    | [37:35] | 000     | EDIT     |

| FBSEL    | [39:38] | 01      | EDIT     |

| FBDLY    | [44:40] | 00000   | EDIT     |

| XDLYSEL  | [45]    | 0       | EDIT     |

| DLYGLA   | [50:46] | 00000   | EDIT     |

| DLYGLB   | [55:51] | 00000   | EDIT     |

| DLYGLC   | [60:56] | 00000   | EDIT     |

| DLYYB    | [65:61] | 00000   | EDIT     |

| DLYYC    | [70:66] | 00000   | EDIT     |

| STATASEL | [71]    | X       | MASKED   |

| STATBSEL | [72]    | X       | MASKED   |

| STATCSEL | [73]    | X       | MASKED   |

| VCOSEL   | [76:74] | 100     | EDIT     |

| DYNASEL  | [77]    | X       | MASKED   |

| DYNBSEL  | [78]    | X       | MASKED   |

| DYNCSEL  | [79]    | X       | MASKED   |

| RESETEN  | [80]    | 1       | READONLY |

Below is the resultant Verilog HDL description of a legal dynamic PLL core configuration generated by SmartGen:

module dyn\_pll\_macro(POWERDOWN, CLKA, LOCK, GLA, GLB, GLC, SDIN, SCLK, SSHIFT, SUPDATE, MODE, SDOUT, CLKB, CLKC);

input POWERDOWN, CLKA; output LOCK, GLA, GLB, GLC; input SDIN, SCLK, SSHIFT, SUPDATE, MODE; output SDOUT; input CLKB, CLKC; wire VCC, GND; VCC VCC\_1\_net(.Y(VCC)); Use quadrant global region assignments by finding the clock net associated with the CCC macro under the Nets tab and creating a quadrant global region for the net, as shown in Figure 4-33.

#### Figure 4-33 • Quadrant Clock Assignment for a Global Net

#### External I/O–Driven CCCs

The above-mentioned recommendation for proper layout techniques will ensure the correct assignment. It is possible that, especially with External I/O–Driven CCC macros, placement of the CCC macro in a desired location may not be achieved. For example, assigning an input port of an External I/O–Driven CCC near a particular CCC location does not guarantee global assignments to the desired location. This is because the clock inputs of External I/O–Driven CCCs can be assigned to any I/O location; therefore, it is possible that the CCC connected to the clock input will be routed to a location other than the one closest to the I/O location, depending on resource availability and placement constraints.

#### **Clock Placer**

The clock placer is a placement engine for low power flash devices that places global signals on the chip global and quadrant global networks. Based on the clock assignment constraints for the chip global and quadrant global clocks, it will try to satisfy all constraints, as well as creating quadrant clock regions when necessary. If the clock placer fails to create the quadrant clock regions for the global signals, it will report an error and stop Layout.

The user must ensure that the constraints set to promote clock signals to quadrant global networks are valid.

# **Cascading CCCs**

The CCCs in low power flash devices can be cascaded. Cascading CCCs can help achieve more accurate PLL output frequency results than those achievable with a single CCC. In addition, this technique is useful when the user application requires the output clock of the PLL to be a multiple of the reference clock by an integer greater than the maximum feedback divider value of the PLL (divide by 128) to achieve the desired frequency.

For example, the user application may require a 280 MHz output clock using a 2 MHz input reference clock, as shown in Figure 4-34 on page 126.

Figure 4-36 • Second-Stage PLL Showing Input of 256 MHz from First Stage and Final Output of 280 MHz

Figure 4-37 shows the simulation results, where the first PLL's output period is 3.9 ns (~256 MHz), and the stage 2 (final) output period is 3.56 ns (~280 MHz).

Stage 2 Output Clock Period Stage 1 Output Clock Period

Figure 4-37 • Model Sim Simulation Results

#### Table 7-8 • Hot-Swap Level 1

| Description                              | Cold-swap                                                                                                                                                                                                                                     |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | No                                                                                                                                                                                                                                            |

| Bus State                                | -                                                                                                                                                                                                                                             |

| Card Ground Connection                   | -                                                                                                                                                                                                                                             |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                                                                                             |

| Example Application                      | System and card with Microsemi FPGA chip are<br>powered down, and the card is plugged into the<br>system. Then the power supplies are turned on for<br>the system but not for the FPGA on the card.                                           |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices: Compliant<br>Other IGLOO/ProASIC3 devices: Compliant if bus<br>switch used to isolate FPGA I/Os from rest of<br>system<br>IGLOOe/ProASIC3E devices: Compliant I/Os can<br>but do not have to be set to hot-insertion mode. |

Table 7-9 • Hot-Swap Level 2

| Description                              | Hot-swap while reset                                                                                                                                                  |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power Applied to Device                  | Yes                                                                                                                                                                   |  |  |

| Bus State                                | Held in reset state                                                                                                                                                   |  |  |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                        |  |  |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                     |  |  |

| Example Application                      | In the PCI hot-plug specification, reset control circuitry isolates the card busses until the card supplies are at their nominal operating levels and stable.         |  |  |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E<br>devices: Compliant I/Os can but do not have to be<br>set to hot-insertion mode.<br>Other IGLOO/ProASIC3 devices: Compliant |  |  |

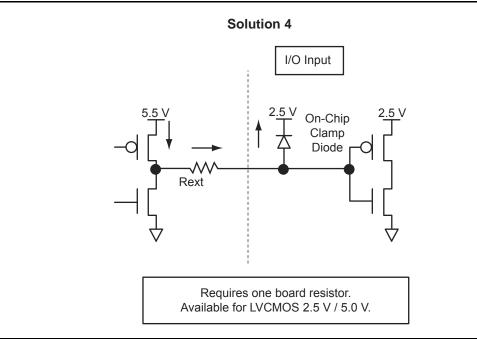

### Solution 4

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

Figure 7-12 • Solution 4

This current draw can occur in the following cases:

- In Active and Static modes:

- Input buffers with pull-up, driven Low

- Input buffers with pull-down, driven High

- Bidirectional buffers with pull-up, driven Low

- Bidirectional buffers with pull-down, driven High

- Output buffers with pull-up, driven Low

- Output buffers with pull-down, driven High

- Tristate buffers with pull-up, driven Low

- Tristate buffers with pull-down, driven High

- In Flash\*Freeze mode:

- Input buffers with pull-up, driven Low

- Input buffers with pull-down, driven High

- Bidirectional buffers with pull-up, driven Low

- Bidirectional buffers with pull-down, driven High

### **Electrostatic Discharge Protection**

Low power flash devices are tested per JEDEC Standard JESD22-A114-B.

These devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

All IGLOO and ProASIC3 devices are tested to the Human Body Model (HBM) and the Charged Device Model (CDM).

Each I/O has two clamp diodes. One diode has its positive (P) side connected to the pad and its negative (N) side connected to VCCI. The second diode has its P side connected to GND and its N side connected to the pad. During operation, these diodes are normally biased in the off state, except when transient voltage is significantly above VCCI or below GND levels.

In 30 k gate devices, the first diode is always off. In other devices, the clamp diode is always on and cannot be switched off.

By selecting the appropriate I/O configuration, the diode is turned on or off. Refer to Table 8-13 for more information about the I/O standards and the clamp diode.

The second diode is always connected to the pad, regardless of the I/O configuration selected.

| I/O Assignment                          | Clamp<br>Diode | Hot<br>Insertion | 5 V Input<br>Tolerance | Input<br>Buffer | Output<br>Buffer |

|-----------------------------------------|----------------|------------------|------------------------|-----------------|------------------|

| 3.3 V LVTTL/LVCMOS                      | No             | Yes              | Yes <sup>1</sup>       | Enabled         | /Disabled        |

| 3.3 V PCI, 3.3 V PCI-X                  | Yes            | No               | Yes <sup>1</sup>       | Enabled         | /Disabled        |

| LVCMOS 2.5 V <sup>2</sup>               | No             | Yes              | No                     | Enabled         | /Disabled        |

| LVCMOS 2.5 V / 5.0 V <sup>2</sup>       | Yes            | No               | Yes <sup>3</sup>       | Enabled         | /Disabled        |

| LVCMOS 1.8 V                            | No             | Yes              | No                     | Enabled         | /Disabled        |

| LVCMOS 1.5 V                            | No             | Yes              | No                     | Enabled         | /Disabled        |

| Voltage-Referenced Input Buffer         | No             | Yes              | No                     | Enabled         | /Disabled        |

| Differential, LVDS/B-LVDS/M-LVDS/LVPECL | No             | Yes              | No                     | Enabled         | /Disabled        |

#### Table 8-13 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in IGLOOe and ProASIC3E Devices

Notes:

1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- In the SmartGen Core Reference Guide, select the LVCMOS5 macro for the LVCMOS 2.5 V / 5.0 V I/O standard or the LVCMOS25 macro for the LVCMOS 2.5 V I/O standard.

- 3. Can be implemented with an external resistor and an internal clamp diode.

# **Power-Up Behavior**

Low power flash devices are power-up/-down friendly; i.e., no particular sequencing is required for power-up and power-down. This eliminates extra board components for power-up sequencing, such as a power-up sequencer.

During power-up, all I/Os are tristated, irrespective of I/O macro type (input buffers, output buffers, I/O buffers with weak pull-ups or weak pull-downs, etc.). Once I/Os become activated, they are set to the user-selected I/O macros. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373 for details.

## **Drive Strength**

Low power flash devices have up to seven programmable output drive strengths. The user can select the drive strength of a particular output in the I/O Attribute Editor or can instantiate a specialized I/O macro, such as OUTBUF\_S\_12 (slew = low, out\_drive = 12 mA).

The maximum available drive strength is 24 mA per I/O. Though no I/O should be forced to source or sink more than 24 mA indefinitely, I/Os may handle a higher amount of current (refer to the device IBIS model for maximum source/sink current) during signal transition (AC current). Every device package has its own power dissipation limit; hence, power calculation must be performed accurately to determine how much current can be tolerated per I/O within that limit.

# I/O Interfacing

Low power flash devices are 5 V–input– and 5 V–output–tolerant if certain I/O standards are selected (refer to the "5 V Input and Output Tolerance" section on page 232). Along with other low-voltage I/O macros, this 5 V tolerance makes these devices suitable for many types of board component interfacing.

| Table 8-19 shows some hi | gh-level interfacing | examples using | low power flash devices. |

|--------------------------|----------------------|----------------|--------------------------|

|                          |                      |                |                          |

|                    | (            | Clock           | I/O   |              |              |                 |

|--------------------|--------------|-----------------|-------|--------------|--------------|-----------------|

| Interface          | Туре         | Frequency       | Туре  | Signals In   | Signals Out  | Data I/O        |

| GM                 | Src Sync     | 125 MHz         | LVTTL | 8            | 8            | 125 Mbps        |

| ТВІ                | Src Sync     | 125 MHz         | LVTTL | 10           | 10           | 125 Mbps        |

| XSBI               | Src Sync     | 644 MHz         | LVDS  | 16           | 16           | 644 Mbps        |

| XGMI               | Src Sync DDR | 156 MHz         | HSTL1 | 32           | 32           | 312 Mbps        |

| FlexBus 3          | Sys Sync     | 104 MHz         | LVTTL | ≤ <b>32</b>  | ≤ <b>32</b>  | ≤ 104           |

| Pos-PHY3/SPI-3     | Sys Sync     | 104             | LVTTL | 8,16,32      | 8,16,32      | $\leq$ 104 Mbps |

| FlexBus 4/SPI-4.1  | Src Sync     | 200 MHz         | HSTL1 | 16,64        | 16,64        | 200 Mbps        |

| Pos-PHY4/SPI-4.2   | Src Sync DDR | ≥ 311 MHz       | LVDS  | 16           | 16           | $\geq$ 622 Mbps |

| SFI-4.1            | Src Sync     | 622 MHz         | LVDS  | 16           | 16           | 622 Mbps        |

| CSIX L1            | Sys Sync     | $\leq$ 250 MHz  | HSTL1 | 32,64,96,128 | 32,64,96,128 | $\leq$ 250 Mbps |

| Hyper Transport    | Sys Sync DDR | $\leq$ 800 MHz  | LVDS  | 2,4,8,16     | 2,4,8,16     | $\leq$ 1.6 Gbps |

| Rapid I/O Parallel | Sys Sync DDR | 250 MHz – 1 GHz | LVDS  | 8,16         | 8,16         | ≤ 2 Gbps        |

| Star Fabric        | CDR          |                 | LVDS  | 4            | 4            | 622 Mbps        |

#### Table 8-19 • High-Level Interface Examples

Note: Sys Sync = System Synchronous Clocking, Src Sync = Source Synchronous Clocking, and CDR = Clock and Data Recovery.

Programming Flash Devices

### **Programmer Ordering Codes**

The products shown in Table 11-4 can be ordered through Microsemi sales and will be shipped directly from Microsemi. Products can also be ordered from Microsemi distributors, but will still be shipped directly from Microsemi. Table 11-4 includes ordering codes for the full kit, as well as codes for replacement items and any related hardware. Some additional products can be purchased from external suppliers for use with the programmers. Ordering codes for adapter modules used with Silicon Sculptor are available at http://www.microsemi.com/soc/products/hardware/program\_debug/ss/modules.aspx.

| Table 11-4 | <ul> <li>Programming</li> </ul> | Ordering | Codes |

|------------|---------------------------------|----------|-------|

| 14010 11 1 |                                 | e au ing | 00000 |

| Description                     | Vendor    | Ordering Code        | Comment                                                                                         |

|---------------------------------|-----------|----------------------|-------------------------------------------------------------------------------------------------|

| FlashPro4 ISP<br>programmer     | Microsemi | FLASHPRO 4           | Uses a 2×5, RA male header connector                                                            |

| FlashPro Lite ISP<br>programmer | Microsemi | FLASHPRO LITE        | Supports small programming header or<br>large header through header converter<br>(not included) |

| Silicon Sculptor 3              | Microsemi | SILICON-SCULPTOR 3   | USB 2.0 high-speed production<br>programmer                                                     |

| Silicon Sculptor II             | Microsemi | SILICON-SCULPTOR II  | Requires add-on adapter modules to<br>support devices                                           |

| Silicon Sculptor ISP<br>module  | Microsemi | SMPA-ISP-ACTEL-3-KIT | Ships with both large and small header support                                                  |

| ISP cable for small<br>header   | Microsemi | ISP-CABLE-S          | Supplied with SMPA-ISP-ACTEL-3-KIT                                                              |

| ISP cable for large<br>header   | Microsemi | PA-ISP-CABLE         | Supplied with SMPA-ISP-ACTEL-3-KIT                                                              |

### **Programmer Device Support**

Refer to www.microsemi.com/soc for the current information on programmer and device support.

### **Certified Programming Solutions**

The Microsemi-certified programmers for flash devices are FlashPro4, FlashPro3, FlashPro Lite, FlashPro, Silicon Sculptor II, Silicon Sculptor 3, and any programmer that is built by BP Microsystems. All other programmers are considered noncertified programmers.

FlashPro4, FlashPro3, FlashPro Lite, FlashPro

The Microsemi family of FlashPro device programmers provides in-system programming in an easy-to-use, compact system that supports all flash families. Whether programming a board containing a single device or multiple devices connected in a chain, the Microsemi line of FlashPro programmers enables fast programming and reprogramming. Programming with the FlashPro series of programmers saves board space and money as it eliminates the need for sockets on the board. There are no built-in algorithms, so there is no delay between product release and programming support. The FlashPro programmer is no longer available.

Silicon Sculptor 3, Silicon Sculptor II

Silicon Sculptor 3 and Silicon Sculptor II are robust, compact, single-device programmers with standalone software for the PC. They are designed to enable concurrent programming of multiple units from the same PC with speeds equivalent to or faster than previous Microsemi programmers.

Noncertified Programmers

Microsemi does not test programming solutions from other vendors, and DOES NOT guarantee programming yield. Also, Microsemi will not perform any failure analysis on devices programmed on non-certified programmers. Please refer to the *Programming and Functional Failure Guidelines* document for more information.

# Microsemi

ProASIC3L FPGA Fabric User's Guide

| Date                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| v1.3<br>(December 2008) | The "Programming Support in Flash Devices" section was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                                                                                                                                                                       | 288      |

|                         | The "Flash Devices" section was updated to include information for IGLOO nano devices. The following sentence was added: IGLOO PLUS devices can also be operated at any voltage between 1.2 V and 1.5 V; the Designer software allows 50 mV increments in the voltage.                                                                                                                                                                                                                | 289      |

|                         | Table 11-4 · Programming Ordering Codes was updated to replace FP3-26PIN-<br>ADAPTER with FP3-10PIN-ADAPTER-KIT.                                                                                                                                                                                                                                                                                                                                                                      | 294      |

|                         | Table 14-6 $\cdot$ Programmer Device Support was updated to add IGLOO nano and ProASIC3 nano devices. AGL400 was added to the IGLOO portion of the table.                                                                                                                                                                                                                                                                                                                             | 317      |

| v1.2<br>(October 2008)  | The "Programming Support in Flash Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                                                                                                         | 288      |

|                         | Figure 11-1 · FlashPro Programming Setup and the "Programming Support in Flash Devices" section are new.                                                                                                                                                                                                                                                                                                                                                                              | 287, 288 |

|                         | Table 14-6 $\cdot$ Programmer Device Support was updated to include A3PE600L with the other ProASIC3L devices, and the RT ProASIC3 family was added.                                                                                                                                                                                                                                                                                                                                  | 317      |

| v1.1<br>(March 2008)    | The "Flash Devices" section was updated to include the IGLOO PLUS family. The text, "Voltage switching is required in-system to switch from a 1.2 V core to 1.5 V core for programming," was revised to state, "Although the device can operate at 1.2 V core voltage, the device can only be reprogrammed when the core voltage is 1.5 V. Voltage switching is required in-system to switch from a 1.2 V supply ( $V_{CC}$ , $V_{CCI}$ , and $V_{JTAG}$ ) to 1.5 V for programming." | 289      |

|                         | The ProASIC3L family was added to Table 14-6 $\cdot$ Programmer Device Support as a separate set of rows rather than combined with ProASIC3 and ProASIC3E devices. The IGLOO PLUS family was included, and AGL015 and A3P015 were added.                                                                                                                                                                                                                                              | 317      |

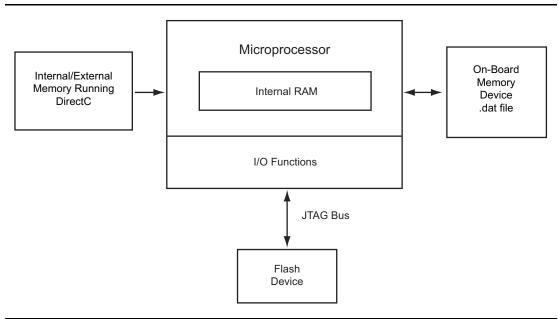

# 15 – Microprocessor Programming of Microsemi's Low Power Flash Devices

# Introduction

The Fusion, IGLOO, and ProASIC3 families of flash FPGAs support in-system programming (ISP) with the use of a microprocessor. Flash-based FPGAs store their configuration information in the actual cells within the FPGA fabric. SRAM-based devices need an external configuration memory, and hybrid nonvolatile devices store the configuration in a flash memory inside the same package as the SRAM FPGA. Since the programming of a true flash FPGA is simpler, requiring only one stage, it makes sense that programming with a microprocessor in-system should be simpler than with other SRAM FPGAs. This reduces bill-of-materials costs and printed circuit board (PCB) area, and increases system reliability.

Nonvolatile flash technology also gives the low power flash devices the advantage of a secure, low power, live-at-power-up, and single-chip solution. Low power flash devices are reprogrammable and offer time-to-market benefits at an ASIC-level unit cost. These features enable engineers to create high-density systems using existing ASIC or FPGA design flows and tools.

This document is an introduction to microprocessor programming only. To explain the difference between the options available, user's guides for DirectC and STAPL provide more detail on implementing each style.

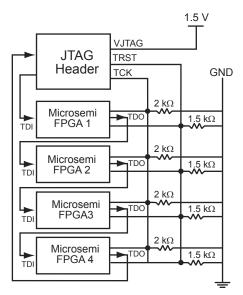

Figure 15-1 • ISP Using Microprocessor

Note: TCK is correctly wired with an equivalent tie-off resistance of  $500 \Omega$ , which satisfies the table for VJTAG of 1.5 V. The resistor values for TRST are not appropriate in this case, as the tie-off resistance of  $375 \Omega$  is below the recommended minimum for VJTAG = 1.5 V, but would be appropriate for a VJTAG setting of 2.5 V or 3.3 V.

#### Figure 16-3 • Parallel Resistance on JTAG Chain of Devices

# **Advanced Boundary Scan Register Settings**

You will not be able to control the order in which I/Os are released from boundary scan control. Testing has produced cases where, depending on I/O placement and FPGA routing, a 5 ns glitch has been seen on exiting programming mode. The following setting is recommended to prevent such I/O glitches:

- 1. In the FlashPro software, configure the advanced BSR settings for **Specify I/O Settings During Programming**.

- 2. Set the input BSR cell to **Low** for the input I/O.

# Microsemi

# Index

### A

AES encryption 305 architecture 147 four I/O banks 13 global 47 IGLOO 12 IGLOO nano 11 IGLOO PLUS 13 IGLOOE 14 ProASIC3 nano 11 ProASIC3E 14 routing 18 spine 57 SRAM and FIFO 151 architecture overview 11 array coordinates 16

### В

boundary scan 357 board-level recommendations 360 chain 359 opcodes 359 brownout voltage 381

# С

CCC 98 board-level considerations 128 cascading 125 **Fusion locations 99** global resources 78 hardwired I/O clock input 124 **IGLOO** locations 97 **IGLOOe** locations 98 locations 96 overview 77 ProASIC3 locations 97 ProASIC3E locations 98 programming 78 software configuration 112 with integrated PLLs 95 without integrated PLLs 95 chip global aggregation 59 CLKDLY macro 81 clock aggregation 60 clock macros 62 clock sources core logic 92 PLL and CLKDLY macros 89 clocks delay adjustment 102 detailed usage information 120 multipliers and dividers 101 phase adjustment 103 physical constraints for quadrant clocks 124 SmartGen settings 121 static timing analysis 123 cold-sparing 382 compiling 261 report 261 contacting Microsemi SoC Products Group customer service 387 email 387 web-based technical support 387 context save and restore 34 customer service 387

# D

DDR architecture 271 design example 282 I/O options 273 input/output support 275 instantiating registers 276 design example 71 design recommendations 62 device architecture 147 DirectC 346 DirectC code 351

### Ε

efficient long-line resources 19 encryption 355

### F

FIFO features 157 initializing 164 memory block consumption 163 software support 170 usage 160 flash switch for programming 9 Flash\*Freeze design flow 39 design guide 34 device behavior 30 I/O state 28 management IP 36 pin locations 31 type 1 24 type 2 26 **ULSICC 40** Flash\*Freeze mode 24

sleep 32 static 23 summary 23 product support customer service 387 email 387 My Cases 388 outside the U.S. 388 technical support 387 website 387 programmers 291 device support 294 programming AES encryption 319 basics 289 features 289 file header definition 323 flash and antifuse 291 flash devices 289 glossary 324 guidelines for flash programming 295 header pin numbers 336 microprocessor 349 power supplies 329 security 313 solution 334 solutions 293 voltage 329 volume services 292 programming support 287

### R

RAM memory block consumption 163 remote upgrade via TCP/IP 354 routing structure 18

### S

security 330 architecture 303 encrypted programming 354 examples 308 features 304 FlashLock 307 FlashROM 137 FlashROM use models 311 in programmable logic 301 overview 301 shutdown mode 32 context save and restore 34 signal integrity problem 337 silicon testing 370 sleep mode 32 context save and restore 34 SmartGen 170 spine architecture 57 spine assignment 68 SRAM features 153 initializing 164 software support 170 usage 157 STAPL player 351 STAPL vs. DirectC 353 static mode 23 switching circuit 344 verification 344 synthesizing 258

## Т

TAP controller state machine 357, 366 tech support ITAR 388 My Cases 388 outside the U.S. 388 technical support 387 transient current VCC 376 VCCI 376 transient current, power-up/-down 375

### U

UJTAG CCC dynamic reconfiguration 368 fine tuning 369 macro 365 operation 366 port usage 367 use to read FlashROM contents 363 ULSICC 40 ultra-fast local lines 18

### V

variable aspect ratio and cascading 161 VersaNet global networks 49 VersaTile 15 very-long-line resources 19 ViewDraw 257 VREF pins manually assigning 265

### W

web-based technical support 387