Welcome to <u>E-XFL.COM</u>

### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | 36864                                                         |

| Number of I/O                  | 97                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.14V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 144-LBGA                                                      |

| Supplier Device Package        | 144-FPBGA (13x13)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p250l-fg144i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

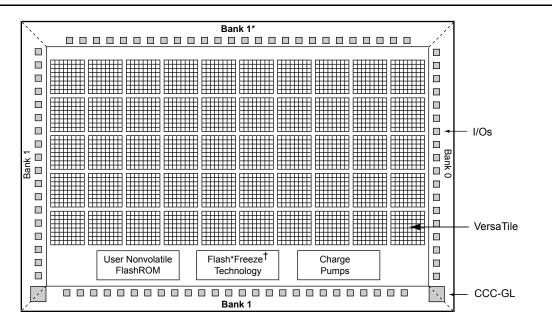

## **Device Overview**

Low power flash devices consist of multiple distinct programmable architectural features (Figure 1-5 on page 13 through Figure 1-7 on page 14):

- FPGA fabric/core (VersaTiles)

- Routing and clock resources (VersaNets)

- FlashROM

- Dedicated SRAM and/or FIFO

- 30 k gate and smaller device densities do not support SRAM or FIFO.

- Automotive devices do not support FIFO operation.

- I/O structures

- Flash\*Freeze technology and low power modes

Notes: \* Bank 0 for the 30 k devices

† Flash\*Freeze mode is supported on IGLOO devices.

Flash\*Freeze Technology and Low Power Modes

# Flash Families Support the Flash\*Freeze Feature

The low power flash FPGAs listed in Table 2-1 support the Flash\*Freeze feature and the functions described in this document.

### Table 2-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

## Low Power Modes Overview

Table 2-2 summarizes the low power modes that achieve power consumption reduction when the FPGA or system is idle.

| Mode     |                        | VCCI | vcc | Core | Clocks | ULSICC<br>Macro                          | To Enter<br>Mode                         | To Resume<br>Operation                 | Trigger  |

|----------|------------------------|------|-----|------|--------|------------------------------------------|------------------------------------------|----------------------------------------|----------|

| Active   |                        | On   | On  | On   | On     | N/A                                      | Initiate clock                           | None                                   | _        |

| Static   | ldle                   | On   | On  | On   | Off    | N/A                                      | Stop clock                               | Initiate<br>clock                      | External |

|          | Flash*Freeze<br>type 1 | On   | On  | On   | On*    | N/A                                      | Assert FF<br>pin                         | Deassert<br>FF pin                     | External |

|          | Flash*Freeze<br>type 2 | On   | On  | On   | On*    | Used to<br>enter<br>Flash*Freeze<br>mode | Assert FF<br>pin and<br>assert<br>LSICC  | Deassert<br>FF pin                     | External |

| Sleep    |                        | On   | Off | Off  | Off    | N/A                                      | Shut down<br>VCC                         | Turn on<br>VCC supply                  | External |

| Shutdown |                        | Off  | Off | Off  | Off    | N/A                                      | Shut down<br>VCC and<br>VCCI<br>supplies | Turn on<br>VCC and<br>VCCI<br>supplies | External |

### Table 2-2 • Power Modes Summary

\* External clocks can be left toggling while the device is in Flash\*Freeze mode. Clocks generated by the embedded PLL will be turned off automatically.

# Static (Idle) Mode

In Static (Idle) mode, none of the clock inputs is switching, and static power is the only power consumed by the device. This mode can be achieved by switching off the incoming clocks to the FPGA, thus benefitting from reduced power consumption. In addition, I/Os draw only minimal leakage current. In this mode, embedded SRAM, I/Os, and registers retain their values so the device can enter and exit this mode just by switching the clocks on or off.

If the device-embedded PLL is used as the clock source, Static (Idle) mode can easily be entered by pulling the PLL POWERDOWN pin LOW (active Low), which will turn off the PLL.

Flash\*Freeze Technology and Low Power Modes

# **Sleep and Shutdown Modes**

## **Sleep Mode**

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs support Sleep mode when device functionality is not required. In Sleep mode,  $V_{CC}$  (core voltage),  $V_{JTAG}$  (JTAG DC voltage), and VPUMP (programming voltage) are grounded, resulting in the FPGA core being turned off to reduce power consumption. While the device is in Sleep mode, the rest of the system can still be operating and driving the input buffers of the device. The driven inputs do not pull up the internal power planes, and the current draw is limited to minimal leakage current.

Table 2-7 shows the power supply status in Sleep mode.

### Table 2-7 • Sleep Mode—Power Supply Requirement for IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 Devices

| Power Supplies | Power Supply State |

|----------------|--------------------|

| VCC            | Powered off        |

| VCCI = VMV     | Powered on         |

| VJTAG          | Powered off        |

| VPUMP          | Powered off        |

Refer to the "Power-Up/-Down Behavior" section on page 33 for more information about I/O states during Sleep mode and the timing diagram for entering and exiting Sleep mode.

## Shutdown Mode

Shutdown mode is supported for all IGLOO nano and IGLOO PLUS devices as well the following IGLOO/e devices: AGL015, AGL030, AGLE600, AGLE3000, and A3PE3000L. Shutdown mode can be used by turning off all power supplies when the device function is not needed. Cold-sparing and hot-insertion features enable these devices to be powered down without turning off the entire system. When power returns, the live-at-power-up feature enables operation of the device after reaching the voltage activation point.

ProASIC3L FPGA Fabric User's Guide

| Date                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                          | Page     |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| v2.1<br>(October 2008) | The title changed from "Flash*Freeze Technology and Low Power Modes in IGLOO, IGLOO PLUS, and ProASIC3L Devices" to Actel's Flash*Freeze Technology and Low Power Modes."                                                                                                                                                                                                                                        | N/A      |  |  |  |

|                        | The "Flash Families Support the Flash*Freeze Feature" section was updated.                                                                                                                                                                                                                                                                                                                                       | 22       |  |  |  |

|                        | Significant changes were made to this document to support Libero IDE v8.4 and later functionality. RT ProASIC3 device support information is new. In addition to the other major changes, the following tables and figures were updated or are new:<br>Figure 2-3 • Flash*Freeze Mode Type 2 – Controlled by Flash*Freeze Pin and                                                                                |          |  |  |  |

|                        | Internal Logic (LSICC signal) – updated<br>Figure 2-5 • Narrow Clock Pulses During Flash*Freeze Entrance and Exit – new                                                                                                                                                                                                                                                                                          | 27       |  |  |  |

|                        | Figure 2-10 • Flash*Freeze Management IP Block Diagram – new                                                                                                                                                                                                                                                                                                                                                     | 30       |  |  |  |

|                        | Figure 2-11 • FSM State Diagram – new                                                                                                                                                                                                                                                                                                                                                                            | 37       |  |  |  |

|                        | Table 2-6 • IGLOO nano and IGLOO PLUS Flash*Freeze Mode (type 1 and type 2)—I/O Pad State – updated                                                                                                                                                                                                                                                                                                              | 38<br>29 |  |  |  |

|                        | Please review the entire document carefully.                                                                                                                                                                                                                                                                                                                                                                     | 20       |  |  |  |

| v1.3<br>(June 2008)    | The family description for ProASIC3L in Table 2-1 • Flash-Based FPGAs was updated to include 1.5 V.                                                                                                                                                                                                                                                                                                              | 22       |  |  |  |

| v1.2<br>(March 2008)   | The part number for this document was changed from 51700094-003-1 to 51700094-004-2.                                                                                                                                                                                                                                                                                                                             | N/A      |  |  |  |

|                        | The title of the document was changed to "Flash*Freeze Technology and Low Power Modes in IGLOO, IGLOO PLUS, and ProASIC3L Devices."                                                                                                                                                                                                                                                                              |          |  |  |  |

|                        | The "Flash*Freeze Technology and Low Power Modes" section was updated to remove the parenthetical phrase, "from 25 $\mu$ W," in the second paragraph. The following sentence was added to the third paragraph: "IGLOO PLUS has an additional feature when operating in Flash*Freeze mode, allowing it to retain I/O states as well as SRAM and register states."                                                 | 21       |  |  |  |

|                        | The "Power Conservation Techniques" section was updated to add $V_{JTAG}$ to the parenthetical list of power supplies that should be tied to the ground plane if unused. Additional information was added regarding how the software configures unused I/Os.                                                                                                                                                     | 2-1      |  |  |  |

|                        | Table 2-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                                                                                | 22       |  |  |  |

|                        | The "Flash*Freeze Mode" section was revised to include that I/O states are preserved in Flash*Freeze mode for IGLOO PLUS devices. The last sentence in the second paragraph was changed to, "If the FF pin is not used, it can be used as a regular I/O." The following sentence was added for Flash*Freeze mode type 2: "Exiting the mode is controlled by either the FF pin OR the user-defined LSICC signal." | 24       |  |  |  |

|                        | The "Flash*Freeze Type 1: Control by Dedicated Flash*Freeze Pin" section was revised to change instructions for implementing this mode, including instructions for implementation with Libero IDE v8.3.                                                                                                                                                                                                          | 24       |  |  |  |

|                        | Figure 2-1 • Flash*Freeze Mode Type 1 – Controlled by the Flash*Freeze Pin was updated.                                                                                                                                                                                                                                                                                                                          | 25       |  |  |  |

|                        | The "Flash*Freeze Type 2: Control by Dedicated Flash*Freeze Pin and Internal Logic" section was renamed from "Type 2 Software Implementation."                                                                                                                                                                                                                                                                   | 26       |  |  |  |

|                        | The "Type 2 Software Implementation for Libero IDE v8.3" section is new.                                                                                                                                                                                                                                                                                                                                         | 2-6      |  |  |  |

Global Resources in Low Power Flash Devices

|                        | able 3-3 • Quadrant Global Pin Name (continued) |                                                         |  |  |  |

|------------------------|-------------------------------------------------|---------------------------------------------------------|--|--|--|

| Differential I/O Pairs | GAAO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GAA1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GABO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GAB1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GACO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GAC1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GBAO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GBA1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GBBO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GBB1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GBCO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GBC1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GDAO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GDA1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GDBO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GDB1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GDCO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GDC1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GEAO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GEA1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GEBO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GEB1/IOuxwByVz                                  |                                                         |  |  |  |

|                        | GECO/IOuxwByVz                                  | The output of the different pair will drive the global. |  |  |  |

|                        | GEC1/IOuxwByVz                                  |                                                         |  |  |  |

### Table 3-3 • Quadrant Global Pin Name (continued)

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

## **Unused Global I/O Configuration**

The unused clock inputs behave similarly to the unused Pro I/Os. The Microsemi Designer software automatically configures the unused global pins as inputs with pull-up resistors if they are not used as regular I/O.

## I/O Banks and Global I/O Standards

In low power flash devices, any I/O or internal logic can be used to drive the global network. However, only the global macro placed at the global pins will use the hardwired connection between the I/O and global network. Global signal (signal driving a global macro) assignment to I/O banks is no different from regular I/O assignment to I/O banks with the exception that you are limited to the pin placement location available. Only global signals compatible with both the VCCI and VREF standards can be assigned to the same bank.

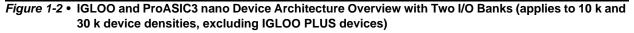

# 4 – Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## Introduction

This document outlines the following device information: Clock Conditioning Circuit (CCC) features, PLL core specifications, functional descriptions, software configuration information, detailed usage information, recommended board-level considerations, and other considerations concerning clock conditioning circuits and global networks in low power flash devices or mixed signal FPGAs.

## **Overview of Clock Conditioning Circuitry**

In Fusion, IGLOO, and ProASIC3 devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations. The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides. For device-specific variations, refer to the "Device-Specific Layout" section on page 94.

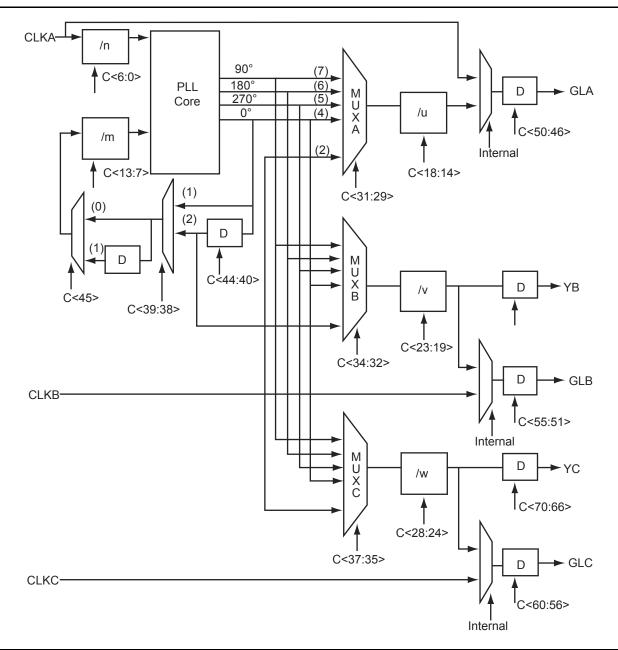

The CCC is composed of the following:

- PLL core

- 3 phase selectors

- 6 programmable delays and 1 fixed delay that advances/delays phase

- 5 programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 4-6 on page 87 because they are automatically configured based on the user's required frequencies)

- · 1 dynamic shift register that provides CCC dynamic reconfiguration capability

Figure 4-1 provides a simplified block diagram of the physical implementation of the building blocks in each of the CCCs.

Figure 4-1 • Overview of the CCCs Offered in Fusion, IGLOO, and ProASIC3

ProASIC3L FPGA Fabric User's Guide

Figure 4-22 • CCC Block Control Bits – Graphical Representation of Assignments

FlashROM in Microsemi's Low Power Flash Devices

# FlashROM Support in Flash-Based Devices

The flash FPGAs listed in Table 5-1 support the FlashROM feature and the functions described in this document.

### Table 5-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

256×18 FIFO is full, even though a 128×18 FIFO was requested. For this example, the Almost-Full flag can be used instead of the Full flag to signal when the 128th data word is reached.

To accommodate different aspect ratios, the almost-full and almost-empty values are expressed in terms of data bits instead of data words. SmartGen translates the user's input, expressed in data words, into data bits internally. SmartGen allows the user to select the thresholds for the Almost-Empty and Almost-Full flags in terms of either the read data words or the write data words, and makes the appropriate conversions for each flag.

After the empty or full states are reached, the FIFO can be configured so the FIFO counters either stop or continue counting. For timing numbers, refer to the appropriate family datasheet.

### Signal Descriptions for FIFO4K18

The following signals are used to configure the FIFO4K18 memory element:

### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 6-6).

| WW[2:0]       | RW[2:0]       | D×W      |

|---------------|---------------|----------|

| 000           | 000           | 4k×1     |

| 001           | 001           | 2k×2     |

| 010           | 010           | 1k×4     |

| 011           | 011           | 512×9    |

| 100           | 100           | 256×18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

### Table 6-6 • Aspect Ratio Settings for WW[2:0]

### WBLK and RBLK

These signals are active-low and will enable the respective ports when LOW. When the RBLK signal is HIGH, that port's outputs hold the previous value.

### WEN and REN

Read and write enables. WEN is active-low and REN is active-high by default. These signals can be configured as active-high or -low.

### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

# Note: For the Automotive ProASIC3 FIFO4K18, for the same clock, 180° out of phase (inverted) between clock pins should be used.

### RPIPE

This signal is used to specify pipelined read on the output. A LOW on RPIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the output in the next clock cycle.

### RESET

This active-low signal resets the control logic and forces the output hold state registers to zero when asserted. It does not reset the contents of the memory array (Table 6-7 on page 160).

While the RESET signal is active, read and write operations are disabled. As with any asynchronous RESET signal, care must be taken not to assert it too close to the edges of active read and write clocks.

### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 6-7 on page 160).

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

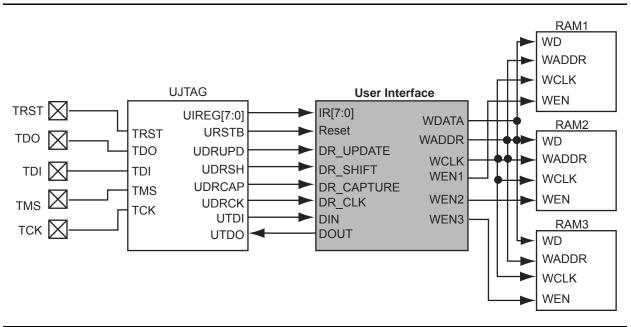

# Initializing the RAM/FIFO

The SRAM blocks can be initialized with data to use as a lookup table (LUT). Data initialization can be accomplished either by loading the data through the design logic or through the UJTAG interface. The UJTAG macro is used to allow access from the JTAG port to the internal logic in the device. By sending the appropriate initialization string to the JTAG Test Access Port (TAP) Controller, the designer can put the JTAG circuitry into a mode that allows the user to shift data into the array logic through the JTAG port using the UJTAG macro. For a more detailed explanation of the UJTAG macro, refer to the "FlashROM in Microsemi's Low Power Flash Devices" section on page 133.

A user interface is required to receive the user command, initialization data, and clock from the UJTAG macro. The interface must synchronize and load the data into the correct RAM block of the design. The main outputs of the user interface block are the following:

- Memory block chip select: Selects a memory block for initialization. The chip selects signals for each memory block that can be generated from different user-defined pockets or simple logic, such as a ring counter (see below).

- Memory block write address: Identifies the address of the memory cell that needs to be initialized.

- Memory block write data: The interface block receives the data serially from the UTDI port of the UJTAG macro and loads it in parallel into the write data ports of the memory blocks.

- Memory block write clock: Drives the WCLK of the memory block and synchronizes the write data, write address, and chip select signals.

Figure 6-8 shows the user interface between UJTAG and the memory blocks.

### Figure 6-8 • Interfacing TAP Ports and SRAM Blocks

An important component of the interface between the UJTAG macro and the RAM blocks is a serialin/parallel-out shift register. The width of the shift register should equal the data width of the RAM blocks. The RAM data arrives serially from the UTDI output of the UJTAG macro. The data must be shifted into a shift register clocked by the JTAG clock (provided at the UDRCK output of the UJTAG macro).

Then, after the shift register is fully loaded, the data must be transferred to the write data port of the RAM block. To synchronize the loading of the write data with the write address and write clock, the output of the shift register can be pipelined before driving the RAM block.

The write address can be generated in different ways. It can be imported through the TAP using a different instruction opcode and another shift register, or generated internally using a simple counter. Using a counter to generate the address bits and sweep through the address range of the RAM blocks is

SmartGen enables the user to configure the desired RAM element to use either a single clock for read and write, or two independent clocks for read and write. The user can select the type of RAM as well as the width/depth and several other parameters (Figure 6-13).

### Figure 6-13 • SmartGen Memory Configuration Interface

SmartGen also has a Port Mapping option that allows the user to specify the names of the ports generated in the memory block (Figure 6-14).

### *Figure 6-14* • Port Mapping Interface for SmartGen-Generated Memory

SmartGen also configures the FIFO according to user specifications. Users can select no flags, static flags, or dynamic flags. Static flag settings are configured using configuration flash and cannot be altered

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

| Date                | Changes                                                                                                                                                                                                                                                                                                                |     |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| v1.1<br>(continued) | Table 6-1 • Flash-Based FPGAs and associated text were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                           | 150 |  |  |

|                     | The text introducing Table 6-8 • Memory Availability per IGLOO and ProASIC3 Device was updated to replace "A3P030 and AGL030" with "15 k and 30 k gate devices." Table 6-8 • Memory Availability per IGLOO and ProASIC3 Device was updated to remove AGL400 and AGLE1500 and include IGLOO PLUS and ProASIC3L devices. | 162 |  |  |

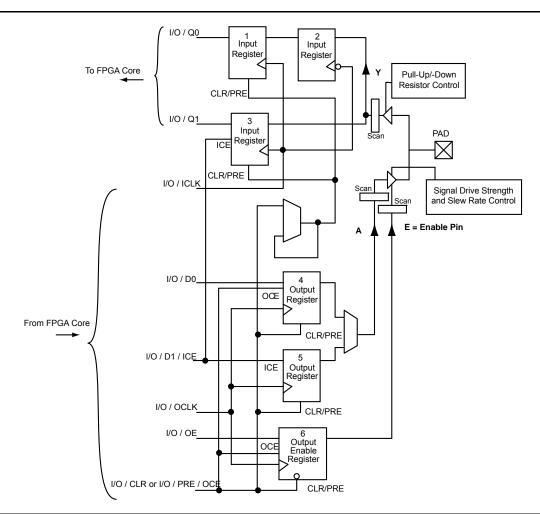

# 7 – I/O Structures in IGLOO and ProASIC3 Devices

## Introduction

Low power flash devices feature a flexible I/O structure, supporting a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank-selectable voltages. IGLOO,<sup>®</sup> ProASIC3<sup>®</sup>L, and ProASIC3 families support Standard, Standard Plus, and Advanced I/Os.

Users designing I/O solutions are faced with a number of implementation decisions and configuration choices that can directly impact the efficiency and effectiveness of their final design. The flexible I/O structure, supporting a wide variety of voltages and I/O standards, enables users to meet the growing challenges of their many diverse applications. Libero SoC software provides an easy way to implement I/Os that will result in robust I/O design.

This document first describes the two different I/O types in terms of the standards and features they support. It then explains the individual features and how to implement them in Libero SoC.

Figure 7-1 • DDR Configured I/O Block Logical Representation

I/O Structures in IGLOO and ProASIC3 Devices

| Solution | Board Components                                                                                                                                                                 | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Two resistors                                                                                                                                                                    | Low to High <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2        | Resistor and Zener 3.3 V                                                                                                                                                         | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3        | Bus switch                                                                                                                                                                       | High                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4        | Minimum resistor value <sup>2,3,4,5</sup><br>R = 47 $\Omega$ at T <sub>J</sub> = 70°C<br>R = 150 $\Omega$ at T <sub>J</sub> = 85°C<br>R = 420 $\Omega$ at T <sub>J</sub> = 100°C | Medium                   | Maximum diode current at 100% duty cycle, signal constantly at 1<br>52.7 mA at $T_J = 70^{\circ}$ C / 10-year lifetime<br>16.5 mA at $T_J = 85^{\circ}$ C / 10-year lifetime<br>5.9 mA at $T_J = 100^{\circ}$ C / 10-year lifetime<br>For duty cycles other than 100%, the currents can be<br>increased by a factor of 1 / (duty cycle).<br>Example: 20% duty cycle at 70°C<br>Maximum current = (1 / 0.2) × 52.7 mA = 5 × 52.7 mA =<br>263.5 mA |

### Table 7-13 • Comparison Table for 5 V–Compliant Receiver Solutions

Notes:

- 1. Speed and current consumption increase as the board resistance values decrease.

- 2. Resistor values ensure I/O diode long-term reliability.

- 3. At 70°C, customers could still use 420  $\Omega$  on every I/O.

- 4. At 85°C, a 5 V solution on every other I/O is permitted, since the resistance is lower (150  $\Omega$ ) and the current is higher. Also, the designer can still use 420  $\Omega$  and use the solution on every I/O.

- 5. At 100°C, the 5 V solution on every I/O is permitted, since 420  $\Omega$  are used to limit the current to 5.9 mA.

### 5 V Output Tolerance

IGLOO and ProASIC3 I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

## Schmitt Trigger

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

The Schmitt trigger is available for the LVTTL, LVCMOS, and 3.3 V PCI I/O standards.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 7-5 on page 179) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

I/O Structures in IGLOOe and ProASIC3E Devices

# Low Power Flash Device I/O Support

The low power flash FPGAs listed in Table 8-1 support I/Os and the functions described in this document.

### Table 8-1 • Flash-Based FPGAs

| Series                                                        | Family <sup>*</sup>  | Description                                                              |

|---------------------------------------------------------------|----------------------|--------------------------------------------------------------------------|

| IGLOO                                                         | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

| ProASIC3 ProASIC3E Higher density ProASIC3 FPGAs with six PLL |                      | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|                                                               | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|                                                               | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|                                                               | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

ProASIC3L FPGA Fabric User's Guide

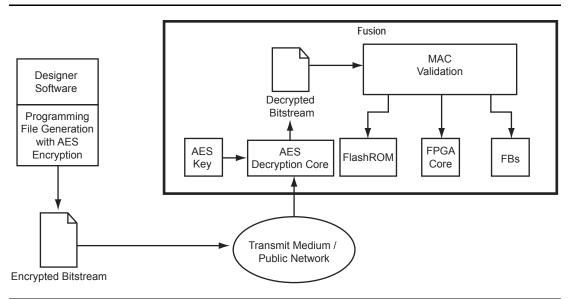

Figure 12-5 • Example Application Scenario Using AES in Fusion Devices

## FlashLock

### Additional Options for IGLOO and ProASIC3 Devices

The user also has the option of prohibiting Write operations to the FPGA array but allowing Verify operations on the FPGA array and/or Read operations on the FlashROM without the use of the FlashLock Pass Key. This option provides the user the freedom of verifying the FPGA array and/or reading the FlashROM contents after the device is programmed, without having to provide the FlashLock Pass Key. The user can incorporate AES encryption on the programming files to better enhance the level of security used.

## **Permanent Security Setting Options**

In applications where a permanent lock is not desired, yet the security settings should not be modifiable, IGLOO and ProASIC3 devices can accommodate this requirement.

This application is particularly useful in cases where a device is located at a remote location and must be reprogrammed with a design or data update. Refer to the "Application 3: Nontrusted Environment—Field Updates/Upgrades" section on page 310 for further discussion and examples of how this can be achieved.

The user must be careful when considering the Permanent FlashLock or Permanent Security Settings option. Once the design is programmed with the permanent settings, it is not possible to reconfigure the security settings already employed on the device. Therefore, exercise careful consideration before programming permanent settings.

### Permanent FlashLock

The purpose of the permanent lock feature is to provide the benefits of the highest level of security to IGLOO and ProASIC3 devices. If selected, the permanent FlashLock feature will create a permanent barrier, preventing any access to the contents of the device. This is achieved by permanently disabling Write and Verify access to the array, and Write and Read access to the FlashROM. After permanently locking the device, it has been effectively rendered one-time-programmable. This feature is useful if the intended applications do not require design or system updates to the device.

## **Programming File Header Definition**

In each STAPL programming file generated, there will be information about how the AES key and FlashLock Pass Key are configured. Table 12-8 shows the header definitions in STAPL programming files for different security levels.

| Security Level                                                     | STAPL File Header Definition          |  |

|--------------------------------------------------------------------|---------------------------------------|--|

| No security (no FlashLock Pass Key or AES key)                     | NOTE "SECURITY" "Disable";            |  |

| FlashLock Pass Key with no AES key                                 | NOTE "SECURITY" "KEYED ";             |  |

| FlashLock Pass Key with AES key                                    | NOTE "SECURITY" "KEYED ENCRYPT ";     |  |

| Permanent Security Settings option enabled                         | NOTE "SECURITY" "PERMLOCK ENCRYPT ";  |  |

| AES-encrypted FPGA array (for programming updates)                 | NOTE "SECURITY" "ENCRYPT CORE ";      |  |

| AES-encrypted FlashROM (for programming updates)                   | NOTE "SECURITY" "ENCRYPT FROM ";      |  |

| AES-encrypted FPGA array and FlashROM (for<br>programming updates) | NOTE "SECURITY" "ENCRYPT FROM CORE "; |  |

## **Example File Headers**

STAPL Files Generated with FlashLock Key and AES Key Containing Key Information

- FlashLock Key / AES key indicated in STAPL file header definition

- · Intended ONLY for secured/trusted environment programming applications

```

_____

NOTE "CREATOR" "Designer Version: 6.1.1.108";

NOTE "DEVICE" "A3PE600";

NOTE "PACKAGE" "208 PQFP";

NOTE "DATE" "2005/04/08";

NOTE "STAPL_VERSION" "JESD71";

NOTE "IDCODE" "$123261CF";

NOTE "DESIGN" "counter32";

NOTE "CHECKSUM" "$EDB9";

NOTE "SAVE_DATA" "FRomStream";

NOTE "SECURITY" "KEYED ENCRYPT ";

NOTE "ALG_VERSION" "1";

NOTE "MAX FREO" "20000000";

NOTE "SILSIG" "$0000000";

NOTE "PASS_KEY" "$00123456789012345678901234567890";

NOTE "AES_KEY" "$ABCDEFABCDEFABCDEFABCDEFABCDEFAB;

_____

```

# List of Changes

| Date                   | Changes                                                                                                                                               | Page |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010              | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.             | N/A  |

| v1.1<br>(October 2008) | The "Introduction" was revised to include information about the core supply voltage range of operation in V2 devices.                                 | 341  |

|                        | IGLOO nano device support was added to Table 14-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit.                                           | 342  |

|                        | The "Circuit Description" section was updated to include IGLOO PLUS core operation from 1.2 V to 1.5 V in 50 mV increments.                           | 343  |

| v1.0<br>(August 2008)  | The "Microsemi's Flash Families Support Voltage Switching Circuit" section was revised to include new families and make the information more concise. | 342  |

The following table lists critical changes that were made in each revision of the chapter.