EXF

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Product StatusObsoleteNumber of LABs/CLBs-Number of Logic Elements/Cells-Total RAM Bits36864Number of I/O97Number of Gates250000Voltage - Supply1.14V ~ 1.575VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGASupplier Device Package144-FPBGA (13x13) | Details                        |                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------|

| Number of Logic Elements/Cells-Total RAM Bits36864Number of I/O97Number of Gates250000Voltage - Supply1.14V ~ 1.575VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGA                                                                                   | Product Status                 | Obsolete                                                       |

| Total RAM Bits36864Number of I/O97Number of Gates250000Voltage - Supply1.14V ~ 1.575VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGA                                                                                                                  | Number of LABs/CLBs            | -                                                              |

| Number of I/O97Number of Gates250000Voltage - Supply1.14V ~ 1.575VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGA                                                                                                                                     | Number of Logic Elements/Cells | -                                                              |

| Number of Gates250000Voltage - Supply1.14V ~ 1.575VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGA                                                                                                                                                    | Total RAM Bits                 | 36864                                                          |

| Voltage - Supply1.14V ~ 1.575VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGA                                                                                                                                                                         | Number of I/O                  | 97                                                             |

| Mounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGA                                                                                                                                                                                                       | Number of Gates                | 250000                                                         |

| Operating Temperature-40°C ~ 100°C (TJ)Package / Case144-LBGA                                                                                                                                                                                                                                 | Voltage - Supply               | 1.14V ~ 1.575V                                                 |

| Package / Case 144-LBGA                                                                                                                                                                                                                                                                       | Mounting Type                  | Surface Mount                                                  |

|                                                                                                                                                                                                                                                                                               | Operating Temperature          | -40°C ~ 100°C (TJ)                                             |

| Supplier Device Package144-FPBGA (13x13)                                                                                                                                                                                                                                                      | Package / Case                 | 144-LBGA                                                       |

|                                                                                                                                                                                                                                                                                               | Supplier Device Package        | 144-FPBGA (13x13)                                              |

| Purchase URL https://www.e-xfl.com/product-detail/microsemi/a3p250l-fgg144i                                                                                                                                                                                                                   | Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p250l-fgg144i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ProASIC3L FPGA Fabric User's Guide

| FlashROM Security Use Models                                                               | 311   |

|--------------------------------------------------------------------------------------------|-------|

| Generating Programming Files                                                               | 313   |

| Conclusion                                                                                 | 324   |

| Glossary                                                                                   | 324   |

| References                                                                                 | 324   |

| Related Documents                                                                          | 325   |

| List of Changes                                                                            | 325   |

|                                                                                            |       |

| 13 In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X | 327   |

| Introduction                                                                               | 327   |

| ISP Architecture                                                                           | 327   |

| ISP Support in Flash-Based Devices                                                         | 328   |

| Programming Voltage (VPUMP) and VJTAG                                                      | 329   |

| Nonvolatile Memory (NVM) Programming Voltage                                               | 329   |

| IEEE 1532 (JTAG) Interface                                                                 | 330   |

| Security                                                                                   | 330   |

| Security in ARM-Enabled Low Power Flash Devices                                            | 331   |

| FlashROM and Programming Files                                                             | 333   |

| Programming Solution                                                                       | 334   |

| ISP Programming Header Information                                                         | 335   |

| Board-Level Considerations                                                                 | 337   |

| Conclusion                                                                                 | 338   |

| Related Documents                                                                          | 338   |

| List of Changes                                                                            | 339   |

|                                                                                            |       |

| 14 Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming            | . 341 |

| Introduction                                                                               | 341   |

| Microsemi's Flash Families Support Voltage Switching Circuit                               | 342   |

| Circuit Description                                                                        | 343   |

| Circuit Verification                                                                       | 344   |

| DirectC                                                                                    | 346   |

| Conclusion                                                                                 | 346   |

| List of Changes                                                                            | 347   |

|                                                                                            |       |

| 15 Microprocessor Programming of Microsemi's Low Power Flash Devices                       |       |

|                                                                                            |       |

| Microprocessor Programming Support in Flash Devices                                        |       |

| Programming Algorithm                                                                      |       |

| Implementation Overview                                                                    |       |

| Hardware Requirement                                                                       | 354   |

| Security                                                                                   |       |

| Conclusion                                                                                 | 355   |

| List of Changes                                                                            | 356   |

|                                                                                            | 0.57  |

| 16 Boundary Scan in Low Power Flash Devices.                                               |       |

| Boundary Scan                                                                              |       |

| TAP Controller State Machine                                                               |       |

| Microsemi's Flash Devices Support the JTAG Feature                                         |       |

| Boundary Scan Support in Low Power Devices                                                 |       |

| Boundary Scan Opcodes                                                                      | 359   |

Flash\*Freeze Technology and Low Power Modes

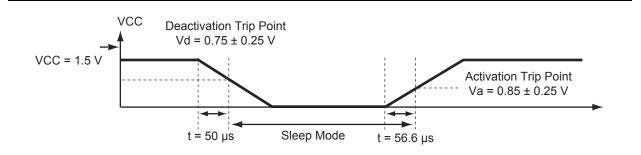

power supply and board-level configurations, the user can easily calculate how long it will take for the core to become inactive or active. For more information, refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373.

Figure 2-8 • Entering and Exiting Sleep Mode, Typical Timing Diagram

### **Context Save and Restore in Sleep or Shutdown Mode**

In Sleep mode or Shutdown mode, the contents of the SRAM, state of the I/Os, and state of the registers are lost when the device is powered off, if no other measure is taken. A low-cost external serial EEPROM can be used to save and restore the contents of the device when entering and exiting Sleep mode or Shutdown mode. In the *Embedded SRAM Initialization Using External Serial EEPROM* application note, detailed information and a reference design are provided for initializing the embedded SRAM using an external serial EEPROM. The user can easily customize the reference design to save and restore the FPGA state when entering and exiting Sleep mode or Shutdown mode. The microcontroller will need to manage this activity; hence, before powering down  $V_{CC}$ , the data will be read from the FPGA and stored externally. In a similar way, after the FPGA is powered up, the microcontroller will allow the FPGA to load the data from external memory and restore its original state.

# Flash\*Freeze Design Guide

This section describes how designers can create reliable designs that use ultra-low power Flash\*Freeze modes optimally. The section below provides guidance on how to select the best Flash\*Freeze mode for any application. The "Design Solutions" section on page 35 gives specific recommendations on how to design and configure clocks, set/reset signals, and I/Os. This section also gives an overview of the design flow and provides details concerning Microsemi's Flash\*Freeze Management IP, which enables clean clock gating and housekeeping. The "Additional Power Conservation Techniques" section on page 41 describes board-level considerations for entering and exiting Flash\*Freeze mode.

## Selecting the Right Flash\*Freeze Mode

Both Flash\*Freeze modes will bring an FPGA into an ultra-low power static mode that retains register and SRAM content and sets I/Os to a predetermined configuration. There are two primary differences that distinguish type 2 mode from type 1, and they must be considered when creating a design using Flash\*Freeze technology.

First, with type 2 mode, the device has an opportunity to wait for a second signal to enable activation of Flash\*Freeze mode. This allows processes to complete prior to deactivating the device, and can be useful to control task completion, data preservation, accidental Flash\*Freeze activation, system shutdown, or any other housekeeping function. The second signal may be derived from an external or into-out internal source. The second difference between type 1 and type 2 modes is that a design for type 2 mode has an opportunity to cleanly manage clocks and data activity before entering and exiting Flash\*Freeze mode. This is particularly important when data preservation is needed, as it ensures valid data is stored prior to entering, and upon exiting, Flash\*Freeze mode.

Type 1 Flash\*Freeze mode is ideally suited for applications with the following design criteria:

- Entering Flash\*Freeze mode is not dependent on any signal other than the external FF pin.

- Internal housekeeping is not required prior to entering Flash\*Freeze.

Global Resources in Low Power Flash Devices

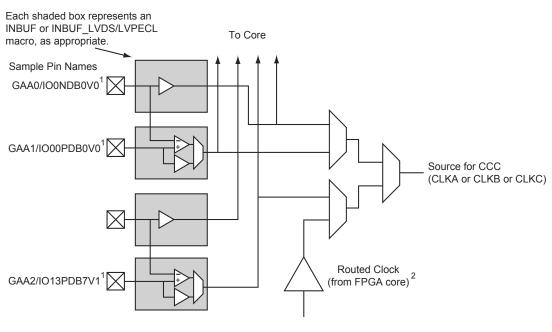

Figure 3-5 shows more detailed global input connections. It shows the global input pins connection to the northwest quadrant global networks. Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection (not supported for IGLOO nano or ProASIC3 nano devices)

- The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Figure 3-5 • Global I/O Overview

Global Resources in Low Power Flash Devices

| I/О Туре               | Beginning of I/O Name | Notes                                                        |  |  |  |

|------------------------|-----------------------|--------------------------------------------------------------|--|--|--|

| Single-Ended           | GFAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a ch       |  |  |  |

|                        | GFA1/IOuxwByVz        | global at a time.                                            |  |  |  |

|                        | GFA2/IOuxwByVz        |                                                              |  |  |  |

|                        | GFBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |  |  |

|                        | GFB1/IOuxwByVz        | global at a time.                                            |  |  |  |

|                        | GFB2/IOuxwByVz        |                                                              |  |  |  |

|                        | GFC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |  |  |

|                        | GFC1/IOuxwByVz        | global at a time.                                            |  |  |  |

|                        | GFC2/IOuxwByVz        |                                                              |  |  |  |

|                        | GCAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |  |  |

|                        | GCA1/IOuxwByVz        | global at a time.                                            |  |  |  |

|                        | GCA2/IOuxwByVz        |                                                              |  |  |  |

|                        | GCBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |  |  |

|                        | GCB1/IOuxwByVz        | global at a time.                                            |  |  |  |

|                        | GCB2/IOuxwByVz        |                                                              |  |  |  |

|                        | GCC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |  |  |

|                        | GCC1/IOuxwByVz        | global at a time.                                            |  |  |  |

|                        | GCC2/IOuxwByVz        |                                                              |  |  |  |

| Differential I/O Pairs | GFAO/IOuxwByVz        | The output of the different pair will drive the chip globa   |  |  |  |

|                        | GFA1/IOuxwByVz        |                                                              |  |  |  |

|                        | GFBO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |  |  |

|                        | GFB1/IOuxwByVz        |                                                              |  |  |  |

|                        | GFCO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |  |  |

|                        | GFC1/IOuxwByVz        |                                                              |  |  |  |

|                        | GCAO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |  |  |

|                        | GCA1/IOuxwByVz        |                                                              |  |  |  |

|                        | GCBO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |  |  |

|                        | GCB1/IOuxwByVz        |                                                              |  |  |  |

|                        | GCCO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |  |  |

|                        | GCC1/IOuxwByVz        |                                                              |  |  |  |

#### Table 3-2 • Chip Global Pin Name

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

# List of Changes

| Date                    | Changes                                                                                                                                                                                                                                                                                                                      | Page   |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                    |        |  |  |

|                         | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                                                                                                                                    |        |  |  |

|                         | The "Global Architecture" section and "VersaNet Global Network Distribution" section were revised for clarity (SARs 20646, 24779).                                                                                                                                                                                           | 47, 49 |  |  |

|                         | The "I/O Banks and Global I/Os" section was moved earlier in the document, renamed to "Chip and Quadrant Global I/Os", and revised for clarity. Figure 3-4 • Global Connections Details, Figure 3-6 • Global Inputs, Table 3-2 • Chip Global Pin Name, and Table 3-3 • Quadrant Global Pin Name are new (SARs 20646, 24779). | 51     |  |  |

|                         | The "Clock Aggregation Architecture" section was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                | 57     |  |  |

|                         | Figure 3-7 • Chip Global Aggregation was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                        | 59     |  |  |

|                         | The "Global Macro and Placement Selections" section is new (SARs 20646, 24779).                                                                                                                                                                                                                                              | 64     |  |  |

| v1.4<br>(December 2008) | The "Global Architecture" section was updated to include 10 k devices, and to include information about VersaNet global support for IGLOO nano devices.                                                                                                                                                                      | 47     |  |  |

|                         | The Table 3-1 • Flash-Based FPGAs was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                               |        |  |  |

|                         | The "VersaNet Global Network Distribution" section was updated to include 10 k devices and to note an exception in global lines for nano devices.                                                                                                                                                                            |        |  |  |

|                         | Figure 3-2 • Simplified VersaNet Global Network (30 k gates and below) is new.                                                                                                                                                                                                                                               | 50     |  |  |

|                         | The "Spine Architecture" section was updated to clarify support for 10 k and nano devices.                                                                                                                                                                                                                                   | 57     |  |  |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                  | 57     |  |  |

|                         | The figure in the CLKBUF_LVDS/LVPECL row of Table 3-8 • Clock Macros was updated to change CLKBIBUF to CLKBUF.                                                                                                                                                                                                               | 62     |  |  |

| v1.3<br>(October 2008)  | A third bullet was added to the beginning of the "Global Architecture" section: In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.                                                                                         |        |  |  |

|                         | The "Global Resource Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                      |        |  |  |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include A3PE600/L in the device column.                                                                                                                                                                                                        |        |  |  |

|                         | Table note 1 was revised in Table 3-9 • I/O Standards within CLKBUF to include AFS600 and AFS1500.                                                                                                                                                                                                                           | 63     |  |  |

| v1.2<br>(June 2008)     | <ul><li>The following changes were made to the family descriptions in Table 3-1 • Flash-Based FPGAs:</li><li>ProASIC3L was updated to include 1.5 V.</li></ul>                                                                                                                                                               | 48     |  |  |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                                               |        |  |  |

The following table lists critical changes that were made in each revision of the chapter.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

global assignments are not allocated properly. See the "Physical Constraints for Quadrant Clocks" section for information on assigning global signals to the quadrant clock networks.

Promoted global signals will be instantiated with CLKINT macros to drive these signals onto the global network. This is automatically done by Designer when the Auto-Promotion option is selected. If the user wishes to assign the signals to the quadrant globals instead of the default chip globals, this can done by using ChipPlanner, by declaring a physical design constraint (PDC), or by importing a PDC file.

#### **Physical Constraints for Quadrant Clocks**

If it is necessary to promote global clocks (CLKBUF, CLKINT, PLL, CLKDLY) to quadrant clocks, the user can define PDCs to execute the promotion. PDCs can be created using PDC commands (pre-compile) or the MultiView Navigator (MVN) interface (post-compile). The advantage of using the PDC flow over the MVN flow is that the Compile stage is able to automatically promote any regular net to a global net before assigning it to a quadrant. There are three options to place a quadrant clock using PDC commands:

- Place a clock core (not hardwired to an I/O) into a quadrant clock location.

- Place a clock core (hardwired to an I/O) into an I/O location (set\_io) or an I/O module location (set\_location) that drives a quadrant clock location.

- Assign a net driven by a regular net or a clock net to a quadrant clock using the following command:

assign\_local\_clock -net <net name> -type quadrant <quadrant clock region>

where

<net name> is the name of the net assigned to the local user clock region.

<quadrant clock region> defines which quadrant the net should be assigned to. Quadrant clock regions are defined as UL (upper left), UR (upper right), LL (lower left), and LR (lower right).

Note: If the net is a regular net, the software inserts a CLKINT buffer on the net.

#### For example:

assign\_local\_clock -net localReset -type quadrant UR

Keep in mind the following when placing quadrant clocks using MultiView Navigator:

#### Hardwired I/O–Driven CCCs

• Find the associated clock input port under the Ports tab, and place the input port at one of the Gmn\* locations using PinEditor or I/O Attribute Editor, as shown in Figure 4-32.

Figure 4-32 • Port Assignment for a CCC with Hardwired I/O Clock Input

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **Recommended Board-Level Considerations**

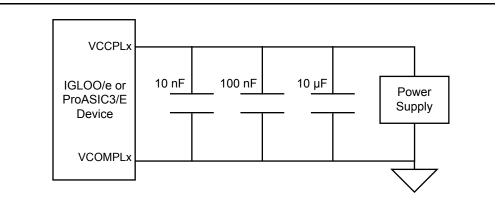

The power to the PLL core is supplied by VCCPLA/B/C/D/E/F (VCCPLx), and the associated ground connections are supplied by VCOMPLA/B/C/D/E/F (VCOMPLx). When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Optionally, the PLL can be turned on/off during normal device operation via the POWERDOWN port (see Table 4-3 on page 84).

## PLL Power Supply Decoupling Scheme

The PLL core is designed to tolerate noise levels on the PLL power supply as specified in the datasheets. When operated within the noise limits, the PLL will meet the output peak-to-peak jitter specifications specified in the datasheets. User applications should always ensure the PLL power supply is powered from a noise-free or low-noise power source.

However, in situations where the PLL power supply noise level is higher than the tolerable limits, various decoupling schemes can be designed to suppress noise to the PLL power supply. An example is provided in Figure 4-38. The VCCPLx and VCOMPLx pins correspond to the PLL analog power supply and ground.

Microsemi strongly recommends that two ceramic capacitors (10 nF in parallel with 100 nF) be placed close to the power pins (less than 1 inch away). A third generic 10  $\mu$ F electrolytic capacitor is recommended for low-frequency noise and should be placed farther away due to its large physical size. Microsemi recommends that a 6.8  $\mu$ H inductor be placed between the supply source and the capacitors to filter out any low-/medium- and high-frequency noise. In addition, the PCB layers should be controlled so the VCCPLx and VCOMPLx planes have the minimum separation possible, thus generating a good-quality RF capacitor.

For more recommendations, refer to the Board-Level Considerations application note.

Recommended 100 nF capacitor:

- Producer BC Components, type X7R, 100 nF, 16 V

- BC Components part number: 0603B104K160BT

- Digi-Key part number: BC1254CT-ND

- Digi-Key part number: BC1254TR-ND

Recommended 10 nF capacitor:

- Surface-mount ceramic capacitor

- Producer BC Components, type X7R, 10 nF, 50 V

- BC Components part number: 0603B103K500BT

- Digi-Key part number: BC1252CT-ND

- Digi-Key part number: BC1252TR-ND

Figure 4-38 • Decoupling Scheme for One PLL (should be replicated for each PLL used)

FlashROM in Microsemi's Low Power Flash Devices

Figure 5-12 shows the programming file generator, which enables different STAPL file generation methods. When you select **Program FlashROM** and choose the UFC file, the FlashROM Settings window appears, as shown in Figure 5-13. In this window, you can select the FlashROM page you want to program and the data value for the configured regions. This enables you to use a different page for different programming files.

*Figure 5-12* • Programming File Generator

#### Figure 5-13 • Setting FlashROM during Programming File Generation

The programming hardware and software can load the FlashROM with the appropriate STAPL file. Programming software handles the single STAPL file that contains multiple FlashROM contents for multiple devices, and programs the FlashROM in sequential order (e.g., for device serialization). This feature is supported in the programming software. After programming with the STAPL file, you can run DEVICE\_INFO to check the FlashROM content.

ProASIC3L FPGA Fabric User's Guide

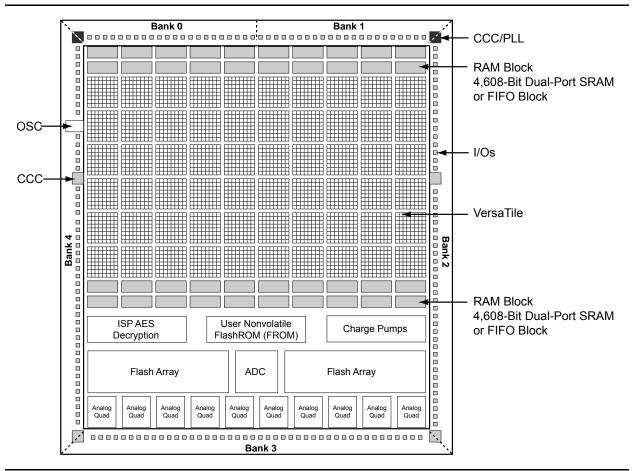

Figure 6-2 • Fusion Device Architecture Overview (AFS600)

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## Example of RAM Initialization

This section of the document presents a sample design in which a 4×4 RAM block is being initialized through the JTAG port. A test feature has been implemented in the design to read back the contents of the RAM after initialization to verify the procedure.

The interface block of this example performs two major functions: initialization of the RAM block and running a test procedure to read back the contents. The clock output of the interface is either the write clock (for initialization) or the read clock (for reading back the contents). The Verilog code for the interface block is included in the "Sample Verilog Code" section on page 167.

For simulation purposes, users can declare the input ports of the UJTAG macro for easier assignment in the testbench. However, the UJTAG input ports should not be declared on the top level during synthesis. If the input ports of the UJTAG are declared during synthesis, the synthesis tool will instantiate input buffers on these ports. The input buffers on the ports will cause Compile to fail in Designer.

Figure 6-10 shows the simulation results for the initialization step of the example design.

The CLK\_OUT signal, which is the clock output of the interface block, is the inverted DR\_UPDATE output of the UJTAG macro. It is clear that it gives sufficient time (while the TAP Controller is in the Data Register Update state) for the write address and data to become stable before loading them into the RAM block.

Figure 6-11 presents the test procedure of the example. The data read back from the memory block matches the written data, thus verifying the design functionality.

Figure 6-10 • Simulation of Initialization Step

Figure 6-11 • Simulation of the Test Procedure of the Example

# Advanced I/Os—IGLOO, ProASIC3L, and ProASIC3

Table 7-2 and Table 7-3 show the voltages and compatible I/O standards for the IGLOO, ProASIC3L, and ProASIC3 families.

I/Os provide programmable slew rates (except 30 K gate devices), drive strengths, and weak pull-up and pull-down circuits. 3.3 V PCI and 3.3 V PCI-X can be configured to be 5 V–tolerant. See the "5 V Input Tolerance" section on page 194 for possible implementations of 5 V tolerance.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section in the datasheet for more information. During power-up, before reaching activation levels, the I/O input and output buffers are disabled while the weak pull-up is enabled. Activation levels are described in the datasheet.

| IGLOO                                                                                  | AGL015 | AGL030 | AGL060 | AGL125 | AGL250             |        | AGL600             | AGL1000              |

|----------------------------------------------------------------------------------------|--------|--------|--------|--------|--------------------|--------|--------------------|----------------------|

| ProASIC3                                                                               | A3P015 | A3P030 | A3P060 | A3P125 | A3P250/<br>A3P250L | A3P400 | A3P600/<br>A3P600L | A3P1000/<br>A3P1000L |

| Single-Ended                                                                           |        |        |        |        |                    |        |                    |                      |

| LVTTL/LVCMOS 3.3 V,<br>LVCMOS 2.5 V / 1.8 V /<br>1.5 V / 1.2 V<br>LVCMOS 2.5 V / 5.0 V | 1      | 1      | 1      | 1      | ✓                  | 1      | 1                  | 1                    |

| 3.3 V PCI/PCI-X                                                                        | -      | -      | ✓      | ✓      | 1                  | 1      | 1                  | 1                    |

| Differential                                                                           |        |        |        |        |                    |        |                    | •                    |

| LVPECL, LVDS, B-LVDS,<br>M-LVDS                                                        | -      | -      | _      | -      | 1                  | 1      | 1                  | 1                    |

Table 7-2 • Supported I/O Standards

## I/O Banks and I/O Standards Compatibility

I/Os are grouped into I/O voltage banks.

Each I/O voltage bank has dedicated I/O supply and ground voltages (VMV/GNDQ for input buffers and VCCI/GND for output buffers). This isolation is necessary to minimize simultaneous switching noise from the input and output (SSI and SSO). The switching noise (ground bounce and power bounce) is generated by the output buffers and transferred into input buffer circuits, and vice versa. Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 7-3 shows the required voltage compatibility values for each of these voltages.

There are four I/O banks on the 250K gate through 1M gate devices.

There are two I/O banks on the 30K, 60K, and 125K gate devices.

I/O standards are compatible if their VCCI and VMV values are identical. VMV and GNDQ are "quiet" input power supply pins and are not used on 30K gate devices (Table 7-3).

Table 7-3 • VCCI Voltages and Compatible IGLOO and ProASIC3 Standards

| VCCI and VMV (typical) | Compatible Standards                             |  |  |  |  |

|------------------------|--------------------------------------------------|--|--|--|--|

| 3.3 V                  | LVTTL/LVCMOS 3.3, PCI 3.3, PCI-X 3.3 LVPECL      |  |  |  |  |

| 2.5 V                  | LVCMOS 2.5, LVCMOS 2.5/5.0, LVDS, B-LVDS, M-LVDS |  |  |  |  |

| 1.8 V                  | LVCMOS 1.8                                       |  |  |  |  |

| 1.5 V                  | LVCMOS 1.5                                       |  |  |  |  |

| 1.2 V                  | LVCMOS 1.2                                       |  |  |  |  |

I/O Structures in IGLOO and ProASIC3 Devices

#### *Figure 7-15* • Timing Diagram (option 2: enables skew circuit)

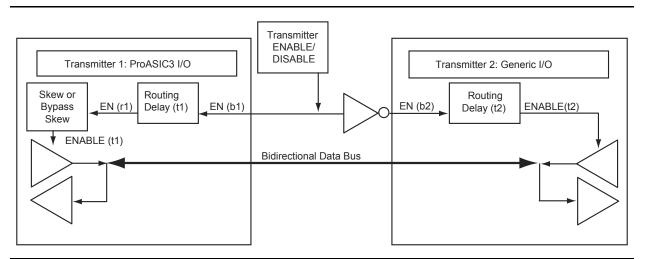

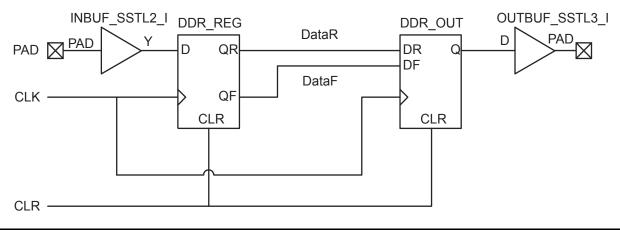

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss and/or transmitter over-stress due to transmitter-to-transmitter current shorts. Figure 7-16 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 7-17 on page 201 shows how bus contention is created, and Figure 7-18 on page 201 shows how it can be avoided with the skew circuit.

Figure 7-16 • Example of Implementation of Skew Circuits in Bidirectional Transmission Systems Using IGLOO or ProASIC3 Devices

|                    | Maximum Performance |                                                             |                                            |  |  |  |  |

|--------------------|---------------------|-------------------------------------------------------------|--------------------------------------------|--|--|--|--|

| Specification      | ProASIC3E           | IGLOOe V2 or V5<br>Devices, 1.5 V DC Core<br>Supply Voltage | IGLOOe V2, 1.2 V DC<br>Core Supply Voltage |  |  |  |  |

| LVTTL/LVCMOS 3.3 V | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |  |  |

| LVCMOS 2.5 V       | 250 MHz             | 230 MHz                                                     | TBD                                        |  |  |  |  |

| LVCMOS 1.8 V       | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |  |  |

| LVCMOS 1.5 V       | 130 MHz             | 120 MHz                                                     | TBD                                        |  |  |  |  |

| PCI                | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |  |  |

| PCI-X              | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |  |  |

| HSTL-I             | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| HSTL-II            | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| SSTL2-I            | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| SSTL2-II           | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| SSTL3-I            | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| SSTL3-II           | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| GTL+ 3.3 V         | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| GTL+ 2.5 V         | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| GTL 3.3 V          | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| GTL 2.5 V          | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |  |  |

| LVDS               | 350 MHz             | 300 MHz                                                     | TBD                                        |  |  |  |  |

| M-LVDS             | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |  |  |

| B LVDS             | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |  |  |

| LVPECL             | 350 MHz             | 300 MHz                                                     | TBD                                        |  |  |  |  |

#### Table 8-7 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected)

I/O Structures in IGLOOe and ProASIC3E Devices

compatible, which means devices can operate at conventional PCI frequencies (33 MHz and 66 MHz). PCI-X is more fault-tolerant than PCI. It also does not have programmable drive strength.

### **Voltage-Referenced Standards**

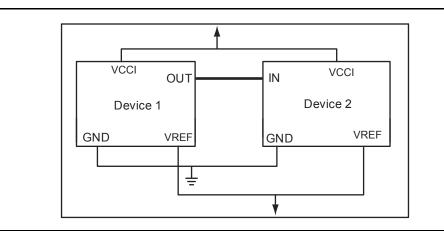

I/Os using these standards are referenced to an external reference voltage (VREF) and are supported on E devices only.

### HSTL Class I and II (High-Speed Transceiver Logic)

These are general-purpose, high-speed 1.5 V bus standards (EIA/JESD 8-6) for signaling between integrated circuits. The signaling range is 0 V to 1.5 V, and signals can be either single-ended or differential. HSTL requires a differential amplifier input buffer and a push-pull output buffer. The reference voltage (VREF) is 0.75 V. These standards are used in the memory bus interface with data switching capability of up to 400 MHz. The other advantages of these standards are low power and fewer EMI concerns.

HSTL has four classes, of which low power flash devices support Class I and II. These classes are defined by standard EIA/JESD 8-6 from the Electronic Industries Alliance (EIA):

- · Class I Unterminated or symmetrically parallel-terminated

- Class II Series-terminated

- · Class III Asymmetrically parallel-terminated

- Class IV Asymmetrically double-parallel-terminated

#### SSTL2 Class I and II (Stub Series Terminated Logic 2.5 V)

These are general-purpose 2.5 V memory bus standards (JESD 8-9) for driving transmission lines, designed specifically for driving the DDR SDRAM modules used in computer memory. SSTL2 requires a differential amplifier input buffer and a push-pull output buffer. The reference voltage (VREF) is 1.25 V.

#### SSTL3 Class I and II (Stub Series Terminated Logic 3.3 V)

These are general-purpose 3.3 V memory bus standards (JESD 8-8) for driving transmission lines. SSTL3 requires a differential amplifier input buffer and a push-pull output buffer. The reference voltage (VREF) is 1.5 V.

Figure 8-7 • SSTL and HSTL Topology

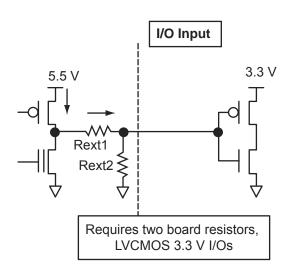

#### Solution 1

#### Figure 8-10 • Solution 1

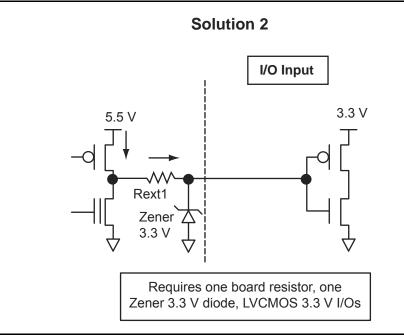

#### Solution 2

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the external resistors and Zener, as shown in Figure 8-11. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

I/O Structures in IGLOOe and ProASIC3E Devices

### 5 V Output Tolerance

IGLOO and ProASIC3 I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

## **Schmitt Trigger**

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

ProASIC3E devices have Schmitt triggers built into their I/O circuitry. The Schmitt trigger is available for the LVTTL, LVCMOS, and 3.3 V PCI I/O standards.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

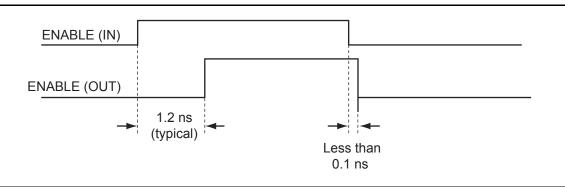

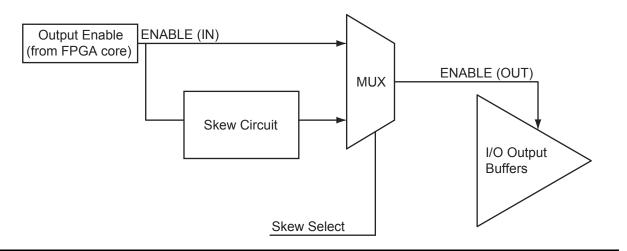

### Selectable Skew between Output Buffer Enable and Disable Times

Low power flash devices have a configurable skew block in the output buffer circuitry that can be enabled to delay output buffer assertion without affecting deassertion time. Since this skew block is only available for the OE signal, the feature can be used in tristate and bidirectional buffers. A typical 1.2 ns delay is added to the OE signal to prevent potential bus contention. Refer to the appropriate family datasheet for detailed timing diagrams and descriptions.

The Skew feature is available for all I/O standards.

This feature can be implemented by using a PDC command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

The configurable skew block is used to delay output buffer assertion (enable) without affecting deassertion (disable) time.

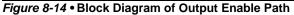

DDR for Microsemi's Low Power Flash Devices

# **Design Example**

Figure 10-9 shows a simple example of a design using both DDR input and DDR output registers. The user can copy the HDL code in Libero SoC software and go through the design flow. Figure 10-10 and Figure 10-11 on page 283 show the netlist and ChipPlanner views of the ddr\_test design. Diagrams may vary slightly for different families.

Figure 10-9 • Design Example

Figure 10-10 • DDR Test Design as Seen by NetlistViewer for IGLOO/e Devices

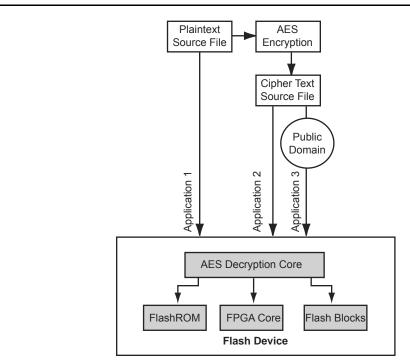

Security in Low Power Flash Devices

# **Security in Action**

This section illustrates some applications of the security advantages of Microsemi's devices (Figure 12-6).

Note: Flash blocks are only used in Fusion devices

Figure 12-6 • Security Options

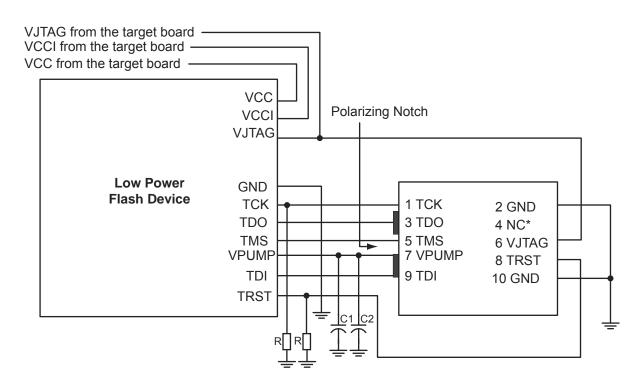

# **Board-Level Considerations**

A bypass capacitor is required from VPUMP to GND for all low power flash devices during programming. This bypass capacitor protects the devices from voltage spikes that may occur on the VPUMP supplies during the erase and programming cycles. Refer to the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for specific recommendations. For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible. The bypass capacitor must be placed within 2.5 cm of the device pins.

Note: \*NC (FlashPro3/3X); Prog\_Mode (FlashPro4). Prog\_Mode on FlashPro4 is an output signal that goes High during device programming and returns to Low when programming is complete. This signal can be used to drive a system to provide a 1.5 V programming signal to IGLOO nano, ProASIC3L, and RT ProASIC3 devices that can run with 1.2 V core voltage but require 1.5 V for programming. IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only), but IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

Figure 13-6 • Board Layout and Programming Header Top View

## Troubleshooting Signal Integrity

## Symptoms of a Signal Integrity Problem

A signal integrity problem can manifest itself in many ways. The problem may show up as extra or dropped bits during serial communication, changing the meaning of the communication. There is a normal variation of threshold voltage and frequency response between parts even from the same lot. Because of this, the effects of signal integrity may not always affect different devices on the same board in the same way. Sometimes, replacing a device appears to make signal integrity problems go away, but this is just masking the problem. Different parts on identical boards will exhibit the same problem sooner or later. It is important to fix signal integrity problems early. Unless the signal integrity problems are severe enough to completely block all communication between the device and the programmer, they may show up as subtle problems. Some of the FlashPro4/3/3X exit codes that are caused by signal integrity problems are not the only possible cause of these

Power-Up/-Down Behavior of Low Power Flash Devices

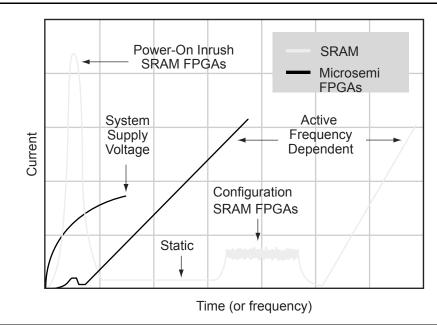

# **Transient Current on VCC**

The characterization of the transient current on VCC is performed on nearly all devices within the IGLOO, ProASIC3L, and ProASIC3 families. A sample size of five units is used from each device family member. All the device I/Os are internally pulled down while the transient current measurements are performed. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCC, when the power supply is powered at ramp-rates ranging from 15 V/ms to 0.15 V/ms, does not exceed the maximum standby current specified in the device datasheets. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCC. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCC is typically in the range of 1–5 mA.

## **Transient Current on VCCI**

The characterization of the transient current on VCCI is performed on devices within the IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, ProASIC3 nano, and ProASIC3L groups of devices, similarly to VCC transient current measurements. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCCI, when the power supply is powered at ramp-rates ranging from 33 V/ms to 0.33 V/ms, does not exceed the maximum standby current specified in the device datasheet. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCCI. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCCI is typically in the range of 1–2 mA.