Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 36864                                                          |

| Number of I/O                  | 151                                                            |

| Number of Gates                | 250000                                                         |

| Voltage - Supply               | 1.14V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                      |

| Supplier Device Package        | 208-PQFP (28x28)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p250l-pqg208i |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ProASIC3L FPGA Fabric User's Guide

|   | Device-Specific Layout                                                   | . 94 |

|---|--------------------------------------------------------------------------|------|

|   | PLL Core Specifications                                                  | 100  |

|   | Functional Description                                                   | 101  |

|   | Software Configuration                                                   | 112  |

|   | Detailed Usage Information                                               | 120  |

|   | Recommended Board-Level Considerations                                   | 128  |

|   | Conclusion                                                               | 129  |

|   | Related Documents                                                        | 129  |

|   | List of Changes                                                          | 129  |

|   |                                                                          |      |

| 5 | FlashROM in Microsemi's Low Power Flash Devices                          |      |

|   | Introduction                                                             | 133  |

|   | Architecture of User Nonvolatile FlashROM                                | 133  |

|   | FlashROM Support in Flash-Based Devices                                  | 134  |

|   | FlashROM Applications                                                    | 136  |

|   | FlashROM Security                                                        | 137  |

|   | Programming and Accessing FlashROM                                       | 138  |

|   | FlashROM Design Flow                                                     |      |

|   | Custom Serialization Using FlashROM                                      |      |

|   | Conclusion                                                               |      |

|   | Related Documents                                                        |      |

|   | List of Changes                                                          |      |

|   |                                                                          | 110  |

| 6 | SRAM and FIFO Memories in Microsemi's Low Power Flash Devices            | 147  |

|   | Introduction                                                             | 147  |

|   | Device Architecture                                                      | 147  |

|   | SRAM/FIFO Support in Flash-Based Devices                                 |      |

|   | SRAM and FIFO Architecture                                               |      |

|   | Memory Blocks and Macros                                                 |      |

|   | Initializing the RAM/FIFO                                                |      |

|   | Software Support                                                         |      |

|   |                                                                          |      |

|   | List of Changes                                                          |      |

|   |                                                                          | 175  |

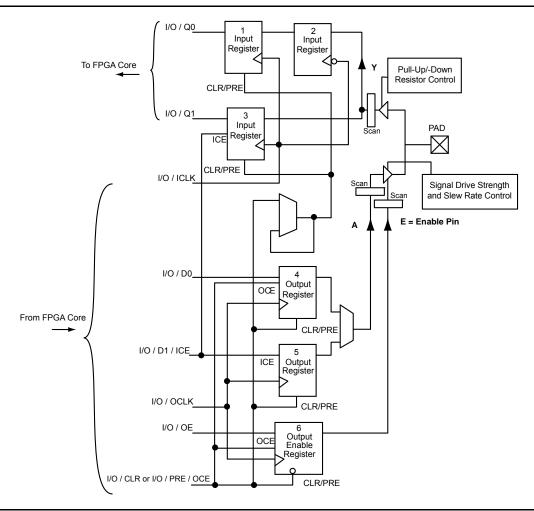

| 7 | I/O Structures in IGLOO and ProASIC3 Devices                             | 175  |

|   |                                                                          |      |

|   | Low Power Flash Device I/O Support                                       |      |

|   | Advanced I/Os—IGLOO, ProASIC3L, and ProASIC3                             |      |

|   |                                                                          |      |

|   | I/O Standards                                                            |      |

|   | I/O Features                                                             |      |

|   | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout |      |

|   | I/O Software Support                                                     |      |

|   |                                                                          |      |

|   | User I/O Naming Convention                                               |      |

|   | Board-Level Considerations                                               |      |

|   |                                                                          |      |

|   | Related Documents                                                        |      |

|   | List of Changes                                                          | 210  |

| 8 | I/O Structures in IGLOOe and ProASIC3E Devices                           | 213  |

| - |                                                                          |      |

Flash\*Freeze Technology and Low Power Modes

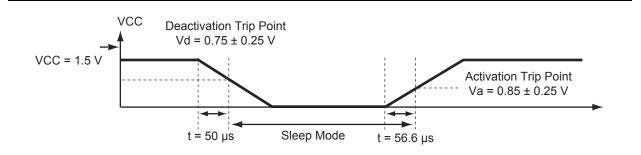

power supply and board-level configurations, the user can easily calculate how long it will take for the core to become inactive or active. For more information, refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373.

Figure 2-8 • Entering and Exiting Sleep Mode, Typical Timing Diagram

## **Context Save and Restore in Sleep or Shutdown Mode**

In Sleep mode or Shutdown mode, the contents of the SRAM, state of the I/Os, and state of the registers are lost when the device is powered off, if no other measure is taken. A low-cost external serial EEPROM can be used to save and restore the contents of the device when entering and exiting Sleep mode or Shutdown mode. In the *Embedded SRAM Initialization Using External Serial EEPROM* application note, detailed information and a reference design are provided for initializing the embedded SRAM using an external serial EEPROM. The user can easily customize the reference design to save and restore the FPGA state when entering and exiting Sleep mode or Shutdown mode. The microcontroller will need to manage this activity; hence, before powering down  $V_{CC}$ , the data will be read from the FPGA and stored externally. In a similar way, after the FPGA is powered up, the microcontroller will allow the FPGA to load the data from external memory and restore its original state.

# Flash\*Freeze Design Guide

This section describes how designers can create reliable designs that use ultra-low power Flash\*Freeze modes optimally. The section below provides guidance on how to select the best Flash\*Freeze mode for any application. The "Design Solutions" section on page 35 gives specific recommendations on how to design and configure clocks, set/reset signals, and I/Os. This section also gives an overview of the design flow and provides details concerning Microsemi's Flash\*Freeze Management IP, which enables clean clock gating and housekeeping. The "Additional Power Conservation Techniques" section on page 41 describes board-level considerations for entering and exiting Flash\*Freeze mode.

## Selecting the Right Flash\*Freeze Mode

Both Flash\*Freeze modes will bring an FPGA into an ultra-low power static mode that retains register and SRAM content and sets I/Os to a predetermined configuration. There are two primary differences that distinguish type 2 mode from type 1, and they must be considered when creating a design using Flash\*Freeze technology.

First, with type 2 mode, the device has an opportunity to wait for a second signal to enable activation of Flash\*Freeze mode. This allows processes to complete prior to deactivating the device, and can be useful to control task completion, data preservation, accidental Flash\*Freeze activation, system shutdown, or any other housekeeping function. The second signal may be derived from an external or into-out internal source. The second difference between type 1 and type 2 modes is that a design for type 2 mode has an opportunity to cleanly manage clocks and data activity before entering and exiting Flash\*Freeze mode. This is particularly important when data preservation is needed, as it ensures valid data is stored prior to entering, and upon exiting, Flash\*Freeze mode.

Type 1 Flash\*Freeze mode is ideally suited for applications with the following design criteria:

- Entering Flash\*Freeze mode is not dependent on any signal other than the external FF pin.

- Internal housekeeping is not required prior to entering Flash\*Freeze.

# **VersaNet Global Network Distribution**

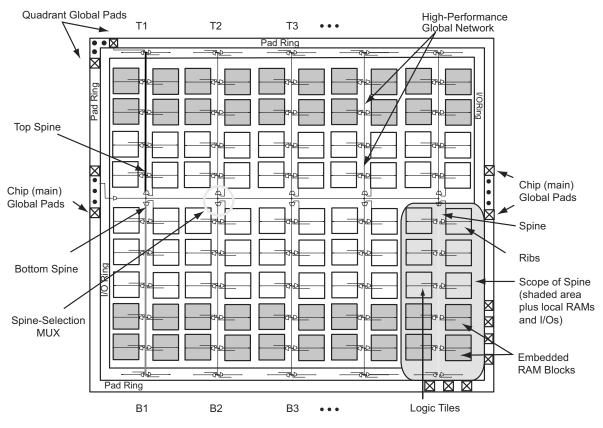

One of the architectural benefits of low power flash architecture is the set of powerful, low-delay VersaNet global networks that can access the VersaTiles, SRAM, and I/O tiles of the device. Each device offers a chip global network with six global lines (except for nano 10 k, 15 k, and 20 k gate devices) that are distributed from the center of the FPGA array. In addition, each device (except the 10 k through 30 k gate device) has four quadrant global networks, each consisting of three quadrant global net resources. These quadrant global networks can only drive a signal inside their own quadrant. Each VersaTile has access to nine global line resources—three quadrant and six chip-wide (main) global networks—and a total of 18 globals are available on the device (3 × 4 regional from each quadrant and 6 global).

Figure 3-1 shows an overview of the VersaNet global network and device architecture for devices 60 k and above. Figure 3-2 and Figure 3-3 on page 50 show simplified VersaNet global networks.

The VersaNet global networks are segmented and consist of spines, global ribs, and global multiplexers (MUXes), as shown in Figure 3-1. The global networks are driven from the global rib at the center of the die or quadrant global networks at the north or south side of the die. The global network uses the MUX trees to access the spine, and the spine uses the clock ribs to access the VersaTile. Access is available to the chip or quadrant global networks and the spines through the global MUXes. Access to the spine using the global MUXes is explained in the "Spine Architecture" section on page 57.

These VersaNet global networks offer fast, low-skew routing resources for high-fanout nets, including clock signals. In addition, these highly segmented global networks offer users the flexibility to create low-skew local clock networks using spines for up to 252 internal/external clocks or other high-fanout nets in low power flash devices. Optimal usage of these low-skew networks can result in significant improvement in design performance.

Figure 3-1 • Overview of VersaNet Global Network and Device Architecture

You can control the maximum number of shared instances allowed for the legalization to take place using the Compile Option dialog box shown in Figure 3-17. Refer to Libero SoC / Designer online help for details on the Compile Option dialog box. A large number of shared instances most likely indicates a floorplanning problem that you should address.

*Figure 3-17* • Shared Instances in the Compile Option Dialog Box

## **Designer Flow for Global Assignment**

To achieve the desired result, pay special attention to global management during synthesis and placeand-route. The current Synplify tool does not insert more than six global buffers in the netlist by default. Thus, the default flow will not assign any signal to the quadrant global network. However, you can use attributes in Synplify and increase the default global macro assignment in the netlist. Designer v6.2 supports automatic quadrant global assignment, which was not available in Designer v6.1. Layout will make the choice to assign the correct signals to global. However, you can also utilize PDC and perform manual global assignment to overwrite any automatic assignment. The following step-by-step suggestions guide you in the layout of your design and help you improve timing in Designer:

- Run Compile and check the Compile report. The Compile report has global information in the "Device Utilization" section that describes the number of chip and quadrant signals in the design. A "Net Report" section describes chip global nets, quadrant global nets, local clock nets, a list of nets listed by fanout, and net candidates for local clock assignment. Review this information. Note that YB or YC are counted as global only when they are used in isolation; if you use YB only and not GLB, this net is not shown in the global/quadrant nets report. Instead, it appears in the Global Utilization report.

- 2. If some signals have a very high fanout and are candidates for global promotion, promote those signals to global using the compile options or PDC commands. Figure 3-18 on page 70 shows the Globals Management section of the compile options. Select **Promote regular nets whose fanout is greater than** and enter a reasonable value for fanouts.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

global assignments are not allocated properly. See the "Physical Constraints for Quadrant Clocks" section for information on assigning global signals to the quadrant clock networks.

Promoted global signals will be instantiated with CLKINT macros to drive these signals onto the global network. This is automatically done by Designer when the Auto-Promotion option is selected. If the user wishes to assign the signals to the quadrant globals instead of the default chip globals, this can done by using ChipPlanner, by declaring a physical design constraint (PDC), or by importing a PDC file.

### **Physical Constraints for Quadrant Clocks**

If it is necessary to promote global clocks (CLKBUF, CLKINT, PLL, CLKDLY) to quadrant clocks, the user can define PDCs to execute the promotion. PDCs can be created using PDC commands (pre-compile) or the MultiView Navigator (MVN) interface (post-compile). The advantage of using the PDC flow over the MVN flow is that the Compile stage is able to automatically promote any regular net to a global net before assigning it to a quadrant. There are three options to place a quadrant clock using PDC commands:

- Place a clock core (not hardwired to an I/O) into a quadrant clock location.

- Place a clock core (hardwired to an I/O) into an I/O location (set\_io) or an I/O module location (set\_location) that drives a quadrant clock location.

- Assign a net driven by a regular net or a clock net to a quadrant clock using the following command:

assign\_local\_clock -net <net name> -type quadrant <quadrant clock region>

where

<net name> is the name of the net assigned to the local user clock region.

<quadrant clock region> defines which quadrant the net should be assigned to. Quadrant clock regions are defined as UL (upper left), UR (upper right), LL (lower left), and LR (lower right).

Note: If the net is a regular net, the software inserts a CLKINT buffer on the net.

#### For example:

assign\_local\_clock -net localReset -type quadrant UR

Keep in mind the following when placing quadrant clocks using MultiView Navigator:

#### Hardwired I/O–Driven CCCs

• Find the associated clock input port under the Ports tab, and place the input port at one of the Gmn\* locations using PinEditor or I/O Attribute Editor, as shown in Figure 4-32.

Figure 4-32 • Port Assignment for a CCC with Hardwired I/O Clock Input

FlashROM in Microsemi's Low Power Flash Devices

# FlashROM Support in Flash-Based Devices

The flash FPGAs listed in Table 5-1 support the FlashROM feature and the functions described in this document.

### Table 5-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

ProASIC3L FPGA Fabric User's Guide

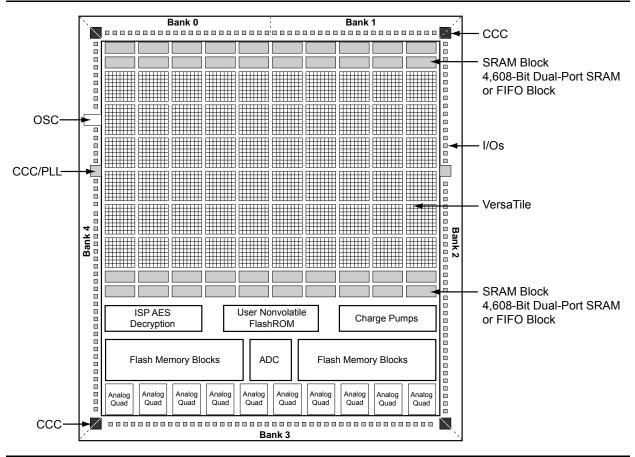

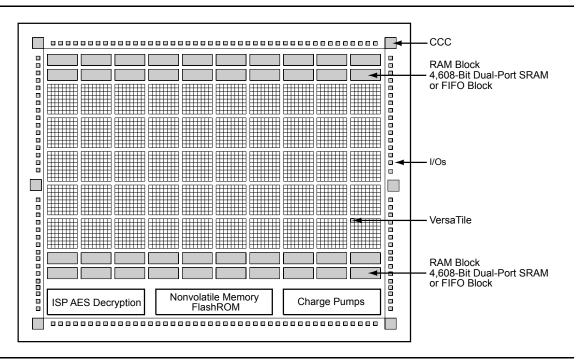

*Figure 5-2* • Fusion Device Architecture Overview (AFS600)

Figure 5-3 • ProASIC3 and IGLOO Device Architecture

## FlashROM Generation and Instantiation in the Design

The SmartGen core generator, available in Libero SoC and Designer, is the only tool that can be used to generate the FlashROM content. SmartGen has several user-friendly features to help generate the FlashROM contents. Instead of selecting each byte and assigning values, you can create a region within a page, modify the region, and assign properties to that region. The FlashROM user interface, shown in Figure 5-10, includes the configuration grid, existing regions list, and properties field. The properties field specifies the region-specific information and defines the data used for that region. You can assign values to the following properties:

- Static Fixed Data—Enables you to fix the data so it cannot be changed during programming time. This option is useful when you have fixed data stored in this region, which is required for the operation of the design in the FPGA. Key storage is one example.

- 2. Static Modifiable Data—Select this option when the data in a particular region is expected to be static data (such as a version number, which remains the same for a long duration but could conceivably change in the future). This option enables you to avoid changing the value every time you enter new data.

- 3. Read from File—This provides the full flexibility of FlashROM usage to the customer. If you have a customized algorithm for generating the FlashROM data, you can specify this setting. You can then generate a text file with data for as many devices as you wish to program, and load that into the FlashPoint programming file generation software to get programming files that include all the data. SmartGen will optionally pass the location of the file where the data is stored if the file is specified in SmartGen. Each text file has only one type of data format (binary, decimal, hex, or ASCII text). The length of each data file must be shorter than or equal to the selected region length. If the data is shorter than the selected region length, the most significant bits will be padded with 0s. For multiple text files for multiple regions, the first lines are for the first device. In SmartGen, Load Sim. Value From File allows you to load the first device data in the MEM file for simulation.

- 4. Auto Increment/Decrement—This scenario is useful when you specify the contents of FlashROM for a large number of devices in a series. You can specify the step value for the serial number and a maximum value for inventory control. During programming file generation, the actual number of devices to be programmed is specified and a start value is fed to the software.

Figure 5-10 • SmartGen GUI of the FlashROM

I/O Structures in IGLOO and ProASIC3 Devices

## I/O Banks

Advanced I/Os are divided into multiple technology banks. Each device has two to four banks, and the number of banks is device-dependent as described above. The bank types have different characteristics, such as drive strength, the I/O standards supported, and timing and power differences.

There are three types of banks: Advanced I/O banks, Standard Plus I/O banks, and Standard I/O banks.

Advanced I/O banks offer single-ended and differential capabilities. These banks are available on the east and west sides of 250K, 400K, 600K, and 1M gate devices.

Standard Plus I/O banks offer LVTTL/LVCMOS and PCI single-ended I/O standards. These banks are available on the north and south sides of 250K, 400K, 600K, and 1M gate devices as well as all sides of 125K and 60K devices.

Standard I/O banks offer LVTTL/LVCMOS single-ended I/O standards. These banks are available on all sides of 30K gate devices.

Table 7-4 shows the I/O bank types, devices and bank locations supported, drive strength, slew rate control, and supported standards.

All inputs and disabled outputs are voltage-tolerant up to 3.3 V.

For more information about I/O and global assignments to I/O banks in a device, refer to the specific pin table for the device in the packaging section of the datasheet and the "User I/O Naming Convention" section on page 206.

|               |                                                           |                                 | I/O S            | Standards Su     | upported                              |

|---------------|-----------------------------------------------------------|---------------------------------|------------------|------------------|---------------------------------------|

| I/O Bank Type | Device and Bank<br>Location                               | Drive Strength                  | LVTTL/<br>LVCMOS | PCI/PCI-X        | LVPECL,<br>LVDS,<br>B-LVDS,<br>M-LVDS |

| Standard      | 30 k gate devices (all banks)                             | Refer to Table 7-14 on page 203 | 1                | Not<br>Supported | Not Supported                         |

| Standard Plus | 60 k and 125 k gate devices (all banks)                   | Refer to Table 7-15 on page 203 | 1                | 1                | Not Supported                         |

|               | North and south banks<br>of 250 k and 1 M gate<br>devices |                                 | ~                | 1                | Not Supported                         |

| Advanced      | East and west banks of 250 k and 1 M gate devices         |                                 | ~                | ~                | 1                                     |

| Table 7-4 • IGLOO and ProASIC3 Bank Type Definitions and Difference | es |

|---------------------------------------------------------------------|----|

|---------------------------------------------------------------------|----|

# 8 – I/O Structures in IGLOOe and ProASIC3E Devices

# Introduction

Low power flash devices feature a flexible I/O structure, supporting a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank-selectable voltages. IGLOO<sup>®</sup>e, ProASIC<sup>®</sup>3EL, and ProASIC3E families support Pro I/Os.

Users designing I/O solutions are faced with a number of implementation decisions and configuration choices that can directly impact the efficiency and effectiveness of their final design. The flexible I/O structure, supporting a wide variety of voltages and I/O standards, enables users to meet the growing challenges of their many diverse applications. The Libero SoC software provides an easy way to implement I/O that will result in robust I/O design.

This document first describes the two different I/O types in terms of the standards and features they support. It then explains the individual features and how to implement them in Libero SoC.

Figure 8-1 • DDR Configured I/O Block Logical Representation

ProASIC3L FPGA Fabric User's Guide

#### Table 8-3 • VCCI Voltages and Compatible IGLOOe and ProASIC3E Standards

| VCCI and VMV (typical) | Compatible Standards                                                                                         |

|------------------------|--------------------------------------------------------------------------------------------------------------|

| 3.3 V                  | LVTTL/LVCMOS 3.3, PCI 3.3, SSTL3 (Class I and II), GTL+ 3.3, GTL 3.3, LVPECL                                 |

| 2.5 V                  | LVCMOS 2.5, LVCMOS 2.5/5.0, SSTL2 (Class I and II), GTL+ 2.5, GTL 2.5, LVDS,<br>DDR LVDS, B-LVDS, and M-LVDS |

| 1.8 V                  | LVCMOS 1.8                                                                                                   |

| 1.5 V                  | LVCMOS 1.5, HSTL (Class I and II)                                                                            |

| 1.2 V                  | LVCMOS 1.2                                                                                                   |

| VREF (typical) | Compatible Standards   |  |

|----------------|------------------------|--|

| 1.5 V          | SSTL3 (Class I and II) |  |

| 1.25 V         | SSTL2 (Class I and II) |  |

| 1.0 V          | GTL+ 2.5, GTL+ 3.3     |  |

| 0.8 V          | GTL 2.5, GTL 3.3       |  |

| 0.75 V         | HSTL (Class I and II)  |  |

#### Table 8-5 • Legal IGLOOe and ProASIC3E I/O Usage Matrix within the Same Bank

| I/O Bank Voltage (typical) | Minibank Voltage (typical) | LVTTL/LVCMOS 3.3 V | LVCMOS 2.5 V | LVCMOS 1.8 V | LVCMOS 1.5 V | 3.3 V PCI/PCI-X | GTL+ (3.3 V) | GTL+ (2.5 V) | GTL (3.3 V) | GTL (2.5 V) | HSTL Class I and II (1.5 V) | SSTL2 Class I and II (2.5 V) | SSTL3 Class I and II (3.3 V) | LVDS, B-LVDS, and M-LVDS,<br>DDR (2.5 V ± 5%) | LVPECL (3.3 V) |

|----------------------------|----------------------------|--------------------|--------------|--------------|--------------|-----------------|--------------|--------------|-------------|-------------|-----------------------------|------------------------------|------------------------------|-----------------------------------------------|----------------|

| 3.3 V                      | -                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

|                            | 0.80 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

|                            | 1.00 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

|                            | 1.50 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

| 2.5 V                      | _                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

|                            | 0.80 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

|                            | 1.00 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

|                            | 1.25 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

| 1.8 V                      | _                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

| 1.5 V                      | _                          |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

|                            | 0.75 V                     |                    |              |              |              |                 |              |              |             |             |                             |                              |                              |                                               |                |

Note: White box: Allowable I/O standard combination Gray box: Illegal I/O standard combination

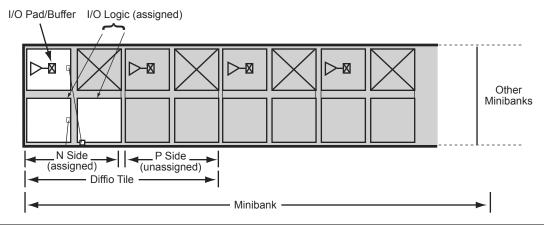

# I/O Bank Structure

Low power flash device I/Os are divided into multiple technology banks. The number of banks is device-dependent. The IGLOOe, ProASIC3EL, and ProASIC3E devices have eight banks (two per side); and IGLOO, ProASIC3L, and ProASIC3 devices have two to four banks. Each bank has its own  $V_{CCI}$  power supply pin. Multiple I/O standards can co-exist within a single I/O bank.

In IGLOOe, ProASIC3EL, and ProASIC3E devices, each I/O bank is subdivided into  $V_{REF}$  minibanks. These are used by voltage-referenced I/Os. VREF minibanks contain 8 to 18 I/Os. All I/Os in a given minibank share a common VREF line (only one VREF pin is needed per VREF minibank). Therefore, if an I/O in a VREF minibank is configured as a VREF pin, the remaining I/Os in that minibank will be able to use the voltage assigned to that pin. If the location of the VREF pin is selected manually in the software, the user must satisfy VREF rules (refer to the "I/O Software Control in Low Power Flash Devices" section on page 251). If the user does not pick the VREF pin manually, the software automatically assigns it.

Figure 8-4 is a snapshot of a section of the I/O ring, showing the basic elements of an I/O tile, as viewed from the Designer place-and-route tool's MultiView Navigator (MVN).

Figure 8-4 • Snapshot of an I/O Tile

Low power flash device I/Os are implemented using two tile types: I/O and differential I/O (diffio).

The diffio tile is built up using two I/O tiles, which form an I/O pair (P side and N side). These I/O pairs are used according to differential I/O standards. Both the P and N sides of the diffio tile include an I/O buffer and two I/O logic blocks (auxiliary and main logic).

Every minibank (E devices only) is built up from multiple diffio tiles. The number of the minibank depends on the different-size dies. Refer to the "Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E" section on page 215 for an illustration of the minibank structure.

Figure 8-5 on page 222 shows a simplified diagram of the I/O buffer circuitry. The Output Enable signal (OE) enables the output buffer to pass the signal from the core logic to the pin. The output buffer contains ESD protection circuitry, an n-channel transistor that shunts all ESD surges (up to the limit of the device ESD specification) to GND. This transistor also serves as an output pull-down resistor.

Each output buffer also contains programmable slew rate, drive strength, programmable power-up state (pull-up/-down resistor), hot-swap, 5 V tolerance, and clamp diode control circuitry. Multiple flash switches (not shown in Figure 8-5 on page 222) are programmed by user selections in the software to activate different I/O features.

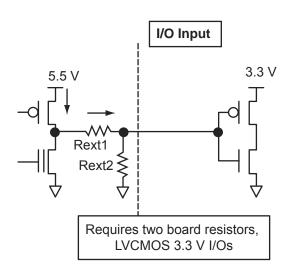

### Solution 1

#### Figure 8-10 • Solution 1

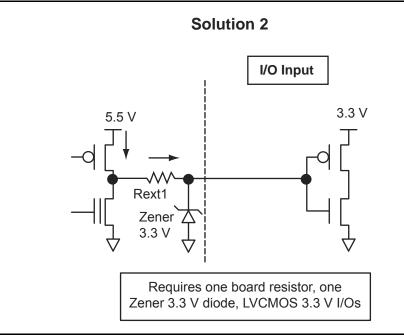

#### Solution 2

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the external resistors and Zener, as shown in Figure 8-11. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

# Software-Controlled I/O Attributes

Users may modify these programmable I/O attributes using the I/O Attribute Editor. Modifying an I/O attribute may result in a change of state in Designer. Table 9-2 details which steps have to be re-run as a function of modified I/O attribute.

|                           | Designer States <sup>1</sup> |        |      |        |       |  |  |  |  |

|---------------------------|------------------------------|--------|------|--------|-------|--|--|--|--|

| I/O Attribute             | Compile                      | Layout | Fuse | Timing | Power |  |  |  |  |

| Slew Control <sup>2</sup> | No                           | No     | Yes  | Yes    | Yes   |  |  |  |  |

| Output Drive (mA)         | No                           | No     | Yes  | Yes    | Yes   |  |  |  |  |

| Skew Control              | No                           | No     | Yes  | Yes    | Yes   |  |  |  |  |

| Resistor Pull             | No                           | No     | Yes  | Yes    | Yes   |  |  |  |  |

| Input Delay               | No                           | No     | Yes  | Yes    | Yes   |  |  |  |  |

| Schmitt Trigger           | No                           | No     | Yes  | Yes    | Yes   |  |  |  |  |

| OUT_LOAD                  | No                           | No     | No   | Yes    | Yes   |  |  |  |  |

| COMBINE_REGISTER          | Yes                          | Yes    | N/A  | N/A    | N/A   |  |  |  |  |

Table 9-2 • Designer State (resulting from I/O attribute modification)

Notes:

1. No = Remains the same, Yes = Re-run the step, N/A = Not applicable

2. Skew control does not apply to IGLOO nano, IGLOO PLUS, and ProASIC3 nano devices.

3. Programmable input delay is applicable only for ProASIC3E, ProASIC3EL, RT ProASIC3, and IGLOOe devices.

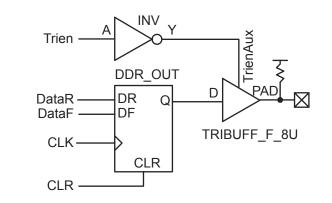

## **DDR Tristate Output Register**

#### Figure 10-7 • DDR Tristate Output Register, LOW Enable, 8 mA, Pull-Up (LVTTL)

#### Verilog

module DDR\_TriStateBuf\_LVTTL\_8mA\_HighSlew\_LowEnb\_PullUp(DataR, DataF, CLR, CLK, Trien, PAD);

input DataR, DataF, CLR, CLK, Trien; output PAD;

wire TrienAux, Q;

```

INV Inv_Tri(.A(Trien),.Y(TrienAux));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

TRIBUFF_F_8U TRIBUFF_F_8U_0_inst(.D(Q),.E(TrienAux),.PAD(PAD));

```

endmodule

### VHDL

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

```

```

entity DDR_TriStateBuf_LVTTL_8mA_HighSlew_LowEnb_PullUp is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; PAD : out std_logic);

end DDR_TriStateBuf_LVTTL_8mA_HighSlew_LowEnb_PullUp;

```

architecture DEF\_ARCH of DDR\_TriStateBuf\_LVTTL\_8mA\_HighSlew\_LowEnb\_PullUp is

```

component INV

port(A : in std_logic := 'U'; Y : out std_logic);

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component TRIBUFF_F_8U

port(D, E : in std_logic := 'U'; PAD : out std_logic);

end component;

signal TrienAux, Q : std_logic ;

begin

```

Inv\_Tri : INV

port map(A => Trien, Y => TrienAux);

# 11 – Programming Flash Devices

# Introduction

This document provides an overview of the various programming options available for the Microsemi flash families. The electronic version of this document includes active links to all programming resources, which are available at http://www.microsemi.com/soc/products/hardware/default.aspx. For Microsemi antifuse devices, refer to the *Programming Antifuse Devices* document.

# **Summary of Programming Support**

FlashPro4 and FlashPro3 are high-performance in-system programming (ISP) tools targeted at the latest generation of low power flash devices offered by the SmartFusion,<sup>®</sup> Fusion, IGLOO,<sup>®</sup> and ProASIC<sup>®</sup>3 families, including ARM-enabled devices. FlashPro4 and FlashPro3 offer extremely high performance through the use of USB 2.0, are high-speed compliant for full use of the 480 Mbps bandwidth, and can program ProASIC3 devices in under 30 seconds. Powered exclusively via USB, FlashPro4 and FlashPro3 provide a VPUMP voltage of 3.3 V for programming these devices.

FlashPro4 replaced FlashPro3 in 2010. FlashPro4 supports SmartFusion, Fusion, ProASIC3, and IGLOO devices as well as future generation flash devices. FlashPro4 also adds 1.2 V programming for IGLOO nano V2 devices. FlashPro4 is compatible with FlashPro3; however it adds a programming mode (PROG\_MODE) signal to the previously unused pin 4 of the JTAG connector. The PROG\_MODE goes high during programming and can be used to turn on a 1.5 V external supply for those devices that require 1.5 V for programming. If both FlashPro3 and FlashPro4 programmers are used for programming the same boards, pin 4 of the JTAG connector must not be connected to anything on the board because FlashPro4 uses pin 4 for PROG\_MODE.

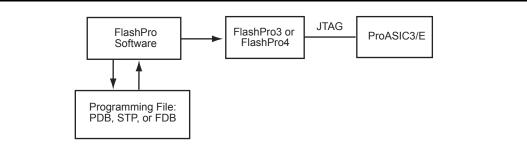

Figure 11-1 • FlashPro Programming Setup

Security in Low Power Flash Devices

# **Security Support in Flash-Based Devices**

The flash FPGAs listed in Table 12-1 support the security feature and the functions described in this document.

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                          |

|----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                    |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                           |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                              |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                             |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                          |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                 |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM Cortex™-M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 12-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 12-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

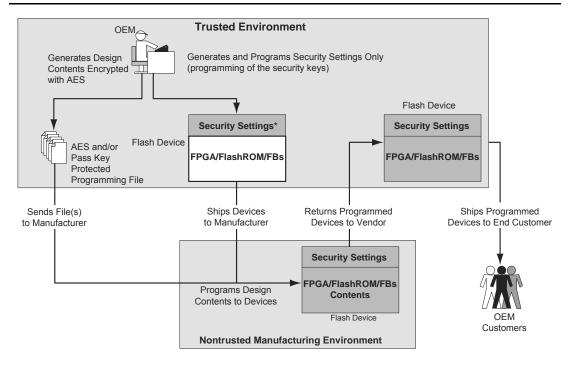

## Application 1: Trusted Environment

As illustrated in Figure 12-7, this application allows the programming of devices at design locations where research and development take place. Therefore, encryption is not necessary and is optional to the user. This is often a secure way to protect the design, since the design program files are not sent elsewhere. In situations where production programming is not available at the design location, programming centers (such as Microsemi In-House Programming) provide a way of programming designs at an alternative, secure, and trusted location. In this scenario, the user generates a STAPL programming file from the Designer software in plaintext format, containing information on the entire design or the portion of the design. Once the design is programmed to unprogrammed devices, the design is protected by this FlashLock Pass Key. If no future programming is needed, the user can consider permanently securing the IGLOO and ProASIC3 device, as discussed in the "Permanent FlashLock" section on page 307.

## **Application 2: Nontrusted Environment—Unsecured Location**

Often, programming of devices is not performed in the same location as actual design implementation, to reduce manufacturing cost. Overseas programming centers and contract manufacturers are examples of this scenario.

To achieve security in this case, the AES key and the FlashLock Pass Key can be initially programmed in-house (trusted environment). This is done by generating a programming file with only the security settings and no design contents. The design FPGA core, FlashROM, and (for Fusion) FB contents are generated in a separate programming file. This programming file must be set with the same AES key that was used to program to the device previously so the device will correctly decrypt this encrypted programming file. As a result, the encrypted design content programming file can be safely sent off-site to nontrusted programming locations for design programming. Figure 12-7 shows a more detailed flow for this application.

Notes:

1. Programmed portion indicated with dark gray.

2. Programming of FBs applies to Fusion only.

Figure 12-7 • Application 2: Device Programming in a Nontrusted Environment

Power-Up/-Down Behavior of Low Power Flash Devices

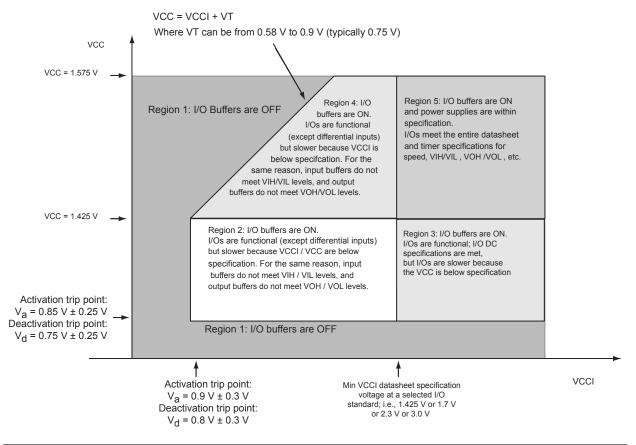

#### Figure 18-3 • I/O State when VCCI Is Powered before VCC

## **Power-Up to Functional Time**

At power-up, device I/Os exit the tristate mode and become functional once the last voltage supply in the power-up sequence (VCCI or VCC) reaches its functional activation level. The power-up–to–functional time is the time it takes for the last supply to power up from zero to its functional level. Note that the functional level of the power supply during power-up may vary slightly within the specification at different ramp-rates. Refer to Table 18-2 for the functional level of the voltage supplies at power-up.

Typical I/O behavior during power-up-to-functional time is illustrated in Figure 18-2 on page 377 and Figure 18-3.

| Device                                                                                                      | VCC Functional<br>Activation Level (V) | VCCI Functional<br>Activation Level (V) |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano,<br>IGLOO PLUS, and ProASIC3L devices running at<br>VCC = 1.5 V* | 0.85 V ± 0.25 V                        | 0.9 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and<br>ProASIC3L devices running at VCC = 1.2 V*                             | 0.85 V ± 0.2 V                         | 0.9 V ± 0.15 V                          |

#### Table 18-2 • Power-Up Functional Activation Levels for VCC and VCCI

Note: \*V5 devices will require a 1.5 V VCC supply, whereas V2 devices can utilize either a 1.2 V or 1.5 V VCC.

Microsemi's low power flash devices meet Level 0 LAPU; that is, they can be functional prior to  $V_{CC}$  reaching the regulated voltage required. This important advantage distinguishes low power flash devices from their SRAM-based counterparts. SRAM-based FPGAs, due to their volatile technology, require hundreds of milliseconds after power-up to configure the design bitstream before they become functional. Refer to Figure 18-4 on page 379 and Figure 18-5 on page 380 for more information.

Figure 18-4 • I/O State as a Function of VCCI and VCC Voltage Levels for IGLOO V5, IGLOO nano V5, IGLOO PLUS V5, ProASIC3L, and ProASIC3 Devices Running at VCC = 1.5 V ± 0.075 V