# E·XF

Welcome to E-XFL.COM

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Detai | ls |

|-------|----|

|-------|----|

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | 36864                                                         |

| Number of I/O                  | 68                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.14V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 100-TQFP                                                      |

| Supplier Device Package        | 100-VQFP (14x14)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p250l-vq100i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Microsemi

Global Resources in Low Power Flash Devices

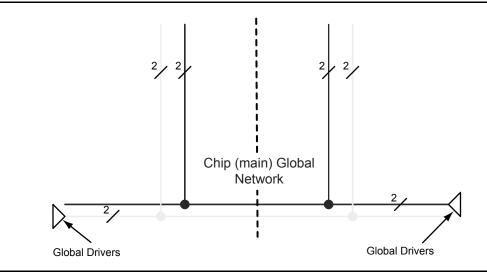

Figure 3-2 • Simplified VersaNet Global Network (30 k gates and below)

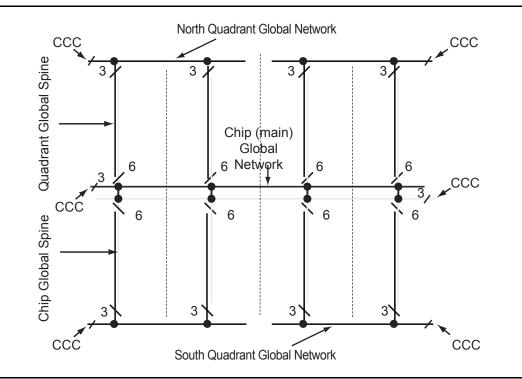

Figure 3-3 • Simplified VersaNet Global Network (60 k gates and above)

## Microsemi

Global Resources in Low Power Flash Devices

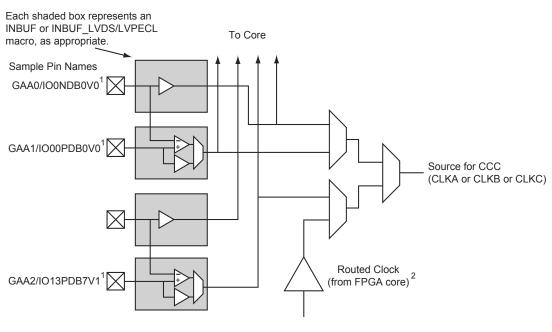

Figure 3-5 shows more detailed global input connections. It shows the global input pins connection to the northwest quadrant global networks. Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection (not supported for IGLOO nano or ProASIC3 nano devices)

- The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Figure 3-5 • Global I/O Overview

ProASIC3L FPGA Fabric User's Guide

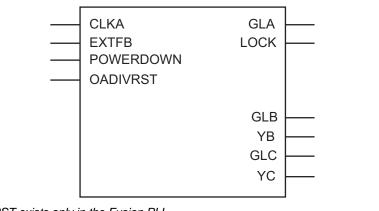

Note: OAVDIVRST exists only in the Fusion PLL.

#### Figure 3-15 • PLLs in Low Power Flash Devices

You can use the syn\_global\_buffers attribute in Synplify to specify a maximum number of global macros to be inserted in the netlist. This can also be used to restrict the number of global buffers inserted. In the Synplicity 8.1 version or newer, a new attribute, syn\_global\_minfanout, has been added for low power flash devices. This enables you to promote only the high-fanout signal to global. However, be aware that you can only have six signals assigned to chip global networks, and the rest of the global signals should be assigned to quadrant global networks. So, if the netlist has 18 global macros, the remaining 12 global macros should have fanout that allows the instances driven by these globals to be placed inside a quadrant.

### **Global Promotion and Demotion Using PDC**

The HDL source file or schematic is the preferred place for defining which signals should be assigned to a clock network using clock macro instantiation. This method is preferred because it is guaranteed to be honored by the synthesis tools and Designer software and stop any replication on this net by the synthesis tool. Note that a signal with fanout may have logic replication if it is not promoted to global during synthesis. In that case, the user cannot promote that signal to global using PDC. See Synplicity Help for details on using this attribute. To help you with global management, Designer allows you to promote a signal to a global network or demote a global macro to a regular macro from the user netlist using the compile options and/or PDC commands.

The following are the PDC constraints you can use to promote a signal to a global network:

1. PDC syntax to promote a regular net to a chip global clock:

assign\_global\_clock -net netname

The following will happen during promotion of a regular signal to a global network:

- If the net is external, the net will be driven by a CLKINT inserted automatically by Compile.

- The I/O macro will not be changed to CLKBUF macros.

- If the net is an internal net, the net will be driven by a CLKINT inserted automatically by Compile.

- 2. PDC syntax to promote a net to a quadrant clock:

assign\_local\_clock -net netname -type quadrant UR|UL|LR|LL

This follows the same rule as the chip global clock network.

The following PDC command demotes the clock nets to regular nets.

unassign\_global\_clock -net netname

DEVICE\_INFO displays the FlashROM content, serial number, Design Name, and checksum, as shown below:

```

EXPORT IDCODE[32] = 123261CF

EXPORT SILSIG[32] = 00000000

User information :

CHECKSUM: 61A0

Design Name:

TOP

Programming Method: STAPL

Algorithm Version: 1

Programmer: UNKNOWN

_____

FlashROM Information :

_____

Security Setting :

Encrypted FlashROM Programming Enabled.

Encrypted FPGA Array Programming Enabled.

_____

```

The Libero SoC file manager recognizes the UFC and MEM files and displays them in the appropriate view. Libero SoC also recognizes the multiple programming files if you choose the option to generate multiple files for multiple FlashROM contents in Designer. These features enable a user-friendly flow for the FlashROM generation and programming in Libero SoC.

## **Custom Serialization Using FlashROM**

You can use FlashROM for device serialization or inventory control by using the Auto Inc region or Read From File region. FlashPoint will automatically generate the serial number sequence for the Auto Inc region with the **Start Value**, **Max Value**, and **Step Value** provided. If you have a unique serial number generation scheme that you prefer, the Read From File region allows you to import the file with your serial number scheme programmed into the region. See the *FlashPro User's Guide* for custom serialization file format information.

The following steps describe how to perform device serialization or inventory control using FlashROM:

- 1. Generate FlashROM using SmartGen. From the Properties section in the FlashROM Settings dialog box, select the **Auto Inc** or **Read From File** region. For the Auto Inc region, specify the desired step value. You will not be able to modify this value in the FlashPoint software.

- 2. Go through the regular design flow and finish place-and-route.

- Select Programming File in Designer and open Generate Programming File (Figure 5-12 on page 144).

- 4. Click **Program FlashROM**, browse to the UFC file, and click **Next**. The FlashROM Settings window appears, as shown in Figure 5-13 on page 144.

- 5. Select the FlashROM page you want to program and the data value for the configured regions. The STAPL file generated will contain only the data that targets the selected FlashROM page.

- 6. Modify properties for the serialization.

- For the Auto Inc region, specify the **Start** and **Max** values.

- For the Read From File region, select the file name of the custom serialization file.

- 7. Select the FlashROM programming file type you want to generate from the two options below:

- Single programming file for all devices: generates one programming file with all FlashROM values.

- One programming file per device: generates a separate programming file for each FlashROM value.

- 8. Enter the number of devices you want to program and generate the required programming file.

- 9. Open the programming software and load the programming file. The programming software, FlashPro3 and Silicon Sculptor II, supports the device serialization feature. If, for some reason, the device fails to program a part during serialization, the software allows you to reuse or skip the serial data. Refer to the *FlashPro User's Guide* for details.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

#### Table 6-2 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA[1:0] | WIDTHB[1:0] | D×W   |

|-------------|-------------|-------|

| 00          | 00          | 4k×1  |

| 01          | 01          | 2k×2  |

| 10          | 10          | 1k×4  |

| 11          | 11          | 512×9 |

Note: The aspect ratio settings are constant and cannot be changed on the fly.

#### BLKA and BLKB

These signals are active-low and will enable the respective ports when asserted. When a BLKx signal is deasserted, that port's outputs hold the previous value.

## Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, BLKB should be tied to ground.

#### WENA and WENB

These signals switch the RAM between read and write modes for the respective ports. A LOW on these signals indicates a write operation, and a HIGH indicates a read.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WENB should be tied to ground.

#### **CLKA and CLKB**

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

Note: For Automotive ProASIC3 devices, dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile.

#### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A LOW on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the corresponding output in the next clock cycle.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, PIPEB should be tied to ground. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A LOW on these signals makes the output retain data from the previous read. A HIGH indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

## Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WMODEB should be tied to ground.

#### RESET

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 6-3 on page 155).

The ROM emulation application is based on RAM block initialization. If the user's main design has access only to the read ports of the RAM block (RADDR, RD, RCLK, and REN), and the contents of the RAM are already initialized through the TAP, then the memory blocks will emulate ROM functionality for the core design. In this case, the write ports of the RAM blocks are accessed only by the user interface block, and the interface is activated only by the TAP Instruction Register contents.

Users should note that the contents of the RAM blocks are lost in the absence of applied power. However, the 1 kbit of flash memory, FlashROM, in low power flash devices can be used to retain data after power is removed from the device. Refer to the "SRAM and FIFO Memories in Microsemi's Low Power Flash Devices" section on page 147 for more information.

## Sample Verilog Code

### Interface Block

```

`define Initialize_start 8'h22 //INITIALIZATION START COMMAND VALUE

`define Initialize_stop 8'h23 //INITIALIZATION START COMMAND VALUE

module interface(IR, rst_n, data_shift, clk_in, data_update, din_ser, dout_ser, test,

test_out,test_clk,clk_out,wr_en,rd_en,write_word,read_word,rd_addr, wr_addr);

input [7:0] IR;

input [3:0] read_word; //RAM DATA READ BACK

input rst_n, data_shift, clk_in, data_update, din_ser; //INITIALIZATION SIGNALS

input test, test_clk; //TEST PROCEDURE CLOCK AND COMMAND INPUT

output [3:0] test_out; //READ DATA

output [3:0] write_word; //WRITE DATA

output [1:0] rd_addr; //READ ADDRESS

output [1:0] wr_addr; //WRITE ADDRESS

output dout_ser; //TDO DRIVER

output clk_out, wr_en, rd_en;

wire [3:0] write_word;

wire [1:0] rd addr;

wire [1:0] wr_addr;

wire [3:0] Q_out;

wire enable, test_active;

reg clk out;

//SELECT CLOCK FOR INITIALIZATION OR READBACK TEST

always @(enable or test_clk or data_update)

begin

case ({test_active})

1 : clk_out = test_clk ;

0 : clk_out = !data_update;

default : clk_out = 1'b1;

endcase

end

assign test_active = test && (IR == 8'h23);

assign enable = (IR == 8'h22);

assign wr_en = !enable;

assign rd_en = !test_active;

assign test_out = read_word;

assign dout_ser = Q_out[3];

//4-bit SIN/POUT SHIFT REGISTER

shift_reg data_shift_reg (.Shiften(data_shift), .Shiftin(din_ser), .Clock(clk_in),

.Q(Q_out));

//4-bit PIPELINE REGISTER

D_pipeline pipeline_reg (.Data(Q_out), .Clock(data_update), .Q(write_word));

```

SmartGen enables the user to configure the desired RAM element to use either a single clock for read and write, or two independent clocks for read and write. The user can select the type of RAM as well as the width/depth and several other parameters (Figure 6-13).

#### Figure 6-13 • SmartGen Memory Configuration Interface

SmartGen also has a Port Mapping option that allows the user to specify the names of the ports generated in the memory block (Figure 6-14).

#### *Figure 6-14* • Port Mapping Interface for SmartGen-Generated Memory

SmartGen also configures the FIFO according to user specifications. Users can select no flags, static flags, or dynamic flags. Static flag settings are configured using configuration flash and cannot be altered

IGLOO and ProASIC3 devices support output slew rate control: high and low. Microsemi recommends the high slew rate option to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected.

### **Output Drive**

The output buffers of IGLOO and ProASIC3 devices can provide multiple drive strengths to meet signal integrity requirements. The LVTTL and LVCMOS (except 1.2 V LVCMOS) standards have selectable drive strengths. Other standards have a preset value.

Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 2.5 V, 5.0 V input, LVCMOS 1.8 V, and LVCMOS 1.5 V. All other I/O standards have a high output slew rate by default.

For 30 k gate devices, refer to Table 7-14. For other ProASIC3 and IGLOO devices, refer to Table 7-15 through Table 7-16 on page 203 for more information about the slew rate and drive strength specification. Refer to Table 7-4 on page 178 for I/O bank type definitions.

There will be a difference in timing between the Standard Plus I/O banks and the Advanced I/O banks. Refer to the I/O timing tables in the datasheet for the standards supported by each device.

Table 7-14 • IGLOO and ProASIC3 Output Drive and Slew for Standard I/O Bank Type (for 30 k gate devices)

| I/O Standards      | 2 mA | 4 mA | 6 mA | 8 mA | Slew |     |

|--------------------|------|------|------|------|------|-----|

| LVTTL/LVCMOS 3.3 V | 1    | 1    | 1    | 1    | High | Low |

| LVCMOS 2.5 V       | 1    | 1    | 1    | 1    | High | Low |

| LVCMOS 1.8 V       | 1    | 1    | -    | -    | High | Low |

| LVCMOS 1.5 V       | 1    | _    | -    | _    | High | Low |

| I/O Standards | 2 mA | 4 mA | 6 mA | 8 mA       | 12 mA    | 16 mA | Slew |     |

|---------------|------|------|------|------------|----------|-------|------|-----|

| LVTTL         | 1    | ~    | 1    | 1          | 1        | 1     | High | Low |

| LVCMOS 3.3 V  | 1    | 1    | ~    | ~          | <i>✓</i> | 1     | High | Low |

| LVCMOS 2.5 V  | 1    | ✓ *  | 1    | <b>√</b> * | 1        | -     | High | Low |

| LVCMOS 1.8 V  | 1    | ✓    | 1    | 1          | -        | -     | High | Low |

| LVCMOS 1.5 V  | ~    | ✓    | -    | _          | -        | -     | High | Low |

Table 7-15 • IGLOO and ProASIC3 Output Drive and Slew for Standard Plus I/O Bank Type

Note: \*Not available in Automotive devices.

| I/O Standards    | 2 mA | 4 mA | 6 mA | 8 mA       | 12 mA    | 16 mA | 24 mA | S    | ew  |

|------------------|------|------|------|------------|----------|-------|-------|------|-----|

| LVTTL            | 1    | ✓    | ✓    | ✓          | <i>✓</i> | ~     | 1     | High | Low |

| LVCMOS 3.3 V     | ✓    | ✓    | ✓    | ✓          | ✓        | 1     | 1     | High | Low |

| LVCMOS 2.5 V     | 1    | ✓ *  | ✓    | ✓ *        | 1        | 1     | 1     | High | Low |

| LVCMOS 2.5/5.0 V | 1    | ✓ *  | ✓    | <b>√</b> * | 1        | 1     | 1     | High | Low |

| LVCMOS 1.8 V     | 1    | ✓    | ✓    | ✓          | 1        | 1     | -     | High | Low |

| LVCMOS 1.5 V     | 1    | ✓    | ✓    | ✓          | ✓        | -     | -     | High | Low |

Note: Not available in Automotive devices.

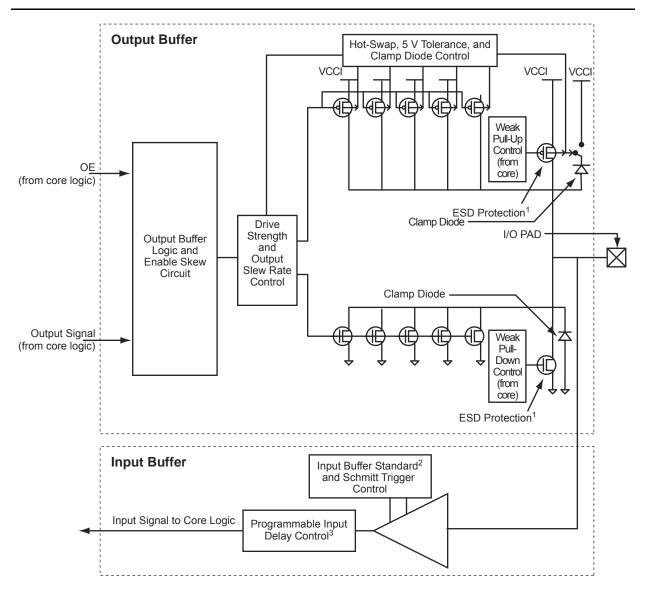

## Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E

Table 8-2 shows the voltages and compatible I/O standards for Pro I/Os. I/Os provide programmable slew rates, drive strengths, and weak pull-up and pull-down circuits. All I/O standards, except 3.3 V PCI and 3.3 V PCI-X, are capable of hot-insertion. 3.3 V PCI and 3.3 V PCI-X can be configured to be 5 V– tolerant. See the "5 V Input Tolerance" section on page 232 for possible implementations of 5 V tolerance. Single-ended input buffers support both the Schmitt trigger and programmable delay options on a per–I/O basis.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section in the datasheet for more information. During power-up, before reaching activation levels, the I/O input and output buffers are disabled while the weak pull-up is enabled. Activation levels are described in the datasheet.

#### Table 8-2 • Supported I/O Standards

|                                                                                                              | A3PE600 | AGLE600 | A3PE1500 | A3PE3000/<br>A3PE3000L | AGLE3000 |

|--------------------------------------------------------------------------------------------------------------|---------|---------|----------|------------------------|----------|

| Single-Ended                                                                                                 |         |         |          |                        |          |

| LVTTL/LVCMOS 3.3 V,<br>LVCMOS 2.5 V / 1.8 V / 1.5 V,<br>LVCMOS 2.5/5.0 V, 3.3 V PCI/PCI-X                    | 1       | ~       | 1        | 1                      | 1        |

| LVCMOS 1.2 V                                                                                                 | _       | 1       | _        | -                      | 1        |

| Differential                                                                                                 |         |         |          |                        |          |

| LVPECL, LVDS, B-LVDS, M-LVDS                                                                                 | 1       | 1       | 1        | 1                      | 1        |

| Voltage-Referenced                                                                                           |         |         |          |                        |          |

| GTL+ 2.5 V / 3.3 V, GTL 2.5 V / 3.3 V,<br>HSTL Class I and II, SSTL2 Class I and II,<br>SSTL3 Class I and II | 1       | 1       | 1        | 1                      | 1        |

I/O Structures in IGLOOe and ProASIC3E Devices

#### Notes:

- 1. All NMOS transistors connected to the I/O pad serve as ESD protection.

- 2. See Table 8-2 on page 215 for available I/O standards.

- 3. Programmable input delay is applicable only to ProASIC3E, IGLOOe, ProASIC3EL, and RT ProASIC3 devices.

Figure 8-5 • Simplified I/O Buffer Circuitry

### I/O Registers

Each I/O module contains several input, output, and enable registers. Refer to Figure 8-5 for a simplified representation of the I/O block. The number of input registers is selected by a set of switches (not shown in Figure 8-3 on page 220) between registers to implement single-ended or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user. A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input Register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy certain rules.

## Software-Controlled I/O Attributes

Users may modify these programmable I/O attributes using the I/O Attribute Editor. Modifying an I/O attribute may result in a change of state in Designer. Table 9-2 details which steps have to be re-run as a function of modified I/O attribute.

|                           | Designer States <sup>1</sup> |        |      |        |       |  |  |  |

|---------------------------|------------------------------|--------|------|--------|-------|--|--|--|

| I/O Attribute             | Compile                      | Layout | Fuse | Timing | Power |  |  |  |

| Slew Control <sup>2</sup> | No                           | No     | Yes  | Yes    | Yes   |  |  |  |

| Output Drive (mA)         | No                           | No     | Yes  | Yes    | Yes   |  |  |  |

| Skew Control              | No                           | No     | Yes  | Yes    | Yes   |  |  |  |

| Resistor Pull             | No                           | No     | Yes  | Yes    | Yes   |  |  |  |

| Input Delay               | No                           | No     | Yes  | Yes    | Yes   |  |  |  |

| Schmitt Trigger           | No                           | No     | Yes  | Yes    | Yes   |  |  |  |

| OUT_LOAD                  | No                           | No     | No   | Yes    | Yes   |  |  |  |

| COMBINE_REGISTER          | Yes                          | Yes    | N/A  | N/A    | N/A   |  |  |  |

Table 9-2 • Designer State (resulting from I/O attribute modification)

Notes:

1. No = Remains the same, Yes = Re-run the step, N/A = Not applicable

2. Skew control does not apply to IGLOO nano, IGLOO PLUS, and ProASIC3 nano devices.

3. Programmable input delay is applicable only for ProASIC3E, ProASIC3EL, RT ProASIC3, and IGLOOe devices.

I/O Software Control in Low Power Flash Devices

VREF for GTL+ 3.3 V

#### Figure 9-13 • Selecting VREF Voltage for the I/O Bank

### **Assigning VREF Pins for a Bank**

The user can use default pins for VREF. In this case, select the **Use default pins for VREFs** check box (Figure 9-13). This option guarantees full VREF coverage of the bank. The equivalent PDC command is as follows:

set\_vref\_default [bank name]

To be able to choose VREF pins, adequate VREF pins must be created to allow legal placement of the compatible voltage-referenced I/Os.

To assign VREF pins manually, the PDC command is as follows:

set\_vref -bank [bank name] [package pin numbers]

For ChipPlanner/PinEditor to show the range of a VREF pin, perform the following steps:

- 1. Assign VCCI to a bank using **MVN > Edit > I/O Bank Settings**.

- 2. Open ChipPlanner. Zoom in on an I/O package pin in that bank.

- 3. Highlight the pin and then right-click. Choose Use Pin for VREF.

## 10 – DDR for Microsemi's Low Power Flash Devices

## Introduction

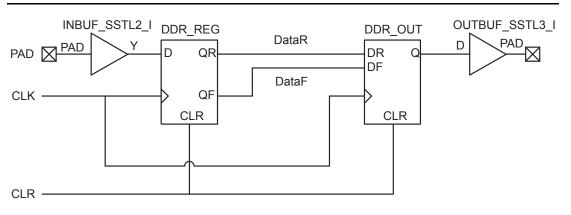

The I/Os in Fusion, IGLOO, and ProASIC3 devices support Double Data Rate (DDR) mode. In this mode, new data is present on every transition (or clock edge) of the clock signal. This mode doubles the data transfer rate compared with Single Data Rate (SDR) mode, where new data is present on one transition (or clock edge) of the clock signal. Low power flash devices have DDR circuitry built into the I/O tiles. I/Os are configured to be DDR receivers or transmitters by instantiating the appropriate special macros (examples shown in Figure 10-4 on page 276 and Figure 10-5 on page 277) and buffers (DDR\_OUT or DDR\_REG) in the RTL design. This document discusses the options the user can choose to configure the I/Os in this mode and how to instantiate them in the design.

## Double Data Rate (DDR) Architecture

Low power flash devices support 350 MHz DDR inputs and outputs. In DDR mode, new data is present on every transition of the clock signal. Clock and data lines have identical bandwidths and signal integrity requirements, making them very efficient for implementing very high-speed systems. High-speed DDR interfaces can be implemented using LVDS (not applicable for IGLOO nano and ProASIC3 nano devices). In IGLOOe, ProASIC3E, AFS600, and AFS1500 devices, DDR interfaces can also be implemented using the HSTL, SSTL, and LVPECL I/O standards. The DDR feature is primarily implemented in the FPGA core periphery and is not tied to a specific I/O technology or limited to any I/O standard.

Figure 10-1 • DDR Support in Low Power Flash Devices

## Microsemi

DDR for Microsemi's Low Power Flash Devices

```

module ddr_test(DIN, CLK, CLR, DOUT);

input DIN, CLK, CLR;

output DOUT;

Inbuf_ddr Inbuf_ddr (.PAD(DIN), .CLR(clr), .CLK(clk), .QR(qr), .QF(qf));

Outbuf_ddr Outbuf_ddr (.DataR(qr),.DataF(qf), .CLR(clr), .CLK(clk),.PAD(DOUT));

INBUF INBUF_CLR (.PAD(CLR), .Y(clr));

INBUF INBUF_CLK (.PAD(CLK), .Y(clk));

```

endmodule

### **Simulation Consideration**

Microsemi DDR simulation models use inertial delay modeling by default (versus transport delay modeling). As such, pulses that are shorter than the actual gate delays should be avoided, as they will not be seen by the simulator and may be an issue in post-routed simulations. The user must be aware of the default delay modeling and must set the correct delay model in the simulator as needed.

## Conclusion

Fusion, IGLOO, and ProASIC3 devices support a wide range of DDR applications with different I/O standards and include built-in DDR macros. The powerful capabilities provided by SmartGen and its GUI can simplify the process of including DDR macros in designs and minimize design errors. Additional considerations should be taken into account by the designer in design floorplanning and placement of I/O flip-flops to minimize datapath skew and to help improve system timing margins. Other system-related issues to consider include PLL and clock partitioning.

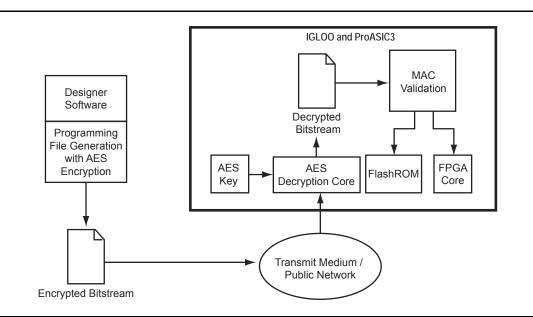

Security in Low Power Flash Devices

The AES key is securely stored on-chip in dedicated low power flash device flash memory and cannot be read out. In the first step, the AES key is generated and programmed into the device (for example, at a secure or trusted programming site). The Microsemi Designer software tool provides AES key generation capability. After the key has been programmed into the device, the device will only correctly decrypt programming files that have been encrypted with the same key. If the individual programming file content is incorrect, a Message Authentication Control (MAC) mechanism inside the device will fail in authenticating the programming file. In other words, when an encrypted programming file is being loaded into a device that has a different programmed AES key, the MAC will prevent this incorrect data from being loaded, preventing possible device damage. See Figure 12-3 on page 304 and Figure 12-4 on page 306 for graphical representations of this process.

It is important to note that the user decides what level of protection will be implemented for the device. When AES protection is desired, the FlashLock Pass Key must be set. The AES key is a content protection mechanism, whereas the FlashLock Pass Key is a device protection mechanism. When the AES key is programmed into the device, the device still needs the Pass Key to protect the FPGA and FlashROM contents and the security settings, including the AES key. Using the FlashLock Pass Key prevents modification of the design contents by means of simply programming the device with a different AES key.

### AES Decryption and MAC Authentication

Low power flash devices have a built-in 128-bit AES decryption core, which decrypts the encrypted programming file and performs a MAC check that authenticates the file prior to programming.

MAC authenticates the entire programming data stream. After AES decryption, the MAC checks the data to make sure it is valid programming data for the device. This can be done while the device is still operating. If the MAC validates the file, the device will be erased and programmed. If the MAC fails to validate, then the device will continue to operate uninterrupted.

This will ensure the following:

- · Correct decryption of the encrypted programming file

- Prevention of erroneous or corrupted data being programmed during the programming file transfer

- Correct bitstream passed to the device for decryption

Figure 12-4 • Example Application Scenario Using AES in IGLOO and ProASIC3 Devices

1. National Institute of Standards and Technology, "ADVANCED ENCRYPTION STANDARD (AES) Questions and Answers," 28 January 2002 (10 January 2005). See http://csrc.nist.gov/archive/aes/index1.html for more information.

UJTAG Applications in Microsemi's Low Power Flash Devices

## **Typical UJTAG Applications**

Bidirectional access to the JTAG port from VersaTiles—without putting the device into test mode creates flexibility to implement many different applications. This section describes a few of these. All are based on importing/exporting data through the UJTAG tiles.

## **Clock Conditioning Circuitry—Dynamic Reconfiguration**

In low power flash devices, CCCs, which include PLLs, can be configured dynamically through either an 81-bit embedded shift register or static flash programming switches. These 81 bits control all the characteristics of the CCC: routing MUX architectures, delay values, divider values, etc. Table 17-3 lists the 81 configuration bits in the CCC.

| Bit Number(s) | Control Function |

|---------------|------------------|

| 80            | RESET ENABLE     |

| 79            | DYNCSEL          |

| 78            | DYNBSEL          |

| 77            | DYNASEL          |

| <76:74>       | VCOSEL [2:0]     |

| 73            | STATCSEL         |

| 72            | STATBSEL         |

| 71            | STATASEL         |

| <70:66>       | DLYC [4:0]       |

| <65:61>       | DLYB {4:0]       |

| <60:56>       | DLYGLC [4:0]     |

| <55:51>       | DLYGLB [4:0]     |

| <50:46>       | DLYGLA [4:0]     |

| 45            | XDLYSEL          |

| <44:40>       | FBDLY [4:0]      |

| <39:38>       | FBSEL            |

| <37:35>       | OCMUX [2:0]      |

| <34:32>       | OBMUX [2:0]      |

| <31:29>       | OAMUX [2:0]      |

| <28:24>       | OCDIV [4:0]      |

| <23:19>       | OBDIV [4:0]      |

| <18:14>       | OADIV [4:0]      |

| <13:7>        | FBDIV [6:0]      |

| <6:0>         | FINDIV [6:0]     |

Table 17-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks

The embedded 81-bit shift register (for the dynamic configuration of the CCC) is accessible to the VersaTiles, which, in turn, have access to the UJTAG tiles. Therefore, the CCC configuration shift register can receive and load the new configuration data stream from JTAG.

Dynamic reconfiguration eliminates the need to reprogram the device when reconfiguration of the CCC functional blocks is needed. The CCC configuration can be modified while the device continues to operate. Employing the UJTAG core requires the user to design a module to provide the configuration data and control the CCC configuration shift register. In essence, this is a user-designed TAP Controller requiring chip resources.

Similar reconfiguration capability exists in the ProASIC<sup>PLUS®</sup> family. The only difference is the number of shift register bits controlling the CCC (27 in ProASIC<sup>PLUS</sup> and 81 in IGLOO, ProASIC3, and Fusion).

UJTAG Applications in Microsemi's Low Power Flash Devices

## Silicon Testing and Debugging

In many applications, the design needs to be tested, debugged, and verified on real silicon or in the final embedded application. To debug and test the functionality of designs, users may need to monitor some internal logic (or nets) during device operation. The approach of adding design test pins to monitor the critical internal signals has many disadvantages, such as limiting the number of user I/Os. Furthermore, adding external I/Os for test purposes may require additional or dedicated board area for testing and debugging.

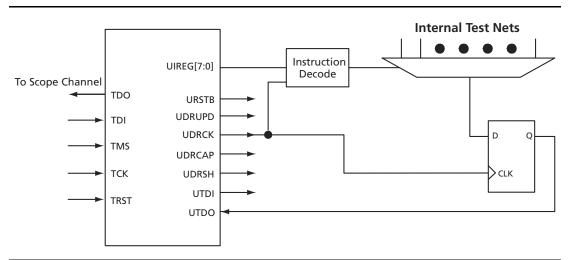

The UJTAG tiles of low power flash devices offer a flexible and cost-effective solution for silicon test and debug applications. In this solution, the signals under test are shifted out to the TDO pin of the TAP Controller. The main advantage is that all the test signals are monitored from the TDO pin; no pins or additional board-level resources are required. Figure 17-6 illustrates this technique. Multiple test nets are brought into an internal MUX architecture. The selection of the MUX is done using the contents of the TAP Controller instruction register, where individual instructions (values from 16 to 127) correspond to different signals under test. The selected test signal can be synchronized with the rising or falling edge of TCK (optional) and sent out to UTDO to drive the TDO output of JTAG.

For flash devices, TDO (the output) is configured as low slew and the highest drive strength available in the technology and/or device. Here are some examples:

- 1. If the device is A3P1000 and VCCI is 3.3 V, TDO will be configured as LVTTL 3.3 V output, 24 mA, low slew.

- If the device is AGLN020 and VCCI is 1.8 V, TDO will be configured as LVCMOS 1.8 V output, 4 mA, low slew.

- 3. If the device is AGLE300 and VCCI is 2.5 V, TDO will be configured as LVCMOS 2.5 V output, 24 mA, low slew.

The test and debug procedure is not limited to the example in Figure 17-5 on page 369. Users can customize the debug and test interface to make it appropriate for their applications. For example, multiple test signals can be registered and then sent out through UTDO, each at a different edge of TCK. In other words, *n* signals are sampled with an  $F_{TCK}$  / *n* sampling rate. The bandwidth of the information sent out to TDO is always proportional to the frequency of TCK.

Figure 17-6 • UJTAG Usage Example in Test and Debug Applications

Power-Up/-Down Behavior of Low Power Flash Devices

#### Figure 18-3 • I/O State when VCCI Is Powered before VCC

### **Power-Up to Functional Time**

At power-up, device I/Os exit the tristate mode and become functional once the last voltage supply in the power-up sequence (VCCI or VCC) reaches its functional activation level. The power-up–to–functional time is the time it takes for the last supply to power up from zero to its functional level. Note that the functional level of the power supply during power-up may vary slightly within the specification at different ramp-rates. Refer to Table 18-2 for the functional level of the voltage supplies at power-up.

Typical I/O behavior during power-up-to-functional time is illustrated in Figure 18-2 on page 377 and Figure 18-3.

| Device                                                                                                      | VCC Functional<br>Activation Level (V) | VCCI Functional<br>Activation Level (V) |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano,<br>IGLOO PLUS, and ProASIC3L devices running at<br>VCC = 1.5 V* | 0.85 V ± 0.25 V                        | 0.9 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and<br>ProASIC3L devices running at VCC = 1.2 V*                             | 0.85 V ± 0.2 V                         | 0.9 V ± 0.15 V                          |

#### Table 18-2 • Power-Up Functional Activation Levels for VCC and VCCI

Note: \*V5 devices will require a 1.5 V VCC supply, whereas V2 devices can utilize either a 1.2 V or 1.5 V VCC.

Microsemi's low power flash devices meet Level 0 LAPU; that is, they can be functional prior to  $V_{CC}$  reaching the regulated voltage required. This important advantage distinguishes low power flash devices from their SRAM-based counterparts. SRAM-based FPGAs, due to their volatile technology, require hundreds of milliseconds after power-up to configure the design bitstream before they become functional. Refer to Figure 18-4 on page 379 and Figure 18-5 on page 380 for more information.

## Microsemi

Power-Up/-Down Behavior of Low Power Flash Devices

## **Related Documents**

### Datasheets

ProASIC3 Flash Family FPGAs http://www.microsemi.com/soc/documents/PA3\_DS.pdf ProASIC3E Flash Family FPGAs http://www.microsemi.com/soc/documents/PA3E\_DS.pdf

## List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                  | Page |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.2<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to the document as supported device types.                                                                                                                                                                                               |      |

| v1.1<br>(October 2008)  | The "Introduction" section was updated to add Military ProASIC3EL and RT<br>ProASIC3 devices to the list of devices that can have inputs driven in while the<br>device is not powered.                                                                                                   | 373  |

|                         | The "Flash Devices Support Power-Up Behavior" section was revised to include new families and make the information more concise.                                                                                                                                                         | 374  |

|                         | The "Cold-Sparing" section was revised to add Military ProASIC3/EL and RT ProASIC3 devices to the lists of devices with and without cold-sparing support.                                                                                                                                | 382  |

|                         | The "Hot-Swapping" section was revised to add Military ProASIC3/EL and RT<br>ProASIC3 devices to the lists of devices with and without hot-swap support.<br>AGL400 was added to the list of devices that do not support hot-swapping.                                                    | 383  |

| v1.0<br>(August 2008)   | This document was revised, renamed, and assigned a new part number. It now includes data for the IGLOO and ProASIC3L families.                                                                                                                                                           | N/A  |

| v1.3<br>(March 2008)    | The "List of Changes" section was updated to include the three different I/O Structure handbook chapters.                                                                                                                                                                                | 384  |

| v1.2<br>(February 2008) | The first sentence of the "PLL Behavior at Brownout Condition" section was updated to read, "When PLL power supply voltage and/or V <sub>CC</sub> levels drop below the VCC brownout levels (0.75 V $\pm$ 0.25 V), the PLL output lock signal goes low and/or the output clock is lost." | 381  |

| v1.1<br>(January 2008)  | The "PLL Behavior at Brownout Condition" section was added.                                                                                                                                                                                                                              | 381  |

sleep 32 static 23 summary 23 product support customer service 387 email 387 My Cases 388 outside the U.S. 388 technical support 387 website 387 programmers 291 device support 294 programming AES encryption 319 basics 289 features 289 file header definition 323 flash and antifuse 291 flash devices 289 glossary 324 guidelines for flash programming 295 header pin numbers 336 microprocessor 349 power supplies 329 security 313 solution 334 solutions 293 voltage 329 volume services 292 programming support 287

### R

RAM memory block consumption 163 remote upgrade via TCP/IP 354 routing structure 18

### S

security 330 architecture 303 encrypted programming 354 examples 308 features 304 FlashLock 307 FlashROM 137 FlashROM use models 311 in programmable logic 301 overview 301 shutdown mode 32 context save and restore 34 signal integrity problem 337 silicon testing 370 sleep mode 32 context save and restore 34 SmartGen 170 spine architecture 57 spine assignment 68 SRAM features 153 initializing 164 software support 170 usage 157 STAPL player 351 STAPL vs. DirectC 353 static mode 23 switching circuit 344 verification 344 synthesizing 258

## Т

TAP controller state machine 357, 366 tech support ITAR 388 My Cases 388 outside the U.S. 388 technical support 387 transient current VCC 376 VCCI 376 transient current, power-up/-down 375

### U

UJTAG CCC dynamic reconfiguration 368 fine tuning 369 macro 365 operation 366 port usage 367 use to read FlashROM contents 363 ULSICC 40 ultra-fast local lines 18

### V

variable aspect ratio and cascading 161 VersaNet global networks 49 VersaTile 15 very-long-line resources 19 ViewDraw 257 VREF pins manually assigning 265

### W

web-based technical support 387