Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                    |

|--------------------------------|--------------------------------------------------------------------|

| Product Status                 | Obsolete                                                           |

| Number of LABs/CLBs            | -                                                                  |

| Number of Logic Elements/Cells |                                                                    |

| Total RAM Bits                 | 147456                                                             |

| Number of I/O                  | 154                                                                |

| Number of Gates                | 1000000                                                            |

| Voltage - Supply               | 1.14V ~ 1.575V                                                     |

| Mounting Type                  | Surface Mount                                                      |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                 |

| Package / Case                 | 208-BFQFP                                                          |

| Supplier Device Package        | 208-PQFP (28x28)                                                   |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1a3p1000l-1pqg208i |

|                                |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Microsemi

FPGA Array Architecture in Low Power Flash Devices

# **Related Documents**

## User's Guides

Designer User's Guide

http://www.microsemi.com/soc/documents/designer\_ug.pdf

# List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                                                          | Page   |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| August 2012             | The "I/O State of Newly Shipped Devices" section is new (SAR 39542).                                                                                                                                                                                                                                                             | 14     |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                        |        |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 1-1 • Flash-Based FPGAs.                                                                                                                                                                                                                                                | 10     |

|                         | Figure 1-2 • IGLOO and ProASIC3 nano Device Architecture Overview with Two I/O<br>Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices)<br>through Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device<br>Architecture Overview with Four I/O Banks (AGL600 device is shown) are new. | 11, 12 |

|                         | Table 1-4 • IGLOO nano and ProASIC3 nano Array Coordinates is new.                                                                                                                                                                                                                                                               | 17     |

| v1.3<br>(October 2008)  | The title of this document was changed from "Core Architecture of IGLOO and ProASIC3 Devices" to "FPGA Array Architecture in Low Power Flash Devices."                                                                                                                                                                           | 9      |

|                         | The "FPGA Array Architecture Support" section was revised to include new families and make the information more concise.                                                                                                                                                                                                         | 10     |

|                         | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to include Military ProASIC3/EL and RT ProASIC3 devices.                                                                                                                                                                                                            | 16     |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 1-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul>                                                                                        |        |

| v1.1<br>(March 2008)    | Table 1-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "Device Overview" section are new.                                                                                                                                                     | 10     |

|                         | The "Device Overview" section was updated to note that 15 k devices do not support SRAM or FIFO.                                                                                                                                                                                                                                 | 11     |

|                         | Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks is new.                                                                                                                                                                                                                                                 | 13     |

|                         | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to add A3P015 and AGL015.                                                                                                                                                                                                                                           | 16     |

|                         | Table 1-3 • IGLOO PLUS Array Coordinates is new.                                                                                                                                                                                                                                                                                 | 16     |

# licroser

Flash\*Freeze Technology and Low Power Modes

#### Flash\*Freeze Type 2: Control by Dedicated Flash\*Freeze Pin and Internal Logic

The device can be made to enter Flash\*Freeze mode by activating the FF pin together with Microsemi's Flash\*Freeze management IP core (refer to the "Flash\*Freeze Management IP" section on page 36 for more information) or user-defined control logic (Figure 2-3 on page 27) within the FPGA core. This method enables the design to perform important activities before allowing the device to enter Flash\*Freeze mode, such as transitioning into a safe state, completing the processing of a critical event. Designers are encouraged to take advantage of Microsemi's Flash\*Freeze Management IP to handle clean entry and exit of Flash\*Freeze mode (described later in this document). The device will only enter Flash\*Freeze mode when the Flash\*Freeze pin is asserted (active Low) and the User Low Static I<sub>CC</sub> (ULSICC) macro input signal, called the LSICC signal, is asserted (High). One condition is not sufficient to enter Flash\*Freeze mode type 2; both the FF pin and LSICC signal must be asserted.

When Flash\*Freeze type 2 is implemented in the design, the ULSICC macro needs to be instantiated by the user. There are no functional differences in the device whether the ULSICC macro is instantiated or not, and whether the LSICC signal is asserted or deasserted. The LSICC signal is used only to control entering Flash\*Freeze mode. Figure 2-4 on page 27 shows the timing diagram for entering and exiting Flash\*Freeze mode type 2.

After exiting Flash\*Freeze mode type 2 by deasserting the Flash\*Freeze pin, the LSICC signal must be deasserted by the user design. This will prevent entering Flash\*Freeze mode by asserting the Flash\*Freeze pin only.

Refer to Table 2-3 for Flash\*Freeze (FF) pin and LSICC signal assertion and deassertion values.

| Table 2-3 • | Flash*Freeze Mode Type 1 and Type 2 – Signal Assertion and Deassertion Values |                 |                   |  |

|-------------|-------------------------------------------------------------------------------|-----------------|-------------------|--|

| Signal      |                                                                               | Assertion Value | Deassertion Value |  |

| Signal                | Assertion Value | Deassertion Value |

|-----------------------|-----------------|-------------------|

| Flash*Freeze (FF) pin | Low             | High              |

| LSICC signal          | High            | Low               |

Notes:

1. The Flash\*Freeze (FF) pin is an active-Low signal, and LSICC is an active-High signal.

2. The LSICC signal is used only in Flash\*Freeze mode type 2.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### Dynamic PLL Configuration

To generate a dynamically reconfigurable CCC, the user should select Dynamic CCC in the configuration section of the SmartGen GUI (Figure 4-26). This will generate both the CCC core and the configuration shift register / control bit MUX.

Figure 4-26 • SmartGen GUI

Even if dynamic configuration is selected in SmartGen, the user must still specify the static configuration data for the CCC (Figure 4-27). The specified static configuration is used whenever the MODE signal is set to LOW and the CCC is required to function in the static mode. The static configuration data can be used as the default behavior of the CCC where required.

Figure 4-27 • Dynamic CCC Configuration in SmartGen

## Microsemi

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

without reprogramming the device. Dynamic flag settings are determined by register values and can be altered without reprogramming the device by reloading the register values either from the design or through the UJTAG interface described in the "Initializing the RAM/FIFO" section on page 164.

SmartGen can also configure the FIFO to continue counting after the FIFO is full. In this configuration, the FIFO write counter will wrap after the counter is full and continue to write data. With the FIFO configured to continue to read after the FIFO is empty, the read counter will also wrap and re-read data that was previously read. This mode can be used to continually read back repeating data patterns stored in the FIFO (Figure 6-15).

Figure 6-15 • SmartGen FIFO Configuration Interface

FIFOs configured using SmartGen can also make use of the port mapping feature to configure the names of the ports.

#### Limitations

Users should be aware of the following limitations when configuring SRAM blocks for low power flash devices:

- SmartGen does not track the target device in a family, so it cannot determine if a configured memory block will fit in the target device.

- Dual-port RAMs with different read and write aspect ratios are not supported.

- Cascaded memory blocks can only use a maximum of 64 blocks of RAM.

- The Full flag of the FIFO is sensitive to the maximum depth of the actual physical FIFO block, not the depth requested in the SmartGen interface.

This current draw can occur in the following cases:

- In Active and Static modes:

- Input buffers with pull-up, driven Low

- Input buffers with pull-down, driven High

- Bidirectional buffers with pull-up, driven Low

- Bidirectional buffers with pull-down, driven High

- Output buffers with pull-up, driven Low

- Output buffers with pull-down, driven High

- Tristate buffers with pull-up, driven Low

- Tristate buffers with pull-down, driven High

- In Flash\*Freeze mode:

- Input buffers with pull-up, driven Low

- Input buffers with pull-down, driven High

- Bidirectional buffers with pull-up, driven Low

- Bidirectional buffers with pull-down, driven High

### **Electrostatic Discharge Protection**

Low power flash devices are tested per JEDEC Standard JESD22-A114-B.

These devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

All IGLOO and ProASIC3 devices are tested to the Human Body Model (HBM) and the Charged Device Model (CDM).

Each I/O has two clamp diodes. One diode has its positive (P) side connected to the pad and its negative (N) side connected to VCCI. The second diode has its P side connected to GND and its N side connected to the pad. During operation, these diodes are normally biased in the off state, except when transient voltage is significantly above VCCI or below GND levels.

In 30 k gate devices, the first diode is always off. In other devices, the clamp diode is always on and cannot be switched off.

By selecting the appropriate I/O configuration, the diode is turned on or off. Refer to Table 8-13 for more information about the I/O standards and the clamp diode.

The second diode is always connected to the pad, regardless of the I/O configuration selected.

| I/O Assignment                          | Clamp<br>Diode | Hot<br>Insertion | 5 V Input<br>Tolerance          | Input<br>Buffer  | Output<br>Buffer |

|-----------------------------------------|----------------|------------------|---------------------------------|------------------|------------------|

| 3.3 V LVTTL/LVCMOS                      | No             | Yes              | Yes <sup>1</sup> Enabled/Disabl |                  | /Disabled        |

| 3.3 V PCI, 3.3 V PCI-X                  | Yes            | No               | Yes <sup>1</sup>                | Enabled/Disabled |                  |

| LVCMOS 2.5 V <sup>2</sup>               | No             | Yes              | No                              | Enabled/Disabled |                  |

| LVCMOS 2.5 V / 5.0 V <sup>2</sup>       | Yes            | No               | Yes <sup>3</sup>                | Enabled          | /Disabled        |

| LVCMOS 1.8 V                            | No             | Yes              | No                              | Enabled/Disabled |                  |

| LVCMOS 1.5 V                            | No             | Yes              | No                              | Enabled/Disabled |                  |

| Voltage-Referenced Input Buffer         | No             | Yes              | No                              | Enabled/Disabled |                  |

| Differential, LVDS/B-LVDS/M-LVDS/LVPECL | No             | Yes              | No                              | Enabled          | /Disabled        |

Table 8-13 • I/O Hot-Swap and 5 V Input Tolerance Capab ilities in IGLOOe and ProASIC3E Devices

Notes:

1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- In the SmartGen Core Reference Guide, select the LVCMOS5 macro for the LVCMOS 2.5 V / 5.0 V I/O standard or the LVCMOS25 macro for the LVCMOS 2.5 V I/O standard.

- 3. Can be implemented with an external resistor and an internal clamp diode.

## Microsemi.

I/O Structures in IGLOOe and ProASIC3E Devices

### 5 V Output Tolerance

IGLOO and ProASIC3 I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

### Schmitt Trigger

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

ProASIC3E devices have Schmitt triggers built into their I/O circuitry. The Schmitt trigger is available for the LVTTL, LVCMOS, and 3.3 V PCI I/O standards.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

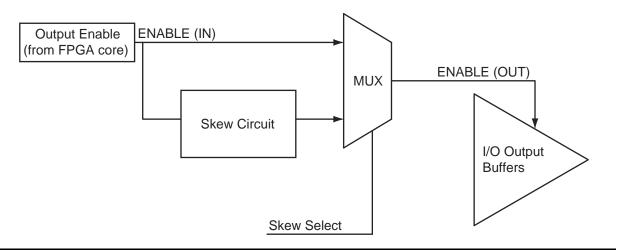

### Selectable Skew between Output Buffer Enable and Disable Times

Low power flash devices have a configurable skew block in the output buffer circuitry that can be enabled to delay output buffer assertion without affecting deassertion time. Since this skew block is only available for the OE signal, the feature can be used in tristate and bidirectional buffers. A typical 1.2 ns delay is added to the OE signal to prevent potential bus contention. Refer to the appropriate family datasheet for detailed timing diagrams and descriptions.

The Skew feature is available for all I/O standards.

This feature can be implemented by using a PDC command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

The configurable skew block is used to delay output buffer assertion (enable) without affecting deassertion (disable) time.

Programming Flash Devices

# Programming Support in Flash Devices

The flash FPGAs listed in Table 11-1 support flash in-system programming and the functions described in this document.

| Table 11-1 • | Flash-Based FPGAs |

|--------------|-------------------|

|--------------|-------------------|

| Series      | Family *                | Description                                                                                                                                                                                                                |  |

|-------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO       | IGLOO                   | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                                                          |  |

|             | IGLOOe                  | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                                                      |  |

|             | IGLOO nano              | The industry's lowest-power, smallest-size solution, supporting 1.2 V to 1.5 V core voltage with Flash*Freeze technology                                                                                                   |  |

|             | IGLOO PLUS              | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                                                 |  |

| ProASIC3    | ProASIC3                | Low power, high-performance 1.5 V FPGAs                                                                                                                                                                                    |  |

|             | ProASIC3E               | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                                                   |  |

|             | ProASIC3 nano           | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                                                        |  |

|             | ProASIC3L               | ProASIC3 FPGAs supporting 1.2 V to 1.5 V core voltage with Flash*Freeze technology                                                                                                                                         |  |

|             | RT ProASIC3             | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                                                |  |

|             | Military ProASIC3/EL    | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                                                      |  |

|             | Automotive ProASIC3     | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                                                       |  |

| SmartFusion | SmartFusion             | Mixed-signal FPGA integrating FPGA fabric, programmable microcontroller subsystem (MSS), including programmable analog and ARM <sup>®</sup> Cortex <sup>™</sup> -M3 hard processor and flash memory in a monolithic device |  |

| Fusion      | Fusion                  | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device                             |  |

| ProASIC     | ProASIC                 | First generation ProASIC devices                                                                                                                                                                                           |  |

|             | ProASIC <sup>PLUS</sup> | Second generation ProASIC devices                                                                                                                                                                                          |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 11-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 11-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the Industry's Lowest Power FPGAs Portfolio.

Security in Low Power Flash Devices

Figure 12-15 • Programming Fusion Security Settings Only

- 2. Choose the desired security level setting and enter the key(s).

- The High security level employs FlashLock Pass Key with AES Key protection.

- The Medium security level employs FlashLock Pass Key protection only.

Figure 12-16 • High Security Level to Implement FlashLock Pass Key and AES Key Protection