#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 25MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 70                                                                             |

| Program Memory Size        | 256КВ (256К х 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2318vte25iv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 6.7.4 Transition Timing

CPU cycle CPU cycle External bus released state  $T_0$ T<sub>1</sub>  $T_2$ φ High impedance Address bus Address High impedance Data bus High impedance AS High impedance RD High impedance HWR. LWR BREQ BACK BREQO\* Minimum 1 state [5] [1] [2] [3] [4] [6] [1] Low level of  $\overline{BREQ}$  pin is sampled at rise of  $T_2$  state. [2] BACK pin is driven low at end of CPU read cycle, releasing bus to external bus master. [3] BREQ pin state is still sampled in external bus released state. [4] High level of BREQ pin is sampled. [5] BACK pin is driven high, ending bus release cycle. [6] BREQO signal goes high 1.5 clocks after BACK signal goes high. Note: \* Output only when BREQOE is set to 1.

## Figure 6.19 shows the timing for transition to the bus released state.

### Figure 6.19 Bus Released State Transition Timing

## 7.1.3 Register Configuration

Table 7.1 summarizes the DTC registers.

### Table 7.1DTC Registers

| Name                             | Abbreviation | R/W | Initial Value | Address <sup>*1</sup> |

|----------------------------------|--------------|-----|---------------|-----------------------|

| DTC mode register A              | MRA          | *2  | Undefined     | *3                    |

| DTC mode register B              | MRB          | *2  | Undefined     | *3                    |

| DTC source address register      | SAR          | *2  | Undefined     | *3                    |

| DTC destination address register | DAR          | *2  | Undefined     | *3                    |

| DTC transfer count register A    | CRA          | *2  | Undefined     | *3                    |

| DTC transfer count register B    | CRB          | *2  | Undefined     | *3                    |

| DTC enable registers             | DTCER        | R/W | H'00          | H'FF30 to H'FF34      |

| DTC vector register              | DTVECR       | R/W | H'00          | H'FF37                |

| Module stop control register     | MSTPCR       | R/W | H'3FFF        | H'FF3C                |

Notes: 1. Lower 16 bits of the address.

2. Registers within the DTC cannot be read or written to directly.

Register information is located in on-chip RAM addresses H'F800 to H'FBFF. It cannot be located in external space. When the DTC is used, do not clear the RAME bit in SYSCR to 0.

#### Pin

#### Selection Method and Pin Functions

P24/TIOCA4/ TMRI1 This pin is used as the 8-bit timer counter reset pin when bits CCLR1 and CCLR0 in TCR1 are both set to 1.

The pin function is switched as shown below according to the combination of the TPU channel 4 setting by bits MD3 to MD0 in TMDR4, bits IOA3 to IOA0 in TIOR4, bits CCLR1 and CCLR0 in TCR4, and bit P24DDR.

| TPU Channel<br>4 Setting | Table Below (1) | Table B   | elow (2)   |

|--------------------------|-----------------|-----------|------------|

| P24DDR                   | _               | 0         | 1          |

| Pin function             | TIOCA4 output   | P24 input | P24 output |

|                          |                 | TIOCA4    | input *1   |

|                          | TMRI            | 1 input   |            |

| TPU Channel  | (2)     | (4)       | (2)    | (4)      | (4)         | (2)  |

|--------------|---------|-----------|--------|----------|-------------|------|

| 4 Setting    | (2)     | (1)       | (2)    | (1)      | (1)         | (2)  |

| MD3 to MD0   | B'0000, | B'01××    | B'001× | B'0010   | B'0         | 011  |

| IOA3 to IOA0 | B'0000  | B'0001 to | B'××00 | Oth      | er than B'× | ×00  |

|              | B'0100  | B'0011    |        |          |             |      |

|              | B'1×××  | B'0101 to |        |          |             |      |

|              | B'0111  |           |        |          |             |      |

| CCLR1,       | _       |           | _      |          | Other       | B'01 |

| CCLR0        |         |           |        |          | than B'01   |      |

| Output       | _       | Output    | _      | PWM      | PWM         | _    |

| function     |         | compare   |        | mode 1   | mode 2      |      |

|              |         | output    |        | output*2 | output      |      |

×: Don't care

Notes: 1. TIOCA4 input when MD3 to MD0 = B'0000 or B'01×× and IOA3 to IOA0 = B'10××.

2. TIOCB4 output is disabled.

# 8.8.4 MOS Input Pull-Up Function

Port C has a built-in MOS input pull-up function that can be controlled by software. This MOS input pull-up function can be used in modes 6 and 7, and can be specified as on or off on an individual bit basis.

When PCDDR bits are cleared to 0 in mode 6 or 7, setting the corresponding PCPCR bits to 1 turns on the MOS input pull-up for that pins.

The MOS input pull-up function is in the off state after a reset, and in hardware standby mode. The prior state is retained in software standby mode.

Table 8.14 summarizes the MOS input pull-up states.

# Table 8.14 MOS Input Pull-Up States (Port C)

| Modes | Reset | Hardware<br>Standby Mode | Software<br>Standby Mode | In Other<br>Operations |

|-------|-------|--------------------------|--------------------------|------------------------|

| 4, 5  | OFF   | OFF                      | OFF                      | OFF                    |

| 6, 7  |       |                          | ON/OFF                   | ON/OFF                 |

Legend:

OFF: MOS input pull-up is always off.

ON/OFF: On when PCDDR = 0 and PCPCR = 1; otherwise off.

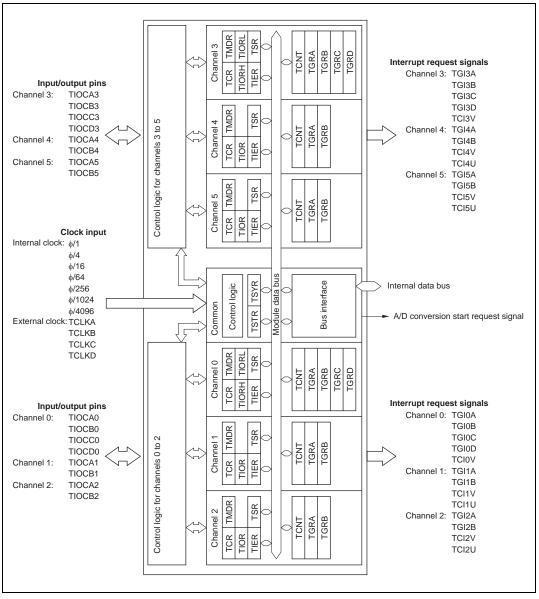

### 9.1.2 Block Diagram

Figure 9.1 shows a block diagram of the TPU.

| Channel | Bit 7<br>IOD3                              | Bit 6<br>IOD2                 | Bit 5<br>IOD1                  | Bit 4<br>IOD0 | Descripti    | on                                                  |                                                             |

|---------|--------------------------------------------|-------------------------------|--------------------------------|---------------|--------------|-----------------------------------------------------|-------------------------------------------------------------|

| 3       | 0                                          | 0                             | 0                              | 0             | TGR3D        | Output disabled                                     | (Initial value)                                             |

|         |                                            |                               |                                | 1             | is output    | Initial output is 0                                 | 0 output at compare match                                   |

|         |                                            |                               | 1                              | 0             | register*2   | output                                              | 1 output at compare match                                   |

|         |                                            |                               |                                | 1             | _            |                                                     | Toggle output at compare match                              |

|         |                                            | 1                             | 0                              | 0             | _            | Output disabled                                     |                                                             |

|         |                                            |                               |                                | 1             | _            | Initial output is 1                                 | 0 output at compare match                                   |

|         |                                            |                               | 1                              | 0             | -            | output                                              | 1 output at compare match                                   |

|         | 1<br>1 0 0 0 TCP2D Conturn input           |                               | Toggle output at compare match |               |              |                                                     |                                                             |

|         | 1                                          | 0                             | 0                              | 0             | TGR3D        | Capture input                                       | Input capture at rising edge                                |

|         | 1 is input source is<br>Capture TIOCD3 pin | Input capture at falling edge |                                |               |              |                                                     |                                                             |

|         |                                            |                               | 1                              | х             | _ register*2 | noobs pin                                           | Input capture at both edges                                 |

|         |                                            | 1                             | ×                              | ×             |              | Capture input<br>source is channel<br>4/count clock | Input capture at TCNT4<br>count-up/count-down <sup>*1</sup> |

|         |                                            |                               |                                |               |              |                                                     | ×: Don't care                                               |

- Notes: 1. When bits TPSC2 to TPSC0 in TCR4 are set to B'000 and  $\phi/1$  is used as the TCNT4 count clock, this setting is invalid and input capture is not generated.

- 2. When the BFB bit in TMDR3 is set to 1 and TGR3D is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

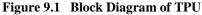

# **10.5** Sample Application

In the example below, the 8-bit timer is used to generate a pulse output with a selected duty cycle, as shown in figure 10.9. The control bits are set as follows:

- [1] In TCR, bit CCLR1 is cleared to 0 and bit CCLR0 is set to 1 so that the timer counter is cleared when its value matches the constant in TCORA.

- [2] In TCSR, bits OS3 to OS0 are set to B'0110, causing the output to change to 1 at a TCORA compare match and to 0 at a TCORB compare match.

With these settings, the 8-bit timer provides output of pulses at a rate determined by TCORA with a pulse width determined by TCORB. No software intervention is required.

Figure 10.9 Example of Pulse Output

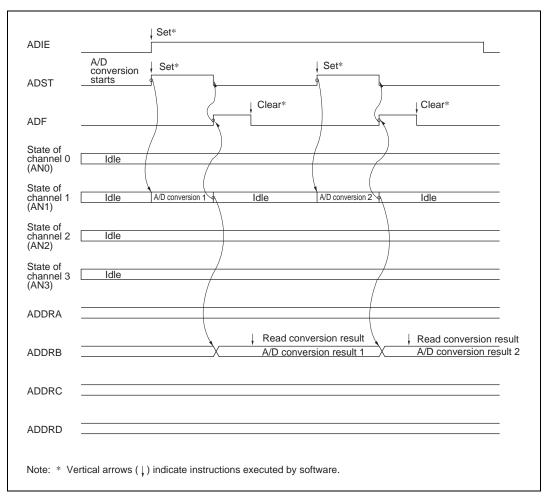

Figure 14.3 Example of A/D Converter Operation (Single Mode, Channel 1 Selected)

# 17.13 Overview of Flash Memory (H8S/2319 F-ZTAT)

## 17.13.1 Features

The H8S/2319 F-ZTAT has 512 kbytes of on-chip flash memory. The features of the flash memory are summarized below.

- Four flash memory operating modes

- Program mode

- Erase mode

- Program-verify mode

- Erase-verify mode

- Programming/erase methods

The flash memory is programmed 128 bytes at a time. Erasing is performed by block erase (in single-block units). To erase the entire flash memory, the individual blocks must be erased sequentially. Block erasing can be performed as required on 4-kbyte, 32-kbyte, and 64-kbyte blocks.

• Programming/erase times

The flash memory programming time is 10.0 ms (typ.) for simultaneous 128-byte programming, equivalent to 78  $\mu$ s (typ.) per byte, and the erase time is 50 ms (typ.).

• Reprogramming capability

The flash memory can be reprogrammed a minimum of 100 times.

• On-board programming modes

There are two modes in which flash memory can be programmed/erased/verified on-board:

- Boot mode

- User program mode

- Automatic bit rate adjustment

With data transfer in boot mode, the bit rate of the chip can be automatically adjusted to match the transfer bit rate of the host.

• Flash memory emulation by RAM

Part of the RAM area can be overlapped onto flash memory, to emulate flash memory updates in real time.

Protect modes

There are three protect modes, hardware, software, and error protect, which allow protected status to be designated for flash memory program/erase/verify operations.

### 17.28.2 PROM Mode Operation

Table 17.57 shows the settings for the operating modes of PROM mode, and table 17.58 lists the commands used in PROM mode. The following sections provide detailed information on each mode.

- Memory-read mode: This mode supports reading, in units of bytes, from the user MAT or user boot MAT.

- Auto-program mode: This mode supports the simultaneous programming of the user MAT and user boot MAT in 128-byte units. Status polling is used to confirm the end of automatic programming.

- Auto-erase mode: This mode only supports the automatic erasing of the entire user MAT or user boot MAT. Status polling is used to confirm the end of automatic erasing.

- Status-read mode: Status polling is used with automatic programming and automatic erasure. Normal completion can be detected by reading the signal on the I/O<sub>6</sub> pin. In status-read mode, error information is output when an error has occurred.

|                            |    |    | Pin Na | me          |                   |

|----------------------------|----|----|--------|-------------|-------------------|

| Mode                       | CE | ŌĒ | WE     | I/O7 to 0   | A18 to 0          |

| Read                       | L  | L  | Н      | Data output | Ain               |

| Output disable             | L  | Н  | Н      | Hi-Z        | Х                 |

| Command write              | L  | Н  | L      | Data input  | Ain <sup>*2</sup> |

| Chip disable <sup>*1</sup> | Н  | Х  | Х      | Hi-Z        | Х                 |

#### Table 17.57 Settings for Each Operating Mode of PROM Mode

Notes: 1. The chip-disable mode is not a standby state; internally, it is an operational state.

2. Ain indicates that there is also an address input in auto-program mode.

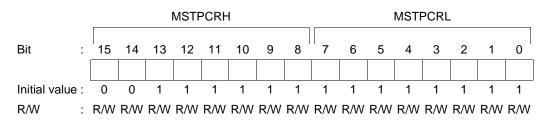

### 19.2.3 Module Stop Control Register (MSTPCR)

MSTPCR is a 16-bit readable/writable register that performs module stop mode control.

MSTPCR is initialized to H'3FFF by a reset and in hardware standby mode. It is not initialized in software standby mode.

Bits 15 to 0—Module Stop (MSTP 15 to MSTP 0): These bits specify module stop mode. See table 19.3 for the method of selecting on-chip supporting modules.

| Bits 15 to 0<br>MSTP15 to MSTP0 | Description              |

|---------------------------------|--------------------------|

| 0                               | Module stop mode cleared |

| 1                               | Module stop mode set     |

# **19.3** Medium-Speed Mode

When the SCK2 to SCK0 bits in SCKCR are set to 1, the operating mode changes to mediumspeed mode as soon as the current bus cycle ends. In medium-speed mode, the CPU operates on the operating clock ( $\phi/2$ ,  $\phi/4$ ,  $\phi/8$ ,  $\phi/16$ , or  $\phi/32$ ) specified by the SCK2 to SCK0 bits. The bus masters other than the CPU (the DTC) also operate in medium-speed mode. On-chip supporting modules other than the bus masters always operate on the high-speed clock ( $\phi$ ).

In medium-speed mode, a bus access is executed in the specified number of states with respect to the bus master operating clock. For example, if  $\phi/4$  is selected as the operating clock, on-chip memory is accessed in 4 states, and internal I/O registers in 8 states.

Medium-speed mode is cleared by clearing all of bits SCK2 to SCK0 to 0. A transition is made to high-speed mode and medium-speed mode is cleared at the end of the current bus cycle.

If a SLEEP instruction is executed when the SSBY bit in SBYCR is cleared to 0, a transition is made to sleep mode. When sleep mode is cleared by an interrupt, medium-speed mode is restored.

# **19.5** Module Stop Mode

# 19.5.1 Module Stop Mode

Module stop mode can be set for individual on-chip supporting modules.

When the corresponding MSTP bit in MSTPCR is set to 1, module operation stops at the end of the bus cycle and a transition is made to module stop mode. The CPU continues operating independently.

Table 19.3 shows MSTP bits and the corresponding on-chip supporting modules.

When the corresponding MSTP bit is cleared to 0, module stop mode is cleared and the module starts operating at the end of the bus cycle. In module stop mode, the internal states of modules other than the SCI and A/D converter are retained.

After reset clearance, all modules other than DTC are in module stop mode.

When an on-chip supporting module is in module stop mode, read/write access to its registers is disabled.

Do not make a transition to sleep mode with MSTPCR set to H'FFFF or H'EFFF, as this will halt operation of the bus controller.

|       |                  |            | Inst      | Adc      | Addressing Mode/<br>Instruction Length (Bytes) | sing<br>-enc   | Moc<br>Tthe | le/<br>Byte    | (se |                                         |    |                   |                                               |                   |                   |                 |

|-------|------------------|------------|-----------|----------|------------------------------------------------|----------------|-------------|----------------|-----|-----------------------------------------|----|-------------------|-----------------------------------------------|-------------------|-------------------|-----------------|

|       |                  | eziS busie |           | цЯ       | (n93,t                                         | -<br>EKu\@EKu+ | 1'bC)       | )99<br>(0. 1/1 |     |                                         | ပိ | Condition Code    | tion                                          | ပိ                | de                | No. of States*1 |

|       | Mnemonic         |            | ua<br>xx# | @E<br>עצ |                                                |                | 0)@<br>100  |                | -   | Operation                               | -  | Т                 | N<br>Z                                        | >                 | U<br>V            | Advanced        |

| SUB   | SUB.W Rs,Rd      | 3          | 2         |          |                                                |                |             |                |     | Rd16-Rs16→Rd16                          |    | <u>ج</u>          | $\leftrightarrow \\ \leftrightarrow$          | $\leftrightarrow$ | $\leftrightarrow$ | -               |

|       | SUB.L #xx:32,ERd | -          | 9         |          |                                                |                |             |                |     | ERd32-#xx:32→ERd32                      |    | [4]               | $\leftrightarrow \\ \leftrightarrow$          | $\leftrightarrow$ | $\leftrightarrow$ | 3               |

|       | SUB.L ERs, ERd   | _          | 7         |          |                                                |                |             |                |     | ERd32-ERs32→ERd32                       |    | [4]               | $\leftrightarrow \leftrightarrow$             | $\leftrightarrow$ | $\leftrightarrow$ | 1               |

| SUBX  | SUBX #xx:8,Rd    | 8          | 2         |          |                                                |                |             |                |     | Rd8-#xx:8-C→Rd8                         |    | $\leftrightarrow$ | $\leftrightarrow$                             | [5] ¢             | $\leftrightarrow$ | -               |

|       | SUBX Rs,Rd       | В          | 2         | 5        |                                                |                |             |                |     | Rd8-Rs8-C→Rd8                           |    | $\leftrightarrow$ | ¢ [5                                          | [5] \$            | $\leftrightarrow$ | 1               |

| SUBS  | SUBS #1,ERd      | _          | 2         |          |                                                |                |             |                |     | ERd32-1→ERd32                           |    |                   |                                               |                   |                   | 1               |

|       | SUBS #2,ERd      | _          | 2         |          |                                                |                |             |                |     | ERd32-2→ERd32                           |    |                   |                                               |                   |                   | 1               |

|       | SUBS #4,ERd      | _          | 7         |          |                                                |                |             |                |     | ERd32-4→ERd32                           |    |                   |                                               |                   |                   | 1               |

| DEC   | DEC.B Rd         | В          | 2         |          |                                                |                |             |                |     | Rd8-1→Rd8                               |    |                   | $\leftrightarrow$                             | $\leftrightarrow$ |                   | -               |

|       | DEC.W #1,Rd      | 8          | 2         | 5        |                                                |                |             |                |     | Rd16-1→Rd16                             |    |                   | $\leftrightarrow$                             | $\leftrightarrow$ |                   | -               |

|       | DEC.W #2,Rd      | >          | 2         |          |                                                |                |             |                |     | Rd16-2→Rd16                             |    |                   | $\leftrightarrow \leftrightarrow$             | $\leftrightarrow$ |                   | -               |

|       | DEC.L #1,ERd     | _          | 2         |          |                                                |                |             |                |     | ERd32-1→ERd32                           |    |                   | $\leftrightarrow \leftrightarrow$             | $\leftrightarrow$ |                   | -               |

|       | DEC.L #2,ERd     | _          | 2         | <u> </u> |                                                |                |             |                |     | ERd32-2→ERd32                           |    |                   | $\leftrightarrow \leftrightarrow \Rightarrow$ | $\leftrightarrow$ |                   | -               |

| DAS   | DAS Rd           | В          | 2         | _        |                                                |                |             |                |     | Rd8 decimal adjust→Rd8                  |    | *                 | $\leftrightarrow \leftrightarrow$             | *                 |                   | 1               |

| MULXU | MULXU.B Rs,Rd    | В          | 2         | <i>.</i> |                                                |                |             |                |     | Rd8 'Rs8→Rd16 (unsigned multiplication) |    |                   |                                               |                   |                   | 12              |

|       | MULXU.W Rs, ERd  | ≥          | 2         |          |                                                |                |             |                |     | Rd16′Rs16→ERd32                         | 1  |                   |                                               |                   |                   | 20              |

|       |                  |            |           |          |                                                |                |             |                |     | (unsigned multiplication)               |    |                   |                                               |                   |                   |                 |

| MULXS | MULXS.B Rs,Rd    | В          | 4         | 4        |                                                |                |             |                |     | Rd8 'Rs8→Rd16 (signed multiplication) – |    |                   | $\leftrightarrow \leftrightarrow \Rightarrow$ |                   |                   | - 13            |

|       | MULXS.W Rs, ERd  | ≥          | 4         |          |                                                |                |             |                |     | Rd16′Rs16→ERd32                         | Ť  |                   | $\leftrightarrow \\ \leftrightarrow$          |                   |                   | 21              |

|       |                  |            |           |          |                                                |                |             |                |     | (signed multiplication)                 |    |                   |                                               |                   |                   |                 |

| Instruc- | Mnemonic        | i.     |       |          |          |       |          |          | Instruction Format | n Format |          |          |          |           |

|----------|-----------------|--------|-------|----------|----------|-------|----------|----------|--------------------|----------|----------|----------|----------|-----------|

| tion     |                 | 21/2   | 1st k | 1st byte | 2nd byte | oyte  | 3rd byte | 4th byte | 5th byte           | 6th byte | 7th byte | 8th byte | 9th byte | 10th byte |

| ROTR     | ROTR.B Rd       | в      | ~     | 3        | 80       | p     |          |          |                    |          |          |          |          |           |

|          | ROTR.B #2, Rd   | ۵      | -     | ю        | U        | Þ     |          |          |                    |          |          |          |          |           |

|          | ROTR.W Rd       | N      | -     | 3        | 6        | rd    |          |          |                    |          |          |          |          |           |

|          | ROTR.W #2, Rd   | N      | -     | 3        | D        | rd    |          |          |                    |          |          |          |          |           |

|          | ROTR.L ERd      | _      | -     | 3        | 8        | 0 erd |          |          |                    |          |          |          |          |           |

|          | ROTR.L #2, ERd  | _      |       | 3        | <u>.</u> | 0 erd |          |          |                    |          |          |          |          |           |

| ROTXL    | ROTXL.B Rd      | в      | -     | 2        | 0        | rd    |          |          |                    |          |          |          |          |           |

|          | ROTXL.B #2, Rd  | ш      | ~     | 2        | 4        | p     |          |          |                    |          |          |          |          |           |

|          | ROTXL.W Rd      | N      | -     | 2        | -        | rd    |          |          |                    |          |          |          |          |           |

|          | ROTXL.W #2, Rd  | ≥      | ~     | 2        | 2        | p     |          |          |                    |          |          |          |          |           |

|          | ROTXL.L ERd     | _      | ٢     | 2        | 3        | 0 erd |          |          |                    |          |          |          |          |           |

|          | ROTXL.L #2, ERd | _      | -     | 2        | 7        | 0 erd |          |          |                    |          |          |          |          |           |

| ROTXR    | ROTXR.B Rd      | в      | ۲     | 3        | 0        | rd    |          |          |                    |          |          |          |          |           |

|          | ROTXR.B #2, Rd  | ш      | -     | 3        | 4        | rd    |          |          |                    |          |          |          |          |           |

|          | ROTXR.W Rd      | $^{>}$ | -     | 3        | ٦        | rd    |          |          |                    |          |          |          |          |           |

|          | ROTXR.W #2, Rd  | ≥      | -     | 3        | 5        | p     |          |          |                    |          |          |          |          |           |

|          | ROTXR.L ERd     | Γ      | 1     | 3        | 3        | 0 erd |          |          |                    |          |          |          |          |           |

|          | ROTXR.L #2, ERd | Γ      | ٢     | 3        | 7        | 0 erd |          |          |                    |          |          |          |          |           |

| RTE      | RTE             |        | 5     | 9        | 7        | 0     |          |          |                    |          |          |          |          |           |

| RTS      | RTS             |        | 5     | 4        | 7        | 0     |          |          |                    |          |          |          |          |           |

| SHAL     | SHAL.B Rd       | в      | -     | 0        | 80       | rd    |          |          |                    |          |          |          |          |           |

|          | SHAL.B #2, Rd   | в      | -     | 0        | U        | rd    |          |          |                    |          |          |          |          |           |

|          | SHAL.W Rd       | ≥      | ~     | 0        | 6        | rd    |          |          |                    |          |          |          |          |           |

|          | SHAL.W #2, Rd   | Ν      | ٢     | 0        | D        | p     |          |          |                    |          |          |          |          |           |

|          | SHAL.L ERd      | _      | -     | 0        | <u>۵</u> | 0 erd |          |          |                    |          |          |          |          |           |

|          | SHAL.L #2, ERd  | -      | -     | 0        | ш.       | 0 erd |          |          |                    |          |          |          |          |           |

## TMDR5—Timer Mode Register 5

### H'FEA1

**TPU5**

| Bit :           | 7 | 6 | 5 | 4 | 3   | 2    |   | 1  |    | 0          |              |

|-----------------|---|---|---|---|-----|------|---|----|----|------------|--------------|

|                 | _ | _ |   | _ | MD3 | MD2  |   | M  | D1 | MD0        |              |

| Initial value : | 1 | 1 | 0 | 0 | 0   | 0    |   | C  | )  | 0          |              |

| Read/Write :    |   | _ |   |   | R/W | R/W  |   | R/ | W  | R/W        |              |

|                 |   |   |   |   |     | Mode | 9 |    |    |            |              |

|                 |   |   |   |   |     | 0    | 0 | 0  | 0  | Normal ope | ration       |

|                 |   |   |   |   |     |      |   |    | 1  | Reserved   |              |

|                 |   |   |   |   |     |      |   | 1  | 0  | PWM mode   | ÷ 1          |

|                 |   |   |   |   |     |      |   |    | 1  | PWM mode   | 2            |

|                 |   |   |   |   |     |      | 1 | 0  | 0  | Phase cour | nting mode 1 |

|                 |   |   |   |   |     |      |   |    | 1  | Phase cour | nting mode 2 |

|                 |   |   |   |   |     |      |   | 1  | 0  | Phase cour | nting mode 3 |

|                 |   |   |   |   |     |      |   |    | 1  | Phase cour | nting mode 4 |

|                 |   |   |   |   |     | 1    |   |    |    | _          |              |

: Don't care

Note: MD3 is a reserved bit. In a write, it should always be written with 0.

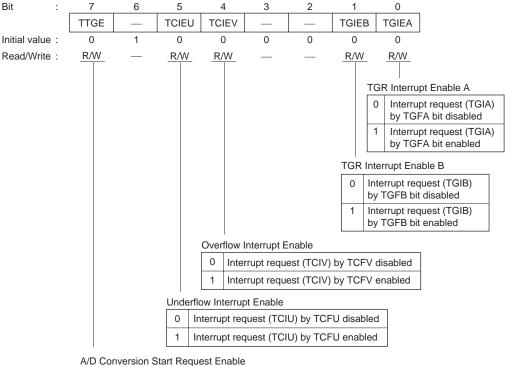

## **TIER5**—Timer Interrupt Enable Register 5

H'FEA4

| 0 | A/D conversion start request generation disabled |   |

|---|--------------------------------------------------|---|

| 1 | A/D conversion start request generation enabled  | 1 |

#### Rev.7.00 Feb. 14, 2007 page 977 of 1108 REJ09B0089-0700

1

1

0

1

1

0

1

0

1

0

1

| RAMER—RAM Emulation Register         |                                |           |   |      |          |                |                | FEDB<br>lid only   | Flash Memory<br>n F-ZTAT versions <sup>*</sup> ) |      |

|--------------------------------------|--------------------------------|-----------|---|------|----------|----------------|----------------|--------------------|--------------------------------------------------|------|

| Bit                                  | :                              | 7         | 6 | 6    | 5        | 4              | 3              | 2                  | 1                                                | 0    |

|                                      |                                | —         |   | _    | _        | —              | RAMS           | RAM2               | RAM1                                             | RAM0 |

| Initial value                        | :                              | 0         | ( | )    | 0        | 0              | 0              | 0                  | 0                                                | 0    |

| Read/Write :                         |                                | _         | _ | _    |          | _              | R/W            | R/W                | R/W                                              | R/W  |

| RAM Select, Flash Memory Area Select |                                |           |   |      |          |                |                |                    |                                                  |      |

|                                      | RAMS                           | RAM2 RAM1 |   | RAM0 | RAM Area |                |                | Block Name         |                                                  |      |

| 0 H'FFDC0                            |                                |           |   |      |          | 00 to H'FFEBFF |                | RAM area, 4 kbytes |                                                  |      |

|                                      | 1 0 0 0 H'000000 to H'000FFF E |           |   |      |          |                | EB0 (4 kbytes) |                    |                                                  |      |

H'001000 to H'001FFF

H'002000 to H'002FFF

H'003000 to H'003FFF

H'004000 to H'004FFF

H'005000 to H'005FFF

H'006000 to H'006FFF

H'007000 to H'007FFF

# Rev.7.00 Feb. 14, 2007 page 990 of 1108 REJ09B0089-0700

: Don't care

EB1 (4 kbytes)

EB2 (4 kbytes)

EB3 (4 kbytes)

EB4 (4 kbytes)

EB5 (4 kbytes)

EB6 (4 kbytes) EB7 (4 kbytes)

Note: \* In the H8S/2314 F-ZTAT, this cannot be used and must not be accessed.

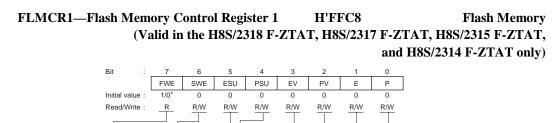

#### H'FF39

Program\* 0

0 Erase mode cleared

Transition to erase mode [Setting condition]

When FWE = 1, SWE = 1, and ESU = 1

Frase<sup>3</sup>

1

Program mode cleared Transition to program mode [Setting condition]

When FWE = 1, SWE = 1, and PSU = 1

Note: \* Valid for addresses H'000000 to H'03FFFF in H8S/2318 F-ZTAT, H'000000 to H'01FFFF in H8S/2317 F-ZTAT, and H'000000 to H'05FFFF in H8S/2315 F-ZTAT and H8S/2314 F-ZTAT.

Note: \* Valid for addresses H'000000 to H'03FFFF in H8S/2318 F-ZTAT, H'000000 to H'01FFFF in H8S/2317 F-ZTAT, and H'000000 to H'05FFFF in H8S/2315 F-ZTAT and H8S/2314 F-ZTAT.

Writes disabled Note: \* Valid for addresses H'000000 to H'03FFFF in H8S/2318 F-ZTAT. Writes enabled H'000000 to H'01FFFF in H8S/2317 F-ZTAT, and H'000000 to [Setting condition] H'05FFFF in H8S/2315 F-ZTAT and H8S/2314 F-ZTAT. When FWE = 1 Note: \* Valid for addresses H'000000 to H'03FFFF in H8S/2318 F-ZTAT.

#### H'000000 to H'01FFFF in H8S/2317 F-ZTAT, and H'000000 to H'05FFFF in H8S/2315 F-ZTAT and H8S/2314 F-ZTAT.

Flash Write Enable

0

1

When a low level is input to the FWE pin (hardware-protected state) When a high level is input to the FWE pin

Note: \* Determined by the state of the FWE pin.

0

1

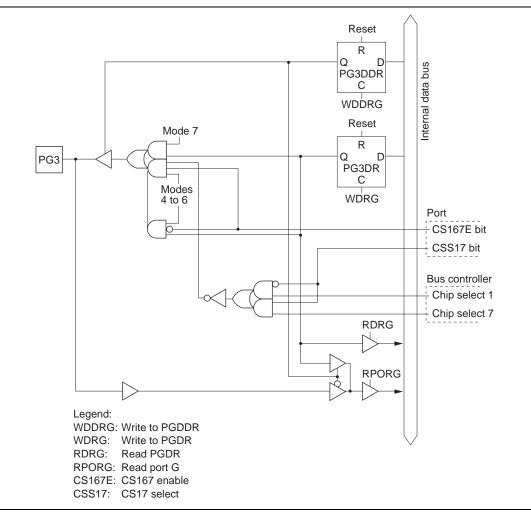

Figure C.11(d) Port G Block Diagram (Pin PG3)