#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 25MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 70                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K × 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 113-TFLGA                                                                      |

| Supplier Device Package    | 113-TFLGA (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2319cvlp25v |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item            | Page     | Revision (See Manual for Details)                                                                                                        |

|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 8.4.2 Register  | 247, 248 | Port 3 Data Direction Register (P3DDR)                                                                                                   |

| Configuration   |          | Port 3 Data Register (P3DR)                                                                                                              |

|                 |          | Port 3 Register (PORT3)                                                                                                                  |

|                 |          | Port 3 Open Drain Control Register (P3ODR)                                                                                               |

|                 |          | Description amended                                                                                                                      |

|                 |          | (Before) retains its prior state after in software standby mode. $\rightarrow$ (After) retains its prior state in software standby mode. |

| 8.6.2 Register  | 254 to   | Port A Data Direction Register (PADDR)                                                                                                   |

| Configuration   | 256      | Port A Data Register (PADR)                                                                                                              |

|                 |          | Port A Register (PORTA)                                                                                                                  |

|                 |          | Port A Open Drain Control Register (PAODR)                                                                                               |

|                 |          | Description amended                                                                                                                      |

|                 |          | (Before) retains its prior state after in software standby mode. $\rightarrow$ (After) retains its prior state in software standby mode. |

| 8.11.2 Register | 284, 285 | Port F Data Direction Register (PFDDR)                                                                                                   |

| Configuration   |          | Port F Data Register (PFDR)                                                                                                              |

|                 |          | Port F Register (PORTF)                                                                                                                  |

|                 |          | Description amended                                                                                                                      |

|                 |          | (Before) retains its prior state after in software standby mode. $\rightarrow$ (After) retains its prior state in software standby mode. |

| 8.12.2 Register | 294, 295 | Port G Data Direction Register (PGDDR)                                                                                                   |

| Configuration   |          | Port G Data Register (PGDR)                                                                                                              |

|                 |          | Port G Register (PORTG)                                                                                                                  |

|                 |          | Description amended                                                                                                                      |

|                 |          | (Before) retains its prior state after in software standby mode. $\rightarrow$ (After) retains its prior state in software standby mode. |

| Туре                     | Instruction | Size <sup>*1</sup> | Function                                                                                                                                                                                                       |

|--------------------------|-------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic<br>operations | DIVXS       | B/W                | Rd ÷ Rs → Rd<br>Performs signed division on data in two general<br>registers: either 16 bits ÷ 8 bits → 8-bit quotient and 8-bit<br>remainder or 32 bits ÷ 16 bits → 16-bit quotient and 16-<br>bit remainder. |

|                          | CMP         | B/W/L              | Rd – Rs, Rd – #IMM<br>Compares data in a general register with data in another<br>general register or with immediate data, and sets CCR<br>bits according to the result.                                       |

|                          | NEG         | B/W/L              | $0 - Rd \rightarrow Rd$<br>Takes the two's complement (arithmetic complement) of data in a general register.                                                                                                   |

|                          | EXTU        | W/L                | Rd (zero extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size,<br>or the lower 16 bits of a 32-bit register to longword size,<br>by padding with zeros on the left.       |

|                          | EXTS        | W/L                | Rd (sign extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size,<br>or the lower 16 bits of a 32-bit register to longword size,<br>by extending the sign bit.               |

|                          | TAS         | В                  | @ERd – 0, 1 $\rightarrow$ ( <bit 7=""> of @Erd)<sup>*2</sup><br/>Tests memory contents, and sets the most significant bit<br/>(bit 7) to 1.</bit>                                                              |

# Rev.7.00 Feb. 14, 2007 page 60 of 1108 REJ09B0089-0700

# Section 2 CPU

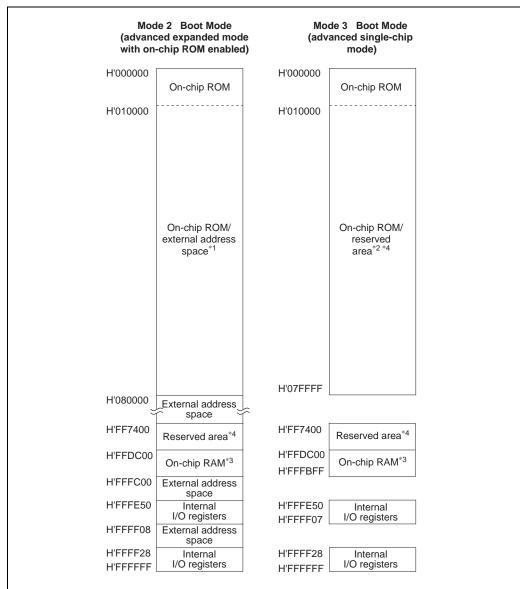

- Notes: 1. External addresses when EAE = 1 in BCRL; on-chip ROM when EAE = 0.

- 2. Reserved area when EAE = 1 in BCRL; on-chip ROM when EAE = 0.

- 3. On-chip RAM is used for flash memory programming. Do not clear the RAME bit to 0 in SYSCR.

- 4. Do not access the reserved areas.

# Figure 3.1 (a) H8S/2319 Memory Map in Each Operating Mode (F-ZTAT Version Only)

# Section 8 I/O Ports

# 8.1 Overview

The H8S/2319 Group has 10 I/O ports (ports 1 to 3, and A to G), and one input-only port (port 4).

Table 8.1 summarizes the port functions. The pins of each port also have other functions.

Each port includes a data direction register (DDR) that controls input/output (not provided for the input-only ports), a data register (DR) that stores output data, and a port register (PORT) used to read the pin states.

Ports A to E have a built-in MOS pull-up function, and in addition to DR and DDR, have a MOS input pull-up control register (PCR) to control the on/off state of MOS input pull-up.

Port 3 and port A include an open drain control register (ODR) that controls the on/off state of the output buffer PMOS.

Ports 1, A to F can drive a single TTL load and 50-pF capacitive load, and ports 2, 3, and G can drive a single TTL load and 30-pF capacitive load.

Ports 1, 2, and ports 34, 35 (only when used as IRQ inputs), ports F0 to F3 (only when used as IRQ inputs), ports G0 and G1 (only when used as IRQ inputs) are schmitt-triggered inputs.

#### Pin

#### Selection Method and Pin Functions

P20/TIOCA3

The pin function is switched as shown below according to the combination of the TPU channel 3 setting by bits MD3 to MD0 in TMDR3, bits IOA3 to IOA0 in TIOR3H, bits CCLR2 to CCLR0 in TCR3, and bit P20DDR.

| TPU Channel<br>3 Setting | Table Below (1) | Table B   | elow (2)   |

|--------------------------|-----------------|-----------|------------|

| P20DDR                   | _               | 0         | 1          |

| Pin function             | TIOCA3 output   | P20 input | P20 output |

|                          |                 | TIOCA3    | input *1   |

| TPU Channel<br>3 Setting | (2)                        | (1)                                        | (2)    | (1)                                   | (1)                     | (2)   |

|--------------------------|----------------------------|--------------------------------------------|--------|---------------------------------------|-------------------------|-------|

| MD3 to MD0               | B'0                        | 000                                        | B'001× | B'0010                                | B'0                     | 011   |

| IOA3 to IOA0             | B'0000<br>B'0100<br>B'1××× | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 | B'××00 | Oth                                   | er than B'×             | ×00   |

| CCLR2 to<br>CCLR0        | _                          | _                                          | —      |                                       | Other<br>than<br>B'001  | B'001 |

| Output<br>function       |                            | Output<br>compare<br>output                |        | PWM<br>mode 1<br>output <sup>*2</sup> | PWM<br>mode 2<br>output |       |

×: Don't care

- Notes: 1. TIOCA3 input when MD3 to MD0 = B'0000 and IOA3 to IOA0 =  $B'10\times\times$ .

- 2. TIOCB3 output is disabled.

# 8.10.2 Register Configuration

Table 8.17 shows the port E register configuration.

#### Table 8.17 Port E Registers

| Name                                | Abbreviation | R/W | Initial Value | Address* |

|-------------------------------------|--------------|-----|---------------|----------|

| Port E data direction register      | PEDDR        | W   | H'00          | H'FEBD   |

| Port E data register                | PEDR         | R/W | H'00          | H'FF6D   |

| Port E register                     | PORTE        | R   | Undefined     | H'FF5D   |

| Port E MOS pull-up control register | PEPCR        | R/W | H'00          | H'FF74   |

Note: \* Lower 16 bits of the address.

## Port E Data Direction Register (PEDDR)

| Bit        | :     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |       | PE7DDR | PE6DDR | PE5DDR | PE4DDR | PE3DDR | PE2DDR | PE1DDR | PE0DDR |

| Initial va | lue : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :     | W      | W      | W      | W      | W      | W      | W      | W      |

PEDDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port E. PEDDR cannot be read; if it is, an undefined value will be read.

PEDDR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

• Modes 4 to 6\*

When 8-bit bus mode has been selected, port E pins function as I/O ports. Setting a PEDDR bit to 1 makes the corresponding port E pin an output port, while clearing the bit to 0 makes the pin an input port.

When 16-bit bus mode has been selected, the input/output direction specification by PEDDR is ignored, and port E is designated for data I/O.

For details of 8-bit and 16-bit bus modes, see section 6, Bus Controller.

• Mode 7\*

Setting PEDDR bits to 1 makes the corresponding port E pins output ports, while clearing the bits to 0 makes the pins input ports.

Note: \* Modes 6 and 7 are not available in the ROMless versions.

# 9.4 Operation

#### 9.4.1 Overview

Operation in each mode is outlined below.

**Normal Operation:** Each channel has a TCNT and TGR register. TCNT performs up-counting, and is also capable of free-running operation, synchronous counting, and external event counting.

Each TGR can be used as an input capture register or output compare register.

**Synchronous Operation:** When synchronous operation is designated for a channel, TCNT for that channel performs synchronous presetting. That is, when TCNT for a channel designated for synchronous operation is rewritten, the TCNT counters for the other channels are also rewritten at the same time. Synchronous clearing of the TCNT counters is also possible by setting the timer synchronization bits in TSYR for channels designated for synchronous operation.

# **Buffer Operation**

• When TGR is an output compare register

When a compare match occurs, the value in the buffer register for the relevant channel is transferred to TGR.

• When TGR is an input capture register

When input capture occurs, the value in TCNT is transferred to TGR and the value previously held in TGR is transferred to the buffer register.

**Cascaded Operation:** The channel 1 counter (TCNT1) and channel 2 counter (TCNT2), or the channel 4 counter (TCNT4) and channel 5 counter (TCNT5), can be connected together to operate as a 32-bit counter.

**PWM Mode:** In this mode, a PWM waveform is output. The output level can be set by means of TIOR. A PWM waveform with a duty of between 0% and 100% can be output, according to the setting of each TGR register.

**Phase Counting Mode:** In this mode, TCNT is incremented or decremented by detecting the phases of two clocks input from the external clock input pins in channels 1, 2, 4, and 5. When phase counting mode is set, the corresponding TCLK pin functions as the clock pin, and TCNT performs up/down-counting.

This can be used for two-phase encoder pulse input.

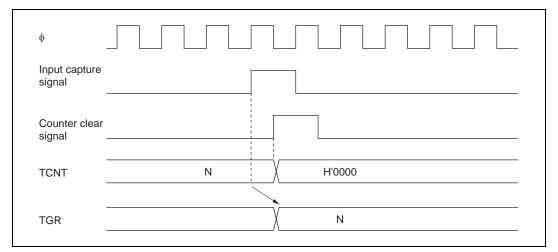

**Timing for Counter Clearing by Compare Match/Input Capture:** Figure 9.38 shows the timing when counter clearing by compare match occurrence is specified, and figure 9.39 shows the timing when counter clearing by input capture occurrence is specified.

| ф                       |            |

|-------------------------|------------|

| Compare<br>match signal |            |

| Counter<br>clear signal |            |

| TCNT                    | N / H'0000 |

| TGR                     | N          |

Figure 9.38 Counter Clear Timing (Compare Match)

Figure 9.39 Counter Clear Timing (Input Capture)

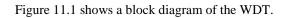

#### 11.1.2 Block Diagram

#### Figure 11.1 Block Diagram of WDT

| Bit        | :     | 7      | 6     | 5   | 4 | 3 | 2    | 1    | 0    |

|------------|-------|--------|-------|-----|---|---|------|------|------|

|            |       | OVF    | WT/IT | TME | _ | — | CKS2 | CKS1 | CKS0 |

| Initial va | lue : | 0      | 0     | 0   | 1 | 1 | 0    | 0    | 0    |

| R/W        | :     | R/(W)* | R/W   | R/W |   | _ | R/W  | R/W  | R/W  |

#### 11.2.2 Timer Control/Status Register (TCSR)

Note: \* Only 0 can be written, to clear the flag.

TCSR is an 8-bit readable/writable<sup>\*</sup> register. Its functions include selecting the clock source to be input to TCNT, and the timer mode.

TCR is initialized to H'18 by a reset and in hardware standby mode. It is not initialized in software standby mode.

Note: \* TCSR is write-protected by a password to prevent accidental overwriting. For details see section 11.2.4, Notes on Register Access.

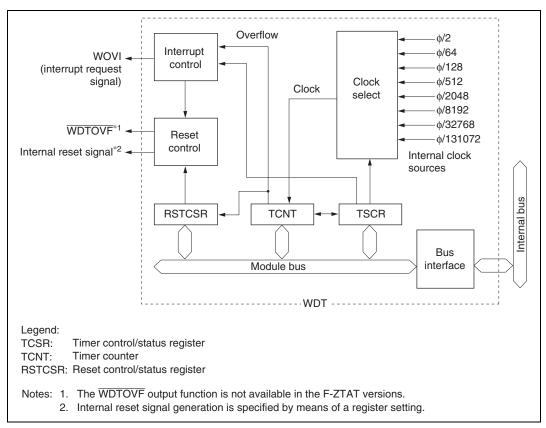

**Bit 7—Overflow Flag (OVF):** Indicates that TCNT has overflowed from H'FF to H'00, when in interval timer mode. This flag cannot be set during watchdog timer operation.

| Bit 7<br>OVF | Description                                                                    |                 |

|--------------|--------------------------------------------------------------------------------|-----------------|

| 0            | [Clearing condition]                                                           | (Initial value) |

|              | Cleared by reading TCSR when $OVF = 1^*$ , then writing 0 to $OVF$             |                 |

| 1            | [Setting condition]                                                            |                 |

|              | Set when TCNT overflows (changes from H'FF to H'00) in interval tim            | er mode         |

| Note: *V     | When $OVE$ is polled and the interval timer interrupt is disabled. $OVE - 1$ m | ust he read at  |

Note: \* When OVF is polled and the interval timer interrupt is disabled, OVF = 1 must be read at least twice.

**Bit 6—Timer Mode Select (WT/TT):** Selects whether the WDT is used as a watchdog timer or interval timer. If used as an interval timer, the WDT generates an interval timer interrupt request (WOVI) when TCNT overflows. If used as a watchdog timer, the WDT generates the  $\overline{WDTOVF}$  signal<sup>\*1</sup> when TCNT overflows.

Figure 11.4 Operation in Watchdog Timer Mode

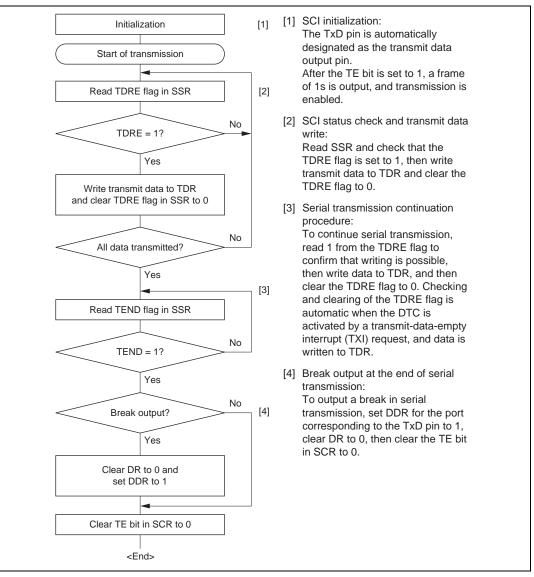

**Serial data transmission (asynchronous mode):** Figure 12.5 shows a sample flowchart for serial transmission.

The following procedure should be used for serial data transmission.

Figure 12.5 Sample Serial Transmission Flowchart

#### **Data Transfer Operations**

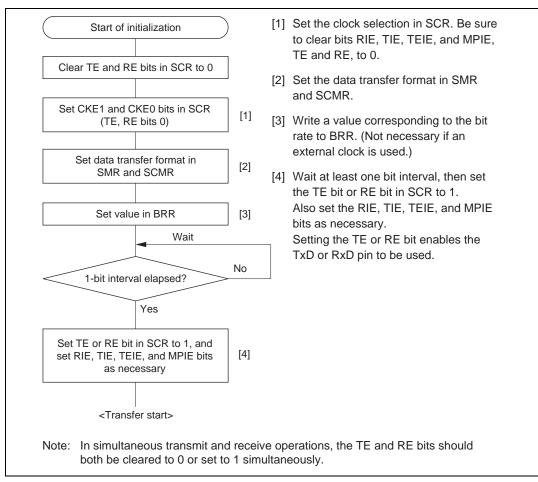

**SCI initialization (synchronous mode):** Before transmitting or receiving data, first clear the TE and RE bits in SCR to 0, then initialize the SCI as described below.

When the operating mode, transfer format, etc., is changed, the TE and RE bits must be cleared to 0 before making the change using the following procedure. When the TE bit is cleared to 0, the TDRE flag is set to 1 and TSR is initialized. Note that clearing the RE bit to 0 does not change the contents of the RDRF, PER, FER, and ORER flags, or the contents of RDR.

Figure 12.15 shows a sample SCI initialization flowchart.

## Figure 12.15 Sample SCI Initialization Flowchart

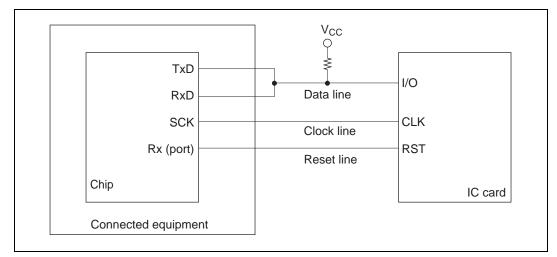

# **13.3.2** Pin Connections

Figure 13.2 shows a schematic diagram of smart card interface related pin connections.

In communication with an IC card, since both transmission and reception are carried out on a single data communication line, the chip's TxD pin and RxD pin should both be connected to the line, as shown in the figure. The data communication line should be pulled up to the  $V_{CC}$  power supply with a resistor.

When the clock generated on the smart card interface is used by an IC card, the SCK pin output is input to the CLK pin of the IC card. No connection is needed if the IC card uses an internal clock.

Chip port output is used as the reset signal.

Other pins must normally be connected to the power supply or ground.

Figure 13.2 Schematic Diagram of Smart Card Interface Pin Connections

Note: If an IC card is not connected, and the TE and RE bits are both set to 1, closed transmission/reception is possible, enabling self-diagnosis to be carried out.

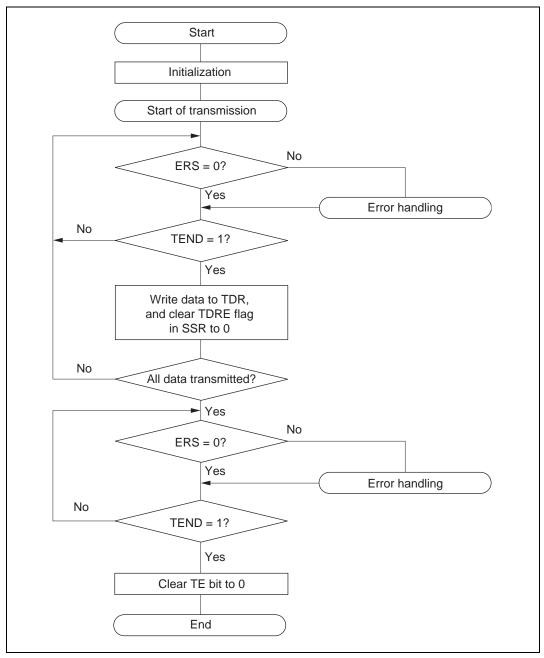

Figure 13.4 Sample Transmission Flowchart

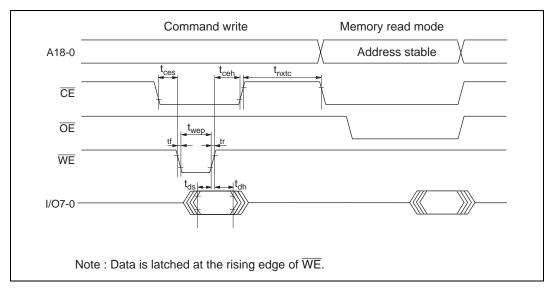

#### 17.29.2 AC Characteristics and Timing in PROM Mode

## Table 17.65 AC Characteristics in Memory Read Mode

Condition:  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_a = 25^{\circ}C \pm 5^{\circ}C$

| Code                    | Symbol            | Min | Max | Unit |  |

|-------------------------|-------------------|-----|-----|------|--|

| Command write cycle     | t <sub>nxtc</sub> | 20  | —   | μS   |  |

| CE hold time            | t <sub>ceh</sub>  | 0   | —   | ns   |  |

| CE setup time           | t <sub>ces</sub>  | 0   | —   | ns   |  |

| Data hold time          | t <sub>dh</sub>   | 50  | —   | ns   |  |

| Data setup time         | t <sub>ds</sub>   | 50  | —   | ns   |  |

| Programming pulse width | t <sub>wep</sub>  | 70  | —   | ns   |  |

| WE rise time            | tr                | _   | 30  | ns   |  |

| WE fall time            | t <sub>f</sub>    | _   | 30  | ns   |  |

|                         |                   |     |     |      |  |

Figure 17.88 Memory Read Timing after Command Write

|     |                         |            | Inst | Ad          | dres<br>tion | ssin     | Addressing Mode/<br>Instruction Length (Bytes) | B de  | rtes |        |                              |    |                |                                               |   |   |                 |

|-----|-------------------------|------------|------|-------------|--------------|----------|------------------------------------------------|-------|------|--------|------------------------------|----|----------------|-----------------------------------------------|---|---|-----------------|

|     |                         | erand Size |      | ua          | l'EBN)       | +uЯ3@\nЯ | E                                              | l'bC) | ee   |        |                              | ပိ | Condition Code | ion                                           | õ | e | No. of States*1 |

|     | Mnemonic                |            | XX#  | ш<br>Ш<br>Ц | @(q<br>100   |          | 98®                                            |       | 00   |        | Operation                    | -  | I              | N<br>Z                                        | > | υ | Advanced        |

| MOV | MOV.W @(d:16,ERs),Rd    | ≥          |      |             | 4            |          |                                                |       |      | @(     | @(d:16,ERs)→Rd16             |    |                | $\leftrightarrow \\ \leftrightarrow$          | 0 |   | ę               |

|     | MOV.W @(d:32,ERs),Rd    | ≥          |      |             | ∞            |          |                                                |       |      | @(i    | @(d:32,ERs)→Rd16             |    |                | $\leftrightarrow$                             | 0 |   | 5               |

|     | MOV.W @ERs+,Rd          | 8          |      |             |              | 2        |                                                |       |      | @E     | @ERs→Rd16,ERs32+2→ERs32  -   |    |                | $\leftrightarrow \leftrightarrow$             | 0 |   | 3               |

|     | MOV.W @aa:16,Rd         | $^{>}$     |      |             |              |          | 4                                              |       |      | @a     | @aa:16→Rd16                  |    |                | $\leftrightarrow \Rightarrow$                 | 0 |   | 3               |

|     | MOV.W @aa:32,Rd         | $\geq$     |      |             |              |          | 9                                              |       |      | @a     | @aa:32→Rd16                  |    | -7             | $\leftrightarrow \leftrightarrow$             | 0 |   | 4               |

|     | MOV.W Rs, @ERd          | ≥          |      | ~           | 2            |          |                                                |       |      | Rs1    | Rs16→@ERd                    |    |                | $\leftrightarrow \leftrightarrow$             | 0 |   | 2               |

|     | MOV.W Rs, @ (d:16,ERd)  | ≥          |      |             | 4            |          |                                                |       |      | Rs1    | Rs16→@(d:16,ERd)             |    |                | $\leftrightarrow \\ \leftrightarrow$          | 0 |   | ю               |

|     | MOV.W Rs, @ (d:32, ERd) | 8          |      |             | 8            |          |                                                |       |      | Rs1    | Rs16→@(d:32,ERd)             |    |                | $\leftrightarrow \leftrightarrow$             | 0 |   | 5               |

|     | MOV.W Rs, @-ERd         | ≥          |      |             |              | 2        |                                                |       |      | ER     | ERd32-2→ERd32,Rs16→@ERd _    |    |                | $\leftrightarrow \\ \leftrightarrow$          | 0 |   | с               |

|     | MOV.W Rs,@aa:16         | ≥          |      |             |              |          | 4                                              |       |      | Rs1    | Rs16→@aa:16                  |    |                | $\leftrightarrow \\ \leftrightarrow$          | 0 |   | r               |

|     | MOV.W Rs,@aa:32         | ≥          |      |             |              |          | 9                                              |       |      | Rs1    | Rs16→@aa:32                  |    |                | $\leftrightarrow$                             | 0 |   | 4               |

|     | MOV.L #xx:32,ERd        | _          | 9    |             |              |          |                                                |       |      | XX#    | #xx:32→ERd32                 |    |                | $\leftrightarrow$                             | 0 |   | ю               |

|     | MOV.L ERS, ERd          | _          |      | 2           |              |          |                                                |       |      | ER     | ERs32→ERd32                  |    |                | $\leftrightarrow \\ \leftrightarrow$          | 0 |   | -               |

|     | MOV.L @ERs,ERd          | _          |      | 4           | 4            |          |                                                |       |      | 8<br>E | @ERs→ERd32                   |    |                | $\leftrightarrow \\ \leftrightarrow$          | 0 |   | 4               |

|     | MOV.L @(d:16,ERs),ERd   | _          |      |             | 9            |          |                                                |       |      | @(i    | @(d:16,ERs)→ERd32            |    | -7             | $\leftrightarrow \leftrightarrow \Rightarrow$ | 0 |   | 5               |

|     | MOV.L @(d:32,ERs),ERd   | _          |      |             | 10           |          |                                                |       |      | @(i    | @(d:32,ERs)→ERd32            |    | -7             | $\leftrightarrow \leftrightarrow$             | 0 |   | 7               |

|     | MOV.L @ERs+,ERd         | _          |      |             |              | 4        |                                                |       |      | @<br>E | @ERs→ERd32,ERs32+4→@ERs32  - |    | -7             | $\leftrightarrow \leftrightarrow$             | 0 |   | 5               |

|     | MOV.L @aa:16,ERd        | _          |      |             |              |          | 9                                              |       |      | @a     | @aa:16→ERd32                 |    |                | $\leftrightarrow \Rightarrow$                 | 0 |   | 5               |

|     | MOV.L @aa:32,ERd        | _          |      | _           | _            |          | ω                                              |       |      | @a     | @aa:32→ERd32                 |    | -7             | $\leftrightarrow \\ \leftrightarrow$          | 0 |   | 6               |

| Appendix B | Internal I/O Registers |

|------------|------------------------|

|------------|------------------------|

| PEDR—Port E Data Register |           |           |           | H'FF6D     |            |                |       | Port E |   |

|---------------------------|-----------|-----------|-----------|------------|------------|----------------|-------|--------|---|

| Bit :                     | 7         | 6         | 5         | 4          | 3          | 2              | 1     | 0      | _ |

|                           | PE7DR     | PE6DR     | PE5DR     | PE4DR      | PE3DR      | PE2DR          | PE1DR | PE0DR  |   |

| Initial value :           | 0         | 0         | 0         | 0          | 0          | 0              | 0     | 0      |   |

| Read/Write :              | R/W       | R/W       | R/W       | R/W        | R/W        | R/W            | R/W   | R/W    |   |

|                           |           | Stor      | es output | data for p | ort E pins | (PE7 to P      | PE0)  |        |   |

| PFDR—Port F Data Register |           |           |           | H'FF6E     |            |                |       | Port ] |   |

| Bit :                     | 7         | 6         | 5         | 4          | 3          | 2              | 1     | 0      | _ |

|                           | PF7DR     | PF6DR     | PF5DR     | PF4DR      | PF3DR      | PF2DR          | PF1DR | PF0DR  |   |

| Initial value :           | 0         | 0         | 0         | 0          | 0          | 0              | 0     | 0      |   |

| Read/Write :              | R/W       | R/W       | R/W       | R/W        | R/W        | R/W            | R/W   | R/W    |   |

| 'GDR—Port G               | Data Reg  |           | es output | data for p | ort F pins | (PF7 to P<br>F | F0)   | Por    | t |

|                           | e         |           |           |            |            |                |       |        |   |

| Bit :                     | 7         | 6         | 5         | 4          | 3          | 2              | 1     | 0      |   |

|                           |           |           |           | PG4DR      | PG3DR      | PG2DR          | PG1DR | PG0DR  |   |

| Initial value :           | Undefined | Jndefined | Undefined | 0          | 0          | 0              | 0     | 0      |   |

| Read/Write :              | _         |           | —         | R/W        | R/W        | R/W            | R/W   | R/W    |   |

|                           |           |           |           |            |            |                |       |        |   |

Stores output data for port G pins (PG4 to PG0)

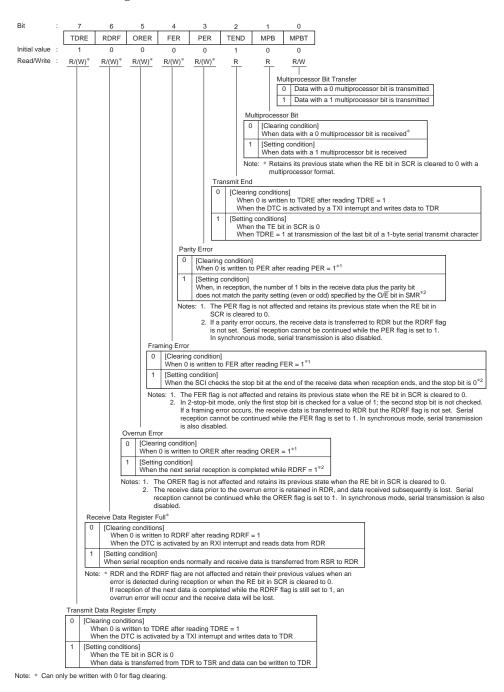

#### SSR1—Serial Status Register 1

**H'FF84**

SCI1