Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                            |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 25MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 70                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2319cvte25v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.3.3 Pin Functions

### Table 1.3Pin Functions

|                                         |                    |                             | Pin No.                     |                                   |        |                                                                                                                                                                                                                               |  |

|-----------------------------------------|--------------------|-----------------------------|-----------------------------|-----------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Туре                                    | Symbol             | TFP-100B,<br>TFP-100G       | FP-100A                     | TLP-113V                          | I/O    | Name and Function                                                                                                                                                                                                             |  |

| Power<br>supply                         | V <sub>cc</sub>    | 40, 65,<br>98               | 42, 67,<br>100              | B3, E11, L7                       | Input  | Power supply: For connection to the power supply. All $V_{CC}$ pins should be connected to the system power supply.                                                                                                           |  |

|                                         | V <sub>SS</sub>    | 7, 18,<br>31, 49,<br>68, 88 | 9, 20,<br>33, 51,<br>70, 90 | A6, D2, E9,<br>G3, J4, K3,<br>K10 | Input  | Ground: For connection to ground<br>(0 V). All $V_{SS}$ pins should be<br>connected to the system power supply<br>(0 V).                                                                                                      |  |

| Internal<br>voltage<br>step-down<br>pin | V <sub>CL</sub> *1 | 60                          | 62                          | G8                                | Output | An external capacitor should be connected between this pin and GND (0 V). Do not connect it to $V_{CC}$ .                                                                                                                     |  |

| Clock                                   | XTAL               | 66                          | 68                          | F10                               | Input  | Connects to a crystal oscillator.<br>See section 18, Clock Pulse<br>Generator, for typical connection<br>diagrams for a crystal oscillator and<br>external clock input.                                                       |  |

|                                         | EXTAL              | 67                          | 69                          | F9                                | Input  | Connects to a crystal oscillator.<br>The EXTAL pin can also input an<br>external clock.<br>See section 18, Clock Pulse<br>Generator, for typical connection<br>diagrams for a crystal oscillator and<br>external clock input. |  |

|                                         | φ                  | 69                          | 71                          | D11                               | Output | System clock: Supplies the system clock to an external device.                                                                                                                                                                |  |

|                                          |                      |                       | Pin No.  |                                      |        |                                                                                                                                                                                                                                 |

|------------------------------------------|----------------------|-----------------------|----------|--------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                                     | Symbol               | TFP-100B,<br>TFP-100G | FP-100A  | TLP-113V                             | I/O    | Name and Function                                                                                                                                                                                                               |

| Watchdog<br>timer (WDT)                  | WDTOVF <sup>*6</sup> | 60                    | 62       | G9                                   | Output | Watchdog timer overflows: The counter overflows signal output pin in watchdog timer mode.                                                                                                                                       |

| Serial com-<br>munication                | TxD1,<br>TxD0        | 9, 8                  | 11, 10   | E4, E1                               | Output | Transmit data (channel 0, 1):<br>Data output pins.                                                                                                                                                                              |

| interface<br>(SCI) Smart<br>Card         | RxD1,<br>RxD0        | 11, 10                | 13, 12   | E2, E3                               | Input  | Receive data (channel 0, 1):<br>Data input pins.                                                                                                                                                                                |

| interface                                | SCK1<br>SCK0         | 13, 12                | 15, 14   | F1, F4                               | I/O    | Serial clock (channel 0, 1):<br>Clock I/O pins.                                                                                                                                                                                 |

| A/D<br>converter                         | AN7 to<br>AN0        | 86 to 79              | 88 to 81 | D7, C7, A7,<br>B8, C8, B9,<br>A8, D9 | Input  | Analog 7 to 0: Analog input pins.                                                                                                                                                                                               |

|                                          | ADTRG                | 93                    | 95       | C6                                   | Input  | A/D conversion external trigger input:<br>Pin for input of an external trigger to<br>start A/D conversion.                                                                                                                      |

| D/A<br>converter                         | DA1, DA0             | 86, 85                | 88, 87   | D7, C7                               | Output | Analog output: D/A converter analog output pins.                                                                                                                                                                                |

| A/D<br>converter<br>and D/A<br>converter | AV <sub>CC</sub>     | 77                    | 79       | A11                                  | Input  | This is the power supply pin for the A/D converter and D/A converter. When the A/D converter and D/A converter are not used, this pin should be connected to the system power supply ( $V_{CC}$ ).                              |

|                                          | AV <sub>SS</sub>     | 87                    | 89       | B7                                   | Input  | This is the ground pin for the A/D<br>converter and D/A converter.<br>This pin should be connected to the<br>system power supply (0 V).                                                                                         |

|                                          | V <sub>ref</sub>     | 78                    | 80       | A9                                   | Input  | This is the reference voltage input pin<br>for the A/D converter and D/A<br>converter.<br>When the A/D converter and D/A<br>converter are not used, this pin should<br>be connected to the system power<br>supply ( $V_{CC}$ ). |

| Bit n<br>DTCEn | Description                                                                  |  |  |  |  |  |  |

|----------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0              | DTC activation by this interrupt is disabled (Initial value)                 |  |  |  |  |  |  |

|                | [Clearing conditions]                                                        |  |  |  |  |  |  |

|                | When the DISEL bit is 1 and the data transfer has ended                      |  |  |  |  |  |  |

|                | <ul> <li>When the specified number of transfers have ended</li> </ul>        |  |  |  |  |  |  |

| 1              | DTC activation by this interrupt is enabled                                  |  |  |  |  |  |  |

|                | [Holding condition]                                                          |  |  |  |  |  |  |

|                | When the DISEL bit is 0 and the specified number of transfers have not ended |  |  |  |  |  |  |

|                | (n = 7 to 0)                                                                 |  |  |  |  |  |  |

#### Bit n—DTC Activation Enable (DTCEn)

A DTCE bit can be set for each interrupt source that can activate the DTC. The correspondence between interrupt sources and DTCE bits is shown in table 7.5, together with the vector numbers generated by the interrupt controller.

For DTCE bit setting, read/write operations must be performed using bit-manipulation instructions such as BSET and BCLR. For the initial setting only, however, when multiple activation sources are set at one time, it is possible to disable interrupts and write after executing a dummy read on the relevant register.

#### 7.2.8 DTC Vector Register (DTVECR)

| Bit         | :    | 7     | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------------|------|-------|--------|--------|--------|--------|--------|--------|--------|

|             |      | SWDTE | DTVEC6 | DTVEC5 | DTVEC4 | DTVEC3 | DTVEC2 | DTVEC1 | DTVEC0 |

| Initial val | ue : | 0     | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W         | :    | R/(W) | R/(W)* |

Note: \* Bits DTVEC6 to DTVEC0 can be written to when SWDTE = 0.

DTVECR is an 8-bit readable/writable register that enables or disables DTC activation by software, and sets a vector number for the software activation interrupt.

DTVECR is initialized to H'00 by a reset and in hardware standby mode.

| Port   | Description                        | Pins             | Mode<br>4                                                                             | Mode<br>5                                   | Mode<br>6 <sup>*1</sup> | Mode<br>7 <sup>*1</sup>              |  |

|--------|------------------------------------|------------------|---------------------------------------------------------------------------------------|---------------------------------------------|-------------------------|--------------------------------------|--|

| Port G | <ul> <li>5-bit I/O port</li> </ul> | PG4/CS0          | When DDR =                                                                            | 0*2: input port                             |                         | I/O port also                        |  |

|        | <ul> <li>Schmitt-</li> </ul>       |                  | When DDR =                                                                            | 1*3: CSO outp                               | ut                      | functions as interrupt               |  |

|        | triggered input<br>(IRQ7, IRQ6)    | PG3/CS1/CS7      | I/O port                                                                              |                                             |                         | input pins                           |  |

|        | (IRQ7, IRQ6)                       |                  |                                                                                       | 1, CS167E = $\frac{1}{1000}$ tions as CS1 c |                         | (IRQ7, IRQ6)<br>and A/D<br>converter |  |

|        |                                    |                  | When DDR = 1, CS167E = 1, and CSS17<br>= 1: Also functions as $\overline{CS7}$ output |                                             |                         |                                      |  |

|        |                                    | PG2/CS2          | I/O port                                                                              | (ADTRG)                                     |                         |                                      |  |

|        |                                    |                  | When DDR = $functions as \overline{C}$                                                |                                             |                         |                                      |  |

|        |                                    | PG1/CS3/IRQ7/CS6 | I/O port                                                                              |                                             |                         |                                      |  |

|        |                                    |                  | When DDR =<br>0: Also function                                                        |                                             |                         |                                      |  |

|        |                                    |                  | When DDR =<br>= 1: Also func<br>interrupt input                                       |                                             |                         |                                      |  |

|        |                                    | PG0/IRQ6/ADTRG   | I/O port also f<br>pin (IRQ6) an<br>(ADTRG)                                           |                                             |                         |                                      |  |

Notes: 1. Modes 6 and 7 are not available in the ROMless versions.

- 2. After a reset in mode 6

- 3. After a reset in mode 4 or 5

#### Port Function Control Register 1 (PFCR1)

| Bit        | :     | 7     | 6     | 5       | 4       | 3    | 2    | 1    | 0    |

|------------|-------|-------|-------|---------|---------|------|------|------|------|

|            |       | CSS17 | CSS36 | PF1CS5S | PF0CS4S | A23E | A22E | A21E | A20E |

| Initial va | lue : | 0     | 0     | 0       | 0       | 1    | 1    | 1    | 1    |

| R/W        | :     | R/W   | R/W   | R/W     | R/W     | R/W  | R/W  | R/W  | R/W  |

PFCR1 is an 8-bit readable/writable register that performs I/O port control. PFCR1 is initialized to H'0F by a reset, and in hardware standby mode.

**Bit 7—CS17 Select (CSS17):** Selects whether  $\overline{CS1}$  or  $\overline{CS7}$  is output from the PG3 pin. For details, see section 8.12, Port G.

**Bit 6—CS36 Select (CSS36):** Selects whether  $\overline{CS3}$  or  $\overline{CS6}$  is output from the PG1 pin. For details, see section 8.12, Port G.

Bit 5—Port F1 Chip Select 5 Select (PF1CS5S): Selects enabling or disabling of  $\overline{CS5}$  output. For details, see section 8.11, Port F.

**Bit 4—Port F0 Chip Select 4 Select (PF0CS4S):** Selects enabling or disabling of  $\overline{CS4}$  output. For details, see section 8.11, Port F.

**Bit 3—Address 23 Enable (A23E):** Enables or disables address output 23 (A23). This bit is valid in modes 4 to 6.

| Bit 3<br>A23E | Description                     |                 |

|---------------|---------------------------------|-----------------|

| 0             | P13DR is output when P13DDR = 1 |                 |

| 1             | A23 is output when P13DDR = 1   | (Initial value) |

**Bit 2—Address 22 Enable (A22E):** Enables or disables address output 22 (A22). This bit is valid in modes 4 to 6.

| Bit 2<br>A22E | Description                     |                 |

|---------------|---------------------------------|-----------------|

| 0             | P12DR is output when P12DDR = 1 |                 |

| 1             | A22 is output when P12DDR = 1   | (Initial value) |

## 8.10.2 Register Configuration

Table 8.17 shows the port E register configuration.

#### Table 8.17 Port E Registers

| Name                                | Abbreviation | R/W | Initial Value | Address* |

|-------------------------------------|--------------|-----|---------------|----------|

| Port E data direction register      | PEDDR        | W   | H'00          | H'FEBD   |

| Port E data register                | PEDR         | R/W | H'00          | H'FF6D   |

| Port E register                     | PORTE        | R   | Undefined     | H'FF5D   |

| Port E MOS pull-up control register | PEPCR        | R/W | H'00          | H'FF74   |

Note: \* Lower 16 bits of the address.

## Port E Data Direction Register (PEDDR)

| Bit        | :     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |       | PE7DDR | PE6DDR | PE5DDR | PE4DDR | PE3DDR | PE2DDR | PE1DDR | PE0DDR |

| Initial va | lue : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :     | W      | W      | W      | W      | W      | W      | W      | W      |

PEDDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port E. PEDDR cannot be read; if it is, an undefined value will be read.

PEDDR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

• Modes 4 to 6\*

When 8-bit bus mode has been selected, port E pins function as I/O ports. Setting a PEDDR bit to 1 makes the corresponding port E pin an output port, while clearing the bit to 0 makes the pin an input port.

When 16-bit bus mode has been selected, the input/output direction specification by PEDDR is ignored, and port E is designated for data I/O.

For details of 8-bit and 16-bit bus modes, see section 6, Bus Controller.

• Mode 7\*

Setting PEDDR bits to 1 makes the corresponding port E pins output ports, while clearing the bits to 0 makes the pins input ports.

Note: \* Modes 6 and 7 are not available in the ROMless versions.

## 9.1.3 Pin Configuration

Table 9.2 summarizes the TPU pins.

## Table 9.2TPU Pins

| Channel | Name                                  | Symbol | I/O   | Function                                                                             |

|---------|---------------------------------------|--------|-------|--------------------------------------------------------------------------------------|

| All     | Clock input A                         | TCLKA  | Input | External clock A input pin<br>(Channel 1 and 5 phase counting mode A<br>phase input) |

|         | Clock input B                         | TCLKB  | Input | External clock B input pin<br>(Channel 1 and 5 phase counting mode B<br>phase input) |

|         | Clock input C                         | TCLKC  | Input | External clock C input pin<br>(Channel 2 and 4 phase counting mode A<br>phase input) |

|         | Clock input D                         | TCLKD  | Input | External clock D input pin<br>(Channel 2 and 4 phase counting mode B<br>phase input) |

| 0       | Input capture/out<br>compare match A0 | TIOCA0 | I/O   | TGR0A input capture input/output compare output/PWM output pin                       |

|         | Input capture/out compare match B0    | TIOCB0 | I/O   | TGR0B input capture input/output compare output/PWM output pin                       |

|         | Input capture/out<br>compare match C0 | TIOCC0 | I/O   | TGR0C input capture input/output compare<br>output/PWM output pin                    |

|         | Input capture/out<br>compare match D0 | TIOCD0 | I/O   | TGR0D input capture input/output compare output/PWM output pin                       |

| 1       | Input capture/out<br>compare match A1 | TIOCA1 | I/O   | TGR1A input capture input/output compare output/PWM output pin                       |

|         | Input capture/out<br>compare match B1 | TIOCB1 | I/O   | TGR1B input capture input/output compare output/PWM output pin                       |

| 2       | Input capture/out compare match A2    | TIOCA2 | I/O   | TGR2A input capture input/output compare output/PWM output pin                       |

|         | Input capture/out compare match B2    | TIOCB2 | I/O   | TGR2B input capture input/output compare output/PWM output pin                       |

**Contention between Overflow/Underflow and Counter Clearing:** If overflow/underflow and counter clearing occur simultaneously, the TCFV/TCFU flag in TSR is not set and TCNT clearing takes precedence.

Figure 9.56 shows the operation timing when a TGR compare match is specified as the clearing source, and H'FFFF is set in TGR.

| φ                       |               |  |

|-------------------------|---------------|--|

| TCNT input<br>clock     |               |  |

| TCNT                    | H'FFFF H'0000 |  |

| Counter<br>clear signal |               |  |

| TGF                     |               |  |

| TCFV flag               | Prohibited    |  |

Figure 9.56 Contention between Overflow and Counter Clearing

## 12.1.4 Register Configuration

The SCI has the internal registers shown in table 12.2. These registers are used to specify asynchronous mode or synchronous mode, the data format, and the bit rate, and to control the transmitter/receiver.

### Table 12.2 SCI Registers

| Channel | Name                         | Abbreviation | R/W     | Initial Value | Address*2 |

|---------|------------------------------|--------------|---------|---------------|-----------|

| 0       | Serial mode register 0       | SMR0         | R/W     | H'00          | H'FF78    |

|         | Bit rate register 0          | BRR0         | R/W     | H'FF          | H'FF79    |

|         | Serial control register 0    | SCR0         | R/W     | H'00          | H'FF7A    |

|         | Transmit data register 0     | TDR0         | R/W     | H'FF          | H'FF7B    |

|         | Serial status register 0     | SSR0         | R/(W)*1 | H'84          | H'FF7C    |

|         | Receive data register 0      | RDR0         | R       | H'00          | H'FF7D    |

|         | Smart card mode register 0   | SCMR0        | R/W     | H'F2          | H'FF7E    |

| 1       | Serial mode register 1       | SMR1         | R/W     | H'00          | H'FF80    |

|         | Bit rate register 1          | BRR1         | R/W     | H'FF          | H'FF81    |

|         | Serial control register 1    | SCR1         | R/W     | H'00          | H'FF82    |

|         | Transmit data register 1     | TDR1         | R/W     | H'FF          | H'FF83    |

|         | Serial status register 1     | SSR1         | R/(W)*1 | H'84          | H'FF84    |

|         | Receive data register 1      | RDR1         | R       | H'00          | H'FF85    |

|         | Smart card mode register 1   | SCMR1        | R/W     | H'F2          | H'FF86    |

| All     | Module stop control register | MSTPCR       | R/W     | H'3FFF        | H'FF3C    |

Notes: 1. Can only be written with 0 for flag clearing.

2. Lower 16 bits of the address.

#### 12.2.3 Transmit Shift Register (TSR)

TSR is a register used to transmit serial data.

To perform serial data transmission, the SCI first transfers transmit data from TDR to TSR, then sends the data to the TxD pin starting with the LSB (bit 0).

When transmission of one byte is completed, the next transmit data is transferred from TDR to TSR, and transmission started, automatically. However, data transfer from TDR to TSR is not performed if the TDRE bit in SSR is set to 1.

TSR cannot be directly read or written to by the CPU.

## 12.2.4 Transmit Data Register (TDR)

| Bit        | :      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|            |        |     |     |     |     |     |     |     |     |

| Initial va | alue : | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W        | :      | R/W |

TDR is an 8-bit register that stores data for serial transmission.

When the SCI detects that TSR is empty, it transfers the transmit data written in TDR to TSR and starts serial transmission. Continuous serial transmission can be carried out by writing the next transmit data to TDR during serial transmission of the data in TSR.

TDR can be read or written to by the CPU at all times.

TDR is initialized to H'FF by a reset, and in standby mode or module stop mode.

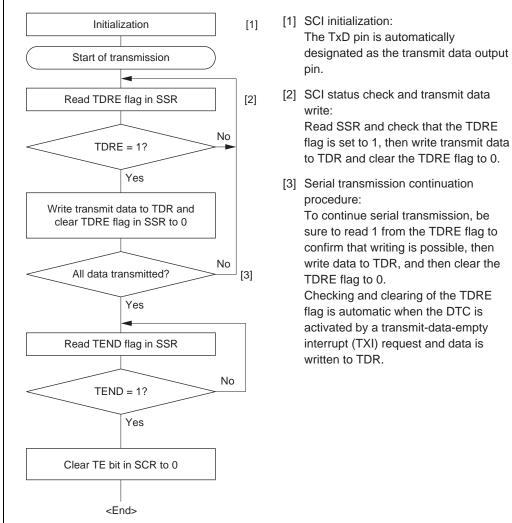

Serial data transmission (synchronous mode): Figure 12.16 shows a sample flowchart for serial transmission.

The following procedure should be used for serial data transmission.

Figure 12.16 Sample Serial Transmission Flowchart

#### 17.20.6 Auto-Erase Mode

- Auto-erase mode supports only total memory erasing.

- Do not perform a command write during auto-erasing.

- Confirm normal end of auto-erasing by checking I/O<sub>6</sub>. Alternatively, status read mode can also be used for this purpose (the I/O<sub>7</sub> status polling pin is used to identify the end of an auto-erase operation).

- Status polling I/O<sub>6</sub> and I/O<sub>7</sub> pin information is retained until the next command write. As long as the next command write has not been performed, reading is possible by enabling CE and OE.

#### **AC Characteristics**

#### Table 17.41 AC Characteristics in Auto-Erase Mode

Conditions:  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_a = 25^{\circ}C \pm 5^{\circ}C$

| Item                       | Symbol             | Min | Max   | Unit |

|----------------------------|--------------------|-----|-------|------|

| Command write cycle        | t <sub>nxtc</sub>  | 20  | —     | μs   |

| CE hold time               | t <sub>ceh</sub>   | 0   |       | ns   |

| CE setup time              | t <sub>ces</sub>   | 0   | —     | ns   |

| Data hold time             | t <sub>dh</sub>    | 50  | _     | ns   |

| Data setup time            | t <sub>ds</sub>    | 50  |       | ns   |

| Write pulse width          | t <sub>wep</sub>   | 70  | —     | ns   |

| Status polling start time  | t <sub>ests</sub>  | 1   |       | ms   |

| Status polling access time | t <sub>spa</sub>   | _   | 150   | ns   |

| Memory erase time          | t <sub>erase</sub> | 100 | 40000 | ms   |

| WE rise time               | t <sub>r</sub>     | _   | 30    | ns   |

| WE fall time               | t <sub>f</sub>     | _   | 30    | ns   |

### 17.28.1 Pin Arrangement of the Socket Adapter

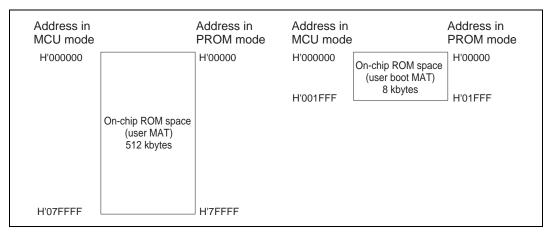

Attach the socket adapter to the LSI in the way shown in figure 17.81. This allows conversion to 40 pins. Figure 17.80 shows the memory mapping of the on-chip ROM, and figure 17.81 shows the arrangement of the socket adapter's pins.

Figure 17.80 Mapping of On-Chip Flash Memory

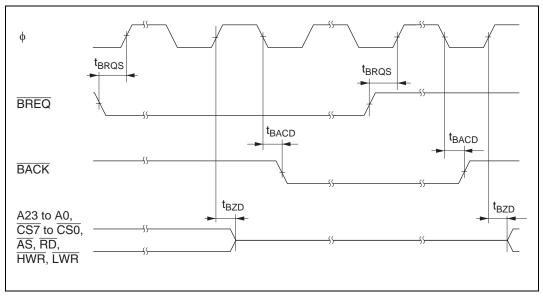

Figure 20.11 External Bus Release Timing

Figure 20.12 External Bus Request Output Timing

## 20.2 Electrical Characteristics of F-ZTAT Versions (H8S/2319 F-ZTAT, H8S/2319E F-ZTAT, H8S/2318 F-ZTAT, H8S/2317 F-ZTAT, H8S/2315 F-ZTAT, H8S/2314 F-ZTAT)

### 20.2.1 Absolute Maximum Ratings

### **Table 20.10 Absolute Maximum Ratings**

Condition B:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to  $75^{\circ}\text{C}$  (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  (wide-range specifications)

| Item                           | Symbol           | Value                                       | Unit |  |  |  |

|--------------------------------|------------------|---------------------------------------------|------|--|--|--|

| Power supply voltage           | V <sub>CC</sub>  | -0.3 to +4.3                                | V    |  |  |  |

| Input voltage (FWE, EMLE)      | V <sub>in</sub>  | –0.3 to V <sub>CC</sub> +0.3                | V    |  |  |  |

| Input voltage (except port 4)  | Vin              | –0.3 to V <sub>CC</sub> +0.3                | V    |  |  |  |

| Input voltage (port 4)         | Vin              | -0.3 to AV <sub>CC</sub> +0.3               | V    |  |  |  |

| Reference power supply voltage | V <sub>ref</sub> | –0.3 to AV <sub>CC</sub> +0.3               | V    |  |  |  |

| Analog power supply voltage    | AV <sub>CC</sub> | -0.3 to +4.3                                | V    |  |  |  |

| Analog input voltage           | V <sub>AN</sub>  | –0.3 to AV <sub>CC</sub> +0.3               |      |  |  |  |

| Operating temperature          | T <sub>opr</sub> | Regular specifications: -20 to +75*         | °C   |  |  |  |

|                                |                  | Wide-range specifications: $-40$ to $+85^*$ | °C   |  |  |  |

| Storage temperature            | T <sub>stg</sub> | -55 to +125                                 | °C   |  |  |  |

Caution: Permanent damage to the chip may result if absolute maximum ratings are exceeded.

Note: \* Condition B: The operating temperature ranges for flash memory programming/erasing are  $T_a = 0^{\circ}C$  to +75°C (regular specifications), and  $T_a = 0^{\circ}C$  to +85°C (wide-range specifications).

# A.3 Operation Code Map

Table A.3 shows the operation code map.

## Table A.3Operation Code Map (1)

|                                                                                                                                  | ш    | DX Table<br>A.3(2) |                 |            |       | IT BLE | JSR             |                 | (3)                    |                 |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----------------|------------|-------|--------|-----------------|-----------------|------------------------|-----------------|--------|------|------|----|-----|-----|-----|-------------------------------------|---------------|--|-----------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|-------|------|--|--|--|--|--|--|--|--|--|--|

|                                                                                                                                  | ш    | ADDX               | SUBX            |            |       | BGT    | Sſ              |                 | Table A.3(3)           | ole A.3         |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  |      | 2                  | CMP             |            |       | BLT    |                 | MOV             | Та                     |                 |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | U    | MOV                |                 |            | BGE   | BGE    | BSR             |                 |                        |                 |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

| 3H is 0.<br>3H is 1.                                                                                                             | ш    | Table<br>A.3(2)    | Table<br>A.3(2) |            |       | BMI    |                 |                 | EEPMOV                 |                 |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>Instruction when most significant bit of BH is 0.</li> <li>Instruction when most significant bit of BH is 1.</li> </ul> | A    | Table<br>A.3(2)    | Table<br>A.3(2) |            |       | BPL    | JMP             | Table<br>A.3(2) | Table<br>A.3(2)        |                 |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | 6    | ADD                | SUB             |            | MOV.B | BVS    | Table<br>A.3(2) |                 | MOV                    | Table<br>A.3(2) |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | 8    | AD                 | SL              |            |       | BVC    |                 | A.3(2           | MOV                    | ADD             | ADDX   | CMP  | SUBX | OR | R   | g   | MOV |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>Instructio</li> <li>Instructio</li> </ul>                                                                               | 7    | LDC                | Table<br>A.3(2) | <b>O</b> W |       | BEQ    | TRAPA           | BST<br>BIST     |                        | AD              | ADI    | CV   | SU   | 0  | XOR | AND | M   |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

| 1st byte     2nd byte       AH     AL       BH     BL                                                                            | 9    | ANDC               | AND             |            |       |        |                 |                 |                        |                 |        |      |      |    |     | BNE | RTE | AND                                 | BAND<br>BIAND |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | 5    | XORC               | XOR             |            |       | BCS    | BSR             | ~               | BOR BXOR<br>BIOR BIXOR | BIOR            |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | 4    | ORC                | OR              |            |       | BCC    | RTS             | OR              |                        |                 |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | e    | LDC<br>*           | Table<br>A.3(2) |            |       | -      |                 |                 |                        |                 |        |      |      |    |     |     |     |                                     |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | BLS | DIVXU | 1010 |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | 2    | STC 1              | Table<br>A.3(2) |            |       |        |                 |                 | BHI                    | MULXU           | i<br>C | BCLK |      |    |     |     |     |                                     |               |  | the chip. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                  | -    | Table<br>A.3(2)    | Table<br>A.3(2) |            |       | BRN    | DIVXU           | H C             | BNU                    |                 |        |      |      |    |     |     |     | Note: * Cannot be used in the chip. |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

| Instruction code                                                                                                                 | 0    | NOP                | Table<br>A.3(2) |            |       | BRA    | MULXU           |                 | BOEL                   |                 |        |      |      |    |     |     |     | Cannot k                            |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

| Instructi                                                                                                                        | AHAL | 0                  | -               | 2          | 3     | 4      | 5               | 9               | 7                      | 80              | 6      | ٨    | ш    | U  | Δ   | ш   | ш   | Note: *                             |               |  |           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |     |       |      |  |  |  |  |  |  |  |  |  |  |

## RENESAS

| Instruction | nstruction H N Z V C |    |    |    | С                                                                               | Definition                                                                         |  |  |  |  |

|-------------|----------------------|----|----|----|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| SUB         | ¢                    | ¢  | \$ | ¢  | ¢                                                                               | $H = Sm-4 \cdot \overline{Dm-4} + \overline{Dm-4} \cdot Rm-4 + Sm-4 \cdot Rm-4$    |  |  |  |  |

|             |                      |    |    |    |                                                                                 | N = Rm                                                                             |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $Z = \overline{Rm} \cdot \overline{Rm-1} \cdot \dots \cdot \overline{R0}$          |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $V = \overline{Sm} \cdot Dm \cdot \overline{Rm} + Sm \cdot \overline{Dm} \cdot Rm$ |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $C = Sm \cdot \overline{Dm} + \overline{Dm} \cdot Rm + Sm \cdot Rm$                |  |  |  |  |

| SUBS        |                      |    |    |    | _                                                                               |                                                                                    |  |  |  |  |

| SUBX        | SUBX ↓ ↓ ↓           |    | \$ | \$ | $H = Sm-4 \cdot \overline{Dm-4} + \overline{Dm-4} \cdot Rm-4 + Sm-4 \cdot Rm-4$ |                                                                                    |  |  |  |  |

|             |                      |    |    |    |                                                                                 | N = Rm                                                                             |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $Z = Z' \cdot \overline{Rm} \cdot \dots \cdot \overline{R0}$                       |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $V = \overline{Sm} \cdot Dm \cdot \overline{Rm} + Sm \cdot \overline{Dm} \cdot Rm$ |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $C = Sm \cdot \overline{Dm} + \overline{Dm} \cdot Rm + Sm \cdot Rm$                |  |  |  |  |

| TAS         | _                    | \$ | \$ | 0  | _                                                                               | N = Dm                                                                             |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $Z = \overline{Dm} \cdot \overline{Dm-1} \cdot \dots \cdot \overline{D0}$          |  |  |  |  |

| TRAPA       |                      |    |    | _  | _                                                                               |                                                                                    |  |  |  |  |

| XOR         | _                    | ¢  | ¢  | 0  | _                                                                               | N = Rm                                                                             |  |  |  |  |

|             |                      |    |    |    |                                                                                 | $Z = \overline{Rm} \cdot \overline{Rm-1} \cdot \dots \cdot \overline{R0}$          |  |  |  |  |

| XORC        | ¢                    | ¢  | ¢  | ¢  | \$                                                                              | Stores the corresponding bits of the result.                                       |  |  |  |  |

|             |                      |    |    |    |                                                                                 | No flags change when the operand is EXR.                                           |  |  |  |  |

#### TIOR3L—Timer I/O Control Register 3L

H'FE83

**TPU3**

| Bit :           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------|------|------|------|------|------|------|------|------|

|                 | IOD3 | IOD2 | IOD1 | IOD0 | IOC3 | IOC2 | IOC1 | IOC0 |

| Initial value : | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Read/Write :    | R/W  |

| 0 | 0 | 0 | 0 | TGR3C                              | Output disabled                                     |                                            |                           |  |

|---|---|---|---|------------------------------------|-----------------------------------------------------|--------------------------------------------|---------------------------|--|

|   |   |   | 1 | is output<br>compare<br>register*1 | Initial output is                                   | 0 output at compare match                  |                           |  |

|   |   | 1 | 0 | register*1                         | 0 output                                            | 1 output at compare match                  |                           |  |

|   |   |   | 1 | ]                                  |                                                     | Toggle output at compare match             |                           |  |

|   | 1 | 0 | 0 | ]                                  | Output disabled                                     |                                            |                           |  |

|   |   |   | 1 | 1                                  | Initial output is 1                                 | 0 output at compare match                  |                           |  |

|   |   |   | 1 | 0                                  | 1                                                   | output                                     | 1 output at compare match |  |

|   |   |   | 1 | 1                                  |                                                     | Toggle output at compare match             |                           |  |

| 1 | 0 | 0 | 0 | TGR3C                              | Capture input                                       | Input capture at rising edge               |                           |  |

|   |   |   | 1 | is input<br>capture                | source is<br>TIOCC3 pin                             | Input capture at falling edge              |                           |  |

|   |   | 1 |   | capture<br>register*               |                                                     | Input capture at both edges                |                           |  |

| - | 1 | s |   |                                    | Capture input<br>source is channel<br>4/count clock | Input capture at TCNT4 count-up count-down |                           |  |

: Don't care

Note: \* When the BFA bit in TMDR3 is set to 1 and TGR3C is used as a buffer register, this setting is invalid and input capture/output compare does not occur.

#### TGR3D I/O Control

| 0 | 0 | 0 | 0 | TGR3D | Output disabled      |                                                     |                                                  |

|---|---|---|---|-------|----------------------|-----------------------------------------------------|--------------------------------------------------|

|   |   |   |   | 1     | is output<br>compare | Initial output is 0<br>output                       | 0 output at compare match                        |

|   |   |   | 1 | 0     | register<br>*2       | oulput                                              | 1 output at compare match                        |

|   |   |   |   | 1     |                      |                                                     | Toggle output at compare match                   |

|   |   | 1 | 0 | 0     |                      | Output disabled                                     |                                                  |

|   |   |   |   | 1     |                      | Initial output is 1                                 | 0 output at compare match                        |

|   |   |   | 1 | 0     |                      | output                                              | 1 output at compare match                        |

|   |   |   |   | 1     |                      |                                                     | Toggle output at compare match                   |

|   | 1 | 0 | 0 | 0     | TGR3D                | Capture input<br>source is                          | Input capture at rising edge                     |

|   |   |   |   | 1     | is input<br>capture  | TIOCD3 pin                                          | Input capture at falling edge                    |

|   |   |   | 1 |       | register<br>*2       |                                                     | Input capture at both edges                      |

|   |   | 1 |   |       | -                    | Capture input<br>source is channel<br>4/count clock | Input capture at TCNT4 count-up/<br>count-down*1 |

: Don't care

- Notes: 1. When bits TPSC2 to TPSC0 in TCR4 are set to B'000 and ∲/1 is used as the TCNT4 count clock, this setting is invalid and input capture does not occur.

- When the BFB bit in TMDR3 is set to 1 and TGR3D is used as a buffer register, this setting is invalid and input capture/output compare does not occur.

Note: When TGRC or TGRD is designated for buffer operation, this setting is invalid and the register operates as a buffer register.

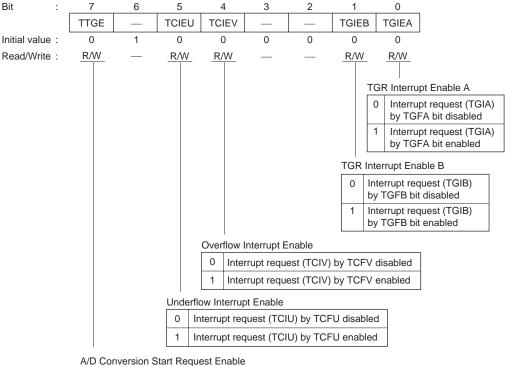

## **TIER5**—Timer Interrupt Enable Register 5

H'FEA4

| 0 | A/D conversion start request generation disabled |   |

|---|--------------------------------------------------|---|

| 1 | A/D conversion start request generation enabled  | 1 |

#### Rev.7.00 Feb. 14, 2007 page 977 of 1108 REJ09B0089-0700

Note: If 0 is written to the CST bit during operation with the TIOC pin designated for output, the counter stops but the TIOC pin output compare output level is retained. If TIOR is written to when the CST bit is cleared to 0, the pin output level will be changed to the set initial output value.

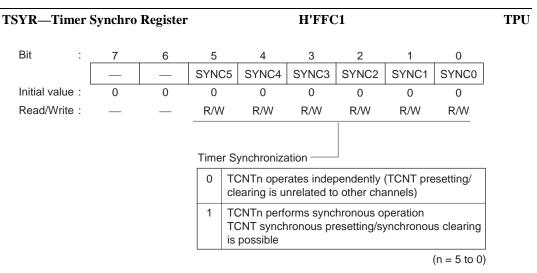

- Notes: 1. To set synchronous operation, the SYNC bits for at least two channels must be set to 1.

- 2. To set synchronous clearing, in addition to the SYNC bit, the TCNT clearing source must also be set by means of bits CCLR2 to CCLR0 in TCR.

#### RENESAS