#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 25MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 70                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 8K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BQFP                                                                     |

| Supplier Device Package    | 100-QFP (14x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2319vf25v |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

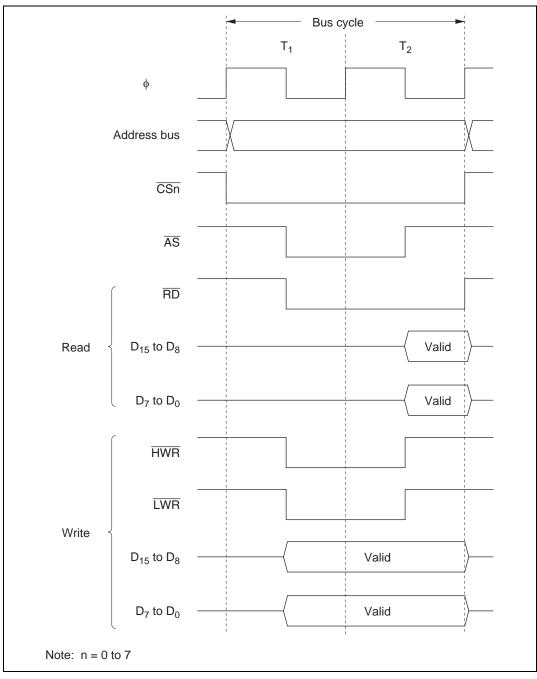

Section 6 Bus Controller

#### Pin

TMO0

#### Selection Method and Pin Functions

The pin function is switched as shown below according to the combination of P26/TIOCA5/ the TPU channel 5 setting by bits MD3 to MD0 in TMDR5, bits IOA3 to IOA0 in TIOR5, bits CCLR1 and CCLR0 in TCR5, bits OS3 to OS0 in TCSR0, and bit P26DDR.

| OS3 to OS0               |                    | Any 1           |             |  |  |

|--------------------------|--------------------|-----------------|-------------|--|--|

| TPU Channel<br>5 Setting | Table<br>Below (1) | Table B         | _           |  |  |

| P26DDR                   | _                  | 0               | —           |  |  |

| Pin function             | TIOCA5<br>output   | P26 input       | TMO0 output |  |  |

|                          |                    | TIOCA5 input *1 |             |  |  |

| TPU Channel<br>5 Setting | (2)                        | (1)                                        | (2)    | (1)                                   | (1)                     | (2)  |  |

|--------------------------|----------------------------|--------------------------------------------|--------|---------------------------------------|-------------------------|------|--|

| MD3 to MD0               |                            | B'01××                                     | B'001× | B'0010                                | B'0                     |      |  |

| IOA3 to IOA0             | B'0000<br>B'0100<br>B'1××× | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 | B'××00 | Oth                                   | er than B'xx00          |      |  |

| CCLR1,<br>CCLR0          | —                          |                                            | —      | —                                     | Other<br>than B'01      | B'01 |  |

| Output<br>function       |                            | Output<br>compare<br>output                | _      | PWM<br>mode 1<br>output <sup>*2</sup> | PWM<br>mode 2<br>output | —    |  |

×: Don't care

Notes: 1. TIOCA5 input when MD3 to MD0 = B'0000 or B'01×× and IOA3 = 1. 2. TIOCB5 output is disabled.

| Channel | Bit 2<br>TPSC2 | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                                        |

|---------|----------------|----------------|----------------|----------------------------------------------------|

| 3       | 0              | 0              | 0              | Internal clock: counts on $\phi/1$ (Initial value) |

|         |                |                | 1              | Internal clock: counts on $\phi/4$                 |

|         |                | 1              | 0              | Internal clock: counts on $\phi/16$                |

|         |                |                | 1              | Internal clock: counts on \u00f64                  |

|         | 1              | 0              | 0              | External clock: counts on TCLKA pin input          |

|         |                |                | 1              | Internal clock: counts on \u00e6/1024              |

|         |                | 1              | 0              | Internal clock: counts on \u00e6/256               |

|         |                |                | 1              | Internal clock: counts on                          |

| Section 9 | 16-Bit Timer Pulse Unit | (TPU) |

|-----------|-------------------------|-------|

|-----------|-------------------------|-------|

| Channel | Bit 2<br>TPSC2 | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                                        |

|---------|----------------|----------------|----------------|----------------------------------------------------|

| 4       | 0              | 0              | 0              | Internal clock: counts on $\phi/1$ (Initial value) |

|         |                |                | 1              | Internal clock: counts on \u00f6/4                 |

|         |                | 1              | 0              | Internal clock: counts on $\phi/16$                |

|         |                |                | 1              | Internal clock: counts on \phi/64                  |

|         | 1              | 0              | 0              | External clock: counts on TCLKA pin input          |

|         |                |                | 1              | External clock: counts on TCLKC pin input          |

|         |                | 1              | 0              | Internal clock: counts on \u00e6/1024              |

|         |                |                | 1              | Counts on TCNT5 overflow/underflow                 |

Note: This setting is ignored when channel 4 is in phase counting mode.

| Channel | Bit 2<br>TPSC2 | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                                        |

|---------|----------------|----------------|----------------|----------------------------------------------------|

| 5       | 0              | 0              | 0              | Internal clock: counts on $\phi/1$ (Initial value) |

|         |                |                | 1              | Internal clock: counts on $\phi/4$                 |

|         |                | 1              | 0              | Internal clock: counts on $\phi/16$                |

|         |                |                | 1              | Internal clock: counts on $\phi/64$                |

|         | 1              | 0              | 0              | External clock: counts on TCLKA pin input          |

|         |                |                | 1              | External clock: counts on TCLKC pin input          |

|         |                | 1              | 0              | Internal clock: counts on $\phi/256$               |

|         |                |                | 1              | External clock: counts on TCLKD pin input          |

Note: This setting is ignored when channel 5 is in phase counting mode.

The correspondence between PWM output pins and registers is shown in table 9.7.

|         |           | (          | Output Pins |

|---------|-----------|------------|-------------|

| Channel | Registers | PWM Mode 1 | PWM Mode 2  |

| 0       | TGR0A     | TIOCA0     | TIOCA0      |

|         | TGR0B     |            | TIOCB0      |

|         | TGR0C     | TIOCC0     | TIOCC0      |

|         | TGR0D     |            | TIOCD0      |

| 1       | TGR1A     | TIOCA1     | TIOCA1      |

|         | TGR1B     |            | TIOCB1      |

| 2       | TGR2A     | TIOCA2     | TIOCA2      |

|         | TGR2B     |            | TIOCB2      |

| 3       | TGR3A     | TIOCA3     | TIOCA3      |

|         | TGR3B     |            | TIOCB3      |

|         | TGR3C     | TIOCC3     | TIOCC3      |

|         | TGR3D     |            | TIOCD3      |

| 4       | TGR4A     | TIOCA4     | TIOCA4      |

|         | TGR4B     |            | TIOCB4      |

| 5       | TGR5A     | TIOCA5     | TIOCA5      |

|         | TGR5B     |            | TIOCB5      |

Note: In PWM mode 2, PWM output is not possible for the TGR register in which the period is set.

# 9.6.2 Interrupt Signal Timing

**TGF Flag Setting Timing in Case of Compare Match:** Figure 9.42 shows the timing for setting of the TGF flag in TSR by compare match occurrence, and TGI interrupt request signal timing.

| φ                       |         |

|-------------------------|---------|

| TCNT input clock        |         |

| TCNT                    | N X N+1 |

| TGR                     | N       |

| Compare<br>match signal |         |

| TGF flag                |         |

| TGI interrupt           |         |

Figure 9.42 TGI Interrupt Timing (Compare Match)

# 10.6 Usage Notes

Note that the following kinds of contention can occur in the 8-bit timer module.

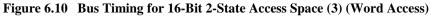

### 10.6.1 Contention between TCNT Write and Clear

If a timer counter clock pulse is generated during the  $T_2$  state of a TCNT write cycle, the clear takes priority, so that the counter is cleared and the write is not performed.

Figure 10.10 shows this operation.

Figure 10.10 Contention between TCNT Write and Clear

# **12.2** Register Descriptions

# 12.2.1 Receive Shift Register (RSR)

RSR is a register used to receive serial data.

The SCI sets serial data input from the RxD pin in RSR in the order received, starting with the LSB (bit 0), and converts it to parallel data. When one byte of data has been received, it is transferred to RDR automatically.

RSR cannot be directly read or written to by the CPU.

#### 12.2.2 Receive Data Register (RDR)

| Bit        | :      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|--------|---|---|---|---|---|---|---|---|

|            |        |   |   |   |   |   |   |   |   |

| Initial va | alue : | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W        | :      | R | R | R | R | R | R | R | R |

RDR is a register that stores received serial data.

When the SCI has received one byte of serial data, it transfers the received serial data from RSR to RDR where it is stored, and completes the receive operation. After this, RSR is receive-enabled.

Since RSR and RDR function as a double buffer in this way, continuous receive operations can be performed.

RDR is a read-only register, and cannot be written to by the CPU.

RDR is initialized to H'00 by a reset, and in standby mode or module stop mode.

### Clock

Either an internal clock generated by the built-in baud rate generator or an external clock input at the SCK pin can be selected as the SCI's serial clock, according to the setting of the  $C/\overline{A}$  bit in SMR and the CKE1 and CKE0 bits in SCR. For details of SCI clock source selection, see table 12.9.

When an external clock is input at the SCK pin, the clock frequency should be 16 times the bit rate used.

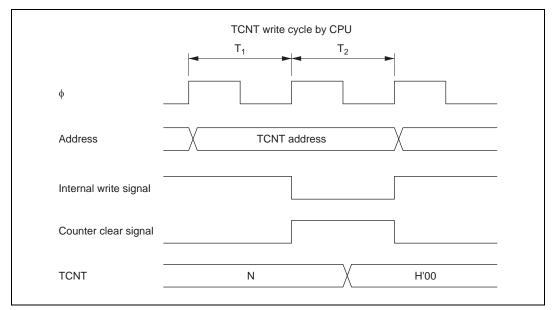

When the SCI is operated on an internal clock, the clock can be output from the SCK pin. The frequency of the clock output in this case is equal to the bit rate, and the phase is such that the rising edge of the clock is at the center of each transmit data bit, as shown in figure 12.3.

Figure 12.3 Relation between Output Clock and Transfer Data Phase (Asynchronous Mode)

### **Data Transfer Operations**

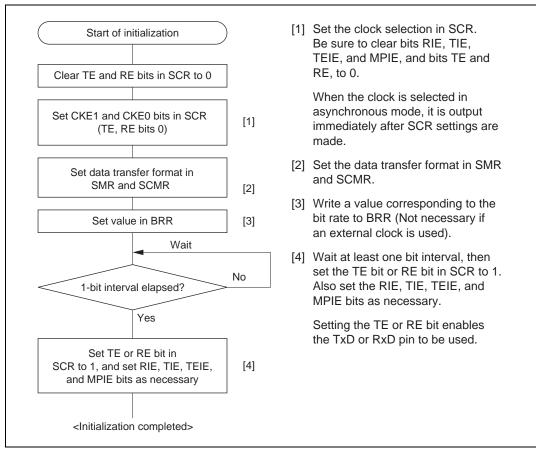

**SCI initialization (asynchronous mode):** Before transmitting or receiving data, first clear the TE and RE bits in SCR to 0, then initialize the SCI as described below.

When the operating mode, transfer format, etc., is changed, the TE and RE bits must be cleared to 0 before making the change using the following procedure. When the TE bit is cleared to 0, the TDRE flag is set to 1 and TSR is initialized. Note that clearing the RE bit to 0 does not change the contents of the RDRF, PER, FER, and ORER flags, or the contents of RDR.

When an external clock is used the clock should not be stopped during operation, including initialization, since operation will be unreliable in this case.

#### Figure 12.4 shows a sample SCI initialization flowchart.

Figure 12.4 Sample SCI Initialization Flowchart

### **Data Transfer Operations**

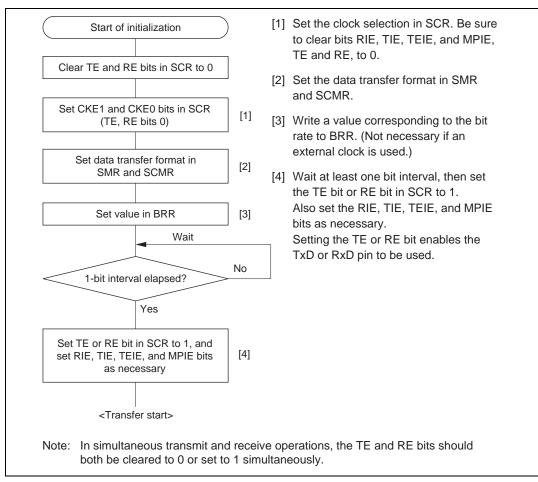

**SCI initialization (synchronous mode):** Before transmitting or receiving data, first clear the TE and RE bits in SCR to 0, then initialize the SCI as described below.

When the operating mode, transfer format, etc., is changed, the TE and RE bits must be cleared to 0 before making the change using the following procedure. When the TE bit is cleared to 0, the TDRE flag is set to 1 and TSR is initialized. Note that clearing the RE bit to 0 does not change the contents of the RDRF, PER, FER, and ORER flags, or the contents of RDR.

Figure 12.15 shows a sample SCI initialization flowchart.

# Figure 12.15 Sample SCI Initialization Flowchart

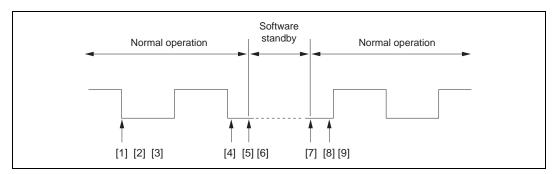

# 13.3.7 Operation in GSM Mode

**Switching the Mode:** When switching between smart card interface mode and software standby mode, the following switching procedure should be followed in order to maintain the clock duty.

- When changing from smart card interface mode to software standby mode

- [1] Set the data register (DR) and data direction register (DDR) corresponding to the SCK pin to the value for the fixed output state in software standby mode.

- [2] Write 0 to the TE bit and RE bit in the serial control register (SCR) to halt the transmit/receive operation. At the same time, set the CKE1 bit to the value for the fixed output state in software standby mode.

- [3] Write 0 to the CKE0 bit in SCR to halt the clock.

- [4] Wait for one serial clock period.During this interval, clock output is fixed at the specified level, with the duty preserved.

- [5] Write H'00 to SMR and SCMR.

- [6] Make the transition to the software standby state.

- When returning to smart card interface mode from software standby mode

- [7] Exit the software standby state.

- [8] Set the CKE1 bit in SCR to the value for the fixed output state (current SCK pin state) when software standby mode is initiated.

- [9] Set smart card interface mode and output the clock. Signal generation is started with the normal duty.

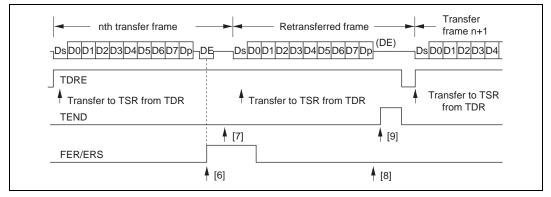

- Retransfer operation when SCI is in transmit mode Figure 13.12 illustrates the retransfer operation when the SCI is in transmit mode.

- [6] If an error signal is sent back from the receiving end after transmission of one frame is completed, the ERS bit in SSR is set to 1. If the RIE bit in SCR is enabled at this time, an ERI interrupt request is generated. The ERS bit in SSR should be kept cleared to 0 until the next parity bit is sampled.

- [7] The TEND bit in SSR is not set for a frame for which an error signal indicating an abnormality is received.

- [8] If an error signal is not sent back from the receiving end, the ERS bit in SSR is not set.

- [9] If an error signal is not sent back from the receiving end, transmission of one frame, including a retransfer, is judged to have been completed, and the TEND bit in SSR is set to 1. If the TIE bit in SCR is enabled at this time, a TXI interrupt request is generated.

If DTC data transfer by a TXI source is enabled, the next data can be written to TDR automatically. When data is written to TDR by the DTC, the TDRE bit is automatically cleared to 0.

Figure 13.12 Retransfer Operation in SCI Transmit Mode

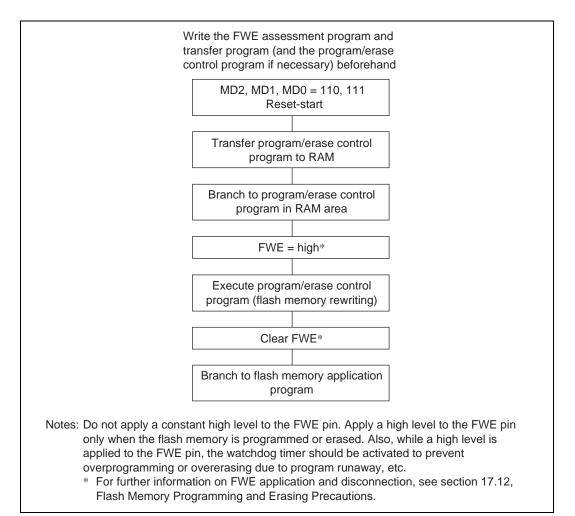

The flash memory itself cannot be read while the SWE bit is set to 1 to perform programming or erasing, so the control program that performs programming and erasing should be run in on-chip RAM or external memory. When the program is located in external memory, an instruction for programming the flash memory and the following instruction should be located in on-chip RAM.

Figure 17.14 shows the procedure for executing the program/erase control program when transferred to on-chip RAM.

Figure 17.14 User Program Mode Execution Procedure

However, the RAM area overlapping flash memory space can be read and written to regardless of whether the SWE bit is set or cleared.

**Do not use interrupts while flash memory is being programmed or erased:** All interrupt requests, including NMI, should be disabled during FWE application to give priority to program/erase operations.

**Do not perform additional programming. Erase the memory before reprogramming:** In onboard programming, perform only one programming operation on a 128-byte programming unit block. In PROM mode, too, perform only one programming operation on a 128-byte programming unit block. Programming should be carried out with the entire programming unit block erased.

**Before programming, check that the chip is correctly mounted in the PROM programmer:** Overcurrent damage to the device can result if the index marks on the PROM programmer socket, socket adapter, and chip are not correctly aligned.

**Do not touch the socket adapter or chip during programming:** Touching either of these can cause contact faults and write errors.

# **17.17.3 Error Protection**

In error protection, an error is detected when MCU runaway occurs during flash memory programming/erasing, or operation is not performed in accordance with the program/erase algorithm, and the program/erase operation is aborted. Aborting the program/erase operation prevents damage to the flash memory due to overprogramming or overerasing.

If the MCU malfunctions during flash memory programming/erasing, the FLER bit is set to 1 in FLMCR2 and the error protection state is entered. The FLMCR1, FLMCR2, EBR1, and EBR2 settings are retained, but program mode or erase mode is aborted at the point at which the error occurred. Program mode or erase mode cannot be re-entered by re-setting the P1, P2, E1, or E2 bit. However, PV1, PV2, EV1, and EV2 bit setting is enabled, and a transition can be made to verify mode.

FLER bit setting conditions are as follows:

- When flash memory is read during programming/erasing (including a vector read or instruction fetch)

- Immediately after exception handling (excluding a reset) during programming/erasing

- When a SLEEP instruction (including software standby) is executed during programming/erasing

- When a bus master other than the CPU (the DTC) has control of the bus during programming/erasing

Error protection is released only by a reset and in hardware standby mode.

Figure 17.47 shows the flash memory state transition diagram.

#### 20.3.2 DC Characteristics

#### **Table 20.21 DC Characteristics**

$\begin{array}{ll} \mbox{Condition B:} & V_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V, } AV_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V, } V_{ref} = 3.0 \mbox{ V to } AV_{CC}, \\ & V_{SS} = AV_{SS} = 0 \mbox{ V}^{*1}, \mbox{ T}_a = -20^{\circ}\mbox{C to } +75^{\circ}\mbox{C (regular specifications)}, \\ & T_a = -40^{\circ}\mbox{C to } +85^{\circ}\mbox{C (wide-range specifications)} \end{array}$

| ltem                                             |                                   | Symbol          | Min                   | Тур | Мах                    | Unit | Test<br>Conditions                                                                  |

|--------------------------------------------------|-----------------------------------|-----------------|-----------------------|-----|------------------------|------|-------------------------------------------------------------------------------------|

| Schmitt<br>trigger input<br>voltage              | Ports 1, 2,<br>IRQ0 to IRQ7       | VT <sup>-</sup> | $V_{CC} \times 0.2$   | _   | _                      | V    |                                                                                     |

|                                                  |                                   | VT <sup>+</sup> | _                     | _   | $V_{CC} \times 0.7$    | V    |                                                                                     |

|                                                  |                                   | $VT^+ - VT^-$   | $V_{CC} \times 0.07$  | _   | _                      | V    | _                                                                                   |

| Input high<br>voltage                            | RES, STBY, NMI,<br>MD2 to MD0     | V <sub>IH</sub> | $V_{CC} \times 0.9$   | —   | V <sub>CC</sub> + 0.3  | V    |                                                                                     |

|                                                  | EXTAL                             | _               | $V_{CC} \times 0.7$   | _   | $V_{CC} + 0.3$         | V    |                                                                                     |

|                                                  | Ports 3, A to G                   | _               | 2.2                   | —   | V <sub>CC</sub> + 0.3  | V    | —                                                                                   |

|                                                  | Port 4                            | _               | 2.2                   | _   | AV <sub>CC</sub> + 0.3 | V    |                                                                                     |

| Input low<br>voltage                             | RES, STBY,<br>MD2 to MD0          | V <sub>IL</sub> | -0.3                  | _   | $V_{CC} \times 0.1$    | V    |                                                                                     |

|                                                  | NMI, EXTAL,<br>ports 3, 4, A to G | _               | -0.3                  | _   | $V_{CC} \times 0.2$    | V    | _                                                                                   |

| Output high                                      | All output pins                   | V <sub>OH</sub> | $V_{CC}-0.5$          | —   | _                      | V    | I <sub>OH</sub> = -200 μA                                                           |

| voltage                                          |                                   |                 | V <sub>cc</sub> – 1.0 | —   | _                      | V    | $I_{OH} = -1 \text{ mA}$                                                            |

| Output low voltage                               | All output pins                   | V <sub>OL</sub> | —                     | _   | 0.4                    | V    | I <sub>OL</sub> = 1.6 mA                                                            |

| Input<br>leakage                                 | RES                               | I <sub>in</sub> | _                     | _   | 10.0                   | μΑ   | $\begin{array}{l} V_{in}=0.5 \text{ V to} \\ V_{CC}-0.5 \text{ V} \end{array}$      |

| current                                          | STBY, NMI,<br>MD2 to MD0          | _               | _                     | —   | 1.0                    | μA   | _                                                                                   |

|                                                  | Port 4                            | -               |                       | —   | 1.0                    | μΑ   | $\begin{array}{l} V_{in} = 0.5 \text{ V to} \\ AV_{CC} - 0.5 \text{ V} \end{array}$ |

| Three-state<br>leakage<br>current<br>(off state) | Ports 1 to 3,<br>A to G           | <sub>TSI</sub>  | —                     | _   | 1.0                    | μΑ   | $V_{in} = 0.5 \text{ V to}$ $V_{CC} - 0.5 \text{ V}$                                |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |                                                                     |                                                                                                        |                                                                                         |                                                                       |                                             |                                                                           |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                   |   |                             | 1   |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|---|-----------------------------|-----|

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        | Insti                                                               | Add                                                                                                    | Addressing Mode/<br>uction Length (By                                                   | sing<br>_eng                                                          | jth (                                       | Addressing Mode/<br>Instruction Length (Bytes)                            | (s                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                   |   |                             |     |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | erand Size                                             |                                                                     | цл                                                                                                     | (n93,k                                                                                  | +uЯ3@\nЯ3                                                             | 4'6C)<br>9                                  | 999<br>(0.1 <sup>4</sup> 1                                                |                                                                | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nditio | Condition Code    | e | No. of States <sup>*1</sup> |     |

|                             | Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        | นช<br>xx#                                                           |                                                                                                        | <b>)</b> @                                                                              | <b>I-</b> @                                                           | ישני<br>100<br>100                          |                                                                           | -                                                              | Operation I H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Z<br>I | ><br>2            | ပ | Advanced                    |     |

| EEPMOV                      | EEPMOV.B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |                                                                     |                                                                                                        |                                                                                         |                                                                       |                                             |                                                                           | 4                                                              | if R4L≠0<br>Repeat @ER5→@ER6<br>ER5+1→ER5<br>ER6+1→ER6<br>R4L-1→R4L<br>Until R4L=0<br>else next;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                   |   | 4+2n*2                      |     |

|                             | EEPMOV.W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |                                                                     |                                                                                                        |                                                                                         |                                                                       |                                             |                                                                           | 4                                                              | if R4≠0<br>Repeat @ER5→@ER6<br>ER5+1→ER5<br>ER6+1→ER6<br>R4-1→R4<br>Until R4=0<br>else next;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                   |   | 4+2n*2                      |     |

| Notes:<br>9 8 7 6 5 4 3 2 1 | The number of states is the number of states required for execution when the instruction<br>n is the initial value of R4L or R4.<br>Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction.<br>Seven states for saving or restoring two registers, nine states for three registers, or ele<br>Cannot be used in the chip.<br>Set to 1 when a carry or borrow occurs at bit 11; otherwise cleared to 0.<br>Set to 1 when the divisor is negative; otherwise cleared to 0.<br>Set to 1 when the divisor is negative; otherwise cleared to 0.<br>Set to 1 when the divisor is negative; otherwise cleared to 0.<br>Set to 1 when the divisor is negative; otherwise cleared to 0.<br>Set to 1 when the divisor is zero; otherwise cleared to 0.<br>Set to 1 when the divisor is required for execution when EXR is valid. | umb<br>R4.<br>storii<br>storii<br>en t<br>en t<br>egat | Der o<br>Der o<br>Der o<br>Der o<br>Ccur<br>he re<br>ccur<br>ive; - | f sta<br>sho<br>vore<br>s at<br>s at<br>s at<br>s at<br>s at<br>s at<br>s at<br>s othe<br>cothe<br>cut | ttes r<br>uld k<br>egisti<br>bit 1<br>bit 2<br>bit 2<br>is z<br>e cle<br>e cle<br>ion v | equi<br>eers,<br>7; ot<br>ero;<br>ero;<br>areccie<br>sareccie<br>then | ired<br>sed<br>then<br>othe<br>arec<br>lear | for e<br>wher<br>wher<br>stat<br>wise<br>wise<br>vise<br>of to<br>0.<br>C | xect<br>xect<br>es fc<br>clea<br>clea<br>clea<br>clea<br>valic | The number of states is the number of states required for execution when the instruction and its operands are located in on-chip memory.<br>In is the initial value of R4L or R4.<br>Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction.<br>Seven states for saving or restoring two registers, nine states for three registers, or eleven states for four registers.<br>Cannot be used in the chip.<br>Set to 1 when a carry or borrow occurs at bit 11; otherwise cleared to 0.<br>Retains its previous value when the result is zero; otherwise cleared to 0.<br>Set to 1 when the divisor is negative; otherwise cleared to 0.<br>Set to 1 when the divisor is negative; otherwise cleared to 0.<br>Set to 1 when the divisor is regative; otherwise cleared to 0.<br>Set to 1 when the divisor is regative; otherwise cleared to 0.<br>Set to 1 when the divisor is regative; otherwise cleared to 0.<br>Set to 1 when the divisor is regative; otherwise cleared to 0.<br>Set to 1 when the divisor is regative; otherwise cleared to 0. | nds a  | e loca<br>gisters |   | on-chip memo                | 1 > |

(8) Block Transfer Instructions

| Table A.6 | Instruction | Execution | Cycles |

|-----------|-------------|-----------|--------|

|-----------|-------------|-----------|--------|

| 6           |                |             |                 |             |                  |                |                  |               |            |                |              |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

|-------------|----------------|-------------|-----------------|-------------|------------------|----------------|------------------|---------------|------------|----------------|--------------|-----------------|-------------|------------------|----------------|----------------|----------------|---------------|-----------------|------------------|-------------------|-------------------|------------------|------------------|----------|----------|-------------------|-------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 80          |                |             |                 |             |                  |                |                  |               |            |                |              |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 7           |                |             |                 |             |                  |                |                  |               |            |                |              |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 9           |                |             |                 |             |                  |                |                  |               |            |                |              |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 5           |                |             |                 |             |                  |                |                  |               |            |                |              |                 |             |                  |                |                |                |               |                 |                  |                   | R:W:M NEXT        |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 4           |                |             |                 |             |                  |                |                  |               |            |                |              |                 |             |                  |                |                |                |               |                 |                  | R:W:M NEXT        | R:B EA            |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| з           |                |             |                 |             | R:W NEXT         |                |                  |               |            |                |              |                 |             | R:W NEXT         |                |                |                |               | R:W:M NEXT      | R:W:M NEXT       | R:B EA            | R:W 4th           |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 2           |                |             | R:W NEXT        |             | R:W 3rd          |                |                  |               |            |                |              | R:W NEXT        |             | R:W 3rd          | R:W NEXT       |                | R:W NEXT       |               | R:B EA          |                  |                   | R:W 3rd           | R:W EA           | R:W EA           | R:W EA   | R:W EA   | R:W EA            | R:W EA            | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   |

| -           | R:W NEXT       | R:W NEXT    | R:W 2nd         | R:W NEXT    | R:W 2nd          | R:W NEXT       | R:W NEXT         | R:W NEXT      | R:W NEXT   | R:W NEXT       | R:W NEXT     | R:W 2nd         | R:W NEXT    | R:W 2nd          | R:W 2nd        | R:W NEXT       | R:W 2nd        | R:W NEXT      | R:W 2nd         | R:W 2nd          | R:W 2nd           | R:W 2nd           |                  | R:W NEXT         | R:W NEXT | R:W NEXT | R:W NEXT          | R:W NEXT          | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT |

| Instruction | ADD.B #xx:8,Rd | ADD.B Rs,Rd | ADD.W #xx:16,Rd | ADD.W Rs,Rd | ADD.L #xx:32,ERd | ADD.L ERS, ERd | ADDS #1/2/4, ERd | ADDX #xx:8,Rd | ADDX Rs,Rd | AND.B #xx:8,Rd | AND.B Rs, Rd | AND.W #xx:16,Rd | AND.W Rs,Rd | AND.L #xx:32,ERd | AND.L ERS, ERd | ANDC #xx:8,CCR | ANDC #xx:8,EXR | BAND #xx:3,Rd | BAND #xx:3,@ERd | BAND #xx:3,@aa:8 | BAND #xx:3,@aa:16 | BAND #xx:3,@aa:32 | BRA d:8 (BT d:8) | BRN d:8 (BF d:8) | BHI d:8  | BLS d:8  | BCC d:8 (BHS d:8) | BCS d:8 (BLO d:8) | BNE d:8  | BEQ d:8  | BVC d:8  | BVS d:8  | BPL d:8  | BMI d:8  | BGE d:8  | BLT d:8  | BGT d:8  |

Rev.7.00 Feb. 14, 2007 page 922 of 1108 REJ09B0089-0700

| Module               | Register                          | Abbreviation | R/W      | Initial Value | Address*1 |

|----------------------|-----------------------------------|--------------|----------|---------------|-----------|

| All SMCI<br>channels | Module stop control register      | MSTPCR       | R/W      | H'3FFF        | H'FF3C    |

| ADC                  | A/D data register AH              | ADDRAH       | R        | H'00          | H'FF90    |

|                      | A/D data register AL              | ADDRAL       | R        | H'00          | H'FF91    |

|                      | A/D data register BH              | ADDRBH       | R        | H'00          | H'FF92    |

|                      | A/D data register BL              | ADDRBL       | R        | H'00          | H'FF93    |

|                      | A/D data register CH              | ADDRCH       | R        | H'00          | H'FF94    |

|                      | A/D data register CL              | ADDRCL       | R        | H'00          | H'FF95    |

|                      | A/D data register DH              | ADDRDH       | R        | H'00          | H'FF96    |

|                      | A/D data register DL              | ADDRDL       | R        | H'00          | H'FF97    |

|                      | A/D control/status register       | ADCSR        | R/(W) *9 | H'00          | H'FF98    |

|                      | A/D control register              | ADCR         | R/W      | H'3F          | H'FF99    |

|                      | Module stop control register      | MSTPCR       | R/W      | H'3FFF        | H'FF3C    |

| DAC0, 1              | D/A data register 0               | DADR0        | R/W      | H'00          | H'FFA4    |

|                      | D/A data register 1               | DADR1        | R/W      | H'00          | H'FFA5    |

|                      | D/A control register 01           | DACR01       | R/W      | H'1F          | H'FFA6    |

| All DAC channels     | Module stop control register      | MSTPCR       | R/W      | H'3FFF        | H'FF3C    |

| On-chip<br>RAM       | System control register           | SYSCR        | R/W      | H'01          | H'FF39    |

| TPU0                 | Timer control register 0          | TCR0         | R/W      | H'00          | H'FFD0    |

|                      | Timer mode register 0             | TMDR0        | R/W      | H'C0          | H'FFD1    |

|                      | Timer I/O control register 0H     | TIOR0H       | R/W      | H'00          | H'FFD2    |

|                      | Timer I/O control register 0L     | TIOR0L       | R/W      | H'00          | H'FFD3    |

|                      | Timer interrupt enable register 0 | TIER0        | R/W      | H'40          | H'FFD4    |

|                      | Timer status register 0           | TSR0         | R/(W) *2 | H'C0          | H'FFD5    |

|                      | Timer counter 0                   | TCNT0        | R/W      | H'0000        | H'FFD6    |

|                      | Timer general register 0A         | TGR0A        | R/W      | H'FFFF        | H'FFD8    |

|                      | Timer general register 0B         | TGR0B        | R/W      | H'FFFF        | H'FFDA    |

|                      | Timer general register 0C         | TGR0C        | R/W      | H'FFFF        | H'FFDC    |

|                      | Timer general register 0D         | TGR0D        | R/W      | H'FFFF        | H'FFDE    |

| TPU1                 | Timer control register 1          | TCR1         | R/W      | H'00          | H'FFE0    |

|                      | Timer mode register 1             | TMDR1        | R/W      | H'C0          | H'FFE1    |