Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

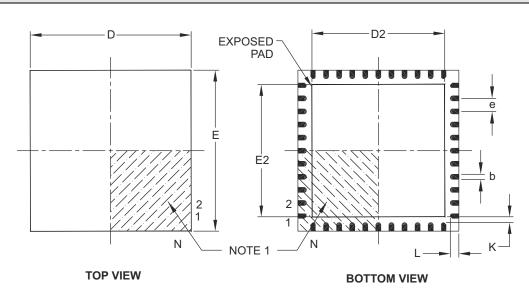

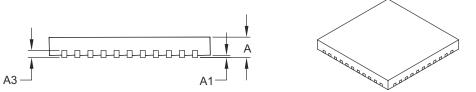

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f737-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F7X7

| Pin Name          | PDIP<br>Pin # | QFN<br>Pin # | TQFP<br>Pin #     | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                          |

|-------------------|---------------|--------------|-------------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------|

|                   |               |              |                   |               |                       | PORTD is a bidirectional I/O port or Parallel Slave Por<br>when interfacing to a microprocessor bus. |

| RD0/PSP0          | 19            | 38           | 38                |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD0               | 15            | 50           | 50                | I/O           | OT/TTE                | Digital I/O.                                                                                         |

| PSP0              |               |              |                   | I/O           |                       | Parallel Slave Port data.                                                                            |

| RD1/PSP1          | 20            | 39           | 39                |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD1               |               |              |                   | I/O           |                       | Digital I/O.                                                                                         |

| PSP1              |               |              |                   | I/O           |                       | Parallel Slave Port data.                                                                            |

| RD2/PSP2          | 21            | 40           | 40                |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD2               |               |              |                   | I/O           |                       | Digital I/O.                                                                                         |

| PSP2              |               |              |                   | I/O           |                       | Parallel Slave Port data.                                                                            |

| RD3/PSP3          | 22            | 41           | 41                |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD3               |               |              |                   | I/O           |                       | Digital I/O.                                                                                         |

| PSP3              |               |              |                   | I/O           | (2)                   | Parallel Slave Port data.                                                                            |

| RD4/PSP4          | 27            | 2            | 2                 |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD4               |               |              |                   | I/O           |                       | Digital I/O.                                                                                         |

| PSP4              |               |              |                   | I/O           | (2)                   | Parallel Slave Port data.                                                                            |

| RD5/PSP5          | 28            | 3            | 3                 |               | ST/TTL <sup>(3)</sup> | Disital I/O                                                                                          |

| RD5<br>PSP5       |               |              |                   | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                                            |

|                   |               |              |                   | 1/0           | ot (3)                | Falaliel Slave Folt data.                                                                            |

| RD6/PSP6<br>RD6   | 29            | 4            | 4                 | I/O           | ST/TTL <sup>(3)</sup> | Digital I/O.                                                                                         |

| PSP6              |               |              |                   | 1/O           |                       | Parallel Slave Port data.                                                                            |

| RD7/PSP7          | 30            | 5            | 5                 | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD7               | 30            | 5            | 5                 | I/O           | 31/112.7              | Digital I/O.                                                                                         |

| PSP7              |               |              |                   | I/O           |                       | Parallel Slave Port data.                                                                            |

| -                 |               |              |                   |               |                       | PORTE is a bidirectional I/O port.                                                                   |

| RE0/RD/AN5        | 8             | 25           | 25                |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RE0               | 0             | 25           | 25                | I/O           | 31/112.7              | Digital I/O.                                                                                         |

| RD                |               |              |                   | ,, C          |                       | Read control for Parallel Slave Port.                                                                |

| AN5               |               |              |                   | I             |                       | Analog input 5.                                                                                      |

| RE1/WR/AN6        | 9             | 26           | 26                |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RE1               | -             | -            | _                 | I/O           |                       | Digital I/O.                                                                                         |

| WR                |               |              |                   | I             |                       | Write control for Parallel Slave Port.                                                               |

| AN6               |               |              |                   | I             |                       | Analog input 6.                                                                                      |

| RE2/CS/AN7        | 10            | 27           | 27                |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RE2               |               |              |                   | I/O           |                       | Digital I/O.                                                                                         |

| CS                |               |              |                   |               |                       | Chip select control for Parallel Slave Port.                                                         |

| AN7               |               |              |                   | -             |                       | Analog input 7.                                                                                      |

| Vss               | —             | 31           | _                 | Р             | _                     | Analog ground reference.                                                                             |

| Vss               | 12, 31        | 6, 30        | 6, 29             | Р             | _                     | Ground reference for logic and I/O pins.                                                             |

| Vdd               |               | 8            | —                 | Р             | _                     | Analog positive supply.                                                                              |

| Vdd               | 11, 32        | 7, 28        | 7, 28             | Р             | —                     | Positive supply for logic and I/O pins.                                                              |

| NC                |               | 13, 29       | 12, 13,<br>33, 34 |               | _                     | These pins are not internally connected. These pins should be left unconnected.                      |

| Legend: I = input |               | 0 = ou       |                   | •             | I/O = inpu            | It/output P = power                                                                                  |

### TABLE 1-3: PIC16F747 AND PIC16F777 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured as a general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

5: Pin location of CCP2 is determined by the CCPMX bit in Configuration Word Register 1.

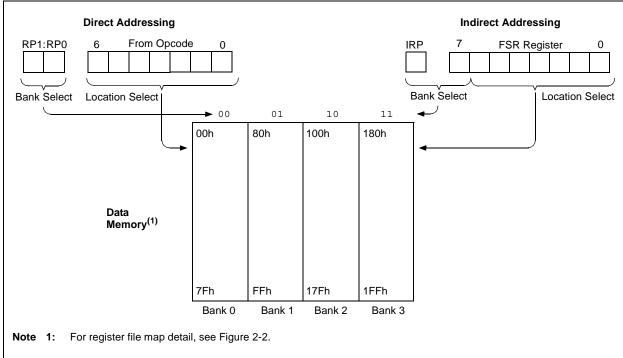

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-5.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### **INDIRECT ADDRESSING** EXAMPLE 2-2: MOVLW 0x20 ; initialize pointer MOVWF FSR ;to RAM NEXT ;clear INDF register CLRF TNDF INCF FSR, F ; inc pointer BTFSS FSR, 4 ;all done? GOTO NEXT ;no clear next CONTINUE ;yes continue :

# FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

| Current<br>System<br>Clock      | SCS bits<1:0><br>Modified to:                | Delay                                         | OSTS<br>bit | IOFS<br>bit  | T1RUN<br>bit | New<br>System<br>Clock                              | Comments                                                                                                                                                                                                                                                                                             |

|---------------------------------|----------------------------------------------|-----------------------------------------------|-------------|--------------|--------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP, XT, HS,<br>T1OSC,<br>EC, RC | 10<br>(INTRC)<br>FOSC<2:0> = LP,<br>XT or HS | 8 Clocks of<br>INTRC                          | 0           | 1 <b>(1)</b> | 0            | INTRC<br>or<br>INTOSC<br>or<br>INTOSC<br>Postscaler | The internal RC oscillator<br>frequency is dependant upon<br>the IRCF bits.                                                                                                                                                                                                                          |

| LP, XT, HS,<br>INTRC,<br>EC, RC | 01<br>(T1OSC)<br>FOSC<2:0> = LP,<br>XT or HS | 8 Clocks of<br>T1OSC                          | 0           | N/A          | 1            | T1OSC                                               | T1OSCEN bit must be enabled.                                                                                                                                                                                                                                                                         |

| INTRC<br>T1OSC                  | 00<br>FOSC<2:0> = EC<br>or<br>FOSC<2:0> = RC | 8 Clocks of<br>EC<br>or<br>RC                 | 1           | N/A          | 0            | EC<br>or<br>RC                                      |                                                                                                                                                                                                                                                                                                      |

| INTRC<br>T1OSC                  | 00<br>FOSC<2:0> = LP,<br>XT, HS              | 1024 Clocks<br>+<br>8 Clocks of<br>LP, XT, HS | 1           | N/A          | 0            | LP, XT, HS                                          | During the 1024 clocks,<br>program execution is clocked<br>from the secondary oscillator<br>until the primary oscillator<br>becomes stable.                                                                                                                                                          |

| LP, XT, HS                      | 00<br>(Due to Reset)<br>LP, XT, HS           | 1024 Clocks                                   | 1           | N/A          | 0            | LP, XT, HS                                          | When a Reset occurs, there is<br>no clock transition sequence.<br>Instruction<br>execution and/or peripheral<br>operation is suspended unless<br>Two-Speed Start-up mode is<br>enabled, after which the INTRC<br>will act as the system clock<br>until the Oscillator Start-up<br>Timer has expired. |

TABLE 4-4: CLOCK SWITCHING MODES

Note 1: If the new clock source is the INTOSC or INTOSC postscaler, then the IOFS bit will be set 4 ms (approx.) after the clock change.

#### 4.7.4 EXITING SLEEP WITH AN INTERRUPT

Any interrupt, such as WDT or INTO, will cause the part to leave the Sleep mode.

The SCS bits are unaffected by a SLEEP command and are the same before and after entering and leaving Sleep. The clock source used after an exit from Sleep is determined by the SCS bits.

#### 4.7.4.1 Sequence of Events

#### If SCS<1:0> = 00:

- 1. The device is held in Sleep until the CPU start-up time-out is complete.

- If the primary system clock is configured as an 2. external oscillator (HS, XT, LP), then the OST will be active waiting for 1024 clocks of the primary system clock. While waiting for the OST, the device will be held in Sleep unless Two-Speed Start-up is enabled. The OST and CPU start-up timers run in parallel. Refer to Section 15.17.3 "Two-Speed Clock Start-up Mode" for details on Two-Speed Start-up.

- 3. After both the CPU start-up timer and the Oscillator Start-up Timer have timed out, the device will exit Sleep and begin instruction execution with the primary clock defined by the FOSC bits.

If SCS < 1:0 > = 01 or 10:

- The device is held in Sleep until the CPU start-up 1. time-out is complete.

- 2. After the CPU start-up timer has timed out, the device will exit Sleep and begin instruction execution with the selected oscillator mode.

- Note: If a user changes SCS<1:0> just before entering Sleep mode, the system clock used when exiting Sleep mode could be different than the system clock used when entering Sleep mode. As an example, if SCS<1:0> = 01, T1OSC is the system clock and the following instructions are executed: BCF

SLEEP

OSCCON, SCS0

then a clock change event is executed. If the primary oscillator is XT, LP or HS, the core will continue to run off T1OSC and execute the SLEEP command.

When Sleep is exited, the part will resume operation with the primary oscillator after the OST has expired.

## 7.9 Resetting Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

# 7.10 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

# 7.11 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 7.6** "**Timer1 Oscillator**") gives users the option to include RTC functionality in their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 7-3, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

| RTCinit | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF<br>MOVLW<br>MOVWF<br>CLRF<br>CLRF<br>MOVLW<br>MOVWF | TMR1H<br>0x80<br>TMR1H<br>TMR1L<br>b'00001111'<br>T1CON<br>secs<br>mins<br>.12<br>hours | ; Preload TMR1 register pair<br>; for 1 second overflow<br>; Configure for external clock,<br>; Asynchronous operation, external oscillator<br>; Initialize timekeeping registers |

|---------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | BANKSEL<br>BSF                                                                        | PIE1<br>PIE1, TMR1IE                                                                    | ; Enable Timer1 interrupt                                                                                                                                                         |

| RTCisr  | RETURN<br>BANKSEL                                                                     | TMR1H                                                                                   |                                                                                                                                                                                   |

|         | BSF                                                                                   | TMR1H, 7                                                                                | ; Preload for 1 sec overflow                                                                                                                                                      |

|         | BCF                                                                                   | PIR1, TMR1IF                                                                            | ; Clear interrupt flag                                                                                                                                                            |

|         | INCF                                                                                  | secs, F                                                                                 | ; Increment seconds                                                                                                                                                               |

|         | MOVF                                                                                  | secs, w                                                                                 |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .60                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 60 seconds elapsed?                                                                                                                                                             |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | seconds                                                                                 | ; Clear seconds                                                                                                                                                                   |

|         | INCF                                                                                  | mins, f                                                                                 | ; Increment minutes                                                                                                                                                               |

|         | MOVF                                                                                  | mins, w                                                                                 |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .60                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 60 seconds elapsed?                                                                                                                                                             |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | mins                                                                                    | ; Clear minutes                                                                                                                                                                   |

|         | INCF                                                                                  | hours, f                                                                                | ; Increment hours                                                                                                                                                                 |

|         | MOVF                                                                                  | hours, w                                                                                |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .24                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 24 hours elapsed?                                                                                                                                                               |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | hours                                                                                   | ; Clear hours                                                                                                                                                                     |

|         | RETURN                                                                                |                                                                                         | ; Done                                                                                                                                                                            |

EXAMPLE 7-3: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

#### 10.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 10-1: SSPSTAT: MSSP STATUS (SPI MODE) REGISTER (ADDRESS 94h)

|       | R/W-0                                                                                                   | R/W-0           | R-0             | ,<br>R-0      | R-0         | 、<br>R-0      | ,<br>R-0     | R-0           |

|-------|---------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------|-------------|---------------|--------------|---------------|

|       | SMP                                                                                                     | CKE             | D/A             | к-0<br>Р      | R-0<br>S    | R-U<br>R/W    | UA           | BF            |

|       | bit 7                                                                                                   | ORL             | DIA             | I             | 5           | 11/00         | 07           | bit 0         |

|       |                                                                                                         |                 |                 |               |             |               |              | DILO          |

| bit 7 | SMP: Sam                                                                                                | ple bit         |                 |               |             |               |              |               |

|       | SPI Master                                                                                              | •               |                 |               |             |               |              |               |

|       | 1 = Input d                                                                                             | ata sampled     | at end of da    | ata output ti | me          |               |              |               |

|       | 0 = Input d                                                                                             | ata sampled     | at middle o     | f data outpu  | it time     |               |              |               |

|       | SPI Slave                                                                                               |                 |                 |               |             |               |              |               |

|       |                                                                                                         | be cleared w    |                 | used in Slav  | /e mode.    |               |              |               |

| bit 6 | CKE: SPI (                                                                                              | Clock Edge      | Select bit      |               |             |               |              |               |

|       |                                                                                                         | nit occurs on   |                 |               |             |               |              |               |

|       | 0 = Iransm                                                                                              | nit occurs on   |                 |               |             |               |              |               |

|       | Note:                                                                                                   | Polarity of o   | clock state is  | s set by the  | CKP bit (SS | PCON1<4>      | ).           |               |

| bit 5 | D/A: Data/                                                                                              | Address bit     |                 |               |             |               |              |               |

|       | Used in I <sup>2</sup> C                                                                                | c mode only.    |                 |               |             |               |              |               |

| bit 4 | P: Stop bit                                                                                             |                 |                 |               |             |               |              |               |

|       | Used in I <sup>2</sup> C                                                                                | mode only.      | This bit is cle | ared when t   | he MSSP me  | odule is disa | bled, SSPEN  | l is cleared. |

| bit 3 | S: Start bit                                                                                            |                 |                 |               |             |               |              |               |

|       | Used in I <sup>2</sup> C                                                                                | c mode only.    |                 |               |             |               |              |               |

| bit 2 | R/W: Read                                                                                               | I/Write bit Inf | ormation        |               |             |               |              |               |

|       | Used in I <sup>2</sup> C                                                                                | c mode only.    |                 |               |             |               |              |               |

| bit 1 | UA: Update                                                                                              | e Address bi    | it              |               |             |               |              |               |

|       |                                                                                                         | c mode only.    |                 |               |             |               |              |               |

| bit 0 | BF: Buffer                                                                                              | Full Status b   | oit (Receive    | mode only)    |             |               |              |               |

|       |                                                                                                         |                 | -               |               |             |               |              |               |

|       | <ol> <li>= Receive complete, SSPBUF is full</li> <li>= Receive not complete, SSPBUF is empty</li> </ol> |                 |                 |               |             |               |              |               |

|       |                                                                                                         |                 |                 |               |             |               |              |               |

|       | Legend:                                                                                                 |                 |                 |               |             |               |              |               |

|       | R = Reada                                                                                               | ble bit         | W = W           | ritable bit   | U = Unim    | plemented     | bit, read as | '0'           |

|       | -n = Value                                                                                              | at POR          | '1' = Bi        | t is set      | '0' = Bit i | s cleared     | x = Bit is u | nknown        |

| REGISTER 10-2: | SSPCON:                                                                                                                                                                                    | MSSP CO                                                             | NTROL (S                      | PI MODE)        | REGISTE         | R 1 (ADDR     | ESS 14h)      |             |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|-----------------|-----------------|---------------|---------------|-------------|

|                | R/W-0                                                                                                                                                                                      | R/W-0                                                               | R/W-0                         | R/W-0           | R/W-0           | R/W-0         | R/W-0         | R/W-0       |

|                | WCOL                                                                                                                                                                                       | SSPOV                                                               | SSPEN                         | CKP             | SSPM3           | SSPM2         | SSPM1         | SSPM0       |

|                | bit 7                                                                                                                                                                                      |                                                                     |                               |                 |                 |               |               | bit 0       |

|                |                                                                                                                                                                                            |                                                                     |                               |                 |                 |               |               |             |

| bit 7          |                                                                                                                                                                                            |                                                                     | Detect bit (7                 |                 | • ·             |               |               |             |

|                |                                                                                                                                                                                            | SPBUF regi:<br>be cleared i                                         | ster is writte                | n while it is s | still transmitt | ting the prev | vious word.   |             |

|                | 0 = No col                                                                                                                                                                                 |                                                                     | i soliwale.)                  |                 |                 |               |               |             |

| bit 6          | SSPOV: R                                                                                                                                                                                   | eceive Over                                                         | flow Indicate                 | or bit          |                 |               |               |             |

|                | SPI Slave i                                                                                                                                                                                |                                                                     |                               |                 |                 |               |               |             |

|                |                                                                                                                                                                                            |                                                                     | ived while th<br>ita in SSPSF |                 |                 |               |               |             |

|                |                                                                                                                                                                                            |                                                                     | PBUF, even i                  |                 |                 |               |               |             |

|                | •                                                                                                                                                                                          | be cleared in                                                       | n software.)                  | -               | -               |               | -             |             |

|                | 0 = No ove                                                                                                                                                                                 |                                                                     |                               |                 |                 |               |               |             |

|                | Note:                                                                                                                                                                                      |                                                                     | mode, the on) is initiated    |                 |                 |               |               | eption (and |

| bit 5          | SSPEN: SV                                                                                                                                                                                  |                                                                     | -                             |                 |                 | or register   |               |             |

|                | <b>SSPEN:</b> Synchronous Serial Port Enable bit $1 =$ Enables serial port and configures SCK, SDO, SDI and $\overline{SS}$ as serial port pins                                            |                                                                     |                               |                 |                 |               |               |             |

|                | 0 = Disable                                                                                                                                                                                | 0 = Disables serial port and configures these pins as I/O port pins |                               |                 |                 |               |               |             |

|                | Note:                                                                                                                                                                                      | When enab                                                           | oled, these p                 | ins must be     | properly co     | nfigured as   | input or outp | out.        |

| bit 4          |                                                                                                                                                                                            | k Polarity Se                                                       |                               |                 |                 |               |               |             |

|                | 1 = Idle state for clock is a high level<br>0 = Idle state for clock is a low level                                                                                                        |                                                                     |                               |                 |                 |               |               |             |

| bit 3-0        |                                                                                                                                                                                            |                                                                     | hronous Ser                   | -               | e Select hits   | 2             |               |             |

| Sit 0 0        |                                                                                                                                                                                            |                                                                     |                               |                 |                 |               | can be used   | as I/O pin. |

|                | $0101 = SPI$ Slave mode, clock = SCK pin. $\overline{SS}$ pin control disabled. $\overline{SS}$ can be used $0100 = SPI$ Slave mode, clock = SCK pin. $\overline{SS}$ pin control enabled. |                                                                     |                               |                 |                 |               | •             |             |

|                | 0011 = SPI Master mode, clock = TMR2 output/2<br>0010 = SPI Master mode, clock = Fosc/64<br>0001 = SPI Master mode, clock = Fosc/16                                                        |                                                                     |                               |                 |                 |               |               |             |

|                |                                                                                                                                                                                            |                                                                     |                               |                 |                 |               |               |             |

|                |                                                                                                                                                                                            |                                                                     | de, clock = l                 |                 |                 |               |               |             |

|                | Note:                                                                                                                                                                                      | Bit combina<br>I <sup>2</sup> C mode c                              | ations not sp<br>only.        | ecifically lis  | ted here are    | e either rese | rved or impl  | emented in  |

|                |                                                                                                                                                                                            |                                                                     |                               |                 |                 |               |               |             |

|                | Legend:                                                                                                                                                                                    |                                                                     |                               |                 |                 |               |               |             |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

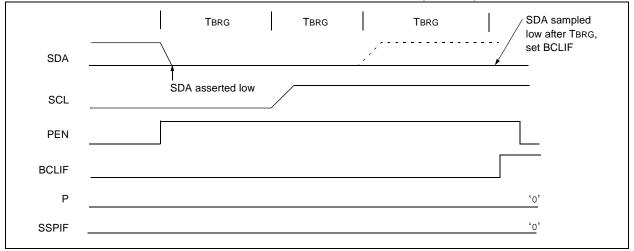

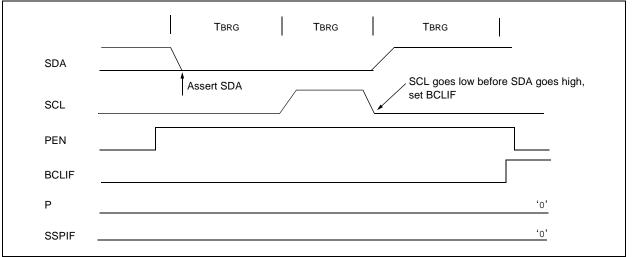

#### 10.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 10-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 10-32).

### FIGURE 10-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 10-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

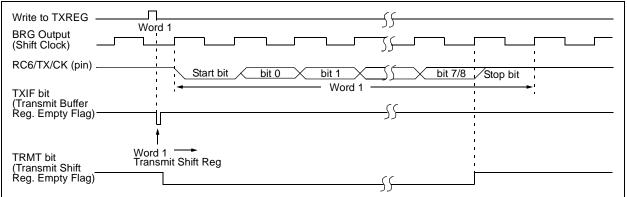

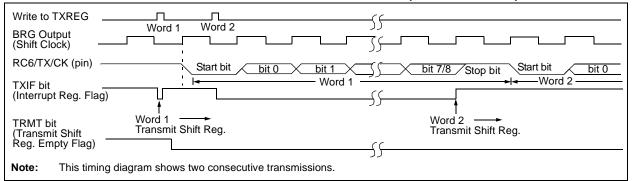

When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (see Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### FIGURE 11-2: ASYNCHRONOUS MASTER TRANSMISSION

#### TABLE 11-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6                                                | Bit 5     | Bit 4  | Bit 3 | Bit 2  | Bit 1     | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|------------------------------------------------------|-----------|--------|-------|--------|-----------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                                 | TMR0IE    | INTOIE | RBIE  | TMR0IF | INTOIF    | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                 | RCIF      | TXIF   | SSPIF | CCP1IF | TMR2IF    | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                                                  | SREN      | CREN   | ADDEN | FERR   | OERR      | RX9D   | 0000 000x             | 0000 000x                       |

| 19h                    | TXREG  | AUSART -             | Transmit                                             | Data Regi | ister  |       |        |           |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                 | RCIE      | TXIE   | SSPIE | CCP1IE | TMR2IE    | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                                                  | TXEN      | SYNC   | —     | BRGH   | TRMT      | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | aud Rate Generator Register 0000 0000 0000 0000 0000 |           |        |       |        | 0000 0000 |        |                       |                                 |

Legend: x = unknown, — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

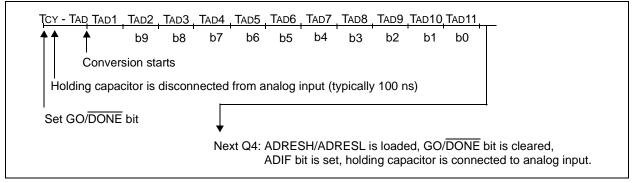

# 12.6 A/D Conversions

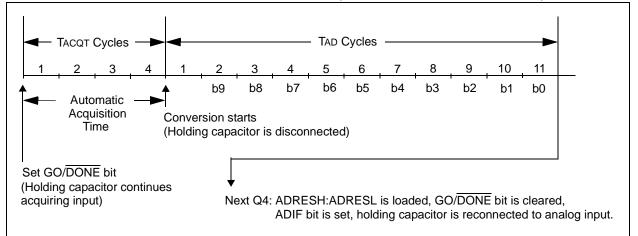

Figure 12-3 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 12-4 shows the operation of the A/D converter after the GO/DONE bit has been set, the ACQT2:ACQT0 bits are set to '010' and a 4 TAD acquisition time is selected before the conversion starts. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

### FIGURE 12-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 12-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

# 13.2 Comparator Operation

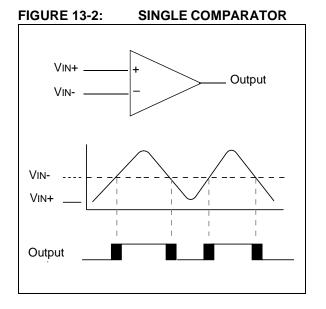

A single comparator is shown in Figure 13-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 13-2 represent the uncertainty due to input offsets and response time.

# 13.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 13-2).

### 13.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

## 13.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. **Section 14.0 "Comparator Voltage Reference Module"** contains a detailed description of the comparator voltage reference module that provides this signal. The internal reference signal is used when comparators are in mode CM<2:0> = 110 (Figure 13-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

# 13.4 Comparator Response Time

Response time is the minimum time after selecting a new reference voltage, or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Section 18.0 "Electrical Characteristics").

# 13.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexors in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 13-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4:>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

- **3:** RA4 is an open collector I/O pin. When used as an output, a pull-up resistor is required.

# PIC16F7X7

| REGIST            | FER 1                                                                                                                           | R 15-2: CONFIGURATION WORD REGISTER 2 (ADDRESS 2008h)                                                                                                   |       |     |       |           |        |           |           |             |            |          |       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----------|--------|-----------|-----------|-------------|------------|----------|-------|

| U-1               | U-1                                                                                                                             | U-1                                                                                                                                                     | U-1   | U-1 | U-1   | U-1       | R/P-1  | U-1       | U-1       | U-1         | U-1        | R/P-1    | R/P-1 |

|                   | _                                                                                                                               | _                                                                                                                                                       | —     | —   | _     |           | BORSEN |           | —         | _           | —          | IESO     | FCMEN |

| bit 13            |                                                                                                                                 |                                                                                                                                                         |       |     |       |           |        |           |           |             |            |          | bit 0 |

| bit 13-7<br>bit 6 | BOR                                                                                                                             | Unimplemented: Read as '1'<br>BORSEN: Brown-out Reset Software Enable bit<br>Refer to Configuration Word Register 1, bit 6 for the function of this bit |       |     |       |           |        |           |           |             |            |          |       |

| bit 5-2           | Refer to Configuration Word Register 1, bit 6 for the function of this bit.<br><b>Unimplemented:</b> Read as '1'                |                                                                                                                                                         |       |     |       |           |        |           |           |             |            |          |       |

| bit 1             | 1 = lr                                                                                                                          | IESO: Internal External Switchover bit<br>1 = Internal External Switchover mode enabled<br>0 = Internal External Switchover mode disabled               |       |     |       |           |        |           |           |             |            |          |       |

| bit 0             | <b>FCMEN:</b> Fail-Safe Clock Monitor Enable bit<br>1 = Fail-Safe Clock Monitor enabled<br>0 = Fail-Safe Clock Monitor disabled |                                                                                                                                                         |       |     |       |           |        |           |           |             |            |          |       |

|                   | Lege                                                                                                                            | end:                                                                                                                                                    |       |     |       |           |        |           |           |             |            |          |       |

|                   | R = I                                                                                                                           | Readabl                                                                                                                                                 | e bit |     | W = 1 | Writable  | e bit  | U = Uni   | mpleme    | nted bit, i | read as '  | 0'       |       |

|                   | -n =                                                                                                                            | Value at                                                                                                                                                | POR   |     | '1' = | Bit is se | t      | '0' = Bit | is cleare | ed          | x = Bit is | s unknov | vn    |

f,b

Bit 'b' in register 'f' is cleared.

# 16.2 Instruction Descriptions

ADDWF

Syntax: Operands:

| ADDLW            | Add Literal and W                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                  |

| Operands:        | $0 \le k \le 255$                                                                                                         |

| Operation:       | $(W) + k \to (W)$                                                                                                         |

| Status Affected: | C, DC, Z                                                                                                                  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k<br>and the result is placed in the W<br>register. |

| are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. | Description:                           |

|------------------------------------------------------------------------------------------|----------------------------------------|

| Add W and f                                                                              | BSF                                    |

| [label] ADDWF f,d                                                                        | Syntax:                                |

| $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                          | Operands:                              |

| (W) + (f) $\rightarrow$ (destination)                                                    | Operation:                             |

|                                                                                          | 0, , , , , , , , , , , , , , , , , , , |

BCF

Syntax:

Operands:

Operation:

Status Affected:

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

Bit Clear f

[ label ] BCF

$\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$

$0 \rightarrow (f < b >)$

None

| ANDLW            | AND Literal with W                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                            |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                          |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

# 18.2 DC Characteristics: Power-Down and Supply Current PIC16F737/747/767/777 (Industrial, Extended) PIC16LF737/747/767/777 (Industrial) (Continued)

|              | 7 <b>37/747/767/777</b><br>strial)         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |        |            |                                |  |  |

|--------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|------------|--------------------------------|--|--|

|              | <b>37/747/767/777</b><br>strial, Extended) |                                                                                                                                    |     |       |        |            | ial                            |  |  |

| Param<br>No. | Device                                     | Тур                                                                                                                                | Max | Units |        | Conditions |                                |  |  |

|              | Supply Current (IDD) <sup>(2,3)</sup>      |                                                                                                                                    |     |       |        |            |                                |  |  |

|              | PIC16LF7X7                                 | 9                                                                                                                                  | 20  | μΑ    | -40°C  |            |                                |  |  |

|              |                                            | 7                                                                                                                                  | 15  | μΑ    | +25°C  | VDD = 2.0V |                                |  |  |

|              |                                            | 7                                                                                                                                  | 15  | μΑ    | +85°C  |            |                                |  |  |

|              | PIC16LF7X7                                 | 16                                                                                                                                 | 30  | μA    | -40°C  |            |                                |  |  |