Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f737-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device specific information about the following devices:

- PIC16F737 PIC16F767

- PIC16F747 PIC16F777

PIC16F737/767 devices are available only in 28-pin packages, while PIC16F747/777 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X7 family share common architecture with the following differences:

- The PIC16F737 and PIC16F767 have one-half of the total on-chip memory of the PIC16F747 and PIC16F777.

- The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5.

- The 28-pin devices have 16 interrupts, while the 40/44-pin devices have 17.

- The 28-pin devices have 11 A/D input channels, while the 40/44-pin devices have 14.

- The Parallel Slave Port is implemented only on the 40/44-pin devices.

- Low-Power modes: RC\_RUN allows the core and peripherals to be clocked from the INTRC, while SEC\_RUN allows the core and peripherals to be clocked from the low-power Timer1. Refer to Section 4.7 "Power-Managed Modes" for further details.

- Internal RC oscillator with eight selectable frequencies, including 31.25 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz and 8 MHz. The INTRC can be configured as a primary or secondary clock source. Refer to Section 4.5 "Internal Oscillator Block" for further details.

- The Timer1 module current consumption has been greatly reduced from 20 μA (previous PIC16 devices) to 1.8 μA typical (32 kHz at 2V), which is ideal for real-time clock applications. Refer to Section 7.0 "Timer1 Module" for further details.

- Extended Watchdog Timer (WDT) that can have a programmable period from 1 ms to 268s. The WDT has its own 16-bit prescaler. Refer to **Section 15.17** "Watchdog Timer (WDT)" for further details.

- Two-Speed Start-up: When the oscillator is configured for LP, XT or HS, this feature will clock the device from the INTRC while the oscillator is warming up. This, in turn, will enable almost immediate code execution. Refer to Section 15.17.3 "Two-Speed Clock Start-up Mode" for further details.

- Fail-Safe Clock Monitor: This feature will allow the device to continue operation if the primary or secondary clock source fails by switching over to the INTRC.

The available features are summarized in Table 1-1. Block diagrams of the PIC16F737/767 and PIC16F747/777 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional information may be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023) which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| Key Features                        | PIC16F737                                               | PIC16F747                                | PIC16F767                                               | PIC16F777                                |

|-------------------------------------|---------------------------------------------------------|------------------------------------------|---------------------------------------------------------|------------------------------------------|

| Operating Frequency                 | DC – 20 MHz                                             | DC – 20 MHz                              | DC – 20 MHz                                             | DC – 20 MHz                              |

| Resets (and Delays)                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                  | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                  |

| Flash Program Memory (14-bit words) | 4K                                                      | 4K                                       | 8K                                                      | 8K                                       |

| Data Memory (bytes)                 | 368                                                     | 368                                      | 368                                                     | 368                                      |

| Interrupts                          | 16                                                      | 17                                       | 16                                                      | 17                                       |

| I/O Ports                           | Ports A, B, C                                           | Ports A, B, C, D, E                      | Ports A, B, C                                           | Ports A, B, C, D, E                      |

| Timers                              | 3                                                       | 3                                        | 3                                                       | 3                                        |

| Capture/Compare/PWM Modules         | 3                                                       | 3                                        | 3                                                       | 3                                        |

| Master Serial Communications        | MSSP, AUSART                                            | MSSP, AUSART                             | MSSP, AUSART                                            | MSSP, AUSART                             |

| Parallel Communications             | —                                                       | PSP                                      | —                                                       | PSP                                      |

| 10-bit Analog-to-Digital Module     | 11 Input Channels                                       | 14 Input Channels                        | 11 Input Channels                                       | 14 Input Channels                        |

| Instruction Set                     | 35 Instructions                                         | 35 Instructions                          | 35 Instructions                                         | 35 Instructions                          |

| Packaging                           | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP |

### TABLE 1-1: PIC16F7X7 DEVICE FEATURES

| Pin Name                        | PDIP<br>Pin # | QFN<br>Pin # | TQFP<br>Pin # | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                        |

|---------------------------------|---------------|--------------|---------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI/RA7<br>OSC1           | 13            | 32           | 30            | I             | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input<br>ST buffer when configured in RC mode; otherwise<br>CMOS. |

| CLKI                            |               |              |               | Ι             |                        | External clock source input. Always associated with<br>pin function OSC1 (see OSC1/CLKI, OSC2/CLKO<br>pins).                                                       |

| RA7                             |               |              |               | I/O           | ST                     | Bidirectional I/O pin.                                                                                                                                             |

| OSC2/CLKO/RA6<br>OSC2           | 14            | 33           | 31            | 0             | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode.                                  |

| CLKO                            |               |              |               | 0             | 07                     | In RC mode, OSC2 pin outputs CLKO which has<br>1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                |

| RA6                             |               |              |               | I/O           | ST                     | Bidirectional I/O pin.                                                                                                                                             |

| MCLR/VPP/RE3<br>MCLR            | 1             | 18           | 18            | I             | ST                     | Master Clear (input) or programming voltage (output).<br>Master Clear (Reset) input. This pin is an<br>active-low Reset to the device.                             |

| Vpp<br>RE3                      |               |              |               | P<br>I        | ST                     | Programming voltage input.<br>Digital input only pin.                                                                                                              |

|                                 |               |              |               |               |                        | PORTA is a bidirectional I/O port.                                                                                                                                 |

| RA0/AN0<br>RA0                  | 2             | 19           | 19            | I/O           | TTL                    | Digital I/O.                                                                                                                                                       |

| AN0<br>RA1/AN1                  | 3             | 20           | 20            | I             | TTL                    | Analog input 0.                                                                                                                                                    |

| RA1<br>AN1                      | 5             | 20           | 20            | I/O<br>I      |                        | Digital I/O.<br>Analog input 1.                                                                                                                                    |

| RA2/AN2/VREF-/CVREF             | 4             | 21           | 21            |               | TTL                    |                                                                                                                                                                    |

| RA2<br>AN2                      |               |              |               | 1/O<br>1      |                        | Digital I/O.<br>Analog input 2.                                                                                                                                    |

| VREF-<br>CVREF                  |               |              |               | <br>          |                        | A/D reference voltage input (low).<br>Comparator voltage reference output.                                                                                         |

| RA3/AN3/VREF+                   | 5             | 22           | 22            |               | TTL                    |                                                                                                                                                                    |

| RA3                             | -             |              |               | I/O           |                        | Digital I/O.                                                                                                                                                       |

| AN3                             |               |              |               | 1             |                        | Analog input 3.                                                                                                                                                    |

| VREF+                           | 6             | 00           | 00            | I             | OT                     | A/D reference voltage input (high).                                                                                                                                |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI | 6             | 23           | 23            | I/O<br>I      | ST                     | Digital I/O – Open-drain when configured as outpu<br>Timer0 external clock input.                                                                                  |

| C1OUT                           |               |              |               | 0             |                        | Comparator 1 output.                                                                                                                                               |

| RA5/AN4/LVDIN/SS/C2OUT<br>RA5   | 7             | 24           | 24            | I/O           | TTL                    | Digital I/O.                                                                                                                                                       |

| AN4                             |               |              |               | T             |                        | Analog input 4.                                                                                                                                                    |

|                                 |               |              |               | 1             |                        | Low-Voltage Detect input.                                                                                                                                          |

| SS<br>C2OUT                     |               |              |               |               |                        | SPI slave select input.<br>Comparator 2 output.                                                                                                                    |

| Legend: I = input               | 1             | 0 = ou       | itout         |               | I/O = inpu             | tt/output P = power                                                                                                                                                |

| TABLE 1-3: | PIC16F747 AND PIC16F777 PINOUT DESCRIPTION |

|------------|--------------------------------------------|

| IADLE 1-3. | PICTOF/4/ AND PICTOF/// PINOUT DESCRIPTION |

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as a general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

5: Pin location of CCP2 is determined by the CCPMX bit in Configuration Word Register 1.

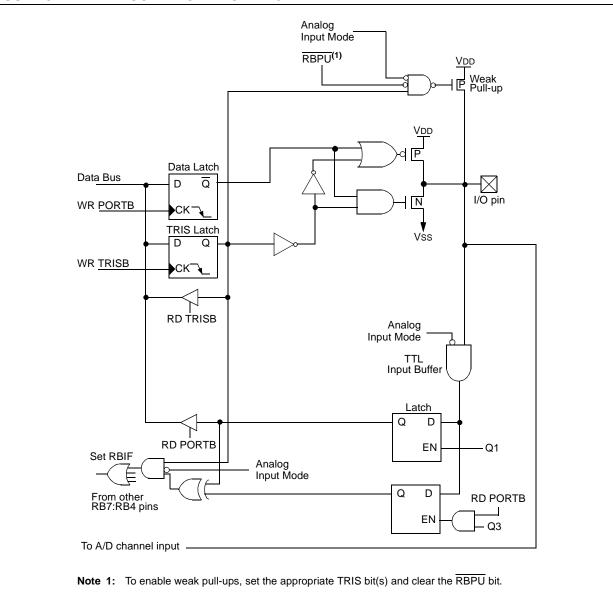

### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register also known as the prescaler), the external INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

### **REGISTER 2-2: OPTION\_REG: OPTION CONTROL REGISTER (ADDRESS 81h, 181h)**

|        | R/W-1            | R/W-1                                                                          | R/W-1         | R/W-1         | R/W-1         | R/W-1     | R/W-1                                  | R/W-1 |  |  |

|--------|------------------|--------------------------------------------------------------------------------|---------------|---------------|---------------|-----------|----------------------------------------|-------|--|--|

|        | RBPU             | INTEDG                                                                         | TOCS          | TOSE          | PSA           | PS2       | PS1                                    | PS0   |  |  |

|        | bit 7            |                                                                                |               |               |               |           |                                        | bit   |  |  |

| oit 7  | <b>RBPU</b> : PO | RTB Pull-up E                                                                  | Enable bit    |               |               |           |                                        |       |  |  |

|        |                  | 3 pull-ups are<br>3 pull-ups are                                               |               | individual po | rt latch valu | es        |                                        |       |  |  |

| it 6   | INTEDG: Ir       | nterrupt Edge                                                                  | Select bit    | -             |               |           |                                        |       |  |  |

|        |                  | ot on rising ed<br>ot on falling ed                                            | 0             |               |               |           |                                        |       |  |  |

| oit 5  |                  | R0 Clock Sour                                                                  |               | it            |               |           |                                        |       |  |  |

|        |                  | 1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKO) |               |               |               |           |                                        |       |  |  |

| oit 4  |                  | R0 Source Ed                                                                   | -             |               |               |           |                                        |       |  |  |

|        |                  | ent on high-to<br>ent on low-to-                                               |               |               |               |           |                                        |       |  |  |

| it 3   | PSA: Pres        | caler Assignm                                                                  | ent bit       |               |               |           |                                        |       |  |  |

|        |                  | ler is assigned<br>ler is assigned                                             |               |               |               |           |                                        |       |  |  |

| it 2-0 | PS2:PS0:         | Prescaler Rate                                                                 | e Select bits | 5             |               |           |                                        |       |  |  |

|        | Bit Va           | alue TMR0 I                                                                    | Rate WDT      | Rate          |               |           |                                        |       |  |  |

|        | 0 0<br>0 0       | 1.4                                                                            | 1:1           |               |               |           |                                        |       |  |  |

|        | 00               |                                                                                | 1:4           |               |               |           |                                        |       |  |  |

|        | 01               |                                                                                |               |               |               |           |                                        |       |  |  |

|        | 10<br>10         | 1.01                                                                           |               | -             |               |           |                                        |       |  |  |

|        | 11               |                                                                                | 28 1:6        | 64            |               |           |                                        |       |  |  |

|        | 11               | 1 1:25                                                                         | 56   1:1      | 28            |               |           |                                        |       |  |  |

|        | Legend:          |                                                                                |               |               |               |           |                                        |       |  |  |

|        | R = Reada        | able bit                                                                       | W = Wr        | ritable bit   | U = Unimp     | olemented | bit, read as                           | '0'   |  |  |

|        | -n = Value       | at POR                                                                         | '1' = Bit     | is set        | '0' = Bit is  | cleared   | 0' = Bit is cleared x = Bit is unknown |       |  |  |

### 4.6.3 CLOCK TRANSITION AND WDT

When clock switching is performed, the Watchdog Timer is disabled because the Watchdog Ripple Counter is used as the Oscillator Start-up Timer (OST).

Note: The OST is only used when switching to XT, HS and LP Oscillator modes.

Once the clock transition is complete (i.e., new oscillator selection switch has occurred), the Watchdog Counter is re-enabled with the Counter Reset. This allows the user to synchronize the Watchdog Timer to the start of execution at the new clock frequency.

### REGISTER 4-2: OSCCON: OSCILLATOR CONTROL REGISTER (ADDRESS 8Fh)

| U-0   | R/W-0 | R/W-0 | R/W-0 | R-0                 | R-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|------|-------|-------|

| —     | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | IOFS | SCS1  | SCS0  |

| bit 7 |       |       |       |                     |      |       | bit 0 |

- bit 7 Unimplemented: Read as '0'

- bit 6-4 IRCF<2:0>: Internal RC Oscillator Frequency Select bits

- 000 = 31.25 kHz

- 001 = 125 kHz 010 = 250 kHz

- O11 = 500 kHz

- 100 = 1 MHz

- 101 = 2 MHz

- 110 = 4 MHz

- 111 = 8 MHz

bit 3 **OSTS:** Oscillator Start-up Time-out Status bit<sup>(1)</sup>

1 = Device is running from the primary system clock

- 0 = Device is running from the Timer1 oscillator (T1OSC) or INTRC as a secondary system clock

- Note 1: Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the oscillator mode.

- bit 2 IOFS: INTOSC Frequency Stable bit

- 1 = Frequency is stable

- 0 = Frequency is not stable

- bit 1-0 SCS<1:0>: Oscillator Mode Select bits

- 00 = Oscillator mode defined by FOSC<2:0>

- 01 = T1OSC is used for system clock

- 10 = Internal RC is used for system clock

- 11 = Reserved

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| <b>REGISTER 7-1:</b> | T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)                                                                              |                                |                                |                                 |                 |             |              |        |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|---------------------------------|-----------------|-------------|--------------|--------|--|

|                      | U-0                                                                                                                       | R-0                            | R/W-0                          | R/W-0                           | R/W-0           | R/W-0       | R/W-0        | R/W-0  |  |

|                      | _                                                                                                                         | T1RUN                          | T1CKPS1                        | T1CKPS0                         | T1OSCEN         | T1SYNC      | TMR1CS       | TMR10N |  |

|                      | bit 7                                                                                                                     |                                |                                |                                 |                 |             |              | bit 0  |  |

|                      |                                                                                                                           |                                |                                |                                 |                 |             |              |        |  |

| bit 7                | -                                                                                                                         | nented: Rea                    |                                |                                 |                 |             |              |        |  |

| bit 6                |                                                                                                                           | •                              | m Clock Sta                    |                                 | 4               |             |              |        |  |

|                      | •                                                                                                                         |                                |                                | Fimer1 oscilla<br>another sourc |                 |             |              |        |  |

| bit 5-4              | -                                                                                                                         |                                |                                | k Prescale Se                   |                 |             |              |        |  |

|                      | -                                                                                                                         | Prescale valu                  |                                |                                 |                 |             |              |        |  |

|                      |                                                                                                                           | Prescale valu                  |                                |                                 |                 |             |              |        |  |

|                      |                                                                                                                           | Prescale valu<br>Prescale valu |                                |                                 |                 |             |              |        |  |

| bit 3                | T1OSCEN                                                                                                                   | I: Timer1 Os                   | scillator Enal                 | ble Control bi                  | t               |             |              |        |  |

|                      | 1 = Oscilla                                                                                                               | ator is enabl                  | ed                             |                                 |                 |             |              |        |  |

|                      | 0 = Oscilla                                                                                                               | ator is shut-o                 | off (the oscill                | ator inverter i                 | s turned off to | o eliminate | power drain  | )      |  |

| bit 2                |                                                                                                                           |                                | ernal Clock I                  | nput Synchro                    | nization Cont   | rol bit     |              |        |  |

|                      | TMR1CS                                                                                                                    |                                |                                | I. S                            |                 |             |              |        |  |

|                      |                                                                                                                           | •                              | e external cl<br>nal clock inp |                                 |                 |             |              |        |  |

|                      | TMR1CS                                                                                                                    |                                |                                |                                 |                 |             |              |        |  |

|                      | This bit is                                                                                                               | ignored. Tin                   | ner1 uses the                  | e internal clo                  | ck when TMR     | 1CS = 0.    |              |        |  |

| bit 1                | TMR1CS:                                                                                                                   | Timer1 Clo                     | ck Source S                    | elect bit                       |                 |             |              |        |  |

|                      | <ul> <li>1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge)</li> <li>0 = Internal clock (Fosc/4)</li> </ul> |                                |                                |                                 |                 |             |              |        |  |

| bit 0                | TMR1ON:                                                                                                                   | Timer1 On                      | bit                            |                                 |                 |             |              |        |  |

|                      | 1 = Enables Timer1<br>0 = Stops Timer1                                                                                    |                                |                                |                                 |                 |             |              |        |  |

|                      | Logond                                                                                                                    |                                |                                |                                 |                 |             |              |        |  |

|                      | Legend:<br>R = Read                                                                                                       | labla bit                      | \\/ _                          | Writable bit                    | 11 - 1 Inim     | plomontod   | hit road oo  | ·0'    |  |

|                      | R = Read                                                                                                                  |                                | vv =                           | winable bil                     | 0 = 0           | piemented   | bit, read as | 0      |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

### 7.9 Resetting Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

### 7.10 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

### 7.11 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 7.6** "**Timer1 Oscillator**") gives users the option to include RTC functionality in their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 7-3, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

| RTCinit | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF<br>MOVLW<br>MOVWF<br>CLRF<br>CLRF<br>MOVLW<br>MOVWF | TMR1H<br>0x80<br>TMR1H<br>TMR1L<br>b'00001111'<br>T1CON<br>secs<br>mins<br>.12<br>hours | ; Preload TMR1 register pair<br>; for 1 second overflow<br>; Configure for external clock,<br>; Asynchronous operation, external oscillator<br>; Initialize timekeeping registers |

|---------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | BANKSEL<br>BSF                                                                        | PIE1<br>PIE1, TMR1IE                                                                    | ; Enable Timer1 interrupt                                                                                                                                                         |

| RTCisr  | RETURN<br>BANKSEL                                                                     | TMR1H                                                                                   |                                                                                                                                                                                   |

|         | BSF                                                                                   | TMR1H, 7                                                                                | ; Preload for 1 sec overflow                                                                                                                                                      |

|         | BCF                                                                                   | PIR1, TMR1IF                                                                            | ; Clear interrupt flag                                                                                                                                                            |

|         | INCF                                                                                  | secs, F                                                                                 | ; Increment seconds                                                                                                                                                               |

|         | MOVF                                                                                  | secs, w                                                                                 |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .60                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 60 seconds elapsed?                                                                                                                                                             |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | seconds                                                                                 | ; Clear seconds                                                                                                                                                                   |

|         | INCF                                                                                  | mins, f                                                                                 | ; Increment minutes                                                                                                                                                               |

|         | MOVF                                                                                  | mins, w                                                                                 |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .60                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 60 seconds elapsed?                                                                                                                                                             |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | mins                                                                                    | ; Clear minutes                                                                                                                                                                   |

|         | INCF                                                                                  | hours, f                                                                                | ; Increment hours                                                                                                                                                                 |

|         | MOVF                                                                                  | hours, w                                                                                |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .24                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 24 hours elapsed?                                                                                                                                                               |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | hours                                                                                   | ; Clear hours                                                                                                                                                                     |

|         | RETURN                                                                                |                                                                                         | ; Done                                                                                                                                                                            |

EXAMPLE 7-3: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

## 9.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

The CCP1, CCP2 and CCP3 modules are identical in operation, with the exception being the operation of the special event trigger. Table 9-1 and Table 9-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 and CCP3 operate the same as CCP1, except where noted.

### 9.1 CCP1 Module

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will clear both TMR1H and TMR1L registers.

### 9.2 CCP2 Module

Capture/Compare/PWM Register 2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match; it will clear both TMR1H and TMR1L registers and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023) and in Application Note *AN594 "Using the CCP Module*(s)" (DS00594).

### 9.3 CCP3 Module

Capture/Compare/PWM Register 3 (CCPR3) is comprised of two 8-bit registers: CCPR3L (low byte) and CCPR3H (high byte). The CCP3CON register controls the operation of CCP3.

### TABLE 9-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### TABLE 9-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                                              |

|-----------|-----------|----------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time base.                                                                                     |

| Capture   | Compare   | Same TMR1 time base.                                                                                     |

| Compare   | Compare   | Same TMR1 time base.                                                                                     |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).<br>The rising edges are aligned. |

| PWM       | Capture   | None.                                                                                                    |

| PWM       | Compare   | None.                                                                                                    |

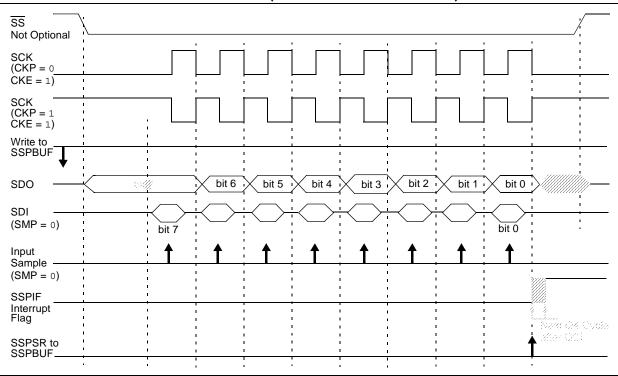

# FIGURE 10-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0) Image: Spin mode waveform (slave mode with cke = 0) Image: Spin mode waveform (slave mode with cke = 0) Image: Spin mode waveform (slave mode with cke = 0) Image: Spin mode waveform (slave mode with cke = 0) Image: Spin mode waveform (slave mode with cke = 0) Image: Spin mode waveform (slave mode with cke = 0) Image: Spin mode waveform (slave mode with cke = 0) Image: Spin mode waveform (slave mode waveform (slaveform (slaveform

### FIGURE 10-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

### 10.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit, during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 10-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, The BF flag Is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

### 10.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

### 10.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

### 10.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

### 10.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

### 10.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

### 10.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

### 10.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

## 11.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is one of the two serial I/O modules. (AUSART is also known as a Serial Communications Interface or SCI.) The AUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The AUSART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The AUSART module also has a multi-processor communication capability using 9-bit address detection.

### **REGISTER 11-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)**

|       | R/W-0                                                                      | R/W-0       | R/W-0         | R/W-0         | U-0         | R/W-0     | ,<br>R-1      | R/W-0                                                                            |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------|-------------|---------------|---------------|-------------|-----------|---------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | CSRC                                                                       | TX9         | TXEN          | SYNC          | _           | BRGH      | TRMT          | TX9D                                                                             |  |  |  |  |  |  |  |  |  |

|       | bit 7                                                                      |             |               |               |             |           |               | bit 0                                                                            |  |  |  |  |  |  |  |  |  |

|       |                                                                            |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 7 | CSRC: Clock<br>Asynchronou                                                 |             | elect bit     |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | Don't care.                                                                |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | Synchronous mode:<br>1 = Master mode (clock generated internally from BRG) |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | 0 = Slave mo                                                               |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 6 | <b>TX9</b> : 9-bit Tr                                                      | ansmit Enal | ole bit       |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | 1 = Selects<br>0 = Selects                                                 |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 5 | TXEN: Trans                                                                | mit Enable  | bit           |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | 1 = Transmit<br>0 = Transmit                                               |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | Note: S                                                                    | BREN/CREM   | V overrides   | TXEN in Syı   | nc mode.    |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 4 | SYNC: AUS                                                                  | ART Mode S  | Select bit    |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | 1 = Synchron<br>0 = Asynchron                                              |             | )             |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 3 | Unimpleme                                                                  | nted: Read  | <b>as</b> '0' |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 2 | BRGH: High                                                                 | Baud Rate   | Select bit    |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | Asynchronou                                                                |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | 1 = High spe<br>0 = Low spe                                                |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | Synchronous                                                                |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | Unused in th                                                               |             |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 1 | TRMT: Trans                                                                |             | egister Statu | s bit         |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | 1 = TSR emp<br>0 = TSR full                                                | oty         |               |               |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 0 | TX9D: 9th bi                                                               | t of Transm | it Data, can  | be Parity bit |             |           |               |                                                                                  |  |  |  |  |  |  |  |  |  |

|       | Legend:                                                                    |             |               |               |             |           |               | ]                                                                                |  |  |  |  |  |  |  |  |  |

|       | R = Readabl                                                                | e hit       | M = M r       | itable bit    | U = Unimple | amented h | it read as 'C | ,                                                                                |  |  |  |  |  |  |  |  |  |

|       | -n = Value at                                                              |             |               |               | •           |           | x = Bit is un |                                                                                  |  |  |  |  |  |  |  |  |  |

|       |                                                                            |             | -             |               |             |           |               | -n = Value at POR $(1' = Bit is set)$ $(0' = Bit is cleared)$ x = Bit is unknown |  |  |  |  |  |  |  |  |  |

| CP C       | CCPMX DEBUG BORV1 BORV0 BOREN MCLRE FOSC2 PWRTEN WDTEN FOSC                                                                                                                             | 1 FOSCO   |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|

| bit 13     |                                                                                                                                                                                         | bit 0     |  |  |  |  |  |  |

| L:140      | OD Flack December Measure Octob Dectedies bits                                                                                                                                          |           |  |  |  |  |  |  |

| bit 13     | <b>CP:</b> Flash Program Memory Code Protection bits                                                                                                                                    |           |  |  |  |  |  |  |

|            | <ul> <li>1 = Code protection off</li> <li>0 = 0000h to 1FFFh code-protected for PIC16F767/777 and 0000h to 0FFFh for PIC16F737/747 (all</li> </ul>                                      | protected |  |  |  |  |  |  |

| bit 12     | CCPMX: CCP2 Multiplex bit                                                                                                                                                               |           |  |  |  |  |  |  |

|            | 1 = CCP2 is on RC1                                                                                                                                                                      |           |  |  |  |  |  |  |

|            | 0 = CCP2 is on RB3                                                                                                                                                                      |           |  |  |  |  |  |  |

| bit 11     | DEBUG: In-Circuit Debugger Mode bit                                                                                                                                                     |           |  |  |  |  |  |  |

|            | <ul> <li>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> </ul>      |           |  |  |  |  |  |  |

| bit 10-9   | 9 Unimplemented: Read as '1'                                                                                                                                                            |           |  |  |  |  |  |  |

| bit 8-7    | BORV<1:0>: Brown-out Reset Voltage bits                                                                                                                                                 |           |  |  |  |  |  |  |

|            | 11 = VBOR set to 2.0V                                                                                                                                                                   |           |  |  |  |  |  |  |

|            | 10 = VBOR set to 2.7V<br>01 = VBOR set to 4.2V                                                                                                                                          |           |  |  |  |  |  |  |

|            | 01 = VBOR set to  4.2V $00 = VBOR set to  4.5V$                                                                                                                                         |           |  |  |  |  |  |  |

| bit 6      | BOREN: Brown-out Reset Enable bit                                                                                                                                                       |           |  |  |  |  |  |  |

|            | BOREN combines with BORSEN to control when BOR is enabled and how it is controlled.                                                                                                     |           |  |  |  |  |  |  |

|            | BOREN:BORSEN:                                                                                                                                                                           |           |  |  |  |  |  |  |

|            | 11 = BOR enabled and always on                                                                                                                                                          |           |  |  |  |  |  |  |

|            | <ul> <li>10 = BOR enabled during operation and disabled during Sleep by hardware</li> <li>01 = BOR controlled by software bit SBOREN – refer to Register 2-8 (PCON&lt;2&gt;)</li> </ul> |           |  |  |  |  |  |  |

|            | 00 = BOR disabled                                                                                                                                                                       |           |  |  |  |  |  |  |

| bit 5      | MCLRE: MCLR/VPP/RE3 Pin Function Select bit                                                                                                                                             |           |  |  |  |  |  |  |

|            | 1 = MCLR/VPP/RE3 pin function is MCLR                                                                                                                                                   |           |  |  |  |  |  |  |

|            | 0 = MCLR/VPP/RE3 pin function is digital input only, MCLR gated to '1'                                                                                                                  |           |  |  |  |  |  |  |

| bit 3      | PWRTEN: Power-up Timer Enable bit                                                                                                                                                       |           |  |  |  |  |  |  |

|            | 1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                   |           |  |  |  |  |  |  |

| bit 2      | WDTEN: Watchdog Timer Enable bit                                                                                                                                                        |           |  |  |  |  |  |  |

|            | 1 = WDT enabled                                                                                                                                                                         |           |  |  |  |  |  |  |

|            | 0 = WDT disabled                                                                                                                                                                        |           |  |  |  |  |  |  |

| bit 4, 1-0 | -0 FOSC2:FOSC0: Oscillator Selection bits                                                                                                                                               |           |  |  |  |  |  |  |

|            | 111 = EXTRC oscillator; CLKO function on OSC2/CLKO/RA6                                                                                                                                  |           |  |  |  |  |  |  |

|            | 110 = EXTRC oscillator; port I/O function on OSC2/CLKO/RA6<br>101 = INTRC oscillator; CLKO function on OSC2/CLKO/RA6 and port I/O function on OSC1/CLKI/RA7                             |           |  |  |  |  |  |  |

|            | 101 = INTRC oscillator; port I/O function on OSC1/CLKI/RA7 and OSC2/CLKO/RA6                                                                                                            |           |  |  |  |  |  |  |

|            | 011 = EXTCLK; port I/O function on OSC2/CLKO/RA6                                                                                                                                        |           |  |  |  |  |  |  |

|            | 010 = HS oscillator<br>001 = XT oscillator                                                                                                                                              |           |  |  |  |  |  |  |

|            | 000 = LP oscillator                                                                                                                                                                     |           |  |  |  |  |  |  |

|            | Legend:                                                                                                                                                                                 |           |  |  |  |  |  |  |

|            | сусни.                                                                                                                                                                                  |           |  |  |  |  |  |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

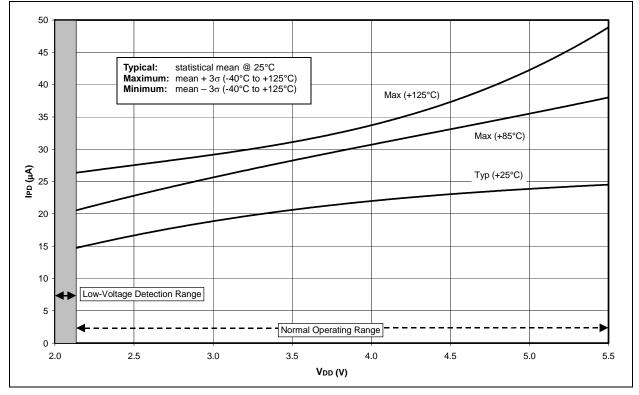

### 15.9 Control Register

The Low-Voltage Detect Control register controls the operation of the Low-Voltage Detect circuitry.

### REGISTER 15-3: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER (ADDRESS 109h)

|         |                                                                                                         |                            |               |               |              | •           |       | ,     |  |

|---------|---------------------------------------------------------------------------------------------------------|----------------------------|---------------|---------------|--------------|-------------|-------|-------|--|

|         | U-0                                                                                                     | U-0                        | R-0           | R/W-0         | R/W-0        | R/W-1       | R/W-0 | R/W-1 |  |

|         | —                                                                                                       | _                          | IRVST         | LVDEN         | LVDL3        | LVDL2       | LVDL1 | LVDL0 |  |

|         | bit 7                                                                                                   |                            |               |               |              |             |       | bit 0 |  |

|         |                                                                                                         |                            |               |               |              |             |       |       |  |

| bit 7-6 | Unimpleme                                                                                               | ented: Read                | <b>as</b> '0' |               |              |             |       |       |  |

| bit 5   | IRVST: Inte                                                                                             | rnal Referer               | nce Voltage   | Stable Flag b | oit          |             |       |       |  |

|         | voltage                                                                                                 | e range                    | C C           | Detect logic  | U U          |             |       | ·     |  |

|         | specifie                                                                                                | ed voltage ra              | ange and the  | e LVD interru | pt should no | t be enable | d     | U U   |  |

| bit 4   | LVDEN: Lo                                                                                               | w-Voltage D                | etect Power   | Enable bit    |              |             |       |       |  |

|         |                                                                                                         | s LVD, powe<br>s LVD, powe |               |               |              |             |       |       |  |

| bit 3-0 | LVDL3:LVDL0: Voltage Detection Limit bits                                                               |                            |               |               |              |             |       |       |  |

|         | <pre>1111 = External analog input is used (input comes from the LVDIN pin) 1110 = Maximum setting</pre> |                            |               |               |              |             |       |       |  |

|         | •                                                                                                       |                            |               |               |              |             |       |       |  |

|         | •                                                                                                       |                            |               |               |              |             |       |       |  |

|         | •<br>0001 = Minimum setting                                                                             |                            |               |               |              |             |       |       |  |