Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f737-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.0 OSCILLATOR CONFIGURATIONS

#### 4.1 Oscillator Types

The PIC16F7X7 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. RC External Resistor/Capacitor with FOSC/4 output on RA6

- 5. RCIO External Resistor/Capacitor with I/O on RA6

- 6. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 7. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 8. ECIO External Clock with I/O on RA6

#### 4.2 Crystal Oscillator/Ceramic Resonators

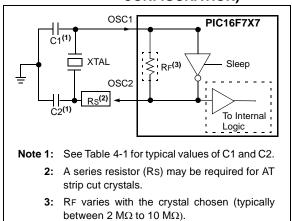

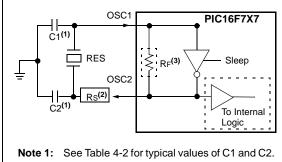

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F7X7 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

#### FIGURE 4-1: CRYSTAL OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 4-1:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR (FOR<br/>DESIGN GUIDANCE ONLY)

| Osc Type | Crystal | Typical Capacitor Values<br>Tested: |       |  |  |  |

|----------|---------|-------------------------------------|-------|--|--|--|

|          | Freq    | C1                                  | C2    |  |  |  |

| LP       | 32 kHz  | 33 pF                               | 33 pF |  |  |  |

|          | 200 kHz | 15 pF                               | 15 pF |  |  |  |

| XT       | 200 kHz | 56 pF                               | 56 pF |  |  |  |

|          | 1 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 4 MHz   | 15 pF                               | 15 pF |  |  |  |

| HS       | 4 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 8 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 20 MHz  | 15 pF                               | 15 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

#### FIGURE 4-2: CERAMIC RESONATOR OPERATION (HS OR XT OSC CONFIGURATION)

- **2:** A series resistor (Rs) may be required.

- 3: RF varies with the resonator chosen (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

#### TABLE 4-2: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| Typical Capacitor Values Used: |          |       |       |  |  |  |  |  |  |  |  |

|--------------------------------|----------|-------|-------|--|--|--|--|--|--|--|--|

| Mode Freq OSC1 OSC2            |          |       |       |  |  |  |  |  |  |  |  |

| XT                             | 455 kHz  | 56 pF | 56 pF |  |  |  |  |  |  |  |  |

|                                | 2.0 MHz  | 47 pF | 47 pF |  |  |  |  |  |  |  |  |

|                                | 4.0 MHz  | 33 pF | 33 pF |  |  |  |  |  |  |  |  |

| HS                             | 8.0 MHz  | 27 pF | 27 pF |  |  |  |  |  |  |  |  |

|                                | 16.0 MHz | 22 pF | 22 pF |  |  |  |  |  |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode rather than XT mode is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is 330Ω.

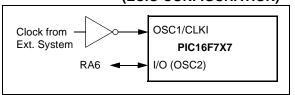

#### 4.3 External Clock Input

The ECIO Oscillator mode requires an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the ECIO Oscillator mode, the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 4-3 shows the pin connections for the ECIO Oscillator mode.

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

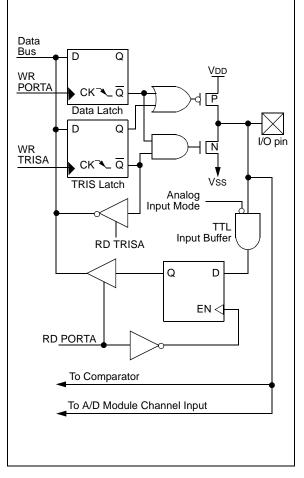

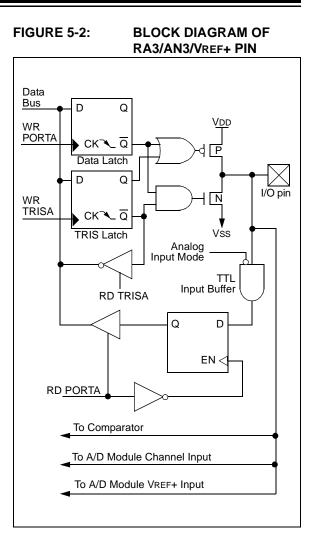

FIGURE 5-1: BLOCK DIAGRAM OF RA0/AN0:RA1/AN1 PINS

| Name          | Bit#  | Buffer                | Function                                                                                                                                                       |

|---------------|-------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT/AN12  | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up or analog input.                                                     |

| RB1/AN10      | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up or analog input.                                                                                 |

| RB2/AN8       | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up or analog input.                                                                                 |

| RB3/CCP2/AN9  | bit 3 | TTL                   | Input/output pin or Capture 2 input/Compare 2 output/PWM 2 output.<br>Internal software programmable weak pull-up or analog input.                             |

| RB4/AN11      | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up or analog input.                                                      |

| RB5/AN13/CCP3 | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up or analog input or Capture 2 input/<br>Compare 2 output/PWM 2 output. |

| RB6/PGC       | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                            |

| RB7/PGD       | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                             |

#### TABLE 5-3:PORTB FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6       | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------|------------|-------|-------------|------------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6         | RB5        | RB4   | RB3   | RB2   | RB1   | RB0   | xx00 0000             | uu00 0000                       |

| 86h, 186h | TRISB      | PORTB | Data Direct | ion Regist | er    |       |       |       |       | 1111 1111             | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG      | TOCS       | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

| 9Fh       | ADCON1     | ADFM  | ADCS2       | VCFG1      | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0000 0000             | 0000 0000                       |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### 6.3 Using Timer0 With an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 6.4 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that the prescaler cannot be used by the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 6-1). Note: Although the prescaler can be assigned to either the WDT or Timer0, but not both, a new divide counter is implemented in the WDT circuit to give multiple WDT time-out selections. This allows TMR0 and WDT to each have their own scaler. Refer to Section 15.17 "Watchdog Timer (WDT)" for further details.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### EXAMPLE 6-1: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0

| CLRWDT  |             | ; | Cl |

|---------|-------------|---|----|

| BANKSEL | OPTION_REG  | ; | Se |

| MOVLW   | b'xxxx0xxx' | ; | Se |

| MOVWF   | OPTION_REG  | ; | va |

|         |             |   |    |

- Clear WDT and prescaler Select Bank of OPTION\_REG Select TMR0, new prescale value and clock source

- TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|------------|----------|-----------|--------|--------|-------|--------|--------|-------|----------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 M | odule Reg | ister  |        |       |        |        |       | xxxx xxxx            | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE      | PEIE      | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 0000 000x            | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU     | INTEDG    | TOCS   | TOSE   | PSA   | PS2    | PS1    | PS0   | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

| REGISTER 9-1: | 9-1: CCPxCON: CCPx CONTROL REGISTER (ADDRESS 17h, 1Dh, 97h)                                                                                                                       |                                                                                                                                                           |                                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-------------------------------------------------|---------------|---------|--|--|--|--|

|               | U-0                                                                                                                                                                               | U-0                                                                                                                                                       | R/W-0                                                                                                                                           | R/W-0                                         | R/W-0                                        | R/W-0                                           | R/W-0         | R/W-0   |  |  |  |  |

|               | —                                                                                                                                                                                 | _                                                                                                                                                         | CCPxX                                                                                                                                           | CCPxY                                         | CCPxM3                                       | CCPxM2                                          | CCPxM1        | CCPxM0  |  |  |  |  |

|               | bit 7                                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                                 |                                               |                                              |                                                 |               | bit 0   |  |  |  |  |

| bit 7-6       | Unimplem                                                                                                                                                                          | ented: Rea                                                                                                                                                | <b>d as</b> '0'                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

| bit 5-4       | CCPxX:CC                                                                                                                                                                          | CCPxX:CCPxY: PWM Least Significant bits                                                                                                                   |                                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

|               | Capture mo                                                                                                                                                                        | Capture mode:                                                                                                                                             |                                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

|               | Unused.                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

|               | Compare m                                                                                                                                                                         | node:                                                                                                                                                     |                                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

|               | Unused.                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

|               | <u>PWM mode</u>                                                                                                                                                                   | _                                                                                                                                                         | I She of the                                                                                                                                    | PWM duty of                                   | vola Tha ai                                  | aht MShe a                                      | re found in ( |         |  |  |  |  |

| bit 3-0       |                                                                                                                                                                                   |                                                                                                                                                           | CPx Mode S                                                                                                                                      | •                                             |                                              | grit MODS al                                    |               |         |  |  |  |  |

|               | 0000 = Cap<br>0100 = Cap<br>0101 = Cap<br>0110 = Cap<br>0111 = Cap<br>1000 = Con<br>1001 = Con<br>1010 = Con<br>1010 = Con<br>1011 = Con<br>1011 = Con<br>CC<br>is e<br>11xx = PW | oture/Compa<br>oture mode,<br>oture mode,<br>oture mode,<br>oture mode,<br>mpare mode<br>mpare mode<br>affected)<br>mpare mode<br>P1 clears Ti<br>mabled) | are/PWM dis<br>every falling<br>every rising<br>every 4th ri<br>every 16th<br>e, set output<br>e, clear outp<br>e, generate s<br>e, trigger spe | sabled (rese<br>g edge<br>l edge<br>sing edge | CCPxIF bit is<br>(CCPxIF bit<br>errupt on ma | s set)<br>is set)<br>tch (CCPxIF<br>s set, CCPx | pin is unaffe | ected); |  |  |  |  |

|               | Legend:                                                                                                                                                                           |                                                                                                                                                           |                                                                                                                                                 |                                               |                                              |                                                 |               |         |  |  |  |  |

|               | R = Reada                                                                                                                                                                         | able bit                                                                                                                                                  | VV = V                                                                                                                                          | Vritable bit                                  | U = Unii                                     | mplemented                                      | bit, read as  | '0'     |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

#### 10.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 10-1: SSPSTAT: MSSP STATUS (SPI MODE) REGISTER (ADDRESS 94h)

|       | R/W-0                    | R/W-0           | R-0             | ,<br>R-0      | R-0         | 、<br>R-0      | ,<br>R-0     | R-0           |

|-------|--------------------------|-----------------|-----------------|---------------|-------------|---------------|--------------|---------------|

|       | SMP                      | CKE             | D/A             | к-0<br>Р      | R-0<br>S    | R-U<br>R/W    | UA           | BF            |

|       | bit 7                    | ORL             | DIA             | I             | 5           | 11/00         | 07           | bit 0         |

|       |                          |                 |                 |               |             |               |              | DILO          |

| bit 7 | SMP: Sam                 | ple bit         |                 |               |             |               |              |               |

|       | SPI Master               | •               |                 |               |             |               |              |               |

|       | 1 = Input d              | ata sampled     | at end of da    | ata output ti | me          |               |              |               |

|       | 0 = Input d              | ata sampled     | at middle o     | f data outpu  | it time     |               |              |               |

|       | SPI Slave                |                 |                 |               |             |               |              |               |

|       |                          | be cleared w    |                 | used in Slav  | /e mode.    |               |              |               |

| bit 6 | CKE: SPI (               | Clock Edge      | Select bit      |               |             |               |              |               |

|       |                          | nit occurs on   |                 |               |             |               |              |               |

|       | 0 = Iransm               | nit occurs on   |                 |               |             |               |              |               |

|       | Note:                    | Polarity of o   | clock state is  | s set by the  | CKP bit (SS | PCON1<4>      | ).           |               |

| bit 5 | D/A: Data/               | Address bit     |                 |               |             |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |               |             |               |              |               |

| bit 4 | P: Stop bit              |                 |                 |               |             |               |              |               |

|       | Used in I <sup>2</sup> C | mode only.      | This bit is cle | ared when t   | he MSSP m   | odule is disa | bled, SSPEN  | l is cleared. |

| bit 3 | S: Start bit             |                 |                 |               |             |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |               |             |               |              |               |

| bit 2 | R/W: Read                | I/Write bit Inf | ormation        |               |             |               |              |               |

|       | Used in I <sup>2</sup> C | c mode only.    |                 |               |             |               |              |               |

| bit 1 | UA: Update               | e Address bi    | it              |               |             |               |              |               |

|       |                          | c mode only.    |                 |               |             |               |              |               |

| bit 0 | BF: Buffer               | Full Status b   | oit (Receive    | mode only)    |             |               |              |               |

|       |                          | e complete,     | -               |               |             |               |              |               |

|       |                          | e not comple    |                 |               |             |               |              |               |

|       |                          |                 |                 |               |             |               |              |               |

|       | Legend:                  |                 |                 |               |             |               |              |               |

|       | R = Reada                | ble bit         | W = W           | ritable bit   | U = Unim    | plemented     | bit, read as | '0'           |

|       | -n = Value               | at POR          | '1' = Bi        | t is set      | '0' = Bit i | s cleared     | x = Bit is u | nknown        |

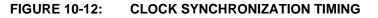

### 10.4.4.5 Clock Synchronization and the CKP Bit

When the CKP bit is cleared, the SCL output is forced to '0'; however, setting the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 10-12).

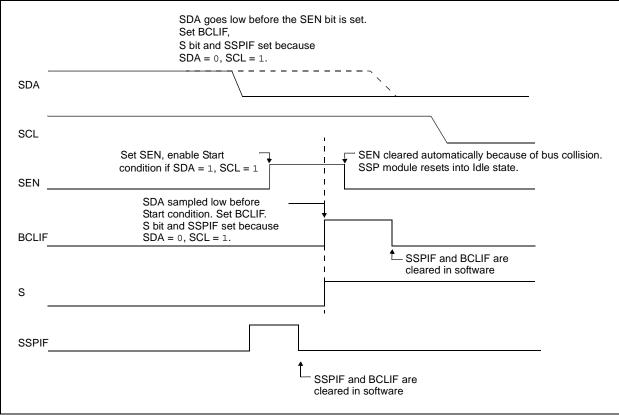

#### 10.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 10-26).

- b) SCL is sampled low before SDA is asserted low (Figure 10-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 10-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 10-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pin is sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 10-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

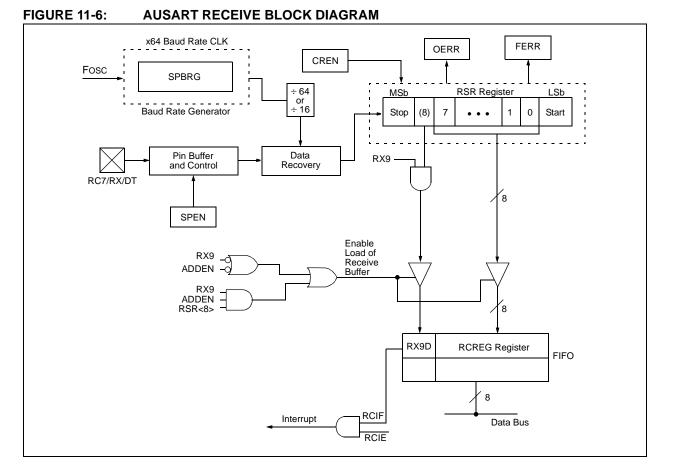

#### 11.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

#### 13.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 13.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Off mode, CM<2:0> = 111. This ensures compatibility to the PIC16F87X devices.

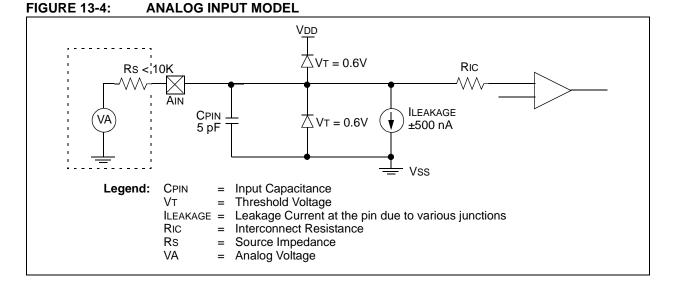

#### 13.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 13-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| TABLE 13-1: | <b>REGISTERS ASSOCIATED WITH COMPARATOR MODULE</b> |

|-------------|----------------------------------------------------|

|-------------|----------------------------------------------------|

| Address                | Name   | Bit 7   | Bit 6       | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|------------------------|--------|---------|-------------|-------------|--------|-------|--------|--------|--------|-----------------|---------------------------------|

| 9Ch                    | CMCON  | C2OUT   | C10UT       | C2INV       | C1INV  | CIS   | CM2    | CM1    | CM0    | 0000 0111       | 0000 0111                       |

| 9Dh                    | CVRCON | CVREN   | CVROE       | CVRR        | —      | CVR3  | CVR2   | CVR1   | CVR0   | 000- 0000       | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE        | TMR0IE      | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x       | 0000 000u                       |

| 0Dh                    | PIR2   | OSFIF   | CMIF        | LVDIF       | —      | BCLIF | _      | CCP3IF | CCP2IF | 000- 0-00       | 000- 0-00                       |

| 8Dh                    | PIE2   | OSFIE   | CMIE        | LVDIE       | —      | BCLIE | _      | CCP3IE | CCP2IE | 000- 0-00       | 000- 0-00                       |

| 05h                    | PORTA  | RA7     | RA6         | RA5         | RA4    | RA3   | RA2    | RA1    | RA0    | xx0x 0000       | uu0u 0000                       |

| 85h                    | TRISA  | PORTA D | Data Direct | ion Registe | ər     |       |        |        |        | 1111 1111       | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

#### 15.15.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge-triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INT0IF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit, INT0IE (INTCON<4>). Flag bit INT0IF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep if bit INT0IE was set prior to going into Sleep. The status of Global Interrupt Enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 15.18 "Power-Down Mode (Sleep)"** for details on Sleep mode.

#### 15.15.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>), see **Section 6.0 "Timer0 Module"**.

#### 15.15.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<4>), see Section 2.2 "Data Memory Organization".

#### 15.16 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, Status registers).

Since the upper 16 bytes of each bank are common in the PIC16F7X7 devices, temporary holding registers, W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP, should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 15-1 can be used.

| EXAMPLE 15-1:   | SAVING STATUS AND W REGISTERS IN RAM |

|-----------------|--------------------------------------|

| EXAIVIPLE 13-1. | SAVING STATUS AND W REGISTERS IN RAW |

| MOVWF<br>SWAPF | W_TEMP<br>STATUS, W | ;Copy W to TEMP register<br>;Swap status to be saved into W |

|----------------|---------------------|-------------------------------------------------------------|

| CLRF           | STATUS              | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0     |

| MOVWF          | STATUS_TEMP         | ;Save status to bank zero STATUS_TEMP register              |

| :              |                     |                                                             |

| :(ISR)         |                     | ;Insert user code here                                      |

| :              |                     |                                                             |

| SWAPF          | STATUS_TEMP, W      | ;Swap STATUS_TEMP register into W                           |

|                |                     | ;(sets bank to original state)                              |

| MOVWF          | STATUS              | ;Move W into STATUS register                                |

| SWAPF          | W_TEMP, F           | ;Swap W_TEMP                                                |

| SWAPF          | W_TEMP, W           | ;Swap W_TEMP into W                                         |

#### REGISTER 15-4: WDTCON: WATCHDOG TIMER CONTROL REGISTER (ADDRESS 105h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-1  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | SWDTEN |

| bit 7 |     |     |        |        |        |        | bit 0  |

- bit 7-5 Unimplemented: Read as '0'

- bit 4-1 WDTPS<3:0>: Watchdog Timer Period Select bits

- 0000 = 1:32 Prescale rate

- 0001 = 1:64 Prescale rate

- 0010 = 1:128 Prescale rate

- 0011 = 1:256 Prescale rate

- 0100 = 1:512 Prescale rate

- 0101 = 1:1024 Prescale rate

- 0110 = 1:2048 Prescale rate

- 0111 = 1:4096 Prescale rate

- 1000 = 1:8192 Prescale rate

- 1001 = 1:16394 Prescale rate

- 1010 = 1:32768 Prescale rate 1011 = 1:65536 Prescale rate

- 1100 = 1:1 Prescale rate

bit 0 **SWDTEN:** Software Enable/Disable for Watchdog Timer bit<sup>(1)</sup>

- 1 = WDT is turned on

- 0 = WDT is turned off

- **Note 1:** If WDTEN configuration bit = 1, then WDT is always enabled irrespective of this control bit. If WDTEN configuration bit = 0, then it is possible to turn WDT on/off with this control bit.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### TABLE 15-6: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address   | Name                                 | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------|--------------------------------------|-------|--------|-------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 81h, 181h | OPTION_REG                           | RBPU  | INTEDG | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

|           | Configuration<br>bits <sup>(1)</sup> | BORV0 | BOREN  | MCLRE | FOSC2  | PWRTEN | WDTEN  | FOSC1  | FOSC0  | 1111 1111            | 1111 1111                       |

| 105h      | WDTCON                               | -     | _      | —     | WDTPS3 | WDTPS2 | WSTPS1 | WDTPS0 | SWDTEN | 0 1000               | 0 1000                          |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note 1:** See Register 15-1 for operation of these bits.

#### 18.4 DC Characteristics: PIC16F737/747/767/777 (Industrial, Extended) PIC16LF737/747/767/777 (Industrial) (Continued)

| DC CHARACTERISTICS |       |                                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extendedOperating voltage VDD range as described inSection 18.1 "DC Characteristics". |      |     |       |                                                                          |  |

|--------------------|-------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|--------------------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                             | Min                                                                                                                                                                                                                                                                  | Тур† | Max | Units | Conditions                                                               |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup>    |                                                                                                                                                                                                                                                                      |      |     |       |                                                                          |  |

| D060               |       | I/O ports                                  | —                                                                                                                                                                                                                                                                    | —    | ±1  | μA    | VSS $\leq$ VPIN $\leq$ VDD, pin at high-impedance                        |  |

| D061               |       | MCLR, RA4/T0CKI                            | _                                                                                                                                                                                                                                                                    | —    | ±5  | μΑ    | $VSS \leq VPIN \leq VDD$                                                 |  |

| D063               |       | OSC1                                       | _                                                                                                                                                                                                                                                                    | _    | ±5  | μΑ    | Vss $\leq$ VPIN $\leq$ VDD,<br>XT, HS and LP oscillator<br>configuration |  |

|                    | Vol   | Output Low Voltage                         |                                                                                                                                                                                                                                                                      |      |     |       |                                                                          |  |

| D080               |       | I/O ports                                  | —                                                                                                                                                                                                                                                                    | —    | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                             |  |

| D083               |       | OSC2/CLKO<br>(RC oscillator configuration) | —                                                                                                                                                                                                                                                                    | —    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                             |  |

|                    |       |                                            | —                                                                                                                                                                                                                                                                    | —    | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                             |  |

|                    | Vон   | Output High Voltage                        |                                                                                                                                                                                                                                                                      |      |     |       |                                                                          |  |

| D090               |       | I/O ports <b>(Note 3)</b>                  | Vdd - 0.7                                                                                                                                                                                                                                                            | —    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |

| D092               |       | OSC2/CLKO<br>(RC oscillator configuration) | Vdd - 0.7                                                                                                                                                                                                                                                            | —    | —   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |

|                    |       |                                            | Vdd - 0.7                                                                                                                                                                                                                                                            | —    | —   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |

| D150*              | Vod   | Open-Drain High Voltage                    | —                                                                                                                                                                                                                                                                    | —    | 12  | V     | RA4 pin                                                                  |  |

|                    |       | Capacitive Loading Specs<br>on Output Pins |                                                                                                                                                                                                                                                                      |      |     |       |                                                                          |  |

| D100               | Cosc2 | OSC2 pin                                   | _                                                                                                                                                                                                                                                                    | -    | 15  | pF    | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1   |  |

| D101               | Сю    | All I/O pins and OSC2<br>(in RC mode)      | _                                                                                                                                                                                                                                                                    | -    | 50  | pF    |                                                                          |  |

| D102               | Св    | SCL, SDA in I <sup>2</sup> C™ mode         | —                                                                                                                                                                                                                                                                    | -    | 400 | pF    |                                                                          |  |

|                    |       | Program Flash Memory                       |                                                                                                                                                                                                                                                                      |      |     |       |                                                                          |  |

| D130               | Ер    | Endurance                                  | 100                                                                                                                                                                                                                                                                  | 1000 | —   | E/W   | 25°C at 5V                                                               |  |

| D131               | Vpr   | VDD for Read                               | 2.0                                                                                                                                                                                                                                                                  |      | 5.5 | V     |                                                                          |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F7X7 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

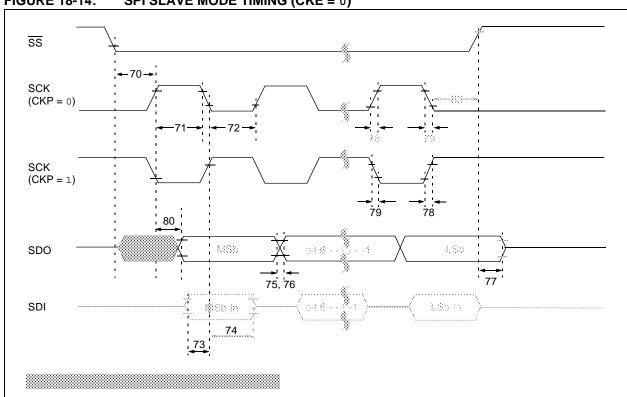

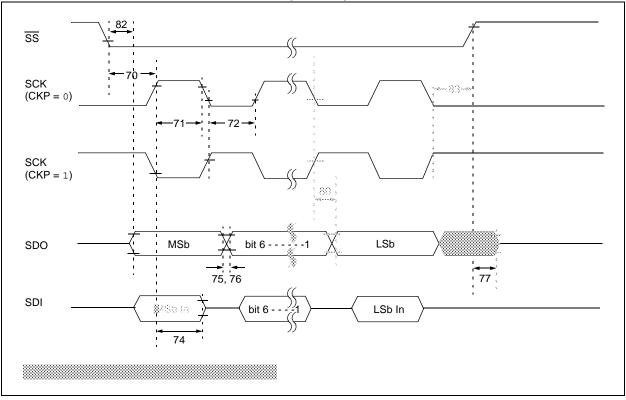

#### FIGURE 18-14: SPI SLAVE MODE TIMING (CKE = 0)

#### SPI SLAVE MODE TIMING (CKE = 1) FIGURE 18-15:

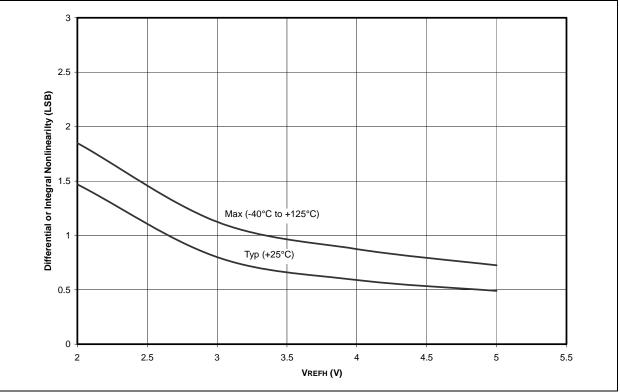

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

NOTES:

| PORTC<br>Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 13                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

| PORTC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |

| RC3/SCK/SCL Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

| RC6/TX/CK Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |

| RC7/RX/DT Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 134, 135                    |

| TRISC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65, 133                     |

| PORTC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |

| PORTD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |