Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f747t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

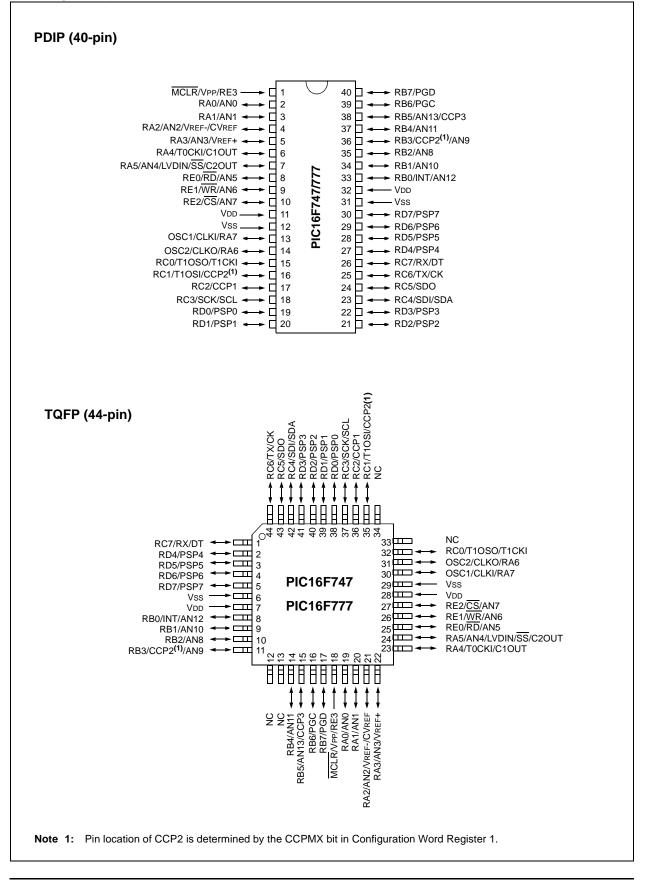

## **Pin Diagrams (Continued)**

#### TABLE 1-2:PIC16F737 AND PIC16F767 PINOUT DESCRIPTION

| Pin Name                          | PDIP<br>SOIC<br>SSOP<br>Pin # | QFN<br>Pin #           | l/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                      |

|-----------------------------------|-------------------------------|------------------------|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI/RA7<br>OSC1             | 9                             | 6                      | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode; otherwise CMOS. |

| CLKI                              |                               |                        | I             |                        | External clock source input. Always associated with pin function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).                                                           |

| RA7                               |                               |                        | I/O           | ST                     | Digital I/O.                                                                                                                                                     |

| OSC2/CLKO/RA6<br>OSC2             | 10                            | 7                      | 0             | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal Oscillator                                      |

| CLKO                              |                               |                        | 0             |                        | mode.<br>In RC mode, OSC2 pin outputs CLKO which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate.                                        |

| RA6                               |                               |                        | I/O           | ST                     | Digital I/O.                                                                                                                                                     |

| MCLR/Vpp/RE3<br>MCLR              | 1                             | 26                     | I             | ST                     | Master Clear (input) or programming voltage (output).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.                           |

| VPP                               |                               |                        | P             | 07                     | Programming voltage input.                                                                                                                                       |

| RE3                               |                               |                        | I             | ST                     | Digital input only pin.                                                                                                                                          |

|                                   |                               |                        |               |                        | PORTA is a bidirectional I/O port.                                                                                                                               |

| RA0/AN0<br>RA0                    | 2                             | 27                     | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

| ANO                               |                               |                        | 1/0           |                        | Analog input 0.                                                                                                                                                  |

| RA1/AN1                           | 3                             | 28                     |               | TTL                    |                                                                                                                                                                  |

| RA1                               | -                             | _                      | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN1                               |                               |                        | I             |                        | Analog input 1.                                                                                                                                                  |

| RA2/AN2/VREF-/CVREF               | 4                             | 1                      |               | TTL                    |                                                                                                                                                                  |

| RA2<br>AN2                        |                               |                        | I/O           |                        | Digital I/O.<br>Analog input 2.                                                                                                                                  |

| VREF-                             |                               |                        |               |                        | A/D reference voltage input (low).                                                                                                                               |

| CVREF                             |                               |                        | 0             |                        | Comparator voltage reference output.                                                                                                                             |

| RA3/AN3/Vref+                     | 5                             | 2                      |               | TTL                    |                                                                                                                                                                  |

| RA3                               |                               |                        | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN3                               |                               |                        | I             |                        | Analog input 3.                                                                                                                                                  |

| Vref+                             |                               |                        | I             |                        | A/D reference voltage input (high).                                                                                                                              |

| RA4/T0CKI/C1OUT                   | 6                             | 3                      |               | ST                     |                                                                                                                                                                  |

| RA4                               |                               |                        | I/O           |                        | Digital I/O – Open-drain when configured as output.                                                                                                              |

| T0CKI<br>C1OUT                    |                               |                        | 0             |                        | Timer0 external clock input.<br>Comparator 1 output bit.                                                                                                         |

| RA5/AN4/LVDIN/SS/C2OUT            | 7                             | 4                      | Ŭ             | TTL                    |                                                                                                                                                                  |

| RA5/AIN4/LVDIN/S5/C2OUT<br>RA5    | '                             | -                      | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN4                               |                               |                        | 1             |                        | Analog input 4.                                                                                                                                                  |

| LVDIN                             |                               |                        | I/O           |                        | Low-Voltage Detect input.                                                                                                                                        |

| SS                                |                               |                        | I             |                        | SPI slave select input.                                                                                                                                          |

| C2OUT                             |                               |                        | 0             |                        | Comparator 2 output bit.                                                                                                                                         |

| Legend: I = input<br>— = Not used |                               | ) = output<br>TL = TTL |               |                        | = input/output P = power<br>= Schmitt Trigger input                                                                                                              |

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

4: Pin location of CCP2 is determined by the CCPMX bit in Configuration Word Register 1.

## PIC16F7X7

| Pin Name          | PDIP<br>Pin # | QFN<br>Pin # | TQFP<br>Pin # | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                          |

|-------------------|---------------|--------------|---------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------|

|                   |               |              |               |               |                       | PORTD is a bidirectional I/O port or Parallel Slave Por<br>when interfacing to a microprocessor bus. |

| RD0/PSP0          | 19            | 38           | 38            |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD0               | 15            | 50           | 00            | I/O           | OI/ITE                | Digital I/O.                                                                                         |

| PSP0              |               |              |               | I/O           |                       | Parallel Slave Port data.                                                                            |

| RD1/PSP1          | 20            | 39           | 39            |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD1               |               |              |               | I/O           |                       | Digital I/O.                                                                                         |

| PSP1              |               |              |               | I/O           |                       | Parallel Slave Port data.                                                                            |

| RD2/PSP2          | 21            | 40           | 40            |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD2               |               |              |               | I/O           |                       | Digital I/O.                                                                                         |

| PSP2              |               |              |               | I/O           |                       | Parallel Slave Port data.                                                                            |

| RD3/PSP3          | 22            | 41           | 41            |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD3               |               |              |               | I/O           |                       | Digital I/O.                                                                                         |

| PSP3              |               |              |               | I/O           |                       | Parallel Slave Port data.                                                                            |

| RD4/PSP4          | 27            | 2            | 2             |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD4               |               |              |               | I/O           |                       | Digital I/O.                                                                                         |

| PSP4              |               |              |               | I/O           | (2)                   | Parallel Slave Port data.                                                                            |

| RD5/PSP5          | 28            | 3            | 3             |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD5               |               |              |               | I/O           |                       | Digital I/O.                                                                                         |

| PSP5              |               |              |               | I/O           | (2)                   | Parallel Slave Port data.                                                                            |

| RD6/PSP6          | 29            | 4            | 4             |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RD6<br>PSP6       |               |              |               | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                                            |

|                   |               | _            | _             | 1/0           | o <del></del>         | Parallel Slave Port data.                                                                            |

| RD7/PSP7          | 30            | 5            | 5             | I/O           | ST/TTL <sup>(3)</sup> | Digital I/O                                                                                          |

| RD7<br>PSP7       |               |              |               | 1/O<br>1/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                                            |

|                   |               |              |               | 1/0           |                       |                                                                                                      |

|                   |               |              | 05            |               | o <del></del>         | PORTE is a bidirectional I/O port.                                                                   |

| RE0/RD/AN5        | 8             | 25           | 25            | I/O           | ST/TTL <sup>(3)</sup> | Digital I/O                                                                                          |

| RE0<br>RD         |               |              |               | 1/O           |                       | Digital I/O.<br>Read control for Parallel Slave Port.                                                |

| AN5               |               |              |               | i             |                       | Analog input 5.                                                                                      |

| RE1/WR/AN6        | 9             | 26           | 26            | •             | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RE1               | 3             | 20           | 20            | I/O           | ST/TIL                | Digital I/O.                                                                                         |

| WR                |               |              |               | ,, C          |                       | Write control for Parallel Slave Port.                                                               |

| AN6               |               |              |               | I             |                       | Analog input 6.                                                                                      |

| RE2/CS/AN7        | 10            | 27           | 27            |               | ST/TTL <sup>(3)</sup> |                                                                                                      |

| RE2               |               |              |               | I/O           |                       | Digital I/O.                                                                                         |

| CS                |               |              |               | I             |                       | Chip select control for Parallel Slave Port.                                                         |

| AN7               |               |              |               | Ι             |                       | Analog input 7.                                                                                      |

| Vss               | —             | 31           |               | Р             | —                     | Analog ground reference.                                                                             |

| Vss               | 12, 31        | 6, 30        | 6, 29         | Р             | -                     | Ground reference for logic and I/O pins.                                                             |

| Vdd               |               | 8            |               | Р             | _                     | Analog positive supply.                                                                              |

| Vdd               | 11, 32        | 7, 28        | 7, 28         | Р             | _                     | Positive supply for logic and I/O pins.                                                              |

| NC                |               | 13, 29       | 12, 13,       |               | _                     | These pins are not internally connected. These pins                                                  |

| -                 |               | , _3         | 33, 34        |               |                       | should be left unconnected.                                                                          |

| Legend: I = input |               | 0 = ou       |               | 1             | i                     | ut/output P = power                                                                                  |

## TABLE 1-3: PIC16F747 AND PIC16F777 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured as a general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

5: Pin location of CCP2 is determined by the CCPMX bit in Configuration Word Register 1.

| Address               | Name       | Bit 7             | Bit 6                                       | Bit 5         | Bit 4           | Bit 3        | Bit 2         | Bit 1        | Bit 0        | Value on:<br>POR, BOR | Details<br>on page |  |

|-----------------------|------------|-------------------|---------------------------------------------|---------------|-----------------|--------------|---------------|--------------|--------------|-----------------------|--------------------|--|

| Bank 2                |            |                   |                                             |               |                 |              |               |              |              |                       |                    |  |

| 100h <sup>(4)</sup>   | INDF       | Addressin         | 0000 0000                                   | 30, 180       |                 |              |               |              |              |                       |                    |  |

| 101h                  | TMR0       | Timer0 Mo         | Timer0 Module Register                      |               |                 |              |               |              |              |                       |                    |  |

| 102h <sup>(4)</sup>   | PCL        | Program (         | Program Counter (PC) Least Significant Byte |               |                 |              |               |              |              |                       |                    |  |

| 103h <sup>(4)</sup>   | STATUS     | IRP               | RP1                                         | RP0           | TO              | PD           | Z             | DC           | С            | 0001 1xxx             | 21, 180            |  |

| 104h <sup>(4)</sup>   | FSR        | Indirect Da       | ata Memory A                                | Address Poir  | nter            |              |               |              |              | XXXX XXXX             | 30, 180            |  |

| 105h                  | WDTCON     | _                 | _                                           |               | WDTPS3          | WDTPS2       | WDTPS1        | WDTPS0       | SWDTEN       | 0 1000                | 187                |  |

| 106h                  | PORTB      | PORTB D           | ata Latch wh                                | en written: F | PORTB pins w    | hen read     |               |              |              | XXXX XXXX             | 64, 180            |  |

| 107h                  | —          | Unimplem          | ented                                       |               |                 |              |               |              |              | —                     | —                  |  |

| 108h                  | —          | Unimplem          | ented                                       |               |                 |              |               |              |              | _                     | _                  |  |

| 109h                  | LVDCON     | _                 | _                                           | IRVST         | LVDEN           | LVDL3        | LVDL2         | LVDL1        | LVDL0        | 00 0101               | 176                |  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | _                 | _                                           | _             | Write Buffer f  | or the upper | 5 bits of the | Program C    | Counter      | 0 0000                | 23, 180            |  |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE               | PEIE                                        | TMR0IE        | INTOIE          | RBIE         | TMR0IF        | INT0IF       | RBIF         | 0000 000x             | 25, 180            |  |

| 10Ch                  | PMDATA     | EEPROM            | EEPROM Data Register Low Byte               |               |                 |              |               |              |              |                       | 32, 181            |  |

| 10Dh                  | PMADR      | EEPROM            | EEPROM Address Register Low Byte            |               |                 |              |               |              |              |                       |                    |  |

| 10Eh                  | PMDATH     | _                 | _                                           | EEPROM D      | Data Register H | ligh Byte    |               |              |              | xx xxxx               | 32, 181            |  |

| 10Fh                  | PMADRH     |                   | _                                           | _             | —               | EEPROM       | Address Re    | gister High  | Byte         | xxxx                  | 32, 181            |  |

| Bank 3                |            |                   |                                             |               |                 |              |               |              |              |                       |                    |  |

| 180h <sup>(4)</sup>   | INDF       | Addressin         | g this location                             | n uses conte  | ents of FSR to  | address dat  | a memory (I   | not a physic | al register) | 0000 0000             | 30, 180            |  |

| 181h                  | OPTION_REG | RBPU              | INTEDG                                      | TOCS          | TOSE            | PSA          | PS2           | PS1          | PS0          | 1111 1111             | 22, 180            |  |

| 182h <sup>(4)</sup>   | PCL        | Program (         | Counter (PC)                                | Least Signif  | ficant Byte     |              |               |              |              | 0000 0000             | 29, 180            |  |

| 183h <sup>(4)</sup>   | STATUS     | IRP               | RP1                                         | RP0           | TO              | PD           | Z             | DC           | С            | 0001 1xxx             | 21, 180            |  |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da       | ata Memory A                                | Address Poir  | nter            |              |               |              |              | XXXX XXXX             | 30, 180            |  |

| 185h                  | _          | Unimplem          | ented                                       |               |                 |              |               |              |              | _                     |                    |  |

| 186h                  | TRISB      | PORTB D           | ata Direction                               | Register      |                 |              |               |              |              | 1111 1111             | 64, 181            |  |

| 187h                  | —          | Unimplem          | ented                                       |               |                 |              |               |              |              | _                     | _                  |  |

| 188h                  | —          |                   | Unimplemented                               |               |                 |              |               |              |              |                       | _                  |  |

| 189h                  | _          | Unimplemented     |                                             |               |                 |              |               |              |              | _                     | _                  |  |

| 18Ah <sup>(1,4)</sup> | PCLATH     |                   | _                                           | _             | Write Buffer f  | or the upper | 5 bits of the | Program C    | Counter      | 0 0000                | 23, 180            |  |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE               | PEIE                                        | TMR0IE        | INTOIE          | RBIE         | TMR0IF        | INTOIF       | RBIF         | 0000 000x             | 25, 180            |  |

| 18Ch                  | PMCON1     | <mark>(</mark> 6) |                                             |               | —               |              | —             | —            | RD           | 10                    | 32, 181            |  |

| 18Dh                  | —          | Reserved          | , maintain cle                              | ar            |                 |              |               |              |              | _                     |                    |  |

| 18Eh                  | —          | Reserved          | , maintain cle                              | ar            |                 |              |               |              |              | _                     |                    |  |

| 18Fh                  |            | Reserved          | , maintain cle                              | ar            |                 |              |               |              |              | _                     |                    |  |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> bits, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOT).

2: Other (non Power-up) Resets include external Reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices (except for RE3), read as '0'.

6: This bit always reads as a '1'.

7: OSCCON<OSTS> bit resets to '0' with dual-speed start-up and LP, HS or HS-PLL selected as the oscillator.

8: RE3 is an input only. The state of the TRISE3 bit has no effect and will always read '1'.

## 4.7.3.2 Returning to Primary Oscillator with a Reset

A Reset will clear SCS<1:0> back to '00'. The sequence for starting the primary oscillator following a Reset is the same for all forms of Reset, including POR. There is no transition sequence from the alternate system clock to the primary system clock on a Reset condition. Instead, the device will reset the state of the OSCCON register and default to the primary system clock. The sequence of events that take place after this will depend upon the value of the FOSC bits in the Configuration register. If the external oscillator is configured as a crystal (HS, XT or LP), the CPU will be held in the Q1 state until 1024 clock cycles have transpired on the primary clock. This is necessary because the crystal oscillator had been powered down until the time of the transition.

During the oscillator start-up time, instruction execution and/or peripheral operation is suspended.

| Note: | If Two-Speed Clock Start-up mode is                                                        |

|-------|--------------------------------------------------------------------------------------------|

|       | enabled, the INTRC will act as the system<br>clock until the Oscillator Start-up Timer has |

|       | timed out.                                                                                 |

If the primary system clock is either RC, EC or INTRC, the CPU will begin operating on the first Q1 cycle following the wake-up event. This means that there is

no oscillator start-up time required because the primary clock is already stable; however, there is a delay between the wake-up event and the following Q2. An internal delay timer of 5-10  $\mu$ s will suspend operation after the Reset to allow the CPU to become ready for code execution. The CPU and peripheral clock will be held in the first Q1.

The sequence of events is as follows:

- 1. A device Reset is asserted from one of many sources (WDT, BOR, MCLR, etc.).

- 2. The device resets and the CPU start-up timer is enabled if in Sleep mode. The device is held in Reset until the CPU start-up time-out is complete.

- 3. If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active waiting for 1024 clocks of the primary system clock. While waiting for the OST, the device will be held in Reset. The OST and CPU start-up timers run in parallel.

- After both the CPU start-up timer and the Oscillator Start-up Timer have timed out, the device will wait for one additional clock cycle and instruction execution will begin.

#### TT1P(1) Q1 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q4 T1OSI OSC1 TOST(4) OSC2 System Clock Peripheral Clock Sleep OSTS Program 0000h PC 0001h Counter

## FIGURE 4-10: TIMING LP CLOCK TO PRIMARY SYSTEM CLOCK AFTER RESET (HS, XT, LP)

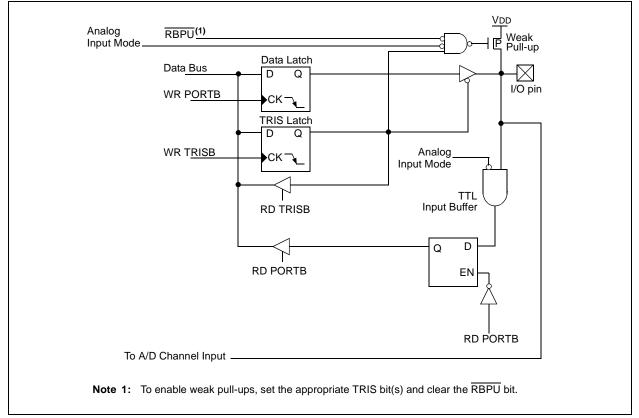

## FIGURE 5-9: BLOCK DIAGRAM OF RB1/AN10 PIN

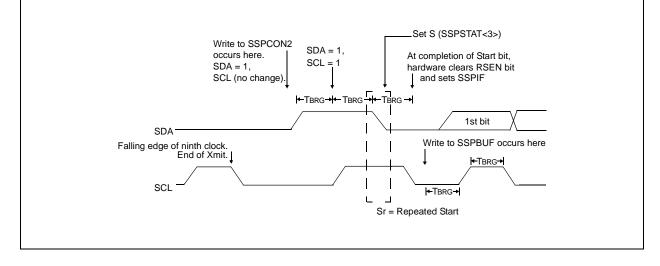

## 10.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 10.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 10-20: REPEATED START CONDITION WAVEFORM

# PIC16F7X7

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

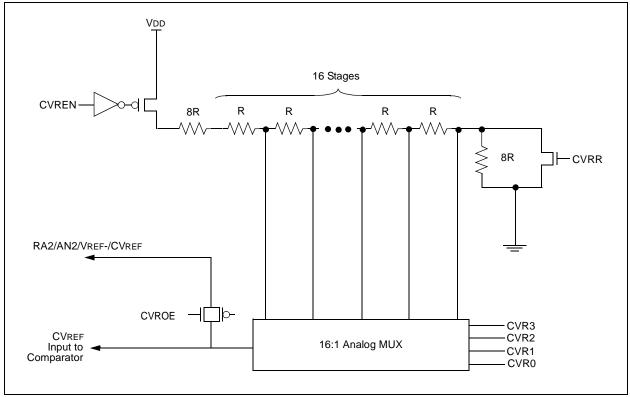

| 9Dh     | CVRCON | CVREN | CVROE | CVRR  | —     | CVR3  | CVR2  | CVR1  | CVR0  | 000-0000 (      | 000- 0000                       |

| 9Ch     | CMCON  | C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   | 0000 0111       | 0000 0111                       |

**Legend:** x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

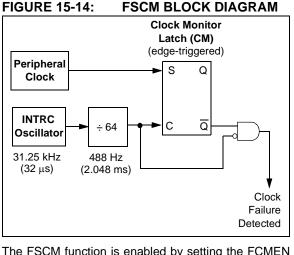

#### 15.17.4 FAIL-SAFE OPTION

The Fail-Safe Clock Monitor (FSCM) is designed to allow the device to continue to operate even in the event of an oscillator failure.

The FSCM function is enabled by setting the FCMEN bit in Configuration Word Register 2.

In the event of an oscillator failure, the FSCM will generate an oscillator fail interrupt and will switch the system clock over to the internal oscillator. The system will continue to come from the internal oscillator until the Fail-Safe condition is exited. The Fail-Safe condition is exited with either a Reset, the execution of a SLEEP instruction or a write to the SCS bits of a different value.

The frequency of the internal oscillator will depend upon the value contained in the IRCF bits. Another clock source can be selected via the IRCF and the SCS bits of the OSCCON register.

FIGURE 15-15: FSCM TIMING DIAGRAM

The FSCM sample clock is generated by dividing the INTRC clock by 64. This will allow enough time between FSCM sample clocks for a system clock edge to occur.

On the rising edge of the postscaled clock, the monitoring latch (CM = 0) will be cleared. On a falling edge of the primary or secondary system clock, the monitoring latch will be set (CM = 1). In the event that a falling edge of the postscaled clock occurs and the monitoring latch is not set, a clock failure has been detected.

While in Fail-Safe mode, a Reset will exit the Fail-Safe condition. If the primary clock source is configured for a crystal, the OST timer will wait for the 1024 clock cycles for the OST time-out and the device will continue running from the internal oscillator until the OST is complete. A SLEEPinstruction, or a write to the SCS bits (where SCS bits do not = 00), can be performed to put the device into a low-power mode.

If Reset occurs while in Fail-Safe mode and the primary clock source is EC or RC, then the device will immediately switch back to EC or RC mode.

Note: Two-Speed Start-up is automatically enabled when the Fail-Safe option is enabled.

### 15.17.4.1 Fail-Safe in Low-Power Mode

A change of SCS<1:0> or the SLEEP instruction will end the Fail-Safe condition. The system clock will default to the source selected by the SCS bits, which is either T1OSC, INTRC or none (Sleep mode). However, the FSCM will continue to monitor the system clock. If the secondary clock fails, the device will immediately switch to the internal oscillator clock. If OSFIE is set, an interrupt will be generated.

| MSSP (I <sup>2</sup> C Mode)                  | ,        |

|-----------------------------------------------|----------|

| MSSP (SPI Mode)                               |          |

| On-Chip Reset Circuit                         | ,        |

| OSC1/CLKI/RA7 Pin                             | L        |

| OSC2/CLKO/RA6 Pin                             |          |

| PIC16F737 and PIC16F767                       |          |

| PIC16F747 and PIC16F777                       |          |

| PORTC (Peripheral Output Override)            |          |

| RC<2:0>, RC<7:5> Pins                         | 5        |

| PORTC (Peripheral Output Override)            | <i>,</i> |

| RC<4:3> Pins                                  | 5        |

| PORTD (In I/O Port Mode)                      |          |

| PORTD and PORTE (Parallel Slave Port)         |          |

| PORTE (In I/O Port Mode)                      |          |

| PWM Mode                                      |          |

| RA0/AN0:RA1/AN1 Pins                          |          |

| RA2/AN2/VREF-/CVREF Pin                       |          |

| RA3/AN3/VREF+ Pin                             |          |

| RA4/T0CKI/C1OUT Pin                           |          |

| RA5/AN4/LVDIN/SS/C2OUT Pin                    |          |

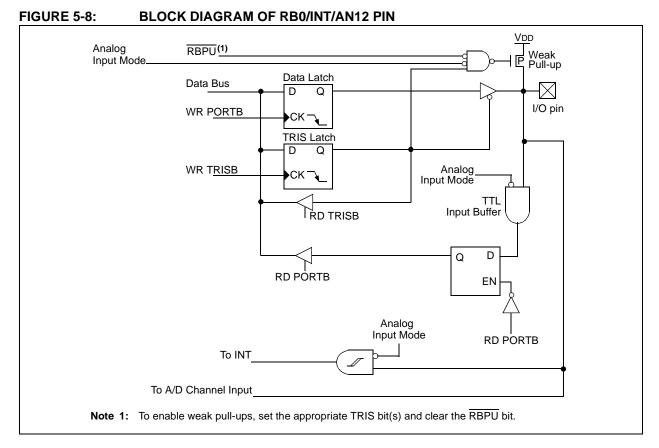

| RB0/INT/AN12 Pin                              |          |

| RB1/AN10 Pin                                  |          |

| RB2/AN8 Pin                                   |          |

| RB3/CCP2/AN9 Pin                              |          |

| RB4/AN11 Pin                                  |          |

| RB5/AN13/CCP3 Pin61                           |          |

| RB6/PGC Pin                                   |          |

| RB7/PGD Pin                                   |          |

| Recommended MCLR Circuit                      |          |

| System Clock                                  |          |

| Timer0/WDT Prescaler73                        |          |

| Timer1                                        |          |

| Timer2                                        |          |

| Watchdog Timer (WDT)                          |          |

| BOR. See Brown-out Reset.                     |          |

| BRG. See Baud Rate Generator.                 |          |

| BRGH Bit                                      | 5        |

| Brown-out Reset (BOR) 169, 172, 173, 179, 180 |          |

| , , , , , , , , , , , , , , , , , , , ,       |          |

## С

| C Compilers                                    |

|------------------------------------------------|

| MPLAB C18202                                   |

| Capture/Compare/PWM (CCP)87                    |

| Capture Mode89                                 |

| CCP Pin Configuration89                        |

| Prescaler                                      |

| Compare Mode 89                                |

| CCP Pin Configuration90                        |

| Software Interrupt Mode90                      |

| Special Event Trigger90                        |

| Special Event Trigger Output                   |

| Timer1 Mode Selection90                        |

| Interaction of Two CCP Modules87               |

| PWM Mode91                                     |

| Duty Cycle91                                   |

| Example Frequencies and Resolutions            |

| Period91                                       |

| Setup for Operation92                          |

| Registers Associated with Capture, Compare and |

| Timer190                                       |

| Registers Associated with PWM and Timer292     |

| Timer Resources87                              |

| CCP1 Module87                                  |

| CCP2 Module                                    |

| CCP3 Module                                    |

| CCPR1H Register                                |

| CCPR1L Register<br>CCPR2H Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| CCDD2U Degister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| CCPR2L Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| CCPR3H Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| CCPR3L Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| CCPxM<3:0> Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| CCPxX and CCPxY Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Clock Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Selection Using OSCCON Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Clock Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Modes (table)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Transition and the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Code Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Call of a Subroutine in Page 1 from Page 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| Changing Between Capture Prescalers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Changing Prescaler Assignment from WDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| to Timer0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Flash Program Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32                                                                               |

| Implementing a Real-Time Clock Using a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Timer1 Interrupt Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| Indirect Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Initializing PORTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| Loading the SSPBUF (SSPSR) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Reading a 16-bit Free Running Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Saving Status and W Registers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Writing a 16-bit Free Running Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Code Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Comparator Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Analog Input Connection Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 165                                                                              |

| Analog Input Connection Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 165<br>165                                                                       |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 165<br>165<br>162                                                                |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 165<br>165<br>162<br>165                                                         |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 165<br>165<br>162<br>165<br>164                                                  |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts<br>Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 165<br>165<br>162<br>165<br>164<br>163                                           |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts<br>Operation<br>Operation During Sleep                                                                                                                                                                                                                                                                                                                                                                                                                         | 165<br>165<br>162<br>165<br>164<br>163<br>165                                    |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts<br>Operation<br>Operation During Sleep<br>Outputs                                                                                                                                                                                                                                                                                                                                                                                                              | 165<br>165<br>162<br>165<br>164<br>163<br>165<br>163                             |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts<br>Operation<br>Operation During Sleep<br>Outputs<br>Reference                                                                                                                                                                                                                                                                                                                                                                                                 | 165<br>162<br>162<br>165<br>164<br>163<br>163<br>163<br>163                      |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts<br>Operation<br>Operation During Sleep<br>Outputs<br>Reference<br>External Signal                                                                                                                                                                                                                                                                                                                                                                              | 165<br>162<br>165<br>164<br>163<br>163<br>163<br>163<br>163                      |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts<br>Operation<br>Operation During Sleep<br>Outputs<br>Reference<br>External Signal<br>Internal Signal                                                                                                                                                                                                                                                                                                                                                           | 165<br>165<br>165<br>164<br>163<br>163<br>163<br>163<br>163<br>163               |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration<br>Effects of a Reset<br>Interrupts<br>Operation<br>Operation During Sleep<br>Outputs<br>Reference<br>External Signal<br>Internal Signal<br>Response Time                                                                                                                                                                                                                                                                                                                                          | 165<br>162<br>162<br>165<br>164<br>163<br>163<br>163<br>163<br>163<br>163<br>163 |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Analog Input Connection Considerations<br>Associated Registers<br>Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Analog Input Connection Considerations<br>Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Analog Input Connection Considerations         Associated Registers         Configuration         Effects of a Reset         Interrupts         Operation         Operation During Sleep         Outputs         Reference         External Signal         Internal Signal         Response Time         Comparator Specifications         Comparator Voltage Reference         Associated Registers         Computed GOTO         Configuration Bits                                                                                                                              |                                                                                  |