Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f767-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

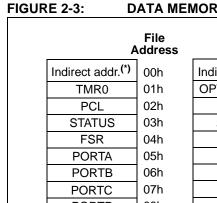

# DATA MEMORY MAP FOR PIC16F747 AND THE PIC16F777

| 0h<br>1h<br>2h<br>3h<br>4h<br>5h<br>6h<br>7h | Indirect addr. <sup>(*)</sup><br>OPTION_REG<br>PCL<br>STATUS<br>FSR<br>TRISA                 | 80h<br>81h<br>82h<br>83h                                                                                                                                                                                                                                                                               | Indirect addr. <sup>(*)</sup><br>TMR0<br>PCL                                                                                                                                                                                                                                 | 100h<br>101h<br>102h                                                                                                                                                                                                                                                                             | Indirect addr. <sup>(*)</sup><br>OPTION_REG<br>PCL                                                                                                                                                                                                                                                                                                   | 180h<br>181h                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1h<br>2h<br>3h<br>4h<br>5h<br>6h             | OPTION_REG<br>PCL<br>STATUS<br>FSR                                                           | 81h<br>82h<br>83h                                                                                                                                                                                                                                                                                      | TMR0<br>PCL                                                                                                                                                                                                                                                                  | 101h                                                                                                                                                                                                                                                                                             | OPTION_REG                                                                                                                                                                                                                                                                                                                                           | 181                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2h<br>3h<br>4h<br>5h<br>6h                   | PCL<br>STATUS<br>FSR                                                                         | 82h<br>83h                                                                                                                                                                                                                                                                                             | PCL                                                                                                                                                                                                                                                                          | 102h                                                                                                                                                                                                                                                                                             | PCL                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4h<br>5h<br>6h                               | FSR                                                                                          | 83h                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5h<br>6h                                     | FSR                                                                                          |                                                                                                                                                                                                                                                                                                        | STATUS                                                                                                                                                                                                                                                                       | 103h                                                                                                                                                                                                                                                                                             | STATUS                                                                                                                                                                                                                                                                                                                                               | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6h                                           |                                                                                              | 84h                                                                                                                                                                                                                                                                                                    | FSR                                                                                                                                                                                                                                                                          | 104h                                                                                                                                                                                                                                                                                             | FSR                                                                                                                                                                                                                                                                                                                                                  | 184                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                              |                                                                                              | 85h                                                                                                                                                                                                                                                                                                    | WDTCON                                                                                                                                                                                                                                                                       | 105h                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 185                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7h                                           | TRISB                                                                                        | 86h                                                                                                                                                                                                                                                                                                    | PORTB                                                                                                                                                                                                                                                                        | 106h                                                                                                                                                                                                                                                                                             | TRISB                                                                                                                                                                                                                                                                                                                                                | 186                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                              | TRISC                                                                                        | 87h                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              | 107h                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 187                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8h                                           | TRISD                                                                                        | 88h                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              | 108h                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 188                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9h                                           | TRISE                                                                                        | 89h                                                                                                                                                                                                                                                                                                    | LVDCON                                                                                                                                                                                                                                                                       | 109h                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 189                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ah                                           | PCLATH                                                                                       | 8Ah                                                                                                                                                                                                                                                                                                    | PCLATH                                                                                                                                                                                                                                                                       | 10Ah                                                                                                                                                                                                                                                                                             | PCLATH                                                                                                                                                                                                                                                                                                                                               | 18A                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bh                                           | INTCON                                                                                       | 8Bh                                                                                                                                                                                                                                                                                                    | INTCON                                                                                                                                                                                                                                                                       | 10Bh                                                                                                                                                                                                                                                                                             | INTCON                                                                                                                                                                                                                                                                                                                                               | 18B                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ch                                           | PIE1                                                                                         | 8Ch                                                                                                                                                                                                                                                                                                    | PMDATA                                                                                                                                                                                                                                                                       | 10Ch                                                                                                                                                                                                                                                                                             | PMCON1                                                                                                                                                                                                                                                                                                                                               | 18C                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Dh                                           | PIE2                                                                                         |                                                                                                                                                                                                                                                                                                        | PMADR                                                                                                                                                                                                                                                                        | 10Dh                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 18D                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Eh                                           | PCON                                                                                         |                                                                                                                                                                                                                                                                                                        | PMDATH                                                                                                                                                                                                                                                                       | 10Eh                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 18E                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fh                                           |                                                                                              |                                                                                                                                                                                                                                                                                                        | PMADRH                                                                                                                                                                                                                                                                       | 10Fh                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 18F                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0h                                           | OSCTUNE                                                                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              | 110h                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 190                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1h                                           | SSPCON2                                                                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2h                                           | PR2                                                                                          | 92h                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3h                                           | SSPADD                                                                                       | 93h                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4h                                           | SSPSTAT                                                                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5h                                           | CCPR3L                                                                                       |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6h                                           | CCPR3H                                                                                       |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  | Quant                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7h                                           | CCP3CON                                                                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8h                                           | TXSTA                                                                                        |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9h                                           | SPBRG                                                                                        |                                                                                                                                                                                                                                                                                                        | 16 Bytes                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                  | 16 Bytes                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ah                                           |                                                                                              |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bh                                           | ADCON2                                                                                       |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ch                                           | CMCON                                                                                        | 9Ch                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Dh                                           | CVRCON                                                                                       | 9Dh                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Eh                                           | ADRESL                                                                                       | 9Eh                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fh                                           | ADCON1                                                                                       | 9Fh                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              | 11Fh                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 19F                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0h                                           | General<br>Purpose<br>Register<br>80 Bytes                                                   | A0h<br>EFh                                                                                                                                                                                                                                                                                             | General<br>Purpose<br>Register<br>80 Bytes                                                                                                                                                                                                                                   | 120h<br>16Fh                                                                                                                                                                                                                                                                                     | General<br>Purpose<br>Register<br>80 Bytes                                                                                                                                                                                                                                                                                                           | 1A0                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                              |                                                                                              | F0h                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                              | 170h                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                      | 1F0                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                              | Accesses<br>70h-7Fh                                                                          |                                                                                                                                                                                                                                                                                                        | Accesses<br>70h-7Fh                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                  | Accesses<br>70h-7Fh                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fh                                           | Dev. 1. 4                                                                                    | FFh                                                                                                                                                                                                                                                                                                    | Bank 2                                                                                                                                                                                                                                                                       | 17Fh                                                                                                                                                                                                                                                                                             | Book 2                                                                                                                                                                                                                                                                                                                                               | 1FF                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                              | Bank 1                                                                                       |                                                                                                                                                                                                                                                                                                        | Bank 2                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                  | Bank 3                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                              | Eh<br>Fh<br>0h<br>1h<br>2h<br>3h<br>5h<br>6h<br>7h<br>8h<br>6h<br>7h<br>8h<br>Ch<br>Eh<br>6h | Eh PCON<br>Fh OSCCON<br>Oh OSCTUNE<br>1h SSPCON2<br>2h PR2<br>3h SSPADD<br>4h SSPSTAT<br>5h CCPR3L<br>6h CCPR3H<br>7h CCP3CON<br>8h TXSTA<br>9h SPBRG<br>Ah<br>Bh ADCON2<br>Ch CMCON<br>Dh CVRCON<br>Eh ADRESL<br>Fh ADCON1<br>Oh<br>General<br>Purpose<br>Register<br>80 Bytes<br>Accesses<br>70h-7Fh | DhPIE28DhEhPCON8EhFhOSCCON8Fh0hOSCTUNE90h1hSSPCON291h2hPR292h3hSSPADD93h4hSSPSTAT94h5hCCPR3L95h6hCCPR3H96h7hCCP3CON97h8hTXSTA98h9hSPBRG99hAh9AhBhADCON29BhChCMCON9ChDhCVRCON9DhEhADRESL9EhFhADCON19Fh0hGeneral<br>Purpose<br>Register<br>80 BytesEFhFhAccesses<br>70h-7FhFfh | DhPIE28DhPMADREhPCON8EhPMDATHFhOSCCON8FhPMDATHOhOSCTUNE90h90h1hSSPCON291h92h2hPR292h93h4hSSPSTAT94h5hCCPR3L95h6hCCPR3H96h7hCCP3CON97h8hTXSTA98h9hSPBRG99h16 Bytes92hAh9AhBhADCON29BhChCMCON9ChDhCVRCON9DhEhADRESL9EhFhADCON19Fh0hGeneralPurposeRegister80 Bytes80 BytesFhAccesses70h-7FhFhFFhFFh | DhPIE28DhPMADR10DhEhPCON8EhPMDATH10EhFhOSCCON8FhPMADRH10Fh0hOSCTUNE90h110h1hSSPCON291h110h2hPR292h110h3hSSPADD93h110h4hSSPSTAT94h10Fh5hCCPR3L95h95h6hCCPR3H96hGeneral7hCCP3CON97hPurpose8hTXSTA98hRegister9hSPBRG99h16 BytesAh9Ah11FhBhADCON29BhChCMCON9ChDhCVRCON9DhEhADRESL9EhFhADCON19Fh0hGeneralPurposeRegister80 Bytes16FhAccesses70h-7Fh16FhFh | DhPIE28DhPMADR10DhEhPCON8EhPMDATH10EhFhOSCCON8FhPMDATH10Eh0hOSCTUNE90h110h1hSSPCON291h2hPR292h3hSSPADD93h4hSSPSTAT94h5hCCPR3L95h6hCCPR3H96h7hCCP3CON97hPurposeRegister8hTXSTA98h9hSPBRG99h16 Bytes16 BytesAh9AhBhADCON29BhChCMCON9Ch9ChDhCVRCON9Dh9DhEhADRESL9Eh9EhFhADCON19FhA0hGeneralPurposeRegister80 Bytes80 BytesEFhAccesses70h-7Fh70h-7FhFfhFhMCCSSAccesses70h-7FhFhMCCSSAccesses70h-7FhFhMCCSSAccesses70h-7FhFfhFhMCCSSAccesses70h-7FhFhTofh-7FhFhFfh |

| Address            | Name       | Bit 7                | Bit 6                                         | Bit 5                     | Bit 4                  | Bit 3               | Bit 2         | Bit 1         | Bit 0        | Value on:<br>POR, BOR | Details<br>on page |

|--------------------|------------|----------------------|-----------------------------------------------|---------------------------|------------------------|---------------------|---------------|---------------|--------------|-----------------------|--------------------|

| Bank 1             |            |                      |                                               |                           |                        |                     |               |               |              |                       |                    |

| 80h <sup>(4)</sup> | INDF       | Addressin            | g this locatio                                | n uses conte              | ents of FSR to a       | address dat         | a memory (r   | not a physic  | al register) | 0000 0000             | 30, 180            |

| 81h                | OPTION_REG | RBPU                 | INTEDG                                        | TOCS                      | T0SE                   | PSA                 | PS2           | PS1           | PS0          | 1111 1111             | 22, 180            |

| 82h <sup>(4)</sup> | PCL        | Program 0            | Program Counter's (PC) Least Significant Byte |                           |                        |                     |               |               |              |                       | 29, 180            |

| 83h <sup>(4)</sup> | STATUS     | IRP                  | RP1                                           | RP0                       | TO                     | PD                  | Z             | DC            | С            | 0001 1xxx             | 21, 180            |

| 84h <sup>(4)</sup> | FSR        | Indirect Da          | ata Memory /                                  | Address Poir              | nter                   |                     |               | •             | •            | xxxx xxxx             | 30, 180            |

| 85h                | TRISA      | PORTA D              | ata Direction                                 | Register                  |                        |                     |               |               |              | 1111 1111             | 55, 181            |

| 86h                | TRISB      | PORTB D              | ata Direction                                 | Register                  |                        |                     |               |               |              | 1111 1111             | 64, 181            |

| 87h                | TRISC      | PORTC D              | ata Direction                                 | Register                  |                        |                     |               |               |              | 1111 1111             | 66, 181            |

| 88h <sup>(5)</sup> | TRISD      | PORTD D              | ata Direction                                 | Register                  |                        |                     |               |               |              | 1111 1111             | 67, 181            |

| 89h <b>(5)</b>     | TRISE      | IBF <sup>(5)</sup>   | OBF <sup>(5)</sup>                            | IBOV <b>(5)</b>           | PSPMODE <sup>(5)</sup> | (8)                 | PORTE Da      | ta Direction  | bits         | 0000 1111             | 69, 181            |

|                    | PCLATH     | _                    |                                               |                           | Write Buffer for       | or the upper        | 5 bits of the | Program C     | Counter      | 0 0000                | 23, 180            |

| 8Bh <sup>(4)</sup> | INTCON     | GIE                  | PEIE                                          | TMR0IE                    | INTOIE                 | RBIE                | TMR0IF        | <b>INT0IF</b> | RBIF         | 0000 000x             | 25, 180            |

| 8Ch                | PIE1       | PSPIE <sup>(3)</sup> | ADIE                                          | RCIE                      | TXIE                   | SSPIE               | CCP1IE        | TMR2IE        | TMR1IE       | 0000 0000             | 24, 181            |

| 8Dh                | PIE2       | OSFIE                | CMIE                                          | LVDIE                     |                        | BCLIE               | —             | CCP3IE        | CCP2IE       | 000- 0-00             | 26, 181            |