#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | <u>.</u>                                                                 |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f767-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 and CCP3 peripheral interrupts.

-n = Value at POR

| REGISTER 2-6: | PIE2: PEF                 | RIPHERAL                  | INTERRU         | PT ENABLE     | E REGISTI    | ER 2 (ADD            | RESS 8DI     | ו)     |

|---------------|---------------------------|---------------------------|-----------------|---------------|--------------|----------------------|--------------|--------|

|               | R/W-0                     | R/W-0                     | R/W-0           | U-0           | R/W-0        | U-0                  | R/W-0        | R/W-0  |

|               | OSFIE                     | CMIE                      | LVDIE           | —             | BCLIE        |                      | CCP3IE       | CCP2IE |

|               | bit 7                     |                           |                 |               |              |                      |              | bit 0  |

|               |                           |                           |                 |               |              |                      |              |        |

| bit 7         | OSFIE: Os                 | cillator Fail I           | nterrupt Ena    | ble bit       |              |                      |              |        |

|               | 1 = Enable<br>0 = Disable | •                         |                 |               |              |                      |              |        |

| bit 6         | CMIE: Con                 | nparator Inte             | rrupt Enable    | e bit         |              |                      |              |        |

|               | 1 = Enable<br>0 = Disable |                           |                 |               |              |                      |              |        |

| bit 5         | LVDIE: Lov                | w-Voltage De              | etect Interrup  | ot Enable bit |              |                      |              |        |

|               |                           | terrupt is ena            |                 |               |              |                      |              |        |

| bit 4         |                           | terrupt is disa           |                 |               |              |                      |              |        |

| bit 3         | •                         | ented: Read               |                 | hla hit       |              |                      |              |        |

| DIL 3         |                           | s Collision Ir            |                 | the SSP whe   | on configure | $d$ for $l^2 \cap M$ | actor mode   |        |

|               |                           |                           |                 | the SSP who   |              |                      |              |        |

| bit 2         | Unimplem                  | ented: Read               | <b>l as</b> '0' |               |              |                      |              |        |

| bit 1         | CCP3IE: C                 | CP3 Interrup              | ot Enable bit   |               |              |                      |              |        |

|               |                           | s the CCP3<br>es the CCP3 | •               |               |              |                      |              |        |

| bit 0         | CCP2IE: C                 | CP2 Interrup              | ot Enable bit   |               |              |                      |              |        |

|               |                           | s the CCP2<br>es the CCP2 |                 |               |              |                      |              |        |

|               | Legend:                   |                           |                 |               |              |                      |              |        |

|               | R = Reada                 | ble bit                   | W = W           | /ritable bit  | U = Unim     | plemented            | bit, read as | '0'    |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

|       | R/W-0                       | R/W-0                            | R/W-0                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0         | U-0                       | R/W-0        | R/W-0        |

|-------|-----------------------------|----------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------|--------------|--------------|

|       | OSFIF                       | CMIF                             | LVDIF                         | IF       —       BCLIF       —       CCP3IF         It Flag bit       bit       bit       bit       bit         ag bit       nged (must be cleared in software)       bit       bit         errupt Flag bit       en below the specified LVD voltage (must be cleared in ter then the specified LVD voltage       Flag bit         Flag bit       ed in the SSP when configured for I <sup>2</sup> C Master mode red       bit         bit       ccurred (must be cleared in software)       occurred         match occurred (must be cleared in software)       e match occurred       function the software)         bit       ccurred (must be cleared in software)       function tered       function tered         bit       ccurred (must be cleared in software)       function tered       function tered         bit       ccurred (must be cleared in software)       function tered       function tered         cott       ccurred (must be cleared in software)       function tered       function tered         cott       ccurred (must be cleared in software)       function tered       function tered         cott       ccurred (must be cleared in software)       function tered       function tered | CCP2IF        |                           |              |              |

|       | bit 7                       |                                  |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              | bit 0        |

| bit 7 | <b>OSFIF:</b> Os            | cillator Fail I                  | nterrupt Flag                 | ı bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                           |              |              |

|       | •                           | n oscillator fa<br>n clock opera |                               | put has char                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nged to INT   | RC (must be               | e cleared in | software)    |

| bit 6 | CMIF: Con                   | nparator Inte                    | errupt Flag bi                | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |                           |              |              |

|       |                             |                                  | has changed<br>has not chang  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ared in softw | vare)                     |              |              |

| bit 5 | LVDIF: Lov                  | w-Voltage De                     | etect Interrup                | ot Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                           |              |              |

|       |                             |                                  |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           | be cleared   | in software) |

| bit 4 | Unimplem                    | ented: Read                      | <b>d as</b> '0'               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              |              |

| bit 3 | BCLIF: Bu                   | s Collision Ir                   | nterrupt Flag                 | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                           |              |              |

|       |                             | collision has<br>s collision ha  |                               | the SSP whe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n configure   | d for I <sup>2</sup> C Ma | aster mode   |              |

| bit 2 | Unimplem                    | ented: Read                      | <b>d as</b> '0'               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              |              |

| bit 1 | CCP3IF: C                   | CP3 Interru                      | pt Flag bit                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              |              |

|       |                             | 1 register ca                    | apture occurr<br>capture occu |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | cleared in s  | oftware)                  |              |              |

|       |                             | 1 register co                    |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nust be clea  | ared in softw             | vare)        |              |

|       | <u>PWM mod</u><br>Unused in | _                                |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              |              |

| bit 0 | CCP2IF: C                   | CP2 Interru                      | ot Flag bit                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              |              |

|       |                             | 1 register ca                    | apture occurr<br>capture occu | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | cleared in s  | oftware)                  |              |              |

|       |                             | 1 register co                    |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nust be clea  | ared in softw             | vare)        |              |

|       | <u>PWM mod</u><br>Unused.   | <u>e:</u>                        |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              |              |

|       | Legend:                     |                                  |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                           |              |              |

|       | R = Reada                   | able bit                         | W = W                         | /ritable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U = Unin      | nplemented                | bit, read as | · '0'        |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

#### 2.2.2.8 PCON Register

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

Note: BOR is unknown on POR. It must be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration Word register).

#### REGISTER 2-8: PCON: POWER CONTROL/STATUS REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|--------|-------|-------|

| _     | —   | —   | —   | —   | SBOREN | POR   | BOR   |

| bit 7 |     |     |     |     |        |       | bit 0 |

- bit 7-3 Unimplemented: Read as '0'

- bit 2 **SBOREN**: Software Brown-out Reset Enable bit

- If BORSEN in Configuration Word 2 is a '1' and BOREN in Configuration Word 1 is '0': 1 = BOR enabled 0 = BOR disabled

- bit 1 **POR**: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 **BOR**: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.5.1 **INTRC MODES**

Using the internal oscillator as the clock source can eliminate the need for up to two external oscillator pins, after which it can be used for digital I/O. Two distinct configurations are available:

- In INTIO1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output.

#### 4.5.2 OSCTUNE REGISTER

The internal oscillator's output has been calibrated at the factory but can be adjusted in the application. This is done by writing to the OSCTUNE register (Register 4-1). The tuning sensitivity is constant throughout the tuning range. The OSCTUNE register has a tuning range of ±12.5%.

When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. The INTRC clock will reach the new frequency within 8 clock cycles (approximately  $8 * 32 \ \mu s = 256 \ \mu s$ ); the INTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred. Operation of features that depend on the 31.25 kHz INTRC clock source frequency, such as the WDT, Fail-Safe Clock Monitor and peripherals, will also be affected by the change in frequency.

#### **REGISTER 4-1: OSCTUNE: OSCILLATOR TUNING REGISTER (ADDRESS 90h)**

| -11 7-1. | COCIONE           |              |                 |             |              |               | ,            |       |

|----------|-------------------|--------------|-----------------|-------------|--------------|---------------|--------------|-------|

|          | U-0               | U-0          | R/W-0           | R/W-0       | R/W-0        | R/W-0         | R/W-0        | R/W-0 |

|          | —                 | _            | TUN5            | TUN4        | TUN3         | TUN2          | TUN1         | TUN0  |

|          | bit 7             |              |                 |             |              |               |              | bit 0 |

| bit 7-6  | Unimplem          | ented: Read  | <b>d as</b> '0' |             |              |               |              |       |

| bit 5-0  | TUN<5:0>:         | Frequency    | Tuning bits     |             |              |               |              |       |

|          | 011111 <b>=  </b> | Maximum fro  | equency         |             |              |               |              |       |

|          | 011110 =          |              |                 |             |              |               |              |       |

|          | •                 |              |                 |             |              |               |              |       |

|          | •                 |              |                 |             |              |               |              |       |

|          | •                 |              |                 |             |              |               |              |       |

|          | 000001 =          |              |                 |             |              |               |              |       |

|          |                   | Center frequ | iency. Oscilla  | ator module | is running a | t the calibra | ted frequend | cy.   |

|          | 111111 =          |              |                 |             |              |               |              |       |

|          | •                 |              |                 |             |              |               |              |       |

|          | •                 |              |                 |             |              |               |              |       |

|          | •                 |              |                 |             |              |               |              |       |

|          | 100000 = I        | Minimum fre  | quency          |             |              |               |              |       |

|          |                   |              |                 |             |              |               |              |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.6.5 CLOCK TRANSITION SEQUENCE

The following are three different sequences for switching the internal RC oscillator frequency:

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- 1. IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for **eight** falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for **eight** falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to a different INTOSC/ INTOSC postscaler frequency.

- The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for **eight** falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. The IOFS bit is set.

- 5. Oscillator switchover is complete.

- 4.6.6 OSCILLATOR DELAY UPON POWER-UP, WAKE-UP AND CLOCK SWITCHING

Table 4-3 shows the different delays invoked for various clock switching sequences. It also shows the delays invoked for POR and wake-up.

| Clo                  | ck Switch                                 | Fraguanay               | Oscillator Delay                               | Comments                                                                                |  |  |  |

|----------------------|-------------------------------------------|-------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| From                 | То                                        | Frequency               | Uscillator Delay                               | Comments                                                                                |  |  |  |

| Sleep/DOP            | INTRC<br>T1OSC                            | 31.25 kHz<br>32.768 kHz | CPU Start-up <sup>(1)</sup>                    |                                                                                         |  |  |  |

| Sleep/POR            | INTOSC/INTOSC<br>Postscaler 125 kHz-8 MHz |                         | 4 ms (approx.) and CPU Start-up <sup>(1)</sup> | Following a wake-up from Sleep mode or POR, CPU start-up is invoked to                  |  |  |  |

| INTRC/<br>Sleep      | EC, RC                                    | DC – 20 MHz             |                                                | allow the CPU to become ready for code execution.                                       |  |  |  |

| INTRC<br>(31.25 kHz) | EC, RC                                    | DC – 20 MHz             |                                                |                                                                                         |  |  |  |

| Sleep                | LP, XT, HS                                | 32.768 kHz-20 MHz       | 1024 Clock Cycles                              | Following a change from INTRC, the OST count of 1024 cycles must occur.                 |  |  |  |

| INTRC<br>(31.25 kHz) | INTOSC/INTOSC<br>Postscaler               | 125 kHz-8 MHz           | 4 ms (approx.)                                 | Refer to <b>Section 4.6.4 "Modifying the</b><br><b>IRCF Bits</b> " for further details. |  |  |  |

### TABLE 4-3: OSCILLATOR DELAY EXAMPLES

**Note 1:** The 5 µs-10 µs start-up delay is based on a 1 MHz system clock.

### 4.7 Power-Managed Modes

### 4.7.1 RC\_RUN MODE

When SCS bits are configured to run from the INTRC, a clock transition is generated if the system clock is not already using the INTRC. The event will clear the OSTS bit and switch the system clock from the primary system clock (if SCS<1:0> = 00) determined by the value contained in the configuration bits, or from the T1OSC (if SCS<1:0> = 01) to the INTRC clock option and shut-down the primary system clock to conserve power. Clock switching will not occur if the primary system clock is already configured as INTRC.

If the system clock does not come from the INTRC (31.25 kHz) when the SCS bits are changed and the IRCF bits in the OSCCON register are configured for a frequency other than INTRC, the frequency may not be stable immediately. The IOFS bit (OSCCON<2>) will be set when the INTOSC or postscaler frequency is stable, after 4 ms (approx.).

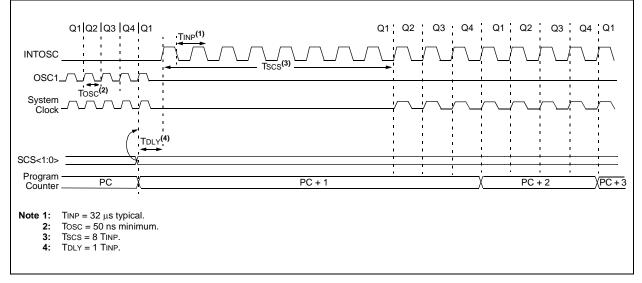

After a clock switch has been executed, the OSTS bit is cleared, indicating a low-power mode and the device does not run from the primary system clock. The internal Q clocks are held in the Q1 state until eight falling edge clocks are counted on the INTRC oscillator. After the eight clock periods have transpired, the clock input to the Q clocks is released and operation resumes (see Figure 4-7).

# PIC16F7X7

NOTES:

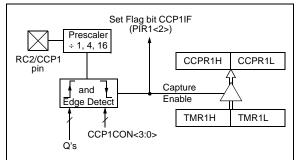

# 9.4 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.4.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an |

|-------|-----------------------------------------|

|       | output, a write to the port can cause a |

|       | capture condition.                      |

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 9.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

### 9.4.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

### 9.4.4 CCP PRESCALER

There are four prescaler settings specified by bits, CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ;the new prescaler      |

|       |             | ;move value and CCP ON  |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ;value                  |

|       |             |                         |

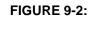

## 9.5 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- clear TMR1H and TMR1L registers

- NOT set interrupt flag bit, TMR1IF (PIR1<0>)

- (for CCP2 only) set the GO/DONE bit (ADCON0<2>)

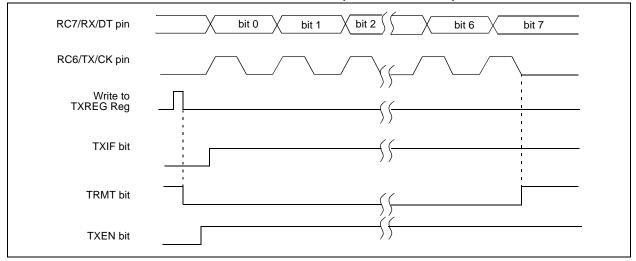

#### 10.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times, as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit (SSPCON1<4>).

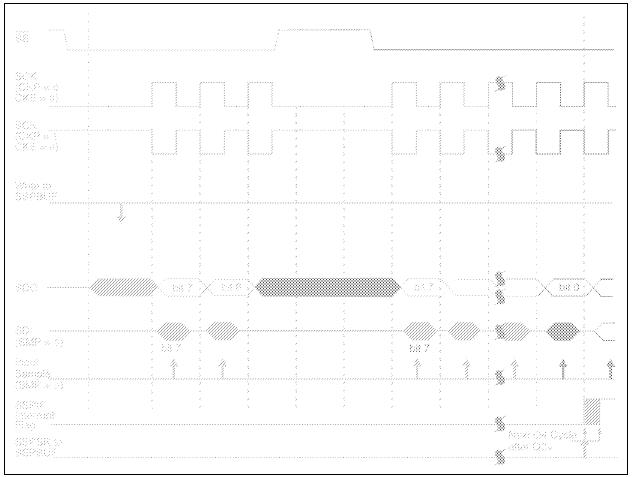

#### 10.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 4h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch

must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

#### FIGURE 10-4: SLAVE SYNCHRONIZATION WAVEFORM

# PIC16F7X7

| ER 11-2: | RCSTA: R                        |                                                                                      |               |               |              |              |                |              |  |  |  |

|----------|---------------------------------|--------------------------------------------------------------------------------------|---------------|---------------|--------------|--------------|----------------|--------------|--|--|--|

|          | R/W-0                           | R/W-0                                                                                | R/W-0         | R/W-0         | R/W-0        | R-0          | R-0            | R-x          |  |  |  |

|          | SPEN                            | RX9                                                                                  | SREN          | CREN          | ADDEN        | FERR         | OERR           | RX9D         |  |  |  |

|          | bit 7                           |                                                                                      |               |               |              |              |                | bit 0        |  |  |  |

| bit 7    | SPEN: Ser                       | ial Port Ena                                                                         | ble bit       |               |              |              |                |              |  |  |  |

|          | -                               | oort enabled                                                                         |               | RC7/RX/D      | Fand RC6/T   | X/CK pins a  | as serial port | pins)        |  |  |  |

| bit 6    | <b>RX9</b> : 9-bit              | Receive Ena                                                                          | able bit      |               |              |              |                |              |  |  |  |

|          |                                 | <ul> <li>1 = Selects 9-bit reception</li> <li>0 = Selects 8-bit reception</li> </ul> |               |               |              |              |                |              |  |  |  |

| bit 5    | SREN: Sin                       | gle Receive                                                                          | Enable bit    |               |              |              |                |              |  |  |  |

|          | <u>Asynchron</u><br>Don't care. | Asynchronous mode:                                                                   |               |               |              |              |                |              |  |  |  |

|          | 1 = Enable<br>0 = Disable       | <u>us mode – N</u><br>s single rece<br>es single rec<br>cleared after                | eive          | complete.     |              |              |                |              |  |  |  |

|          | <u>Synchrono</u><br>Don't care. | us mode – S                                                                          | <u>Slave:</u> |               |              |              |                |              |  |  |  |

| bit 4    | CREN: Cor                       | ntinuous Re                                                                          | ceive Enable  | e bit         |              |              |                |              |  |  |  |

|          |                                 | ous mode:<br>s continuou<br>es continuou                                             |               |               |              |              |                |              |  |  |  |

|          |                                 |                                                                                      |               | til enable bi | CREN is cle  | eared (CRE   | N overrides    | SREN)        |  |  |  |

| bit 3    | ADDEN: A                        | ddress Dete                                                                          | ect Enable bi | t             |              |              |                |              |  |  |  |

|          | Asynchron                       | ous mode 9                                                                           | -bit (RX9 = 1 | <u>.):</u>    |              |              |                |              |  |  |  |

|          | RSR<                            | 8> is set                                                                            |               |               | upt and load |              |                |              |  |  |  |

|          |                                 |                                                                                      |               | l bytes are r | eceived and  | ninth bit ca | n be used a    | s parity bit |  |  |  |

| bit 2    |                                 | ming Error t                                                                         |               |               |              |              |                |              |  |  |  |

|          | 1 = Framin<br>0 = No frar       |                                                                                      | be updated    | by reading    | RCREG regi   | ster and red | ceiving next   | valid byte)  |  |  |  |

| bit 1    | OERR: OV                        | errun Error I                                                                        | pit           |               |              |              |                |              |  |  |  |

|          | 1 = Overru<br>0 = No ove        |                                                                                      | be cleared b  | by clearing l | oit CREN)    |              |                |              |  |  |  |

| bit 0    | <b>RX9D:</b> 9th                | bit of Receiv                                                                        | ved Data      |               |              |              |                |              |  |  |  |

|          | Can be par                      | ity bit but m                                                                        | ust be calcul | lated by use  | er firmware. |              |                |              |  |  |  |

|          | Legend:                         |                                                                                      |               |               |              |              |                |              |  |  |  |

|          | R = Reada                       | ble bit                                                                              | W = W         | ritable bit   | U = Unim     | plemented    | bit, read as   | '0'          |  |  |  |

|          |                                 | at POR                                                                               |               | t is set      | '0' = Bit is | -            | ,              | -            |  |  |  |

| Baud        | Fosc = 8 MHz<br>Baud |            |                             | F      | Fosc = 4 MHz |                             |        | Fosc = 2 MHz |                             |       | Fosc = 1 MHz |                             |  |

|-------------|----------------------|------------|-----------------------------|--------|--------------|-----------------------------|--------|--------------|-----------------------------|-------|--------------|-----------------------------|--|

| Rate<br>(K) | Kbaud                | %<br>Error | SPBRG<br>Value<br>(decimal) | Kbaud  | %<br>Error   | SPBRG<br>Value<br>(decimal) | Kbaud  | %<br>Error   | SPBRG<br>Value<br>(decimal) | Kbaud | %<br>Error   | SPBRG<br>Value<br>(decimal) |  |

| 0.3         | NA                   | _          | _                           | 0.300  | 0            | 207                         | 0.300  | 0            | 103                         | 0.300 | 0            | 51                          |  |

| 1.2         | 1.202                | +0.16      | 103                         | 1.202  | +0.16        | 51                          | 1.202  | +0.16        | 25                          | 1.202 | +0.16        | 12                          |  |

| 2.4         | 2.404                | +0.16      | 51                          | 2.404  | +0.16        | 25                          | 2.404  | +0.16        | 12                          | 2.232 | -6.99        | 6                           |  |

| 9.6         | 9.615                | +0.16      | 12                          | 8.929  | -6.99        | 6                           | 10.417 | +8.51        | 2                           | NA    | _            | _                           |  |

| 19.2        | 17.857               | -6.99      | 6                           | 20.833 | +8.51        | 2                           | NA     | _            | —                           | NA    | —            | —                           |  |

| 28.8        | 31.250               | +8.51      | 3                           | 31.250 | +8.51        | 1                           | 31.250 | +8.51        | 0                           | NA    | _            | _                           |  |

| 38.4        | 41.667               | +8.51      | 2                           | NA     | _            | _                           | NA     | —            | _                           | NA    | _            | _                           |  |

| 57.6        | 62.500               | +8.51      | 1                           | 62.500 | 8.51         | 0                           | NA     | _            | _                           | NA    | —            | _                           |  |

### TABLE 11-5: INTRC BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

# TABLE 11-6: INTRC BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| Baud        | Fosc = 8 MHz |            |                             | Fosc = 4 MHz |            |                             | Fosc = 2 MHz |            |                             | Fosc = 1 MHz |            |                             |

|-------------|--------------|------------|-----------------------------|--------------|------------|-----------------------------|--------------|------------|-----------------------------|--------------|------------|-----------------------------|

| Rate<br>(K) | Kbaud        | %<br>Error | SPBRG<br>Value<br>(decimal) |

| 0.3         | NA           | _          | _                           | NA           | _          | _                           | NA           | _          | _                           | 0.300        | 0          | 207                         |

| 1.2         | NA           | —          | —                           | 1.202        | +0.16      | 207                         | 1.202        | +0.16      | 103                         | 1.202        | +0.16      | 51                          |

| 2.4         | 2.404        | +0.16      | 207                         | 2.404        | +0.16      | 103                         | 2.404        | +0.16      | 51                          | 2.404        | +0.16      | 25                          |

| 9.6         | 9.615        | +0.16      | 51                          | 9.615        | +0.16      | 25                          | 9.615        | +0.16      | 12                          | 8.929        | -6.99      | 6                           |

| 19.2        | 19.231       | +0.16      | 25                          | 19.231       | +0.16      | 12                          | 17.857       | -6.99      | 6                           | 20.833       | +8.51      | 2                           |

| 28.8        | 29.412       | +2.12      | 16                          | 27.778       | -3.55      | 8                           | 31.250       | +8.51      | 3                           | 31.250       | +8.51      | 1                           |

| 38.4        | 38.462       | +0.16      | 12                          | 35.714       | -6.99      | 6                           | 41.667       | +8.51      | 2                           | NA           | _          | _                           |

| 57.6        | 55.556       | -3.55      | 8                           | 62.500       | +8.51      | 3                           | 62.500       | +8.51      | 1                           | 62.500       | +8.51      | 0                           |

| Address                | Name       | Bit 7                | Bit 6    | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      | Valu<br>all o<br>Res | ther |

|------------------------|------------|----------------------|----------|-------------|--------|-------|--------|--------|--------|---------------|------|----------------------|------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCO<br>N | GIE                  | PEIE     | TMR0IE      | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000          | 000x | 0000                 | 000u |

| 0Ch                    | PIR1       | PSPIF <sup>(1)</sup> | ADIF     | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000          | 0000 | 0000                 | 0000 |

| 18h                    | RCSTA      | SPEN                 | RX9      | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000          | 000x | 0000                 | 000x |

| 19h                    | TXREG      | AUSART               | Transmit | Register    |        |       |        |        |        | 0000          | 0000 | 0000                 | 0000 |

| 8Ch                    | PIE1       | PSPIE <sup>(1)</sup> | ADIE     | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000          | 0000 | 0000                 | 0000 |

| 98h                    | TXSTA      | CSRC                 | TX9      | TXEN        | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000          | -010 | 0000                 | -010 |

| 99h                    | SPBRG      | Baud Rate            | e Genera | tor Registe | ər     |       |        |        |        | 0000          | 0000 | 0000                 | 0000 |

Legend: x = unknown, — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

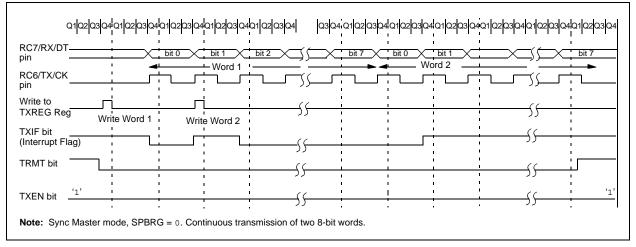

#### FIGURE 11-9: SYNCHRONOUS TRANSMISSION

#### FIGURE 11-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

© 2003-2013 Microchip Technology Inc.

# 15.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Low-Voltage Detect (LVD)

- Interrupts

- Watchdog Timer (WDT)

- Two-Speed Start-up

- Fail-Safe Clock Monitor

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT) which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes and is enabled or disabled using a configuration bit. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

Additional information on special features is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023).

## 15.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory locations 2007h and 2008h.

The user will note that address 2007h is beyond the user program memory space which can be accessed only during programming.

# 16.0 INSTRUCTION SET SUMMARY

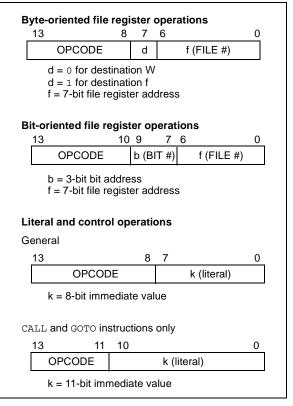

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories are presented in Figure 16-1, while the various opcode fields are summarized in Table 16-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> Assembler. A complete description of each instruction is also available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16F7X7 products, do not use |

|       | the OPTION and TRIS instructions.     |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 16.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

# TABLE 16-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                |