### Microchip Technology - PIC16F767T-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

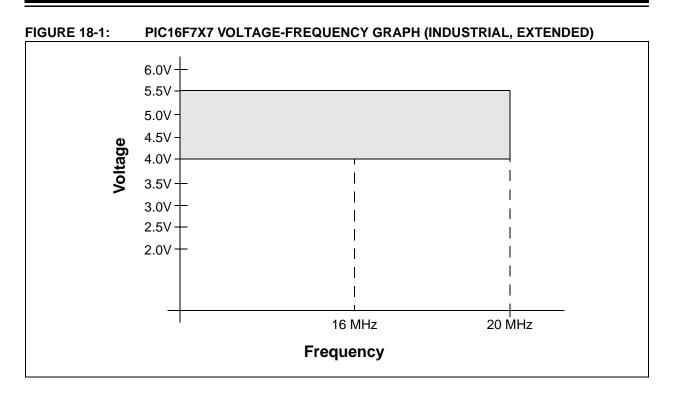

| Detailo                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f767t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                          | PDIP<br>Pin # | QFN<br>Pin #    | TQFP<br>Pin #     | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                  |

|-----------------------------------|---------------|-----------------|-------------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------|

|                                   |               |                 |                   |               |                        | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs. |

| RB0/INT/AN12<br>RB0               | 33            | 9               | 8                 | I/O           | TTL/ST(1)              | Digital I/O.                                                                                                 |

| INT<br>AN12                       |               |                 |                   |               |                        | External interrupt.<br>Analog input channel 12.                                                              |

| RB1/AN10                          | 34            | 10              | 9                 |               | TTL                    |                                                                                                              |

| RB1<br>AN10                       |               |                 |                   | I/O<br>I      |                        | Digital I/O.<br>Analog input channel 10.                                                                     |

| RB2/AN8                           | 35            | 11              | 10                |               | TTL                    |                                                                                                              |

| RB2<br>AN8                        |               |                 |                   | I/O<br>I      |                        | Digital I/O.<br>Analog input channel 8.                                                                      |

| RB3/CCP2/AN9<br>RB3               | 36            | 12              | 11                | I/O           | TTL                    | Digital I/O.                                                                                                 |

| CCP2 <sup>(5)</sup><br>AN9        |               |                 |                   | I/O           |                        | CCP2 capture input, compare output, PWM output<br>Analog input channel 9.                                    |

| RB4/AN11                          | 37            | 14              | 14                |               | TTL                    |                                                                                                              |

| RB4<br>AN11                       |               |                 |                   | I/O<br>I      |                        | Digital I/O.<br>Analog input channel 11                                                                      |

| RB5/AN13/CCP3                     | 38            | 15              | 15                |               | TTL                    |                                                                                                              |

| RB5<br>AN13                       |               |                 |                   | I/O<br>I      |                        | Digital I/O.<br>Analog input channel 13.                                                                     |

| CCP3                              |               |                 |                   | I             |                        | CCP3 capture input, compare output, PWM output                                                               |

| RB6/PGC<br>RB6                    | 39            | 16              | 16                | I/O           | TTL/ST <sup>(2)</sup>  | Digital I/O.                                                                                                 |

| PGC                               |               |                 |                   | I/O           |                        | In-Circuit Debugger and ICSP™ programming clock.                                                             |

| RB7/PGD                           | 40            | 17              | 17                |               | TTL/ST <sup>(2)</sup>  |                                                                                                              |

| RB7<br>PGD                        |               |                 |                   | I/O<br>I/O    |                        | Digital I/O.<br>In-Circuit Debugger and ICSP programming<br>data.                                            |

| Legend: I = input<br>— = Not used | 4             | O = ou<br>TTL = | ıtput<br>TTL inpu | ı             | I/O = inpu<br>ST = Sch | it/output P = power<br>mitt Trigger input                                                                    |

### TABLE 1-3: PIC16F747 AND PIC16F777 PINOUT DESCRIPTION (CONTINUED)

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as a general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

5: Pin location of CCP2 is determined by the CCPMX bit in Configuration Word Register 1.

### 2.2.2.8 PCON Register

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

Note: BOR is unknown on POR. It must be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is not predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration Word register).

### REGISTER 2-8: PCON: POWER CONTROL/STATUS REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|--------|-------|-------|

| _     | —   |     |     | _   | SBOREN | POR   | BOR   |

| bit 7 |     |     |     |     |        |       | bit 0 |

- bit 7-3 Unimplemented: Read as '0'

- bit 2 **SBOREN**: Software Brown-out Reset Enable bit

- If BORSEN in Configuration Word 2 is a '1' and BOREN in Configuration Word 1 is '0': 1 = BOR enabled 0 = BOR disabled

- bit 1 **POR**: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 **BOR**: Brown-out Reset Status bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 5.4 PORTD and TRISD Registers

This section is not applicable to the PIC16F737 or PIC16F767.

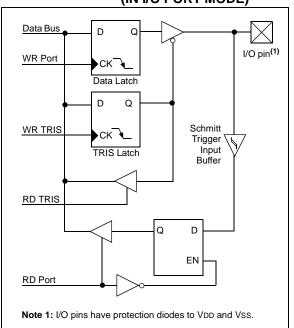

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

### FIGURE 5-18: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit#  | Buffer Type           | Function                                            |

|----------|-------|-----------------------|-----------------------------------------------------|

| RD0/PSP0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 0. |

| RD1/PSP1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 1. |

| RD2/PSP2 | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 2. |

| RD3/PSP3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 3. |

| RD4/PSP4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 4. |

| RD5/PSP5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 5. |

| RD6/PSP6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 6. |

| RD7/PSP7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin or Parallel Slave Port bit 7. |

### TABLE 5-7: PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH POR |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Address | Name  | Bit 7 | Bit 6    | Bit 5     | Bit 4     | Bit 3                                  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------|-------|----------|-----------|-----------|----------------------------------------|-------|-------|-------|-----------------------|---------------------------------|

| 08h     | PORTD | RD7   | RD6      | RD5       | RD4       | RD3                                    | RD2   | RD1   | RD0   | xxxx xxxx             | uuuu uuuu                       |

| 88h     | TRISD | PORTE | D Data D | Direction | 1111 1111 | 1111 1111                              |       |       |       |                       |                                 |

| 89h     | TRISE | IBF   | OBF      | IBOV      | PSPMODE   | PSPMODE -(1) PORTE Data Direction bits |       |       |       |                       | 0000 1111                       |

Legend: x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: RE3 is an input only. The state of the TRISE3 bit has no effect and will always read '1'.

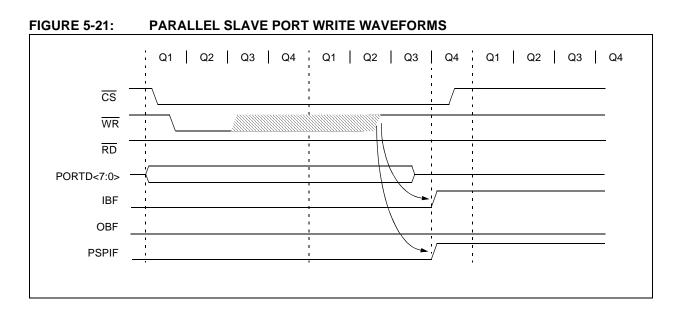

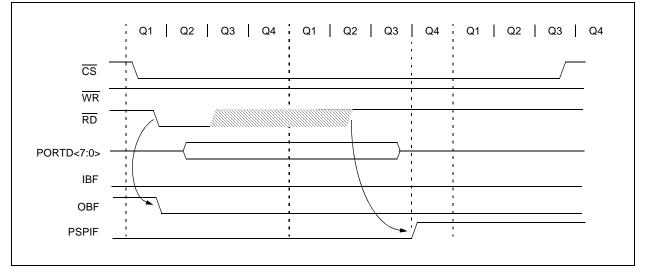

### FIGURE 5-22: PARALLEL SLAVE PORT READ WAVEFORMS

### TABLE 5-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4          | Bit 3     | Bit 2                     | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------|----------|-----------|----------------|-----------|---------------------------|--------|--------|-----------------------|---------------------------------|

| 08h     | PORTD  | Port Data            | Latch wh | en writte | n: Port pins v | vhen read |                           |        |        | xxxx xxxx             | uuuu uuuu                       |

| 09h     | PORTE  | _                    | _        |           | —              | RE3       | RE2                       | RE1    | RE0    | x000                  | x000                            |

| 89h     | TRISE  | IBF                  | OBF      | IBOV      | PSPMODE        | (2)       | PORTE Data Direction bits |        |        | 0000 1111             | 0000 1111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF           | SSPIF     | CCP1IF                    | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE           | SSPIE     | CCP1IE                    | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 9Fh     | ADCON1 | ADFM                 | ADCS2    | VCFG1     | VCFG0          | PCFG3     | PCFG2                     | PCFG1  | PCFG0  | 0000 0000             | 0000 0000                       |

**Legend:** x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F737/767; always maintain these bits clear.

2: RE3 is an input only. The state of the TRISE3 bit has no effect and will always read '1'.

© 2003-2013 Microchip Technology Inc.

NOTES:

### 9.6 PWM Mode (PWM)

In Pulse-Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

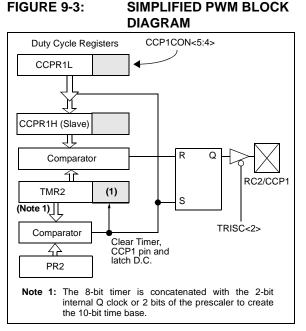

Figure 9-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 9.6.3** "**Setup for PWM Operation**".

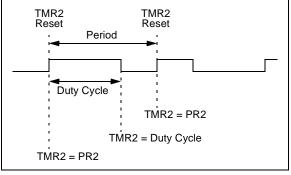

A PWM output (Figure 9-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### 9.6.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

### **EQUATION 9-1:**

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 9.4    |

|-------|-------------------------------------------|

|       | "Capture Mode") is not used in the deter- |

|       | mination of the PWM frequency. The post-  |

|       | scaler could be used to have a servo      |

|       | update rate at a different frequency than |

|       | the PWM output.                           |

### 9.6.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

### **EQUATION 9-2:**

```

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>)•

Tosc • (TMR2 Prescale Value)

```

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

### 10.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a Transmit/Receive Shift register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>) and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the

data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision detect bit, WCOL (SSPCON<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 10-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

### EXAMPLE 10-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been received (transmit complete)? |

|------|-------|-------------|----------------------------------------------|

|      | BRA   | LOOP        | ;No                                          |

|      | MOVF  | SSPBUF, W   | ;WREG reg = contents of SSPBUF               |

|      | MOVWF | RXDATA      | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W   | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSPBUF      | ;New data to xmit                            |

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

### 10.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON<4>). See **Section 10.4.4** "Clock Stretching" for more detail.

### 10.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see **Section 10.4.4 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 10-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

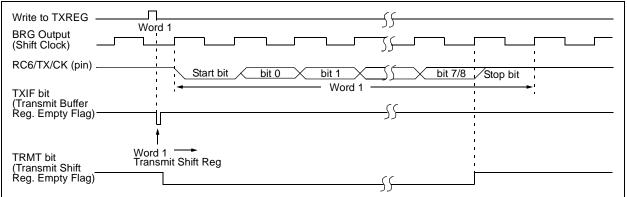

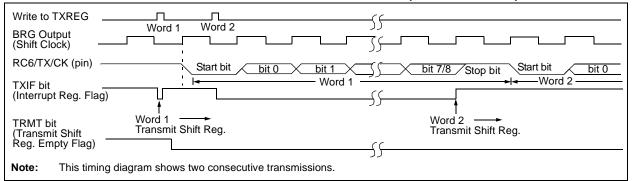

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse. When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (see Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

### FIGURE 11-2: ASYNCHRONOUS MASTER TRANSMISSION

### TABLE 11-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|----------|-------------|--------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE      | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                       |

| 19h                    | TXREG  | AUSART -             | Transmit | Data Regi   | ister  |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN        | SYNC   | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Genera | tor Registe | er     |       |        |        |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

| REGISTER 12-1: | ADCON0:                                                                                                                                                                                         | A/D CONT                     | ROL REG            | ISTER 0 (A     | DDRESS         | 1Fh)                           |                |       |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------|----------------|----------------|--------------------------------|----------------|-------|--|--|--|

|                | R/W-0                                                                                                                                                                                           | R/W-0                        | R/W-0              | R/W-0          | R/W-0          | R/W-0                          | R/W-0          | R/W-0 |  |  |  |

|                | ADCS1                                                                                                                                                                                           | ADCS0                        | CHS2               | CHS1           | CHS0           | GO/DONE                        | CHS3           | ADON  |  |  |  |

|                | bit 7                                                                                                                                                                                           |                              |                    |                |                |                                |                | bit 0 |  |  |  |

| bit 7-6        | ADCS1:AI                                                                                                                                                                                        | D <b>CS0:</b> A/D C          | onversion C        | lock Select I  | bits           |                                |                |       |  |  |  |

|                | If ADCS2 =                                                                                                                                                                                      | = 0:                         |                    |                |                |                                |                |       |  |  |  |

|                | 000 = Fos                                                                                                                                                                                       |                              |                    |                |                |                                |                |       |  |  |  |

|                | 001 = Fos<br>010 = Fos                                                                                                                                                                          |                              |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | (clock derive                | d from an R        | C oscillation  | n)             |                                |                |       |  |  |  |

|                | If ADCS2 =                                                                                                                                                                                      | <u>= 1:</u>                  |                    |                |                |                                |                |       |  |  |  |

|                | 00 = Fosc                                                                                                                                                                                       |                              |                    |                |                |                                |                |       |  |  |  |

|                | 01 = Fosc<br>10 = Fosc                                                                                                                                                                          |                              |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | clock derived                | I from an RC       | coscillation)  |                |                                |                |       |  |  |  |

| bit 5-3        | CHS<2:0>                                                                                                                                                                                        | : Analog Cha                 | nnel Select        | bits           |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 00 (AN                 | ,                  |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 01 (AN<br>annel 02 (AN |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 03 (AN                 | ,                  |                |                |                                |                |       |  |  |  |

|                | 0100 = Ch                                                                                                                                                                                       | annel 04 (AN                 | <b>1</b> 4)        |                |                |                                |                |       |  |  |  |

|                | 0101 = Ch                                                                                                                                                                                       | annel 05 (AN                 | 15) <sup>(1)</sup> |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 06 (AN<br>annel 07 (AN |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 08 (AN                 |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 09 (AN                 |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 10 (AN<br>annel 11 (AN | ,                  |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 12 (AN                 |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | annel 13 (AN                 | <b>I</b> 13)       |                |                |                                |                |       |  |  |  |

|                | 111x = Un                                                                                                                                                                                       |                              |                    |                |                |                                |                |       |  |  |  |

|                | Note 1:                                                                                                                                                                                         | •                            | ) will result i    |                | •              | product varia<br>on as unimple | •              |       |  |  |  |

| bit 2          | GO/DONE                                                                                                                                                                                         | : A/D Conver                 | sion Status        | bit            |                |                                |                |       |  |  |  |

|                | <ul> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle. This bit is automatically cleared by hardware when the A/D conversion has completed.</li> </ul> |                              |                    |                |                |                                |                |       |  |  |  |

|                | 0 = A/D co                                                                                                                                                                                      | onversion cor                | npleted/not i      | n progress     |                |                                |                |       |  |  |  |

| bit 1          | CHS<3>: /                                                                                                                                                                                       | Analog Chani                 | nel Select bi      | t (see bit 5-3 | B for bit sett | ings)                          |                |       |  |  |  |

| bit 0          |                                                                                                                                                                                                 | D Conversion                 |                    |                |                |                                |                |       |  |  |  |

|                |                                                                                                                                                                                                 | nverter modu                 |                    | 0              | on orating o   | rroot                          |                |       |  |  |  |

|                | 0 = A/D converter is shut-off and consumes no operating current                                                                                                                                 |                              |                    |                |                |                                |                |       |  |  |  |

|                | Legend:                                                                                                                                                                                         |                              |                    |                |                |                                |                |       |  |  |  |

|                | R = Reada                                                                                                                                                                                       | able bit                     | W = W              | ritable bit    | U = Unir       | nplemented b                   | it, read as '( | )'    |  |  |  |

|                | -n = Value                                                                                                                                                                                      |                              |                    | it is set      |                | •                              | x = Bit is ur  |       |  |  |  |

|                |                                                                                                                                                                                                 |                              | · - D              |                | <b>2</b> – Bit |                                |                |       |  |  |  |

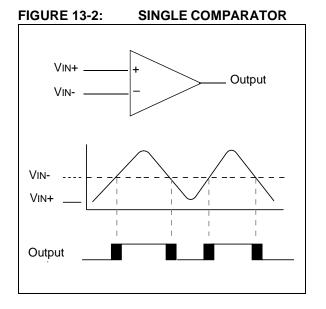

### 13.2 Comparator Operation

A single comparator is shown in Figure 13-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 13-2 represent the uncertainty due to input offsets and response time.

### 13.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 13-2).

### 13.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

### 13.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. **Section 14.0 "Comparator Voltage Reference Module"** contains a detailed description of the comparator voltage reference module that provides this signal. The internal reference signal is used when comparators are in mode CM<2:0> = 110 (Figure 13-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

### 13.4 Comparator Response Time

Response time is the minimum time after selecting a new reference voltage, or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Section 18.0 "Electrical Characteristics").

### 13.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexors in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 13-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4:>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

- **3:** RA4 is an open collector I/O pin. When used as an output, a pull-up resistor is required.

| REGIST            | FER 1  | 5-2: (    | CONFIG                                | URATI     | ON WO    | ORD RI    | EGISTER 2            | 2 (ADD    | RESS      | 2008h)      |            |          |       |

|-------------------|--------|-----------|---------------------------------------|-----------|----------|-----------|----------------------|-----------|-----------|-------------|------------|----------|-------|

| U-1               | U-1    | U-1       | U-1                                   | U-1       | U-1      | U-1       | R/P-1                | U-1       | U-1       | U-1         | U-1        | R/P-1    | R/P-1 |

|                   | _      | _         | —                                     | —         | _        |           | BORSEN               | _         | —         | _           | —          | IESO     | FCMEN |

| bit 13            |        |           |                                       |           |          |           |                      |           |           |             |            |          | bit 0 |

| bit 13-7<br>bit 6 | BOR    | SEN: Br   | i <b>ted:</b> Rea                     | Reset S   | oftware  |           | bit<br>for the funct | ion of th | nic hit   |             |            |          |       |

| bit 5-2           |        |           | ited: Rea                             |           | U        | 1, DIL U  |                      |           | lis bit.  |             |            |          |       |

| bit 1             | 1 = lr | nternal E | al Extern<br>External S<br>External S | Switchov  | ver mode | e enable  |                      |           |           |             |            |          |       |

| bit 0             | 1 = F  | ail-Safe  | -Safe Cl<br>Clock M<br>Clock M        | onitor er | nabled   | ble bit   |                      |           |           |             |            |          |       |

|                   | Lege   | end:      |                                       |           |          |           |                      |           |           |             |            |          |       |

|                   | R = I  | Readabl   | e bit                                 |           | W = 1    | Writable  | e bit                | U = Uni   | mpleme    | nted bit, i | read as '  | 0'       |       |

|                   | -n =   | Value at  | POR                                   |           | '1' =    | Bit is se | t                    | 0' = Bit  | is cleare | ed          | x = Bit is | s unknov | vn    |

| -             |                     |                    | -                   |                    |                    |

|---------------|---------------------|--------------------|---------------------|--------------------|--------------------|

| Oscillator    | Power-u             | qu                 | Brown-out           | Reset              | Wake-up from       |

| Configuration | PWRTE = 0           | PWRTE = 1          | PWRTE = 0           | <b>PWRTE =</b> 1   | Sleep              |

| XT, HS, LP    | TPWRT + 1024 • TOSC | 1024 • Tosc        | TPWRT + 1024 • Tosc | 1024 • Tosc        | 1024 • Tosc        |

| EXTRC, INTRC  | TPWRT               | 5-10 μs <b>(1)</b> | TPWRT               | 5-10 μs <b>(1)</b> | 5-10 μs <b>(1)</b> |

| T1OSC         | —                   | _                  | _                   | _                  | 5-10 μs <b>(1)</b> |

TABLE 15-1: TIME-OUT IN VARIOUS SITUATIONS

Note 1: CPU start-up is always invoked on POR, BOR and wake-up from Sleep. The 5 μs-10 μs delay is based on a 1 MHz system clock.

### TABLE 15-2: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | ТО | PD |                                                                   |

|-----|-----|----|----|-------------------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                                         |

| 1   | 0   | 1  | 1  | Brown-out Reset                                                   |

| 1   | 1   | 0  | 1  | WDT Reset                                                         |

| 1   | 1   | 0  | 0  | WDT Wake-up                                                       |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                                |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep           |

**Legend:** u = unchanged, x = unknown

### TABLE 15-3: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 10x              |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uuu              |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uuu              |

| WDT Reset                          | 000h                  | 0000 luuu          | uuu              |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uuu              |

| Brown-out Reset                    | 000h                  | 0001 1xxx          | 1u0              |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uuu              |

**Legend:** u = unchanged, x = unknown, — = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

### REGISTER 15-4: WDTCON: WATCHDOG TIMER CONTROL REGISTER (ADDRESS 105h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-1  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | SWDTEN |

| bit 7 |     |     |        |        |        |        | bit 0  |

- bit 7-5 Unimplemented: Read as '0'

- bit 4-1 WDTPS<3:0>: Watchdog Timer Period Select bits

- 0000 = 1:32 Prescale rate

- 0001 = 1:64 Prescale rate

- 0010 = 1:128 Prescale rate

- 0011 = 1:256 Prescale rate

- 0100 = 1:512 Prescale rate

- 0101 = 1:1024 Prescale rate

- 0110 = 1:2048 Prescale rate

- 0111 = 1:4096 Prescale rate

- 1000 = 1:8192 Prescale rate

- 1001 = 1:16394 Prescale rate

- 1010 = 1:32768 Prescale rate 1011 = 1:65536 Prescale rate

- 1100 = 1:1 Prescale rate

bit 0 **SWDTEN:** Software Enable/Disable for Watchdog Timer bit<sup>(1)</sup>

- 1 = WDT is turned on

- 0 = WDT is turned off

- **Note 1:** If WDTEN configuration bit = 1, then WDT is always enabled irrespective of this control bit. If WDTEN configuration bit = 0, then it is possible to turn WDT on/off with this control bit.

| Legend:           |                                                     |                      |                    |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

### TABLE 15-6: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address   | Name                                 | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------|--------------------------------------|-------|--------|-------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 81h, 181h | OPTION_REG                           | RBPU  | INTEDG | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

|           | Configuration<br>bits <sup>(1)</sup> | BORV0 | BOREN  | MCLRE | FOSC2  | PWRTEN | WDTEN  | FOSC1  | FOSC0  | 1111 1111            | 1111 1111                       |

| 105h      | WDTCON                               | -     | _      | —     | WDTPS3 | WDTPS2 | WSTPS1 | WDTPS0 | SWDTEN | 0 1000               | 0 1000                          |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note 1:** See Register 15-1 for operation of these bits.

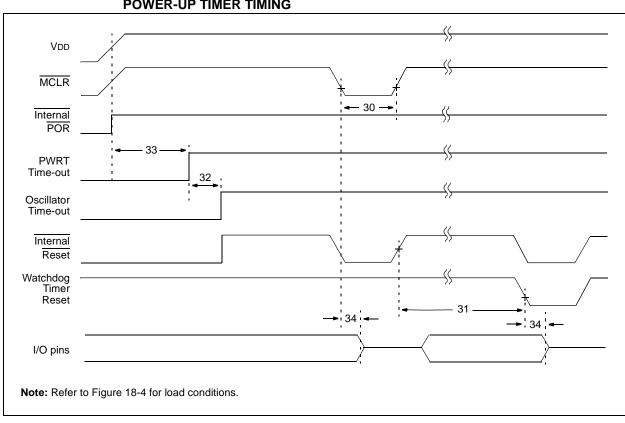

### FIGURE 18-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

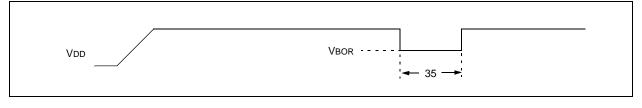

### FIGURE 18-8: BROWN-OUT RESET TIMING

### TABLE 18-6:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Sym   | Characteristic                                           | Min                                                                                                                                                                                                                                                               | Тур†                                                                                                                                                                                                                                                                                                  | Max                                                                                                                                                                                                                                                                                                                                     | Units                                                                                                                                                                                                                                             | Conditions                                                                                                                                                                                                                                                  |

|-------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMCL  | MCLR Pulse Width (low)                                   | 2                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                       | μS                                                                                                                                                                                                                                                | VDD = 5V, -40°C to +85°C                                                                                                                                                                                                                                    |

| Twdt  | Watchdog Timer Time-out Period<br>(no prescaler)         | 13.6                                                                                                                                                                                                                                                              | 16                                                                                                                                                                                                                                                                                                    | 18.4                                                                                                                                                                                                                                                                                                                                    | ms                                                                                                                                                                                                                                                | VDD = 5V, -40°C to +85°C                                                                                                                                                                                                                                    |

| Tost  | Oscillation Start-up Timer Period                        | _                                                                                                                                                                                                                                                                 | 1024 Tosc                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                   | Tosc = OSC1 period                                                                                                                                                                                                                                          |

| TPWRT | Power-up Timer Period                                    | 61.2                                                                                                                                                                                                                                                              | 72                                                                                                                                                                                                                                                                                                    | 82.8                                                                                                                                                                                                                                                                                                                                    | ms                                                                                                                                                                                                                                                | VDD = 5V, -40°C to +85°C                                                                                                                                                                                                                                    |

| Tioz  | I/O High-Impedance from MCLR Low or Watchdog Timer Reset | —                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                     | 2.1                                                                                                                                                                                                                                                                                                                                     | μS                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                             |

| TBOR  | Brown-out Reset Pulse Width                              | 100                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                                                                       | μS                                                                                                                                                                                                                                                | $VDD \leq VBOR (D005)$                                                                                                                                                                                                                                      |

|       | TMCL<br>TWDT<br>TOST<br>TPWRT<br>TIOZ                    | TMCL     MCLR Pulse Width (low)       TWDT     Watchdog Timer Time-out Period<br>(no prescaler)       TOST     Oscillation Start-up Timer Period       TPWRT     Power-up Timer Period       TIOZ     I/O High-Impedance from MCLR Low or<br>Watchdog Timer Reset | TMCL     MCLR Pulse Width (low)     2       TWDT     Watchdog Timer Time-out Period<br>(no prescaler)     13.6       TOST     Oscillation Start-up Timer Period     —       TPWRT     Power-up Timer Period     61.2       TIOZ     I/O High-Impedance from MCLR Low or<br>Watchdog Timer Reset     — | TMCL     MCLR Pulse Width (low)     2       TWDT     Watchdog Timer Time-out Period<br>(no prescaler)     13.6     16       TOST     Oscillation Start-up Timer Period     —     1024 Tosc       TPWRT     Power-up Timer Period     61.2     72       TIOZ     I/O High-Impedance from MCLR Low or<br>Watchdog Timer Reset     —     — | TMCLMCLR Pulse Width (low)2—TWDTWatchdog Timer Time-out Period<br>(no prescaler)13.61618.4TOSTOscillation Start-up Timer Period—1024 Tosc—TPWRTPower-up Timer Period61.27282.8TIOZI/O High-Impedance from MCLR Low or<br>Watchdog Timer Reset—2.1 | TMCLMCLR Pulse Width (low)2—μsTWDTWatchdog Timer Time-out Period<br>(no prescaler)13.61618.4msTOSTOscillation Start-up Timer Period—1024 Tosc——TPWRTPower-up Timer Period61.27282.8msTIOZI/O High-Impedance from MCLR Low or<br>Watchdog Timer Reset——2.1μs |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

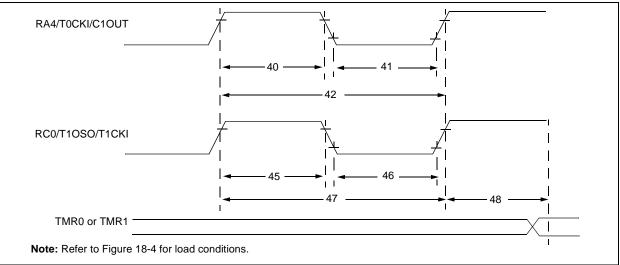

#### **FIGURE 18-9:** TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| Param<br>No. | Symbol    |                                       | Characteristic                                                                  |                | Min                                       | Тур† | Max    | Units | Conditions                            |

|--------------|-----------|---------------------------------------|---------------------------------------------------------------------------------|----------------|-------------------------------------------|------|--------|-------|---------------------------------------|

| 40*          | Тт0Н      | T0CKI High Pulse                      | Width                                                                           | No prescaler   | 0.5 TCY + 20                              |      | —      | ns    | Must also meet                        |

|              |           |                                       |                                                                                 | With prescaler | 10                                        | _    |        | ns    | parameter 42                          |

| 41*          | TT0L      | T0CKI Low Pulse                       | Width                                                                           | No prescaler   | 0.5 TCY + 20                              | _    |        | ns    | Must also meet                        |

|              |           |                                       |                                                                                 | With prescaler | 10                                        | —    | —      | ns    | parameter 42                          |

| 42*          | TT0P      | T0CKI Period                          |                                                                                 | No prescaler   | Tcy + 40                                  | _    | _      | ns    |                                       |

|              |           |                                       |                                                                                 | With prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —    | —      | ns    | N = prescale<br>value (2, 4,,<br>256) |

| 45*          | T⊤1H      | T1CKI High Time                       | Synchronous, Pre                                                                | scaler = 1     | 0.5 Tcy + 20                              |      |        | ns    | Must also meet                        |

|              |           |                                       | Synchronous,                                                                    | PIC16F7X7      | 15                                        | —    | —      | ns    | parameter 47                          |

|              |           |                                       | Prescaler = 2, 4, 8                                                             | PIC16LF7X7     | 25                                        | _    |        | ns    | -                                     |

|              |           |                                       | Asynchronous                                                                    | PIC16F7X7      | 30                                        | _    |        | ns    |                                       |

|              |           |                                       |                                                                                 | PIC16LF7X7     | 50                                        | —    | —      | ns    |                                       |

| 46*          | TT1L      | T1CKI Low Time                        | Synchronous, Pre                                                                | scaler = 1     | 0.5 Tcy + 20                              | —    | —      | ns    | Must also meet                        |

|              |           |                                       | Synchronous,                                                                    | PIC16F7X7      | 15                                        | —    | —      | ns    | parameter 47                          |

|              |           |                                       | Prescaler = 2, 4, 8                                                             | PIC16LF7X7     | 25                                        | _    | _      | ns    |                                       |

|              |           |                                       | Asynchronous                                                                    | PIC16F7X7      | 30                                        | -    | _      | ns    |                                       |

|              |           |                                       |                                                                                 | PIC16LF7X7     | 50                                        | _    | _      | ns    |                                       |

| 47*          | TT1P      | T1P T1CKI Input Synchronous<br>Period | Synchronous                                                                     | PIC16F7X7      | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale<br>value (1, 2, 4, 8)    |

|              |           |                                       |                                                                                 | PIC16LF7X7     | Greater of:<br>50 or <u>Tcy + 40</u><br>N | _    | —      | ns    | N = prescale<br>value (1, 2, 4, 8)    |

|              |           |                                       | Asynchronous                                                                    | PIC16F7X7      | 60                                        |      |        | ns    |                                       |

|              |           |                                       |                                                                                 | PIC16LF7X7     | 100                                       | _    | _      | ns    |                                       |

|              | F⊤1       |                                       | er1 Oscillator Input Frequency Range<br>illator enabled by setting bit T1OSCEN) |                |                                           | _    | 200    | kHz   |                                       |

| 48           | TCKEZTMR1 | Delay from Extern                     | al Clock Edge to Ti                                                             | mer Increment  | 2 Tosc                                    | _    | 7 Tosc | —     |                                       |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param<br>No. | Symbol                | Characterist                                                          | ic                                | Min          | Тур†     | Мах       | Units    | Conditions |

|--------------|-----------------------|-----------------------------------------------------------------------|-----------------------------------|--------------|----------|-----------|----------|------------|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Inpu | t                                 | Тсү          | —        | —         | ns       |            |

| 71*          | TscH                  | SCK Input High Time (Slave r                                          | node)                             | Tcy + 20     |          | —         | ns       |            |

| 72*          | TscL                  | SCK Input Low Time (Slave m                                           | Tcy + 20                          |              | —        | ns        |          |            |

| 73*          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDI Data Input                                          | 100                               | _            | —        | ns        |          |            |

| 74*          | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input t                                         | Data Input to SCK Edge            |              | _        |           | ns       |            |

| 75*          | TDOR                  | SDO Data Output Rise Time                                             | PIC16F7X7<br>PIC16LF7X7           | —            | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 76*          | TDOF                  | SDO Data Output Fall Time                                             | ·                                 | —            | 10       | 25        | ns       |            |

| 77*          | TssH2doZ              | SS ↑ to SDO Output High-Imp                                           | pedance                           | 10           | _        | 50        | ns       |            |

| 78*          | TscR                  | SCK Output Rise Time<br>(Master mode)                                 | <b>°</b>                          |              | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 79*          | TscF                  | SCK Output Fall Time (Maste                                           | r mode)                           | —            | 10       | 25        | ns       |            |

| 80*          | TscH2doV,<br>TscL2doV | SDO Data Output Valid after<br>SCK Edge                               | PIC16F7X7<br>PIC16LF7X7           | —            | _        | 50<br>145 | ns<br>ns |            |

| 81*          | TDOV2SCH,<br>TDOV2SCL | SDO Data Output Setup to SO                                           | SDO Data Output Setup to SCK Edge |              | _        |           | ns       |            |

| 82*          | TssL2doV              | SDO Data Output Valid after $\overline{SS} \downarrow Edge$           |                                   | _            |          | 50        | ns       |            |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                                   |                                   | 1.5 Tcy + 40 | _        | —         | ns       |            |

### TABLE 18-10: SPI MODE REQUIREMENTS

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

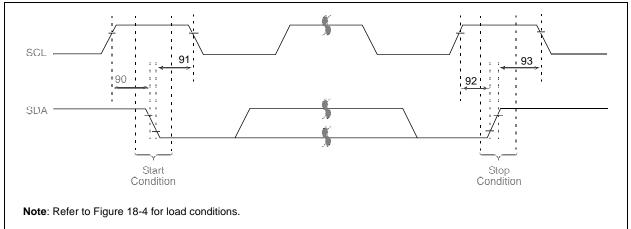

#### I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING FIGURE 18-16:

### APPENDIX A: REVISION HISTORY

### **Revision A (June 2003)**