Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f777-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register also known as the prescaler), the external INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## **REGISTER 2-2: OPTION\_REG: OPTION CONTROL REGISTER (ADDRESS 81h, 181h)**

|        | R/W-1            | R/W-1                               | R/W-1         | R/W-1         | R/W-1                                 | R/W-1     | R/W-1        | R/W-1 |  |  |  |

|--------|------------------|-------------------------------------|---------------|---------------|---------------------------------------|-----------|--------------|-------|--|--|--|

|        | RBPU             | INTEDG                              | TOCS          | TOSE          | PSA                                   | PS2       | PS1          | PS0   |  |  |  |

|        | bit 7            |                                     |               |               |                                       |           |              | bit   |  |  |  |

| oit 7  | <b>RBPU</b> : PO | RTB Pull-up E                       | Enable bit    |               |                                       |           |              |       |  |  |  |

|        |                  | 3 pull-ups are<br>3 pull-ups are    |               | individual po | rt latch valu                         | es        |              |       |  |  |  |

| it 6   | INTEDG: Ir       | nterrupt Edge                       | Select bit    | -             |                                       |           |              |       |  |  |  |

|        |                  | ot on rising ed<br>ot on falling ed | 0             |               |                                       |           |              |       |  |  |  |

| oit 5  |                  | R0 Clock Sour                       |               | it            |                                       |           |              |       |  |  |  |

|        |                  | ion on RA4/T(<br>I instruction cy   |               | CLKO)         |                                       |           |              |       |  |  |  |

| oit 4  |                  | T0SE: TMR0 Source Edge Select bit   |               |               |                                       |           |              |       |  |  |  |

|        |                  | ent on high-to<br>ent on low-to-    |               |               |                                       |           |              |       |  |  |  |

| it 3   | PSA: Pres        | caler Assignm                       | ent bit       |               |                                       |           |              |       |  |  |  |

|        |                  | ler is assigned<br>ler is assigned  |               |               |                                       |           |              |       |  |  |  |

| it 2-0 | PS2:PS0:         | Prescaler Rate                      | e Select bits | 5             |                                       |           |              |       |  |  |  |

|        | Bit Va           | alue TMR0 I                         | Rate WDT      | Rate          |                                       |           |              |       |  |  |  |

|        | 0 0<br>0 0       |                                     | 1:1           |               |                                       |           |              |       |  |  |  |

|        | 00               |                                     | 1:4           |               |                                       |           |              |       |  |  |  |

|        | 01               |                                     |               |               |                                       |           |              |       |  |  |  |

|        | 10<br>10         | 1.01                                |               | -             |                                       |           |              |       |  |  |  |

|        | 11               |                                     | 28 1:6        | 64            |                                       |           |              |       |  |  |  |

|        | 11               | 1 1:25                              | 56   1:1      | 28            |                                       |           |              |       |  |  |  |

|        | Legend:          |                                     |               |               |                                       |           |              |       |  |  |  |

|        | R = Reada        | able bit                            | W = Wr        | ritable bit   | U = Unimp                             | olemented | bit, read as | '0'   |  |  |  |

|        | -n = Value       | at POR                              | '1' = Bit     | is set        | '0' = Bit is cleared x = Bit is unkno |           |              |       |  |  |  |

## 2.2.2.5 PIR1 Register

bit 5

The PIR1 register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

## REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ADDRESS 0Ch)

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |  |

|----------------------|-------|------|------|-------|--------|--------|--------|--|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |  |

| bit 7                |       |      |      |       |        |        | bit 0  |  |

- bit 7 **PSPIF:** Parallel Slave Port Read/Write Interrupt Flag bit<sup>(1)</sup>

- 1 = A read or a write operation has taken place (must be cleared in software)

- 0 =No read or write has occurred

Note: PSPIF is reserved on 28-pin devices; always maintain this bit clear.

- bit 6 ADIF: A/D Converter Interrupt Flag bit

- 1 = An A/D conversion is completed (must be cleared in software)

- 0 = The A/D conversion is not complete

- RCIF: AUSART Receive Interrupt Flag bit

- 1 = The AUSART receive buffer is full

- 0 = The AUSART receive buffer is empty

- bit 4 **TXIF**: AUSART Transmit Interrupt Flag bit

- 1 = The AUSART transmit buffer is empty

- 0 = The AUSART transmit buffer is full

- bit 3 **SSPIF**: Synchronous Serial Port (SSP) Interrupt Flag bit

- 1 = The SSP interrupt condition has occurred and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are: SPI:

- A transmission/reception has taken place.

- I<sup>2</sup>C Slave:

- A transmission/reception has taken place.

- I<sup>2</sup>C Master:

A transmission/reception has taken place. The initiated Start condition was completed by the SSP module. The initiated Stop condition was completed by the SSP module. The initiated Restart condition was completed by the SSP module. The initiated Acknowledge condition was completed by the SSP module. A Start condition occurred while the SSP module was Idle (multi-master system). A Stop condition occurred while the SSP module was Idle (multi-master system).

- 0 = No SSP interrupt condition has occurred

- bit 2 **CCP1IF**: CCP1 Interrupt Flag bit

- Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

- Compare mode:

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

- PWM mode:

- Unused in this mode.

- bit 1 **TMR2IF**: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

- bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = TMR1 register did not overflow

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

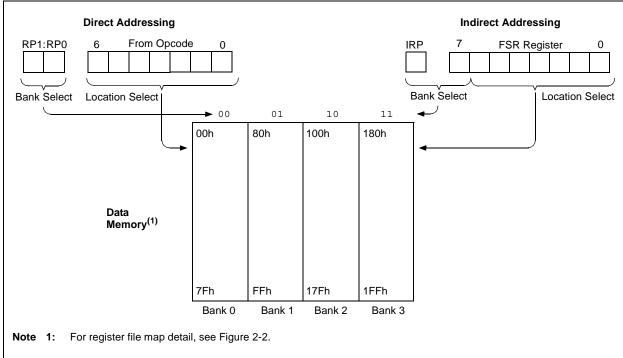

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-5.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### **INDIRECT ADDRESSING** EXAMPLE 2-2: MOVLW 0x20 ; initialize pointer MOVWF FSR ;to RAM NEXT ;clear INDF register CLRF TNDF INCF FSR, F ; inc pointer BTFSS FSR, 4 ;all done? GOTO NEXT ;no clear next CONTINUE ;yes continue :

## FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

## 10.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate a receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 10.4.7** "**Baud Rate Generator**" for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start enable bit, SEN (SSPCON2<0>).

- SSPIF is set. The MSSP module will wait the required Start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

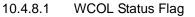

## 10.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

## FIGURE 10-19: FIRST START BIT TIMING

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

| David               |         | Fosc = 20 MHz |                             |         | Fosc = 16 M | Hz                          |         | Fosc = 10 M | Hz                          |

|---------------------|---------|---------------|-----------------------------|---------|-------------|-----------------------------|---------|-------------|-----------------------------|

| Baud<br>Rate<br>(K) | Kbaud   | %<br>Error    | SPBRG<br>Value<br>(decimal) | Kbaud   | %<br>Error  | SPBRG<br>Value<br>(decimal) | Kbaud   | %<br>Error  | SPBRG<br>Value<br>(decimal) |

| 0.3                 | —       | _             | _                           | —       | _           | _                           | -       | _           | _                           |

| 1.2                 | 1.221   | 1.75          | 255                         | 1.202   | 0.17        | 207                         | 1.202   | 0.17        | 129                         |

| 2.4                 | 2.404   | 0.17          | 129                         | 2.404   | 0.17        | 103                         | 2.404   | 0.17        | 64                          |

| 9.6                 | 9.766   | 1.73          | 31                          | 9.615   | 0.16        | 25                          | 9.766   | 1.73        | 15                          |

| 19.2                | 19.531  | 1.72          | 15                          | 19.231  | 0.16        | 12                          | 19.531  | 1.72        | 7                           |

| 28.8                | 31.250  | 8.51          | 9                           | 27.778  | 3.55        | 8                           | 31.250  | 8.51        | 4                           |

| 33.6                | 34.722  | 3.34          | 8                           | 35.714  | 6.29        | 6                           | 31.250  | 6.99        | 4                           |

| 57.6                | 62.500  | 8.51          | 4                           | 62.500  | 8.51        | 3                           | 52.083  | 9.58        | 2                           |

| HIGH                | 1.221   | _             | 255                         | 0.977   | _           | 255                         | 0.610   | —           | 255                         |

| LOW                 | 312.500 | _             | 0                           | 250.000 | _           | 0                           | 156.250 | _           | 0                           |

| David               |        | Fosc = 4 MH | łz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|---------------------|--------|-------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| Baud<br>Rate<br>(K) | Kbaud  | %<br>Error  | SPBRG<br>Value<br>(decimal) | Kbaud             | %<br>Error | SPBRG<br>Value<br>(decimal) |  |  |

| 0.3                 | 0.300  | 0           | 207                         | 0.3               | 0          | 191                         |  |  |

| 1.2                 | 1.202  | 0.17        | 51                          | 1.2               | 0          | 47                          |  |  |

| 2.4                 | 2.404  | 0.17        | 25                          | 2.4               | 0          | 23                          |  |  |

| 9.6                 | 8.929  | 6.99        | 6                           | 9.6               | 0          | 5                           |  |  |

| 19.2                | 20.833 | 8.51        | 2                           | 19.2              | 0          | 2                           |  |  |

| 28.8                | 31.250 | 8.51        | 1                           | 28.8              | 0          | 1                           |  |  |

| 33.6                | _      | _           | _                           | _                 | _          | _                           |  |  |

| 57.6                | 62.500 | 8.51        | 0                           | 57.6              | 0          | 0                           |  |  |

| HIGH                | 0.244  | _           | 255                         | 0.225             | _          | 255                         |  |  |

| LOW                 | 62.500 | _           | 0                           | 57.6              | _          | 0                           |  |  |

## TABLE 11-4:BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

|                     | 1        | Fosc = 20 MHz |                             |          | Fosc = 16 MH | łz                          | Fosc = 10 MHz |            |                             |

|---------------------|----------|---------------|-----------------------------|----------|--------------|-----------------------------|---------------|------------|-----------------------------|

| Baud<br>Rate<br>(K) | Kbaud    | %<br>Error    | SPBRG<br>Value<br>(decimal) | Kbaud    | %<br>Error   | SPBRG<br>Value<br>(decimal) | Kbaud         | %<br>Error | SPBRG<br>Value<br>(decimal) |

| 0.3                 | —        | _             | _                           | —        | _            | _                           |               | _          | _                           |

| 1.2                 | _        | _             | _                           | _        | _            | _                           | _             | _          | _                           |

| 2.4                 | —        | _             | _                           | —        | _            | —                           | 2.441         | 1.71       | 255                         |

| 9.6                 | 9.615    | 0.16          | 129                         | 9.615    | 0.16         | 103                         | 9.615         | 0.16       | 64                          |

| 19.2                | 19.231   | 0.16          | 64                          | 19.231   | 0.16         | 51                          | 19.531        | 1.72       | 31                          |

| 28.8                | 29.070   | 0.94          | 42                          | 29.412   | 2.13         | 33                          | 28.409        | 1.36       | 21                          |

| 33.6                | 33.784   | 0.55          | 36                          | 33.333   | 0.79         | 29                          | 32.895        | 2.10       | 18                          |

| 57.6                | 59.524   | 3.34          | 20                          | 58.824   | 2.13         | 16                          | 56.818        | 1.36       | 10                          |

| HIGH                | 4.883    | _             | 255                         | 3.906    | _            | 255                         | 2.441         | _          | 255                         |

| LOW                 | 1250.000 | _             | 0                           | 1000.000 | _            | 0                           | 625.000       | _          | 0                           |

| Baud                |         | Fosc = 4 MH | z                           | Fosc = 3.6864 MHz |            |                             |  |  |

|---------------------|---------|-------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| Baud<br>Rate<br>(K) | Kbaud   | %<br>Error  | SPBRG<br>Value<br>(decimal) | Kbaud             | %<br>Error | SPBRG<br>Value<br>(decimal) |  |  |

| 0.3                 | _       | _           | _                           | _                 | _          | —                           |  |  |

| 1.2                 | 1.202   | 0.17        | 207                         | 1.2               | 0          | 191                         |  |  |

| 2.4                 | 2.404   | 0.17        | 103                         | 2.4               | 0          | 95                          |  |  |

| 9.6                 | 9.615   | 0.16        | 25                          | 9.6               | 0          | 23                          |  |  |

| 19.2                | 19.231  | 0.16        | 12                          | 19.2              | 0          | 11                          |  |  |

| 28.8                | 27.798  | 3.55        | 8                           | 28.8              | 0          | 7                           |  |  |

| 33.6                | 35.714  | 6.29        | 6                           | 32.9              | 2.04       | 6                           |  |  |

| 57.6                | 62.500  | 8.51        | 3                           | 57.6              | 0          | 3                           |  |  |

| HIGH                | 0.977   | —           | 255                         | 0.9               | _          | 255                         |  |  |

| LOW                 | 250.000 | _           | 0                           | 230.4             | _          | 0                           |  |  |

## 12.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has 11 inputs for the PIC16F737 and PIC16F767 devices and 14 for the PIC16F747 AND PIC16F777 devices.

The A/D converter allows conversion of an analog input signal to a corresponding 10-bit digital number.

A new feature for the A/D converter is the addition of programmable acquisition time. This feature allows the user to select a new channel for conversion and to set the GO/DONE bit immediately. When the GO/DONE bit is set, the selected channel is sampled for the programmed acquisition time before a conversion is actually started. This removes the firmware overhead required to allow for an acquisition (sampling) period (see Register 12-3 and Section 12.2 "Selecting and Configuring Automatic Acquisition Time"). The module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 12-1, controls the operation of the A/D module and clock source. The ADCON1 register, shown in Register 12-2, configures the functions of the port pins, justification and voltage reference sources. The ADCON2, shown in Register 12-3, configures the programmed acquisition time.

Additional information on using the A/D module can be found in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN546 "Using the Analog-to-Digital (A/D) Converter" (DS00546).

## PIC16F7X7

| REGISTER 12-2: | ADCO                                           | ADCON1: A/D CONTROL REGISTER 1 (ADDRESS 9Fh)                                  |         |            |           |        |        |        |        |        |                |        |        |        |       |

|----------------|------------------------------------------------|-------------------------------------------------------------------------------|---------|------------|-----------|--------|--------|--------|--------|--------|----------------|--------|--------|--------|-------|

|                | R/W-                                           | 0                                                                             | R/W-0   | R          | /W-0      | R/     | W-0    | R/     | W-0    | R      | R/W-0          | F      | R/W-0  | R      | /W-0  |

|                | ADFI                                           | M                                                                             | ADCS2   | V          | CFG1      | VC     | FG0    | PC     | FG3    | P      | CFG2           | P      | PCFG1  | PC     | FG0   |

|                | bit 7                                          |                                                                               |         |            |           |        |        |        |        | •      |                |        |        |        | bit 0 |

|                |                                                |                                                                               |         |            |           |        |        |        |        |        |                |        |        |        |       |

| bit 7          | ADFM:                                          | : A/D R                                                                       | esult F | ormat S    | Select b  | oit    |        |        |        |        |                |        |        |        |       |

|                | 1 = Rig                                        |                                                                               |         |            |           |        |        |        |        |        |                |        |        |        |       |

|                | 0 = Lef                                        | -                                                                             |         |            | •         |        |        | DRES   | L are  | read a | <b>IS</b> '0'. |        |        |        |       |

| bit 6          | ADCS2                                          |                                                                               |         |            | •         |        |        |        |        |        |                |        |        |        |       |

|                | 1 = A/E<br>0 = Dis                             |                                                                               | source  | IS DIVIC   | aed by    | wo wi  | nen sy | stem   | CIOCK  | IS USE | d              |        |        |        |       |

| bit 5          | VCFG1                                          | VCFG1: Voltage Reference Configuration bit 1                                  |         |            |           |        |        |        |        |        |                |        |        |        |       |

|                |                                                | e = VREF- is connected to Vss<br>= VREF- is connected to external VREF- (RA2) |         |            |           |        |        |        |        |        |                |        |        |        |       |

| bit 4          |                                                | VCFG0: Voltage Reference Configuration bit 0                                  |         |            |           |        |        |        |        |        |                |        |        |        |       |

|                |                                                | 0 = VREF+ is connected to VDD                                                 |         |            |           |        |        |        |        |        |                |        |        |        |       |

|                | 1 = VREF+ is connected to external VREF+ (RA3) |                                                                               |         |            |           |        |        |        |        |        |                |        |        |        |       |

| bit 3-0        | PCFG<3:0>: A/D Port Configuration bits         |                                                                               |         |            |           |        |        |        |        |        |                |        |        |        |       |

|                |                                                | AN13                                                                          | AN12    | AN11       | AN10      | AN9    | AN8    | AN7    | AN6    | AN5    | AN4            | AN3    | AN2    | AN1    | AN0   |

|                | 0000                                           | А                                                                             | А       | А          | А         | А      | Α      | А      | А      | А      | А              | А      | Α      | А      | А     |

|                | 0001                                           | Α                                                                             | Α       | Α          | Α         | А      | Α      | А      | А      | Α      | Α              | А      | Α      | А      | А     |

|                | 0010                                           | D                                                                             | А       | А          | Α         | А      | А      | А      | А      | Α      | А              | А      | А      | А      | А     |

|                | 0011                                           | D                                                                             | D       | А          | Α         | А      | А      | А      | А      | А      | А              | А      | А      | А      | А     |

|                | 0100                                           | D                                                                             | D       | D          | Α         | А      | А      | А      | А      | А      | А              | А      | А      | А      | А     |

|                | 0101                                           | D                                                                             | D       | D          | D         | А      | A      | A      | А      | Α      | A              | А      | A      | А      | A     |

|                | 0110                                           | D                                                                             | D       | D          | D         | D      | A      | A      | A      | A      | A              | A      | A      | A      | A     |

|                | 0111                                           | D                                                                             | D       | D          | D         | D      | D      | A      | A      | A      | A              | A      | A      | A      | A     |

|                | 1000                                           | D<br>D                                                                        | D<br>D  | D<br>D     | D<br>D    | D<br>D | D<br>D | D<br>D | A<br>D | A<br>A | A<br>A         | A<br>A | A<br>A | A<br>A | A     |

|                | 1001                                           | D                                                                             | D       | D          | D         | D      | D      | D      | D      | D      | A              | A      | A      | A      | A     |

|                | 1010                                           | D                                                                             | D       | D          | D         | D      | D      | D      | D      | D      | D              | A      | A      | A      | A     |

|                | 1100                                           | D                                                                             | D       | D          | D         | D      | D      | D      | D      | D      | D              | D      | A      | A      | A     |

|                | 1101                                           | D                                                                             | D       | D          | D         | D      | D      | D      | D      | D      | D              | D      | D      | A      | A     |

|                | 1110                                           | D                                                                             | D       | D          | D         | D      | D      | D      | D      | D      | D              | D      | D      | D      | А     |

|                | 1111                                           | D                                                                             | D       | D          | D         | D      | D      | D      | D      | D      | D              | D      | D      | D      | D     |

|                | Legend                                         | d: A =                                                                        | Analog  | ı input, E | D = Digit | al I/O |        |        |        |        |                |        |        |        |       |

|                | •• •                                           |                                                                               |         |            | -         |        |        |        | 40     |        |                |        |        |        |       |

AN5 through AN7 are only available on the 40-pin product variant (PIC16F747 and PIC16F777). Note:

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

© 2003-2013 Microchip Technology Inc.

## **PIC16F7X7**

| REGISTER 12-3: | ADCON2: A/D CONTROL REGISTER 2 (ADDRESS 9Bh) |     |       |       |       |     |     |       |  |  |  |

|----------------|----------------------------------------------|-----|-------|-------|-------|-----|-----|-------|--|--|--|

|                | U-0                                          | U-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |  |  |  |

|                |                                              | —   | ACQT2 | ACQT1 | ACQT0 | —   | _   | _     |  |  |  |

|                | bit 7                                        |     |       |       |       |     |     | bit 0 |  |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-3 ACQT<2:0>: A/D Acquisition Time Select bits

$000 = 0^{(1)}$ 001 = 2 TAD 010 = 4 TAD011 = 6 TAD 100 = 8 TAD 101 = **12T**AD 110 = 16 TAD 111 = 20 TAD

> Note 1: If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and VSS) or the voltage level on the RA3/AN3/VREF+ and RA2/AN2/VREF-/CVREF pins.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted.

Each port pin associated with the A/D converter can be configured as an analog input or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0 register) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 12-1.

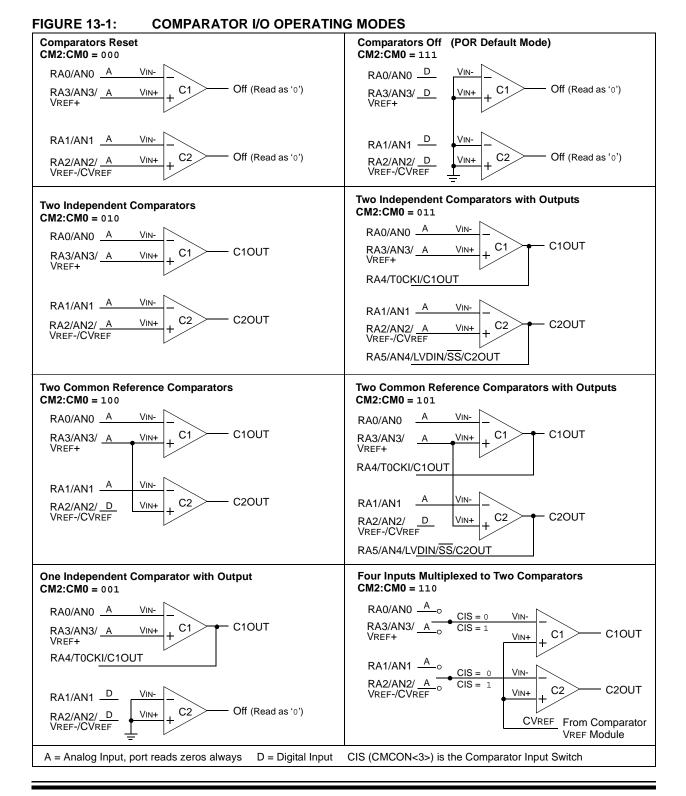

## 13.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select these modes. Figure 13-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in the electrical specifications (Section 18.0 "Electrical Characteristics").

**Note:** Comparator interrupts should be disabled during a Comparator mode change. Otherwise, a false interrupt may occur.

f,b

Bit 'b' in register 'f' is cleared.

## 16.2 Instruction Descriptions

ADDWF

Syntax: Operands:

| ADDLW            | Add Literal and W                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                  |

| Operands:        | $0 \le k \le 255$                                                                                                         |

| Operation:       | $(W) + k \to (W)$                                                                                                         |

| Status Affected: | C, DC, Z                                                                                                                  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k<br>and the result is placed in the W<br>register. |

| are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. | Description:    |

|------------------------------------------------------------------------------------------|-----------------|

| Add W and f                                                                              | BSF             |

| [label] ADDWF f,d                                                                        | Syntax:         |

| $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                          | Operands:       |

| (W) + (f) $\rightarrow$ (destination)                                                    | Operation:      |

| 0.00.7                                                                                   | Otatura Affarat |

BCF

Syntax:

Operands:

Operation:

Status Affected:

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

Bit Clear f

[ label ] BCF

$\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$

$0 \rightarrow (f < b >)$

None

| ANDLW            | AND Literal with W                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                            |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                          |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

## PIC16F7X7

| MOVF             | Move f                                                                                                                                                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                            |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                              |

| Status Affected: | Z                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are<br>moved to a destination dependant<br>upon the status of 'd'. If $d = 0$ ,<br>the destination is W register. If<br>d = 1, the destination is file register<br>'f' itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                           |

|------------------|---------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                    |

| Operands:        | $0 \leq k \leq 255$                                                                         |

| Operation:       | $k \rightarrow (W)$                                                                         |

| Status Affected: | None                                                                                        |

| Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as '0's. |

| RETFIE           | Return from Interrupt                         |

|------------------|-----------------------------------------------|

| Syntax:          | [label] RETFIE                                |

| Operands:        | None                                          |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$ |

| Status Affected: | None                                          |

| MOVWF            | Move W to f                                |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |

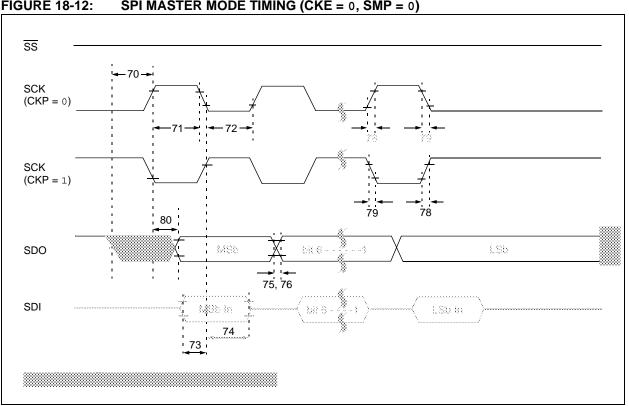

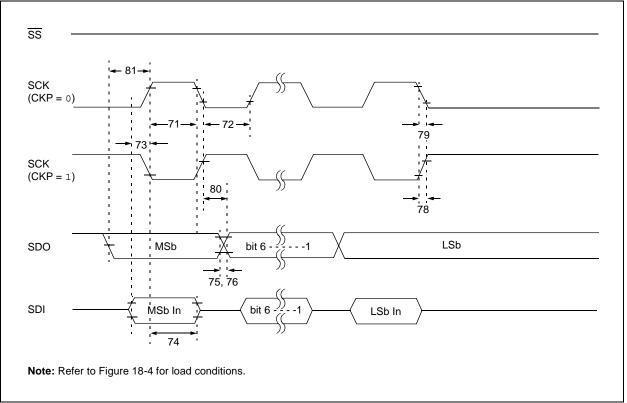

#### **FIGURE 18-12:** SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

| Param.<br>No. | Symbol  | Characte             | eristic      | Min         | Мах  | Units | Conditions                                  |

|---------------|---------|----------------------|--------------|-------------|------|-------|---------------------------------------------|

| 100* Ti       | Тнідн   | Clock High Time      | 100 kHz mode | 4.0         |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                      | 400 kHz mode | 0.6         |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                      | SSP module   | 1.5 TCY     | _    |       |                                             |

| 101*          | TLOW    | Clock Low Time       | 100 kHz mode | 4.7         |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                      | 400 kHz mode | 1.3         |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                      | SSP module   | 1.5 TCY     | _    |       |                                             |

| 102*          | TR      | SDA and SCL Rise     | 100 kHz mode | —           | 1000 | ns    |                                             |

|               |         | Time                 | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 103*          | TF      | SDA and SCL Fall     | 100 kHz mode | —           | 300  | ns    |                                             |

|               |         | Time                 | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 90*           | TSU:STA | Start Condition      | 100 kHz mode | 4.7         | _    | μs    | Only relevant for Repeated                  |

|               |         | Setup Time           | 400 kHz mode | 0.6         |      | μS    | Start condition                             |

| 91*           | THD:STA | Start Condition Hold | 100 kHz mode | 4.0         | _    | μs    | After this period, the first                |

|               |         | Time                 | 400 kHz mode | 0.6         | —    | μs    | clock pulse is generated                    |

| 106*          | THD:DAT | Data Input Hold      | 100 kHz mode | 0           | —    | ns    |                                             |

|               |         | Time                 | 400 kHz mode | 0           | 0.9  | μS    |                                             |

| 107*          | TSU:DAT | Data Input Setup     | 100 kHz mode | 250         | —    | ns    | (Note 2)                                    |

|               |         | Time                 | 400 kHz mode | 100         | —    | ns    |                                             |

| 92*           | Tsu:sto | Stop Condition       | 100 kHz mode | 4.7         | —    | μS    | _                                           |

|               |         | Setup Time           | 400 kHz mode | 0.6         | —    | μS    |                                             |

| 109*          | ΤΑΑ     | Output Valid from    | 100 kHz mode | —           | 3500 | ns    | (Note 1)                                    |

|               |         | Clock                | 400 kHz mode | —           | —    | ns    |                                             |

| 110*          | TBUF    | Bus Free Time        | 100 kHz mode | 4.7         | _    | μS    | Time the bus must be free                   |

|               |         |                      | 400 kHz mode | 1.3         | —    | μS    | before a new transmission can start         |

|               | Св      | Bus Capacitive Load  | ling         | —           | 400  | pF    |                                             |

| TABLE 18-12: I | I <sup>2</sup> C™ BUS DATA | REQUIREMENTS |

|----------------|----------------------------|--------------|

|----------------|----------------------------|--------------|

These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system but the requirement, TsU:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

\*

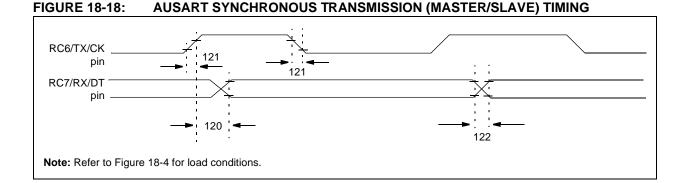

## TABLE 18-13: AUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol        | Characteristic                                                        |            | Min | Тур† | Max | Units | Conditions |

|--------------|---------------|-----------------------------------------------------------------------|------------|-----|------|-----|-------|------------|

| 120          | TCKH2DTV      | <u>SYNC XMIT (MASTER &amp; SLAVE)</u><br>Clock High to Data Out Valid | PIC16F7X7  |     | _    | 80  | ns    |            |

|              |               |                                                                       | PIC16LF7X7 | _   |      | 100 | ns    |            |

| 121          | TCKRF         | Clock Out Rise Time and Fall Time                                     | PIC16F7X7  | _   | _    | 45  | ns    |            |

|              | (Master mode) |                                                                       | PIC16LF7X7 | _   | —    | 50  | ns    |            |

| 122          | Tdtrf         | Data Out Rise Time and Fall Time                                      | PIC16F7X7  | _   |      | 45  | ns    |            |

|              |               |                                                                       | PIC16LF7X7 |     |      | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

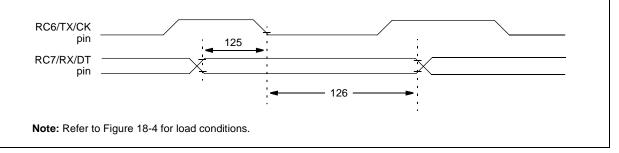

## FIGURE 18-19: AUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 18-14: AUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                                                                 | Min | Тур† | Max | Units | Conditions |

|--------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125          | TDTV2CKL | SYNC RCV (MASTER & SLAVE)<br>Data Setup before CK $\downarrow$ (DT setup time) | 15  | _    | _   | ns    |            |

| 126          | TCKL2DTL | Data Hold after CK $\downarrow$ (DT hold time)                                 | 15  | -    | -   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

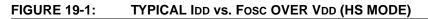

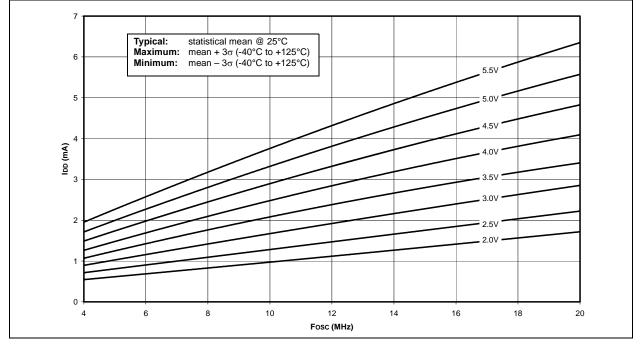

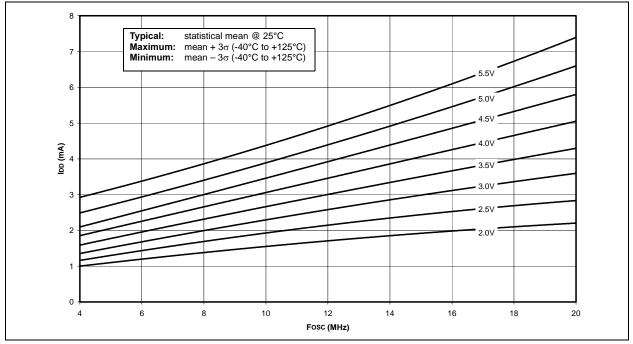

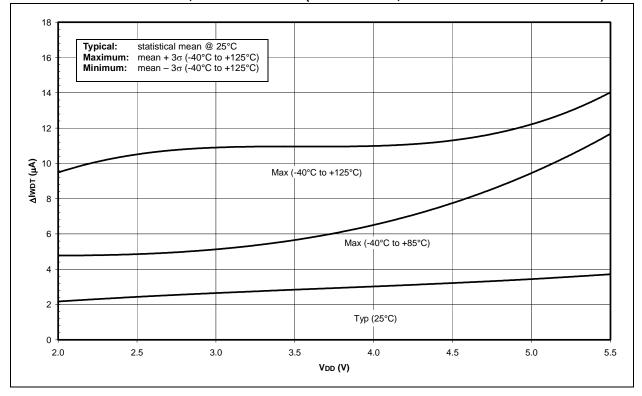

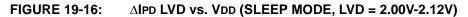

## 19.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2003-2013 Microchip Technology Inc.

FIGURE 19-15: △IPD WDT, -40°C TO +125°C (SLEEP MODE, ALL PERIPHERALS DISABLED)

## 20.2 Package Details

The following sections give the technical details of the packages.

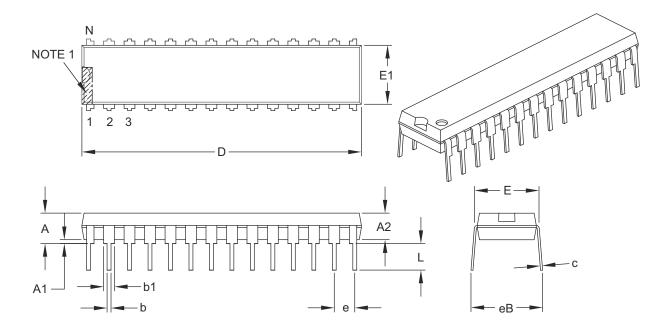

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES           |       |          |       |  |  |

|----------------------------|------------------|-------|----------|-------|--|--|

| Dimensio                   | Dimension Limits |       |          | MAX   |  |  |

| Number of Pins             | Ν                | 28    |          |       |  |  |

| Pitch                      | е                |       | .100 BSC |       |  |  |

| Top to Seating Plane       | А                | _     | -        | .200  |  |  |

| Molded Package Thickness   | A2               | .120  | .135     | .150  |  |  |

| Base to Seating Plane      | A1               | .015  | -        | -     |  |  |

| Shoulder to Shoulder Width | E                | .290  | .310     | .335  |  |  |

| Molded Package Width       | E1               | .240  | .285     | .295  |  |  |

| Overall Length             | D                | 1.345 | 1.365    | 1.400 |  |  |

| Tip to Seating Plane       | L                | .110  | .130     | .150  |  |  |

| Lead Thickness             | С                | .008  | .010     | .015  |  |  |

| Upper Lead Width           | b1               | .040  | .050     | .070  |  |  |

| Lower Lead Width           | b                | .014  | .018     | .022  |  |  |

| Overall Row Spacing §      | eB               | -     | _        | .430  |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

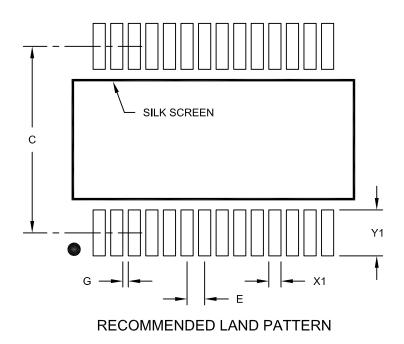

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |  |

|--------------------------|-------------|----------|------|------|--|

| Dimension                | MIN         | NOM      | MAX  |      |  |

| Contact Pitch            | E           | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С           |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1          |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1          |          |      | 1.75 |  |

| Distance Between Pads    | G           | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support