Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf747-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

#### **REGISTER 2-4:** PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS 8Ch) R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 PSPIE<sup>(1)</sup> ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE bit 7 bit 0 PSPIE: Parallel Slave Port Read/Write Interrupt Enable bit<sup>(1)</sup> bit 7 1 = Enables the PSP read/write interrupt 0 = Disables the PSP read/write interrupt Note 1: PSPIE is reserved on 28-pin devices; always maintain this bit clear. bit 6 ADIE: A/D Converter Interrupt Enable bit 1 = Enables the A/D converter interrupt 0 = Disables the A/D converter interrupt bit 5 RCIE: AUSART Receive Interrupt Enable bit 1 = Enables the AUSART receive interrupt 0 = Disables the AUSART receive interrupt bit 4 TXIE: AUSART Transmit Interrupt Enable bit 1 = Enables the AUSART transmit interrupt 0 = Disables the AUSART transmit interrupt bit 3 SSPIE: Synchronous Serial Port Interrupt Enable bit 1 = Enables the SSP interrupt 0 = Disables the SSP interrupt CCP1IE: CCP1 Interrupt Enable bit bit 2 1 = Enables the CCP1 interrupt 0 = Disables the CCP1 interrupt bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit 1 = Enables the TMR2 to PR2 match interrupt 0 = Disables the TMR2 to PR2 match interrupt bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit 1 = Enables the TMR1 overflow interrupt 0 = Disables the TMR1 overflow interrupt Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

#### 2.2.2.5 PIR1 Register

bit 5

The PIR1 register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ADDRESS 0Ch)

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |  |

|----------------------|-------|------|------|-------|--------|--------|--------|--|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |  |

| bit 7                |       |      |      |       |        |        | bit 0  |  |

- bit 7 **PSPIF:** Parallel Slave Port Read/Write Interrupt Flag bit<sup>(1)</sup>

- 1 = A read or a write operation has taken place (must be cleared in software)

- 0 =No read or write has occurred

Note: PSPIF is reserved on 28-pin devices; always maintain this bit clear.

- bit 6 ADIF: A/D Converter Interrupt Flag bit

- 1 = An A/D conversion is completed (must be cleared in software)

- 0 = The A/D conversion is not complete

- RCIF: AUSART Receive Interrupt Flag bit

- 1 = The AUSART receive buffer is full

- 0 = The AUSART receive buffer is empty

- bit 4 **TXIF**: AUSART Transmit Interrupt Flag bit

- 1 = The AUSART transmit buffer is empty

- 0 = The AUSART transmit buffer is full

- bit 3 **SSPIF**: Synchronous Serial Port (SSP) Interrupt Flag bit

- 1 = The SSP interrupt condition has occurred and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are: SPI:

- A transmission/reception has taken place.

- I<sup>2</sup>C Slave:

- A transmission/reception has taken place.

- I<sup>2</sup>C Master:

A transmission/reception has taken place. The initiated Start condition was completed by the SSP module. The initiated Stop condition was completed by the SSP module. The initiated Restart condition was completed by the SSP module. The initiated Acknowledge condition was completed by the SSP module. A Start condition occurred while the SSP module was Idle (multi-master system). A Stop condition occurred while the SSP module was Idle (multi-master system).

- 0 = No SSP interrupt condition has occurred

- bit 2 **CCP1IF**: CCP1 Interrupt Flag bit

- Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

- Compare mode:

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

- PWM mode:

- Unused in this mode.

- bit 1 **TMR2IF**: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

- bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = TMR1 register did not overflow

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### 3.3 Reading the Flash Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit, RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction; therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

#### 3.4 Operation During Code-Protect

Flash program memory has its own code-protect mechanism. External read and write operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal Flash program memory, regardless of the state of the code-protect configuration bits.

|                      | BSF               | STATUS, RP1 | ;                                                                                          |

|----------------------|-------------------|-------------|--------------------------------------------------------------------------------------------|

|                      | BCF               | STATUS, RP0 | ; Bank 2                                                                                   |

|                      | MOVF              | ADDRH, W    | ;                                                                                          |

|                      | MOVWF             | PMADRH      | ; MSByte of Program Address to read                                                        |

|                      | MOVF              | ADDRL, W    | ;                                                                                          |

|                      | MOVWF             | PMADR       | ; LSByte of Program Address to read                                                        |

|                      | BSF               | STATUS, RP0 | ; Bank 3 Required                                                                          |

| Required<br>Sequence | BSF<br>NOP<br>NOP | PMCON1, RD  | ; EEPROM Read Sequence<br>; memory is read in the next two cycles after BSF PMCON1,RD<br>; |

|                      | BCF               | STATUS, RPO | ; Bank 2                                                                                   |

|                      | MOVF              | PMDATA, W   | ; W = LSByte of Program PMDATA                                                             |

|                      | MOVF              | PMDATH, W   | ; W = MSByte of Program PMDATH                                                             |

EXAMPLE 3-1: FLASH PROGRAM READ

| TABLE 3-1: | <b>REGISTERS ASSOCIATED WITH PROGRAM FLASH</b> |

|------------|------------------------------------------------|

|            |                                                |

| Address | Name   | Bit 7                   | Bit 6                            | Bit 5 | Bit 4   | Bit 3      | Bit 2     | Bit 1      | Bit 0     | Value<br>POR, |      | Valu<br>all c<br>Res | other |

|---------|--------|-------------------------|----------------------------------|-------|---------|------------|-----------|------------|-----------|---------------|------|----------------------|-------|

| 10Dh    | PMADR  | EEPROM A                | EEPROM Address Register Low Byte |       |         |            |           |            |           | xxxx          | xxxx | uuuu                 | uuuu  |

| 10Fh    | PMADRH | -                       | —                                | —     | _       | EEPRON     | Address   | Register H | ligh Byte |               | xxxx | u                    | uuuu  |

| 10Ch    | PMDATA | EEPROM D                | EEPROM Data Register Low Byte    |       |         |            |           |            |           | xxxx          | xxxx | uuuu                 | uuuu  |

|         | PMDATH |                         |                                  | EEPR  | OM Data | a Register | High Byte | 9          |           | xx            | xxxx | uu                   | uuuu  |

| 18Ch    | PMCON1 | reserved <sup>(1)</sup> | _                                | _     | _       | _          |           | _          | RD        | 1             | 0    | 1                    | 0     |

**Legend:** x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are not used during Flash access. **Note 1:** This bit always reads as a '1'.

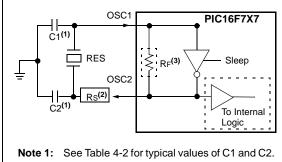

#### FIGURE 4-2: CERAMIC RESONATOR OPERATION (HS OR XT OSC CONFIGURATION)

- **2:** A series resistor (Rs) may be required.

- 3: RF varies with the resonator chosen (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

#### TABLE 4-2: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| Typical Capacitor Values Used: |          |       |       |  |  |  |  |  |  |

|--------------------------------|----------|-------|-------|--|--|--|--|--|--|

| Mode Freq OSC1 OSC2            |          |       |       |  |  |  |  |  |  |

| XT                             | 455 kHz  | 56 pF | 56 pF |  |  |  |  |  |  |

|                                | 2.0 MHz  | 47 pF | 47 pF |  |  |  |  |  |  |

|                                | 4.0 MHz  | 33 pF | 33 pF |  |  |  |  |  |  |

| HS                             | 8.0 MHz  | 27 pF | 27 pF |  |  |  |  |  |  |

|                                | 16.0 MHz | 22 pF | 22 pF |  |  |  |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode rather than XT mode is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is 330Ω.

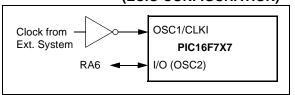

#### 4.3 External Clock Input

The ECIO Oscillator mode requires an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the ECIO Oscillator mode, the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 4-3 shows the pin connections for the ECIO Oscillator mode.

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

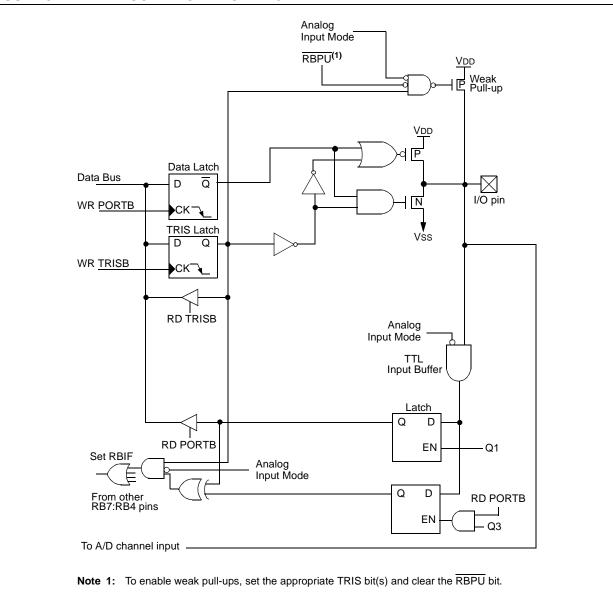

# 5.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

#### 5.1 PORTA and the TRISA Register

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in Configuration Register 1H (see **Section 15.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA3:RA0 and RA5 as A/D converter inputs is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register 1). Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register.

| Note: | On a Power-on Reset, RA5 and RA3:RA0          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the RA pins even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 5-1: INITIALIZING PORTA

| BCF<br>BCF | STATUS, |       | ;<br>; Bank0            |

|------------|---------|-------|-------------------------|

| -          |         | ICI I | ,                       |

| CLRF       | PORTA   |       | ; Initialize PORTA by   |

|            |         |       | ; clearing output       |

|            |         |       | ; data latches          |

| BSF        | STATUS, | RP0   | ; Select Bank 1         |

| MOVLW      | 0x0F    |       | ; Configure all pins    |

| MOVWF      | ADCON1  |       | ; as digital inputs     |

| MOVLW      | 0xCF    |       | ; Value used to         |

|            |         |       | ; initialize data       |

|            |         |       | ; direction             |

| MOVWF      | TRISA   |       | ; Set RA<3:0> as inputs |

|            |         |       | ; RA<5:4> as outputs    |

|            |         |       | ; TRISA<7:6>are always  |

|            |         |       | ; read as '0'.          |

# PIC16F7X7

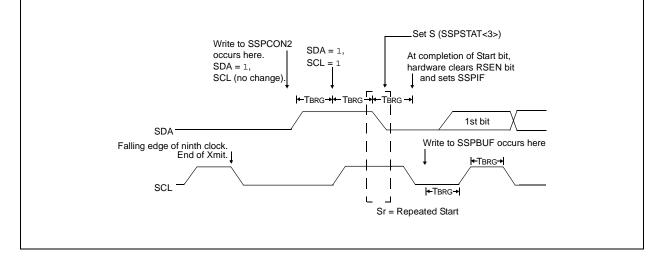

#### 10.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 10.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

#### FIGURE 10-20: REPEATED START CONDITION WAVEFORM

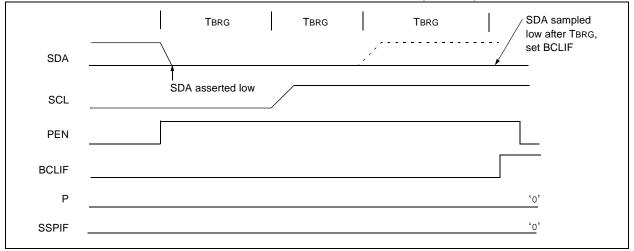

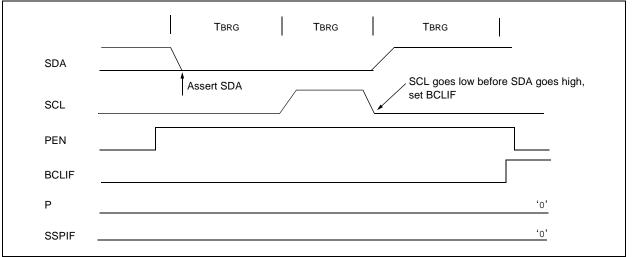

#### 10.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 10-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 10-32).

#### FIGURE 10-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 10-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

#### 11.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is one of the two serial I/O modules. (AUSART is also known as a Serial Communications Interface or SCI.) The AUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The AUSART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The AUSART module also has a multi-processor communication capability using 9-bit address detection.

#### **REGISTER 11-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)**

|       | R/W-0                                                    | R/W-0       | R/W-0         | R/W-0          | U-0            | R/W-0     | ,<br>R-1      | R/W-0 |  |  |

|-------|----------------------------------------------------------|-------------|---------------|----------------|----------------|-----------|---------------|-------|--|--|

|       | CSRC                                                     | TX9         | TXEN          | SYNC           | _              | BRGH      | TRMT          | TX9D  |  |  |

|       | bit 7                                                    |             |               |                |                |           |               | bit 0 |  |  |

|       |                                                          |             |               |                |                |           |               |       |  |  |

| bit 7 | CSRC: Clock Source Select bit<br>Asynchronous mode:      |             |               |                |                |           |               |       |  |  |

|       | Don't care.                                              |             |               |                |                |           |               |       |  |  |

|       | <u>Synchronous</u><br>1 = Master m                       |             | generated i   | nternally from | n BRG)         |           |               |       |  |  |

|       | 0 = Slave mo                                             |             |               |                |                |           |               |       |  |  |

| bit 6 | <b>TX9</b> : 9-bit Tr                                    | ansmit Enal | ole bit       |                |                |           |               |       |  |  |

|       | 1 = Selects<br>0 = Selects                               |             |               |                |                |           |               |       |  |  |

| bit 5 | TXEN: Trans                                              | mit Enable  | bit           |                |                |           |               |       |  |  |

|       | 1 = Transmit<br>0 = Transmit                             |             |               |                |                |           |               |       |  |  |

|       | Note: S                                                  | BREN/CREM   | V overrides   | TXEN in Syı    | nc mode.       |           |               |       |  |  |

| bit 4 | SYNC: AUS                                                | ART Mode S  | Select bit    |                |                |           |               |       |  |  |

|       | 1 = Synchron<br>0 = Asynchron                            |             | )             |                |                |           |               |       |  |  |

| bit 3 | Unimpleme                                                | nted: Read  | <b>as</b> '0' |                |                |           |               |       |  |  |

| bit 2 | BRGH: High                                               | Baud Rate   | Select bit    |                |                |           |               |       |  |  |

|       | Asynchronou                                              |             |               |                |                |           |               |       |  |  |

|       | 1 = High spe<br>0 = Low spe                              |             |               |                |                |           |               |       |  |  |

|       | Synchronous                                              |             |               |                |                |           |               |       |  |  |

|       | Unused in th                                             |             |               |                |                |           |               |       |  |  |

| bit 1 | TRMT: Trans                                              |             | egister Statu | s bit          |                |           |               |       |  |  |

|       | 1 = TSR emp<br>0 = TSR full                              | oty         |               |                |                |           |               |       |  |  |

| bit 0 | <b>TX9D:</b> 9th bit of Transmit Data, can be Parity bit |             |               |                |                |           |               |       |  |  |

|       | Legend:                                                  |             |               |                |                |           |               | ]     |  |  |

|       | R = Readabl                                              | e hit       | M = M r       | itable bit     | U = Unimple    | amented h | it read as 'C | ,     |  |  |

|       | -n = Value at                                            |             | '1' = Bit     |                | '0' = Bit is c |           | x = Bit is un |       |  |  |

|       |                                                          |             | -             |                |                |           |               |       |  |  |

| Baud<br>Rate<br>(K) | Fosc = 20 MHz |            |                             |         | Fosc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |

|---------------------|---------------|------------|-----------------------------|---------|-------------|-----------------------------|---------------|------------|-----------------------------|

|                     | Kbaud         | %<br>Error | SPBRG<br>Value<br>(decimal) | Kbaud   | %<br>Error  | SPBRG<br>Value<br>(decimal) | Kbaud         | %<br>Error | SPBRG<br>Value<br>(decimal) |

| 0.3                 | —             | _          | _                           | —       | _           | _                           | _             | _          | _                           |

| 1.2                 | 1.221         | 1.75       | 255                         | 1.202   | 0.17        | 207                         | 1.202         | 0.17       | 129                         |

| 2.4                 | 2.404         | 0.17       | 129                         | 2.404   | 0.17        | 103                         | 2.404         | 0.17       | 64                          |

| 9.6                 | 9.766         | 1.73       | 31                          | 9.615   | 0.16        | 25                          | 9.766         | 1.73       | 15                          |

| 19.2                | 19.531        | 1.72       | 15                          | 19.231  | 0.16        | 12                          | 19.531        | 1.72       | 7                           |

| 28.8                | 31.250        | 8.51       | 9                           | 27.778  | 3.55        | 8                           | 31.250        | 8.51       | 4                           |

| 33.6                | 34.722        | 3.34       | 8                           | 35.714  | 6.29        | 6                           | 31.250        | 6.99       | 4                           |

| 57.6                | 62.500        | 8.51       | 4                           | 62.500  | 8.51        | 3                           | 52.083        | 9.58       | 2                           |

| HIGH                | 1.221         | _          | 255                         | 0.977   | _           | 255                         | 0.610         | —          | 255                         |

| LOW                 | 312.500       | _          | 0                           | 250.000 | _           | 0                           | 156.250       | _          | 0                           |

| David               |        | Fosc = 4 MH | łz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|---------------------|--------|-------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| Baud<br>Rate<br>(K) | Kbaud  | %<br>Error  | SPBRG<br>Value<br>(decimal) | Kbaud             | %<br>Error | SPBRG<br>Value<br>(decimal) |  |  |

| 0.3                 | 0.300  | 0           | 207                         | 0.3               | 0          | 191                         |  |  |

| 1.2                 | 1.202  | 0.17        | 51                          | 1.2               | 0          | 47                          |  |  |

| 2.4                 | 2.404  | 0.17        | 25                          | 2.4               | 0          | 23                          |  |  |

| 9.6                 | 8.929  | 6.99        | 6                           | 9.6               | 0          | 5                           |  |  |

| 19.2                | 20.833 | 8.51        | 2                           | 19.2              | 0          | 2                           |  |  |

| 28.8                | 31.250 | 8.51        | 1                           | 28.8              | 0          | 1                           |  |  |

| 33.6                | _      | _           | _                           | _                 | _          | _                           |  |  |

| 57.6                | 62.500 | 8.51        | 0                           | 57.6              | 0          | 0                           |  |  |

| HIGH                | 0.244  | _           | 255                         | 0.225             | _          | 255                         |  |  |

| LOW                 | 62.500 | _           | 0                           | 57.6              | _          | 0                           |  |  |

### TABLE 11-4:BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

|                     | Fosc = 20 MHz |            |                             | Fosc = 16 MHz |            |                             | Fosc = 10 MHz |            |                             |  |

|---------------------|---------------|------------|-----------------------------|---------------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| Baud<br>Rate<br>(K) | Kbaud         | %<br>Error | SPBRG<br>Value<br>(decimal) | Kbaud         | %<br>Error | SPBRG<br>Value<br>(decimal) | Kbaud         | %<br>Error | SPBRG<br>Value<br>(decimal) |  |

| 0.3                 | —             | _          | _                           | —             | _          | _                           |               | _          | _                           |  |

| 1.2                 | _             | _          | _                           | —             | _          | _                           | _             | _          | _                           |  |

| 2.4                 | —             | _          | _                           | —             | _          | _                           | 2.441         | 1.71       | 255                         |  |

| 9.6                 | 9.615         | 0.16       | 129                         | 9.615         | 0.16       | 103                         | 9.615         | 0.16       | 64                          |  |

| 19.2                | 19.231        | 0.16       | 64                          | 19.231        | 0.16       | 51                          | 19.531        | 1.72       | 31                          |  |

| 28.8                | 29.070        | 0.94       | 42                          | 29.412        | 2.13       | 33                          | 28.409        | 1.36       | 21                          |  |

| 33.6                | 33.784        | 0.55       | 36                          | 33.333        | 0.79       | 29                          | 32.895        | 2.10       | 18                          |  |

| 57.6                | 59.524        | 3.34       | 20                          | 58.824        | 2.13       | 16                          | 56.818        | 1.36       | 10                          |  |

| HIGH                | 4.883         | _          | 255                         | 3.906         | _          | 255                         | 2.441         | _          | 255                         |  |

| LOW                 | 1250.000      | _          | 0                           | 1000.000      | _          | 0                           | 625.000       | _          | 0                           |  |

| Baud                |         | Fosc = 4 MH | z                           | Fosc = 3.6864 MHz |            |                             |  |  |

|---------------------|---------|-------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| Baud<br>Rate<br>(K) | Kbaud   | %<br>Error  | SPBRG<br>Value<br>(decimal) | Kbaud             | %<br>Error | SPBRG<br>Value<br>(decimal) |  |  |

| 0.3                 | _       | _           | _                           | _                 | _          | —                           |  |  |

| 1.2                 | 1.202   | 0.17        | 207                         | 1.2               | 0          | 191                         |  |  |

| 2.4                 | 2.404   | 0.17        | 103                         | 2.4               | 0          | 95                          |  |  |

| 9.6                 | 9.615   | 0.16        | 25                          | 9.6               | 0          | 23                          |  |  |

| 19.2                | 19.231  | 0.16        | 12                          | 19.2              | 0          | 11                          |  |  |

| 28.8                | 27.798  | 3.55        | 8                           | 28.8              | 0          | 7                           |  |  |

| 33.6                | 35.714  | 6.29        | 6                           | 32.9              | 2.04       | 6                           |  |  |

| 57.6                | 62.500  | 8.51        | 3                           | 57.6              | 0          | 3                           |  |  |

| HIGH                | 0.977   | —           | 255                         | 0.9               | _          | 255                         |  |  |

| LOW                 | 250.000 | _           | 0                           | 230.4             | _          | 0                           |  |  |

When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (see Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

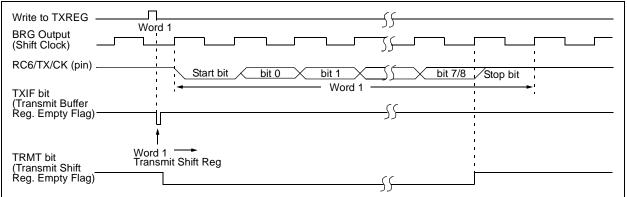

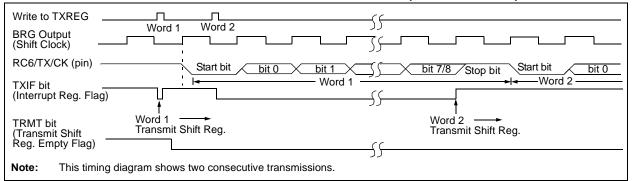

#### FIGURE 11-2: ASYNCHRONOUS MASTER TRANSMISSION

#### TABLE 11-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                             | Bit 6    | Bit 5       | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|-----------------------------------|----------|-------------|--------|-------|-----------|-----------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                               | PEIE     | TMR0IE      | INTOIE | RBIE  | TMR0IF    | INTOIF    | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>              | ADIF     | RCIF        | TXIF   | SSPIF | CCP1IF    | TMR2IF    | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                              | RX9      | SREN        | CREN   | ADDEN | FERR      | OERR      | RX9D   | 0000 000x             | 0000 000x                       |

| 19h                    | TXREG  | REG AUSART Transmit Data Register |          |             |        |       | 0000 0000 | 0000 0000 |        |                       |                                 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>              | ADIE     | RCIE        | TXIE   | SSPIE | CCP1IE    | TMR2IE    | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                              | TX9      | TXEN        | SYNC   | —     | BRGH      | TRMT      | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate                         | e Genera | tor Registe | er     |       |           |           |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

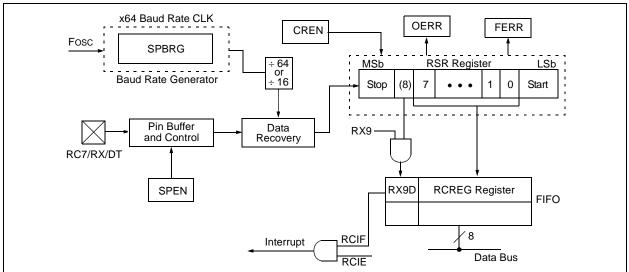

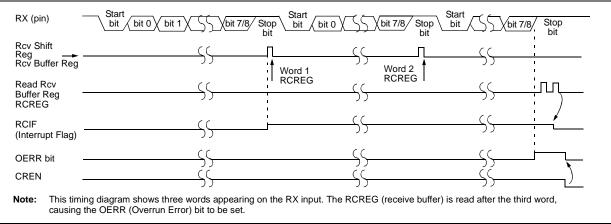

#### 11.2.2 AUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 11-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit, CREN (RCSTA<4>).

The heart of the receiver is the Receive (Serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit, RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, the Overrun Error bit, OERR (RCSTA<1>), will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit, OERR, has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received. It is, therefore, essential to clear error bit OERR if it is set. Framing Error bit, FERR (RCSTA<2>), is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values; therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

#### TABLE 15-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register              | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|-----------------------|------------------------------------|--------------------------|---------------------------------|

| W                     | XXXX XXXX                          | uuuu uuuu                | <u>uuuu</u> uuuu                |

| INDF                  | N/A                                | N/A                      | N/A                             |

| TMR0                  | xxxx xxxx                          | uuuu uuuu                | นนนน นนนน                       |

| PCL                   | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS                | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <sup>(3)</sup>        |

| FSR                   | XXXX XXXX                          | <br>uuuu uuuu            |                                 |

| PORTA                 | xx0x 0000                          | uu0u 0000                | นนนน นนนน                       |

| PORTB                 | xx00 0000                          | uu00 0000                | นนนน นนนน                       |

| PORTC                 | XXXX XXXX                          | <u>uuuu</u> uuuu         | นนนน นนนน                       |

| PORTD                 | XXXX XXXX                          | นนนน นนนน                | นนนน นนนน                       |

| PORTE (PIC16F737/767) | x                                  | u                        | u                               |

| PORTE (PIC16F747/777) | x000                               | u000                     | uuuu                            |

| PCLATH                | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON                | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

| PIR1                  | 0000 0000                          | 0000 0000                | uuuu uuuu <b>(1)</b>            |

| PIR2                  | 000- 0-00                          | 000- 0-00                | uuu- u-uu                       |

| TMR1L                 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                 | -000 0000                          | -uuu uuuu                | -uuu uuuu                       |

| TMR2                  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                 | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON                | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPCON2               | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON               | 00 0000                            | 00 0000                  | uu uuuu                         |

| CCP2CON               | 00 0000                            | 00 0000                  | uu uuuu                         |

| CCP3CON               | 00 0000                            | 00 0000                  | uuuu uuuu                       |

| CCPR2L                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR2H                | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR3L                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR3H                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| RCSTA                 | 0000 000x                          | 0000 000x                | uuuu uuuu                       |

| TXREG                 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| RCREG                 | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| ADRESH                | xxxx xxxx                          | uuuu uuuu                | <br>uuuu uuuu                   |

| ADCON0                | 0000 0000                          | 0000 0000                | <br>uuuu uuuu                   |

| OPTION_REG            | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

**Legend:** u = unchanged, x = unknown, — = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** One or more bits in INTCON, PIR1 and PR2 will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 15-3 for Reset value for specific condition.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                              |  |  |  |  |  |

| Operation:       | (f) $-1 \rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 TCY instruction. |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                   |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                              |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2 TCY<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                            |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                         |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                            |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                            |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits<10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                              |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                 |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                             |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                        |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>ORed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

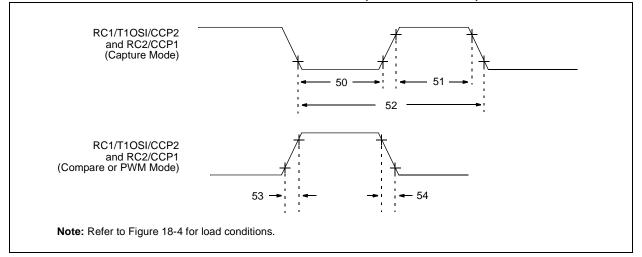

TABLE 18-8: CAPTURE/COMPARE/PWM REQUIREMENTS (ALL CCP MODULES)

| Param<br>No. | Symbol                 | Characteristic                          |                |                        | Min          | Тур† | Max | Units                              | Conditions |

|--------------|------------------------|-----------------------------------------|----------------|------------------------|--------------|------|-----|------------------------------------|------------|

| 50*          | TccL                   | CCP1, CCP2 and                          | No prescaler   |                        | 0.5 Tcy + 20 | —    | —   | ns                                 |            |

|              |                        | CCP3 Input Low                          | With prescaler | PIC16F7X7              | 10           | _    | —   | ns                                 |            |

|              |                        | Time                                    |                | PIC16LF7X7             | 20           | _    | —   | ns                                 |            |

| 51*          | 51* TccH CCP1, CCP2 ar |                                         | No prescaler   |                        | 0.5 TCY + 20 | _    | —   | ns                                 |            |

|              |                        | CCP3 Input High<br>Time                 | With prescaler | PIC16F7X7              | 10           | _    | —   | ns                                 |            |

|              |                        |                                         |                | PIC16LF7X7             | 20           |      | _   | ns                                 |            |

| 52*          | TCCP                   | CCP1, CCP2 and (                        | od             | <u>3 Tcy + 40</u><br>N | —            |      | ns  | N = prescale<br>value (1, 4 or 16) |            |

| 53*          | TCCR                   | CCP1, CCP2 and CCP3 Output              |                | PIC16F7X7              | —            | 10   | 25  | ns                                 |            |

|              |                        | Rise Time                               | Rise Time      |                        | —            | 25   | 50  | ns                                 |            |

| 54*          | TCCF                   | CCP1, CCP2 and CCP3 Output<br>Fall Time |                | PIC16F7X7              | —            | 10   | 25  | ns                                 |            |

|              |                        |                                         |                | PIC16LF7X7             | _            | 25   | 45  | ns                                 |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

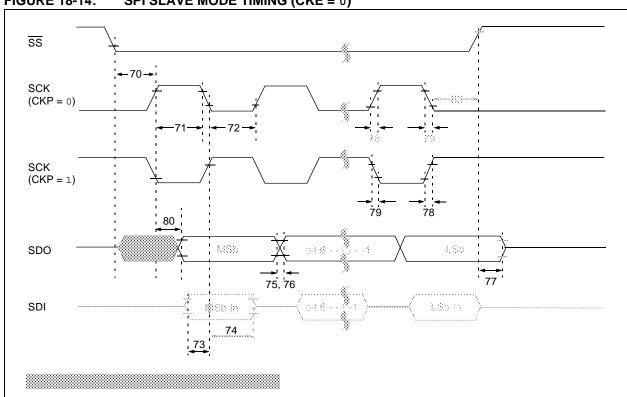

#### FIGURE 18-14: SPI SLAVE MODE TIMING (CKE = 0)

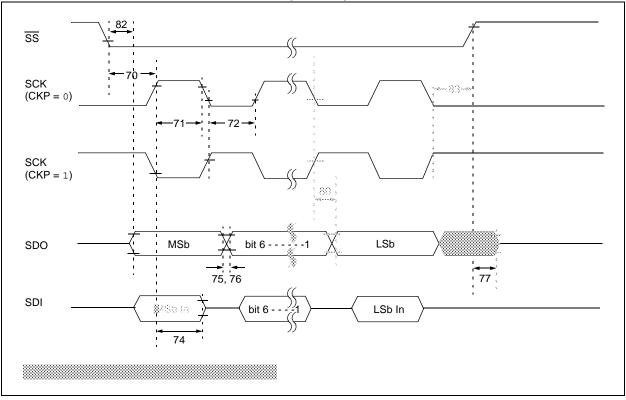

#### SPI SLAVE MODE TIMING (CKE = 1) FIGURE 18-15:

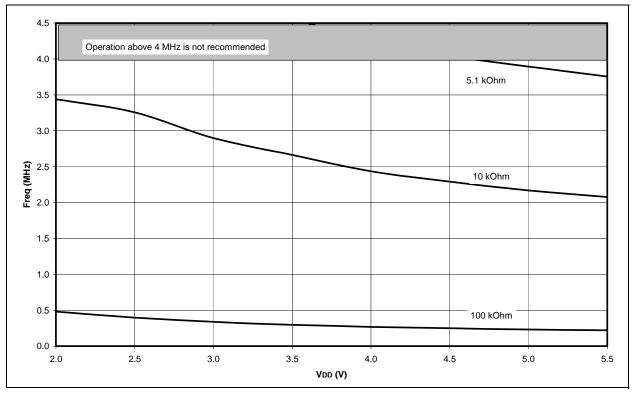

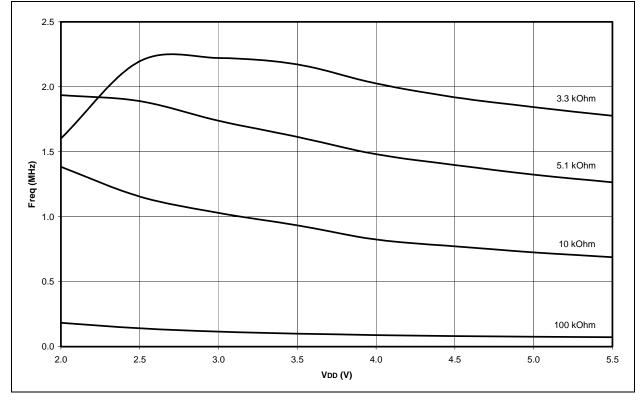

#### FIGURE 19-12: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, +25°C)

DS30498D-page 240

Example

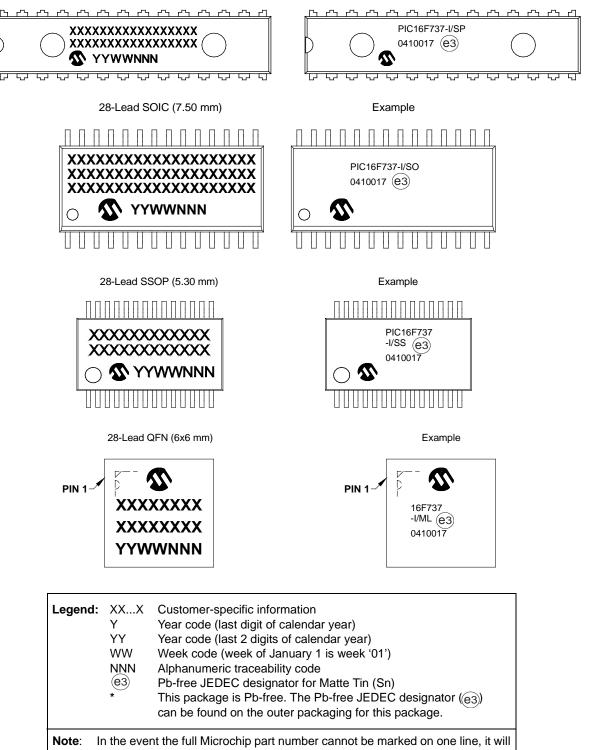

# 20.0 PACKAGING INFORMATION

#### 20.1 Package Marking Information

28-Lead SPDIP (.300")

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support