Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf767-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

|       | R/W-0                                                                                                                            | R/W-0                            | R/W-0                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0        | U-0                       | R/W-0        | R/W-0        |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|--------------|--------------|--|--|--|

|       | OSFIF                                                                                                                            | CMIF                             | LVDIF                         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BCLIF        | —                         | CCP3IF       | CCP2IF       |  |  |  |

|       | bit 7                                                                                                                            |                                  |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              | bit 0        |  |  |  |

| bit 7 | <b>OSFIF:</b> Os                                                                                                                 | cillator Fail I                  | nterrupt Flag                 | ı bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                           |              |              |  |  |  |

|       | •                                                                                                                                | n oscillator fa<br>n clock opera |                               | put has char                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nged to INT  | RC (must be               | e cleared in | software)    |  |  |  |

| bit 6 | CMIF: Con                                                                                                                        | nparator Inte                    | errupt Flag bi                | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                           |              |              |  |  |  |

|       | <ul> <li>1 = Comparator input has changed (must be cleared in software)</li> <li>0 = Comparator input has not changed</li> </ul> |                                  |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

| bit 5 | LVDIF: Lov                                                                                                                       | w-Voltage De                     | etect Interrup                | ot Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |                           |              |              |  |  |  |

|       |                                                                                                                                  |                                  |                               | low the specter of the specter of the specter of the specific term of term |              |                           | be cleared   | in software) |  |  |  |

| bit 4 | Unimplem                                                                                                                         | ented: Read                      | <b>d as</b> '0'               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

| bit 3 | BCLIF: Bu                                                                                                                        | s Collision Ir                   | nterrupt Flag                 | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                           |              |              |  |  |  |

|       |                                                                                                                                  | collision has<br>s collision ha  |                               | the SSP whe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | n configure  | d for I <sup>2</sup> C Ma | aster mode   |              |  |  |  |

| bit 2 | Unimplem                                                                                                                         | ented: Read                      | <b>d as</b> '0'               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

| bit 1 | CCP3IF: C                                                                                                                        | CP3 Interru                      | pt Flag bit                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

|       |                                                                                                                                  | 1 register ca                    | apture occurr<br>capture occu | ed (must be<br>rred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | cleared in s | oftware)                  |              |              |  |  |  |

|       |                                                                                                                                  | 1 register co                    | ompare matc<br>compare mat    | h occurred (n<br>ch occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nust be clea | ared in softw             | vare)        |              |  |  |  |

|       | <u>PWM mod</u><br>Unused in                                                                                                      | _                                |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

| bit 0 | CCP2IF: C                                                                                                                        | CP2 Interru                      | ot Flag bit                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

|       |                                                                                                                                  | 1 register ca                    | apture occurr<br>capture occu | ed (must be<br>rred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | cleared in s | oftware)                  |              |              |  |  |  |

|       |                                                                                                                                  | 1 register co                    | ompare matc<br>compare mat    | h occurred (r<br>ch occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nust be clea | ared in softw             | vare)        |              |  |  |  |

|       | <u>PWM mod</u><br>Unused.                                                                                                        | <u>e:</u>                        |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

|       | Legend:                                                                                                                          |                                  |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                           |              |              |  |  |  |

|       | R = Reada                                                                                                                        | able bit                         | W = W                         | /ritable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U = Unin     | nplemented                | bit, read as | · '0'        |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

#### 4.0 OSCILLATOR CONFIGURATIONS

#### 4.1 Oscillator Types

The PIC16F7X7 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. RC External Resistor/Capacitor with FOSC/4 output on RA6

- 5. RCIO External Resistor/Capacitor with I/O on RA6

- 6. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 7. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 8. ECIO External Clock with I/O on RA6

#### 4.2 Crystal Oscillator/Ceramic Resonators

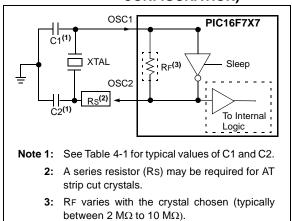

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F7X7 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

#### FIGURE 4-1: CRYSTAL OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 4-1:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR (FOR<br/>DESIGN GUIDANCE ONLY)

| Osc Type | Crystal | Typical Capa<br>Tes |       |  |

|----------|---------|---------------------|-------|--|

|          | Freq    | C1                  | C2    |  |

| LP       | 32 kHz  | 33 pF               | 33 pF |  |

|          | 200 kHz | 15 pF               | 15 pF |  |

| XT       | 200 kHz | 56 pF               | 56 pF |  |

|          | 1 MHz   | 15 pF               | 15 pF |  |

|          | 4 MHz   | 15 pF               | 15 pF |  |

| HS       | 4 MHz   | 15 pF               | 15 pF |  |

|          | 8 MHz   | 15 pF               | 15 pF |  |

|          | 20 MHz  | 15 pF               | 15 pF |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

## PIC16F7X7

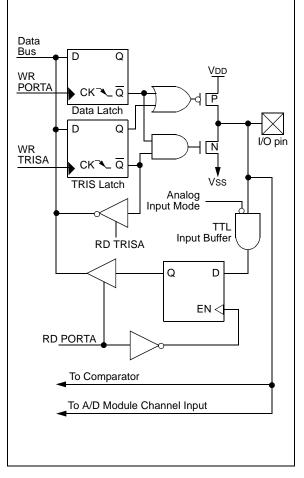

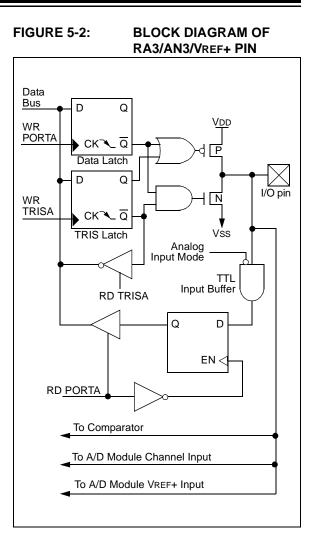

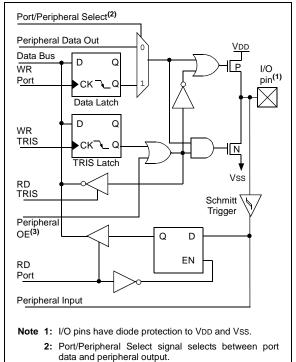

FIGURE 5-1: BLOCK DIAGRAM OF RA0/AN0:RA1/AN1 PINS

#### 5.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings and to **Section 16.1 "Read-Modify-Write Operations"** for additional information on read-modify-write operations.

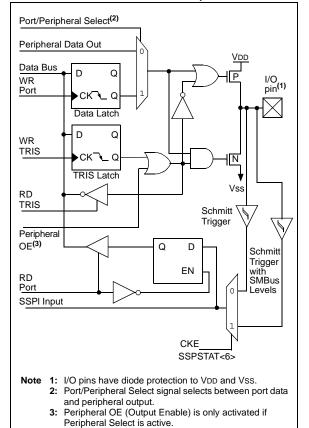

#### FIGURE 5-16: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5> PINS

Peripheral OE (Output Enable) is only activated if Peripheral Select is active.

#### FIGURE 5-17:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3> PINS

| REGISTER 5-1: | TRISE RE   | GISTER (A                                                                                                                    | DDRESS 8        | 39h)                  |              |             |              |             |  |  |  |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------|-------------|--------------|-------------|--|--|--|

|               | R-0        | R-0                                                                                                                          | R/W-0           | R/W-0                 | U-0          | R/W-1       | R/W-1        | R/W-1       |  |  |  |

|               | IBF        | OBF                                                                                                                          | IBOV            | PSPMODE               | _(1)         | TRISE2      | TRISE1       | TRISE0      |  |  |  |

|               | bit 7      |                                                                                                                              |                 |                       |              |             |              | bit 0       |  |  |  |

|               |            |                                                                                                                              |                 |                       |              |             |              |             |  |  |  |

| bit 7         |            | ave Port Sta                                                                                                                 |                 | bits:                 |              |             |              |             |  |  |  |

|               | -          | Buffer Full Sta                                                                                                              |                 | e waiting to be       | road by the  | CDU         |              |             |  |  |  |

|               |            | <ul> <li>1 = A word has been received and is waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul> |                 |                       |              |             |              |             |  |  |  |

| bit 6         | OBF: Outp  | ut Buffer Full                                                                                                               | Status bit      |                       |              |             |              |             |  |  |  |

|               |            | -                                                                                                                            |                 | eviously writter      | n word       |             |              |             |  |  |  |

| bit 5         |            | tput buffer ha                                                                                                               |                 | ı<br>bit (in Micropro |              |             |              |             |  |  |  |

| Dit 5         |            |                                                                                                                              |                 | usly input word       |              | ,           | ust be clea  | red in      |  |  |  |

|               | softwa     |                                                                                                                              |                 |                       |              |             |              |             |  |  |  |

|               | 0 = No ove | erflow occurre                                                                                                               | ed              |                       |              |             |              |             |  |  |  |

| bit 4         |            | : Parallel Sla                                                                                                               |                 | le Select bit         |              |             |              |             |  |  |  |

|               |            | l Slave Port r<br>al Purpose I/0                                                                                             |                 |                       |              |             |              |             |  |  |  |

| bit 3         |            | ented: Read                                                                                                                  |                 |                       |              |             |              |             |  |  |  |

| bit 0         | •          |                                                                                                                              |                 | state of the TR       | ISE3 bit has | no effect a | nd will alwa | vs read '1' |  |  |  |

| bit 2         |            | ta Direction                                                                                                                 | -               |                       |              |             |              |             |  |  |  |

|               |            |                                                                                                                              |                 | RE2/CS/AN7            |              |             |              |             |  |  |  |

|               | 1 = Input  |                                                                                                                              | ·               |                       |              |             |              |             |  |  |  |

|               | 0 = Output |                                                                                                                              |                 |                       |              |             |              |             |  |  |  |

| bit 1         |            | irection Cont                                                                                                                | rol bit for pin | RE1/WR/AN6            |              |             |              |             |  |  |  |

|               | 1 = Input  |                                                                                                                              |                 |                       |              |             |              |             |  |  |  |

| bit 0         |            |                                                                                                                              | ol hit for nin  | RE0/RD/AN5            |              |             |              |             |  |  |  |

| DILU          | 1 = Input  |                                                                                                                              |                 | REU/RD/ANS            |              |             |              |             |  |  |  |

|               | 0 = Output |                                                                                                                              |                 |                       |              |             |              |             |  |  |  |

|               |            |                                                                                                                              |                 |                       |              |             |              |             |  |  |  |

|               | Legend:    |                                                                                                                              |                 |                       |              |             |              |             |  |  |  |

|               | R = Reada  | ıble bit                                                                                                                     | W = W           | ritable bit           | U = Unimpl   | emented bi  | t, read as ' | 0'          |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

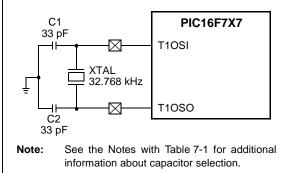

#### 7.6 Timer1 Oscillator

A crystal oscillator circuit is built between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during all power-managed modes. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

#### FIGURE 7-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

### TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq   | C1    | C2    |

|----------|--------|-------|-------|

| LP       | 32 kHz | 33 pF | 33 pF |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **4:** Capacitor values are for design guidance only.

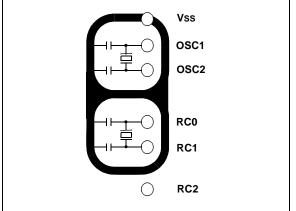

#### 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single sided PCB or in addition to a ground plane.

#### 7.8 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" signal (CCP1M3:CCP1M0 = 1011), the signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event triggers from the CCP1 |      |      |     |  |  |  |  |  |  |

|-------|------------------------------------------|------|------|-----|--|--|--|--|--|--|

|       | module will not set interrupt flag bit,  |      |      |     |  |  |  |  |  |  |

|       | TMR1IF                                   | (PIR | 1<0> | >). |  |  |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

### PIC16F7X7

NOTES:

#### 8.0 TIMER2 MODULE

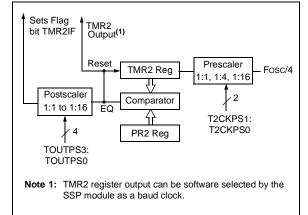

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable and is cleared on any device Reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt, latched in flag bit, TMR2IF (PIR1<1>).

Timer2 can be shut-off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

Register 8-1 shows the Timer2 Control register.

Additional information on timer modules is available in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

#### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

#### 8.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module which optionally uses it to generate the shift clock.

#### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

### PIC16F7X7

| REGISTER 9-1: | CCPxCON                                                                                                                                                                           | I: CCPx C                                                                                                                                                 |                                                                                                                                                 | REGISTER                                      | (ADDRES                                      | S 17h, 1DI                                      | h, <b>97h)</b> |         |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-------------------------------------------------|----------------|---------|--|--|--|

|               | U-0                                                                                                                                                                               | U-0                                                                                                                                                       | R/W-0                                                                                                                                           | R/W-0                                         | R/W-0                                        | R/W-0                                           | R/W-0          | R/W-0   |  |  |  |

|               | —                                                                                                                                                                                 | _                                                                                                                                                         | CCPxX                                                                                                                                           | CCPxY                                         | CCPxM3                                       | CCPxM2                                          | CCPxM1         | CCPxM0  |  |  |  |

|               | bit 7                                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                                 |                                               |                                              |                                                 |                | bit 0   |  |  |  |

| bit 7-6       | Unimplem                                                                                                                                                                          | ented: Rea                                                                                                                                                | <b>d as</b> '0'                                                                                                                                 |                                               |                                              |                                                 |                |         |  |  |  |