Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf767-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

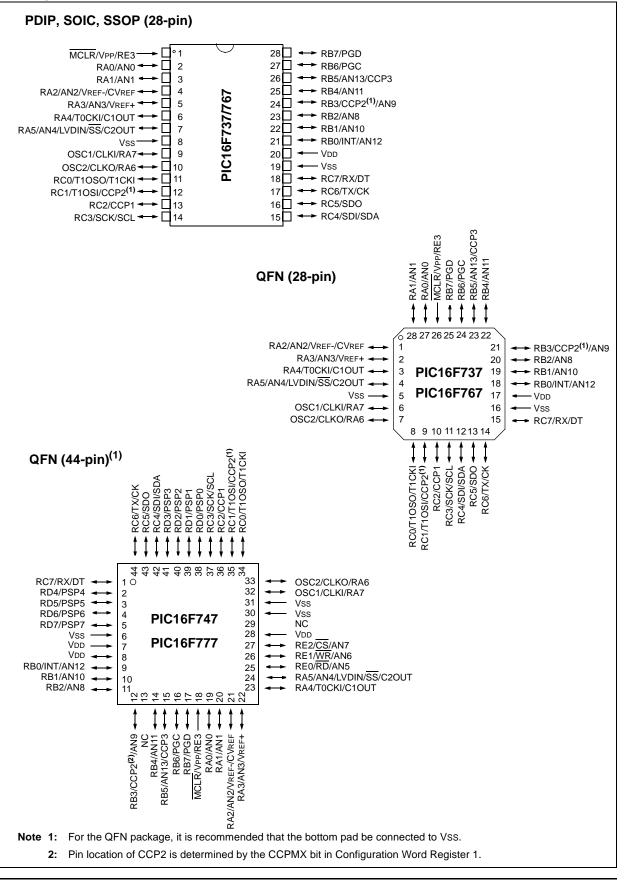

### **Pin Diagrams**

### **Table of Contents**

| 1.0   | Device Overview                                                              | 5   |

|-------|------------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                          | 15  |

| 3.0   | Reading Program Memory                                                       | 31  |

| 4.0   | Oscillator Configurations                                                    | 33  |

| 5.0   | I/O Ports                                                                    | 49  |

| 6.0   | Timer0 Module                                                                | 73  |

| 7.0   | Timer1 Module                                                                | 77  |

| 8.0   | Timer2 Module                                                                | 85  |

| 9.0   | Capture/Compare/PWM Modules                                                  | 87  |

| 10.0  | Master Synchronous Serial Port (MSSP) Module                                 | 93  |

| 11.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 133 |

| 12.0  | Analog-to-Digital Converter (A/D) Module                                     | 151 |

| 13.0  | Comparator Module                                                            | 161 |

| 14.0  | Comparator Voltage Reference Module                                          | 167 |

| 15.0  | Special Features of the CPU                                                  | 169 |

| 16.0  | Instruction Set Summary                                                      | 193 |

| 17.0  | Development Support                                                          | 201 |

|       |                                                                              |     |

| 19.0  | DC and AC Characteristics Graphs and Tables                                  | 235 |

|       | Packaging Information                                                        |     |

| Appe  | ndix A: Revision History                                                     |     |

| Appe  | ndix B: Device Differences                                                   | 265 |

| Appe  | ndix C: Conversion Considerations                                            |     |

|       | Nicrochip Web Site                                                           |     |

| Custo | omer Change Notification Service                                             | 275 |

| Custo | omer Support                                                                 | 275 |

| Read  | ler Response                                                                 | 276 |

| PIC1  | 6F7X7 Product Identification System                                          | 277 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit, TMR1IE (PIE1<0>).

The Timer1 oscillator can be used as a secondary clock source in low-power modes. When the T1RUN bit is set along with SCS<1:0> = 01, the Timer1 oscillator is providing the system clock. If the Fail-Safe Clock Monitor is enabled and the Timer1 oscillator fails while providing the system clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

### 7.1 Timer1 Operation

Timer1 can operate in one of three modes:

- as a Timer

- as a Synchronous Counter

- as an Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP1 module as the special event trigger (see **Section 9.4** "**Capture Mode**"). Register 7-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC0/T1OSO/T1CKI and RC1/T1OSI/CCP2 pins become inputs. That is, the TRISB<7:6> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

### 7.9 Resetting Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

### 7.10 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

### 7.11 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 7.6** "**Timer1 Oscillator**") gives users the option to include RTC functionality in their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 7-3, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

| RTCinit | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF<br>MOVLW<br>MOVWF<br>CLRF<br>CLRF<br>MOVLW<br>MOVWF | TMR1H<br>0x80<br>TMR1H<br>TMR1L<br>b'00001111'<br>T1CON<br>secs<br>mins<br>.12<br>hours | ; Preload TMR1 register pair<br>; for 1 second overflow<br>; Configure for external clock,<br>; Asynchronous operation, external oscillator<br>; Initialize timekeeping registers |

|---------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | BANKSEL<br>BSF                                                                        | PIE1<br>PIE1, TMR1IE                                                                    | ; Enable Timer1 interrupt                                                                                                                                                         |

| RTCisr  | RETURN<br>BANKSEL                                                                     | TMR1H                                                                                   |                                                                                                                                                                                   |

|         | BSF                                                                                   | TMR1H, 7                                                                                | ; Preload for 1 sec overflow                                                                                                                                                      |

|         | BCF                                                                                   | PIR1, TMR1IF                                                                            | ; Clear interrupt flag                                                                                                                                                            |

|         | INCF                                                                                  | secs, F                                                                                 | ; Increment seconds                                                                                                                                                               |

|         | MOVF                                                                                  | secs, w                                                                                 |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .60                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 60 seconds elapsed?                                                                                                                                                             |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | seconds                                                                                 | ; Clear seconds                                                                                                                                                                   |

|         | INCF                                                                                  | mins, f                                                                                 | ; Increment minutes                                                                                                                                                               |

|         | MOVF                                                                                  | mins, w                                                                                 |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .60                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 60 seconds elapsed?                                                                                                                                                             |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | mins                                                                                    | ; Clear minutes                                                                                                                                                                   |

|         | INCF                                                                                  | hours, f                                                                                | ; Increment hours                                                                                                                                                                 |

|         | MOVF                                                                                  | hours, w                                                                                |                                                                                                                                                                                   |

|         | SUBLW                                                                                 | .24                                                                                     |                                                                                                                                                                                   |

|         | BTFSS                                                                                 | STATUS, Z                                                                               | ; 24 hours elapsed?                                                                                                                                                               |

|         | RETURN                                                                                |                                                                                         | ; No, done                                                                                                                                                                        |

|         | CLRF                                                                                  | hours                                                                                   | ; Clear hours                                                                                                                                                                     |

|         | RETURN                                                                                |                                                                                         | ; Done                                                                                                                                                                            |

EXAMPLE 7-3: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| REGISTER 8-1: | T2CON:                | TIMER2 C                                             |                 | REGISTER     | (ADDRESS    | 5 12h) |         |         |  |  |  |  |  |

|---------------|-----------------------|------------------------------------------------------|-----------------|--------------|-------------|--------|---------|---------|--|--|--|--|--|

|               | U-0                   | R/W-0                                                | R/W-0           | R/W-0        | R/W-0       | R/W-0  | R/W-0   | R/W-0   |  |  |  |  |  |

|               |                       | TOUTPS3                                              | TOUTPS2         | TOUTPS1      | TOUTPS0     | TMR2ON | T2CKPS1 | T2CKPS0 |  |  |  |  |  |

|               | bit 7                 |                                                      |                 |              | ·           |        |         | bit 0   |  |  |  |  |  |

| bit 7         | Unimple               | mented: Rea                                          | <b>d as</b> '0' |              |             |        |         |         |  |  |  |  |  |

| bit 6-3       | -                     | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |                 |              |             |        |         |         |  |  |  |  |  |

|               | 0000 = 1<br>0001 = 1  | :1 Postscale<br>:2 Postscale<br>:3 Postscale         |                 |              |             |        |         |         |  |  |  |  |  |

|               | •                     |                                                      |                 |              |             |        |         |         |  |  |  |  |  |

|               | •                     |                                                      |                 |              |             |        |         |         |  |  |  |  |  |

|               | 1111 <b>= 1</b>       | :16 Postscale                                        | )               |              |             |        |         |         |  |  |  |  |  |

| bit 2         | TMR2ON: Timer2 On bit |                                                      |                 |              |             |        |         |         |  |  |  |  |  |

|               | 1 = Time<br>0 = Time  |                                                      |                 |              |             |        |         |         |  |  |  |  |  |

| bit 1-0       | T2CKPS                | 1:T2CKPS0:                                           | Timer2 Cloc     | k Prescale S | Select bits |        |         |         |  |  |  |  |  |

|               |                       | scaler is 1<br>scaler is 4                           |                 |              |             |        |         |         |  |  |  |  |  |

|               |                       | scaler is 16                                         |                 |              |             |        |         |         |  |  |  |  |  |

|               | Legend                | :                                                    |                 |              |             |        |         |         |  |  |  |  |  |

|               |                       |                                                      |                 |              |             |        |         | (0)     |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value or<br>POR, BC |    | Valu<br>all c<br>Res | other |

|------------------------|--------|----------------------|--------------|---------|---------|---------|--------|---------|---------|---------------------|----|----------------------|-------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE         | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000 00             | 0x | 0000                 | 000u  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF         | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 00             | 00 | 0000                 | 0000  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE         | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 00             | 00 | 0000                 | 0000  |

| 11h                    | TMR2   | Timer2 M             | odule Regis  | ster    |         |         |        |         |         | 0000 00             | 00 | 0000                 | 0000  |

| 12h                    | T2CON  | —                    | TOUTPS3      | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 00             | 00 | -000                 | 0000  |

| 92h                    | PR2    | Timer2 Pe            | eriod Regist | ter     |         |         |        |         |         | 1111 11             | 11 | 1111                 | 1111  |

Legend: x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F737/767 devices; always maintain these bits clear.

### 10.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 10.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

### 10.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

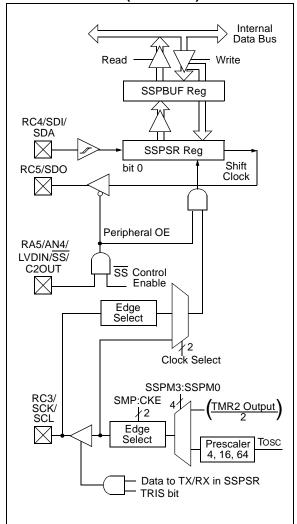

### 10.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/LVDIN/SS/C2OUT

Figure 10-1 shows the block diagram of the MSSP module when operating in SPI mode.

### FIGURE 10-1:

### MSSP BLOCK DIAGRAM (SPI MODE)

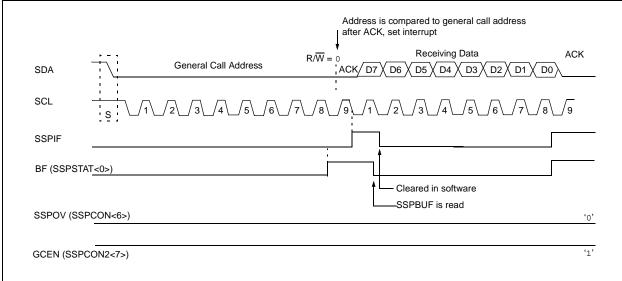

#### 10.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set and while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 10-15).

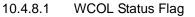

### 10.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

### FIGURE 10-19: FIRST START BIT TIMING

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

| ER 11-2: | RCSTA: R                                                                                                                                    |                                          |               |               |              |              |                |              |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|---------------|--------------|--------------|----------------|--------------|--|--|--|--|

|          | R/W-0                                                                                                                                       | R/W-0                                    | R/W-0         | R/W-0         | R/W-0        | R-0          | R-0            | R-x          |  |  |  |  |

|          | SPEN                                                                                                                                        | RX9                                      | SREN          | CREN          | ADDEN        | FERR         | OERR           | RX9D         |  |  |  |  |

|          | bit 7                                                                                                                                       |                                          |               |               |              |              |                | bit 0        |  |  |  |  |

| bit 7    | SPEN: Ser                                                                                                                                   | ial Port Ena                             | ble bit       |               |              |              |                |              |  |  |  |  |

|          | -                                                                                                                                           | oort enabled                             |               | RC7/RX/D      | Fand RC6/T   | X/CK pins a  | as serial port | pins)        |  |  |  |  |

| bit 6    | <b>RX9</b> : 9-bit                                                                                                                          | Receive Ena                              | able bit      |               |              |              |                |              |  |  |  |  |

|          |                                                                                                                                             | s 9-bit recep<br>s 8-bit recep           |               |               |              |              |                |              |  |  |  |  |

| bit 5    | SREN: Sin                                                                                                                                   | gle Receive                              | Enable bit    |               |              |              |                |              |  |  |  |  |

|          | <u>Asynchronous mode:</u><br>Don't care.                                                                                                    |                                          |               |               |              |              |                |              |  |  |  |  |

|          | Synchronous mode – Master:<br>1 = Enables single receive<br>0 = Disables single receive<br>This bit is cleared after reception is complete. |                                          |               |               |              |              |                |              |  |  |  |  |

|          | <u>Synchrono</u><br>Don't care.                                                                                                             | us mode – S                              | <u>Slave:</u> |               |              |              |                |              |  |  |  |  |

| bit 4    | CREN: Cor                                                                                                                                   | ntinuous Re                              | ceive Enable  | e bit         |              |              |                |              |  |  |  |  |

|          |                                                                                                                                             | ous mode:<br>s continuou<br>es continuou |               |               |              |              |                |              |  |  |  |  |

|          |                                                                                                                                             |                                          |               | til enable bi | CREN is cle  | eared (CRE   | N overrides    | SREN)        |  |  |  |  |

| bit 3    | ADDEN: A                                                                                                                                    | ddress Dete                              | ect Enable bi | t             |              |              |                |              |  |  |  |  |

|          | Asynchron                                                                                                                                   | ous mode 9                               | -bit (RX9 = 1 | <u>.):</u>    |              |              |                |              |  |  |  |  |

|          | RSR<                                                                                                                                        | 8> is set                                |               |               | upt and load |              |                |              |  |  |  |  |

|          |                                                                                                                                             |                                          |               | l bytes are r | eceived and  | ninth bit ca | n be used a    | s parity bit |  |  |  |  |

| bit 2    |                                                                                                                                             | ming Error t                             |               |               |              |              |                |              |  |  |  |  |

|          | 1 = Framin<br>0 = No frar                                                                                                                   |                                          | be updated    | by reading    | RCREG regi   | ster and red | ceiving next   | valid byte)  |  |  |  |  |

| bit 1    | OERR: OV                                                                                                                                    | errun Error I                            | oit           |               |              |              |                |              |  |  |  |  |

|          | 1 = Overru<br>0 = No ove                                                                                                                    |                                          | be cleared b  | by clearing l | oit CREN)    |              |                |              |  |  |  |  |

| bit 0    | <b>RX9D:</b> 9th                                                                                                                            | bit of Receiv                            | ved Data      |               |              |              |                |              |  |  |  |  |

|          | Can be par                                                                                                                                  | ity bit but m                            | ust be calcul | lated by use  | er firmware. |              |                |              |  |  |  |  |

|          | Legend:                                                                                                                                     |                                          |               |               |              |              |                |              |  |  |  |  |

|          | R = Reada                                                                                                                                   | ble bit                                  | W = W         | ritable bit   | U = Unim     | plemented    | bit, read as   | '0'          |  |  |  |  |

|          |                                                                                                                                             | at POR                                   |               | t is set      | '0' = Bit is | -            | ,              | -            |  |  |  |  |

| REGISTER 12-3: | ADCON2: A/D CONTROL REGISTER 2 (ADDRESS 9Bh)     U-0   U-0   R/W-0   R/W-0   U-0   U-0   U-0     —   —   ACQT2   ACQT1   ACQT0   —   —   —   — |     |       |       |       |     |     |       |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------|-----|-----|-------|--|--|

|                | U-0                                                                                                                                            | U-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |  |  |

|                |                                                                                                                                                | —   | ACQT2 | ACQT1 | ACQT0 | —   | _   | _     |  |  |

|                | bit 7                                                                                                                                          |     |       |       |       |     |     | bit 0 |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-3 ACQT<2:0>: A/D Acquisition Time Select bits

$000 = 0^{(1)}$ 001 = 2 TAD 010 = 4 TAD011 = 6 TAD 100 = 8 TAD 101 = **12T**AD 110 = 16 TAD 111 = 20 TAD

> Note 1: If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and VSS) or the voltage level on the RA3/AN3/VREF+ and RA2/AN2/VREF-/CVREF pins.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted.

Each port pin associated with the A/D converter can be configured as an analog input or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0 register) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 12-1.

| REGIST            | REGISTER 15-2: CONFIGURATION WORD REGISTER 2 (ADDRESS 2008h)                                                                              |                                                                                                                              |       |     |       |           |        |          |           |             |            |          |       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----------|--------|----------|-----------|-------------|------------|----------|-------|

| U-1               | U-1                                                                                                                                       | U-1                                                                                                                          | U-1   | U-1 | U-1   | U-1       | R/P-1  | U-1      | U-1       | U-1         | U-1        | R/P-1    | R/P-1 |

|                   | _                                                                                                                                         | _                                                                                                                            | —     | —   | _     |           | BORSEN |          | —         | _           | —          | IESO     | FCMEN |

| bit 13            |                                                                                                                                           |                                                                                                                              |       |     |       |           |        |          |           |             |            |          | bit 0 |

| bit 13-7<br>bit 6 | <b>BORSEN:</b> Brown-out Reset Software Enable bit<br>Refer to Configuration Word Register 1, bit 6 for the function of this bit.         |                                                                                                                              |       |     |       |           |        |          |           |             |            |          |       |

| bit 5-2           | Unimplemented: Read as '1'                                                                                                                |                                                                                                                              |       |     |       |           |        |          |           |             |            |          |       |

| bit 1             | IESO: Internal External Switchover bit<br>1 = Internal External Switchover mode enabled<br>0 = Internal External Switchover mode disabled |                                                                                                                              |       |     |       |           |        |          |           |             |            |          |       |

| bit 0             | 1 = F                                                                                                                                     | <b>FCMEN:</b> Fail-Safe Clock Monitor Enabled<br>1 = Fail-Safe Clock Monitor enabled<br>0 = Fail-Safe Clock Monitor disabled |       |     |       |           |        |          |           |             |            |          |       |

|                   | Lege                                                                                                                                      | end:                                                                                                                         |       |     |       |           |        |          |           |             |            |          |       |

|                   | R = I                                                                                                                                     | Readabl                                                                                                                      | e bit |     | W = 1 | Writable  | e bit  | U = Uni  | mpleme    | nted bit, i | read as '  | 0'       |       |

|                   | -n =                                                                                                                                      | Value at                                                                                                                     | POR   |     | '1' = | Bit is se | t      | 0' = Bit | is cleare | ed          | x = Bit is | s unknov | vn    |

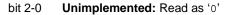

### 15.2 Reset

The PIC16F7X7 differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset during normal operation

- WDT Wake-up during Sleep

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The  $\overline{TO}$  and  $\overline{PD}$  bits are set or cleared differently in different Reset situations, as indicated in Table 15-3. These bits are used in software to determine the nature of the Reset. Upon a POR, BOR or wake-up from Sleep, the CPU requires approximately 5-10 µs to become ready for code execution. This delay runs in parallel with any other timers. See Table 15-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 15-1.

### FIGURE 15-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

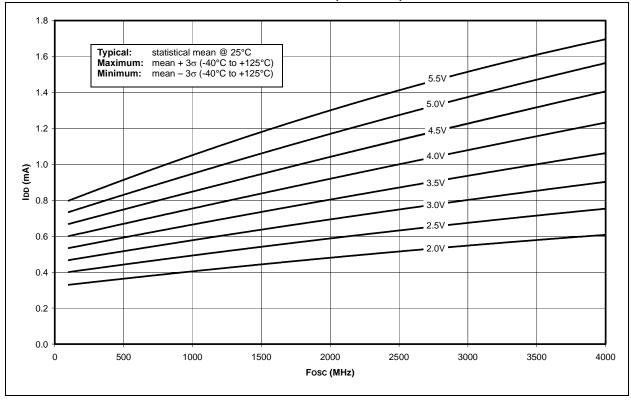

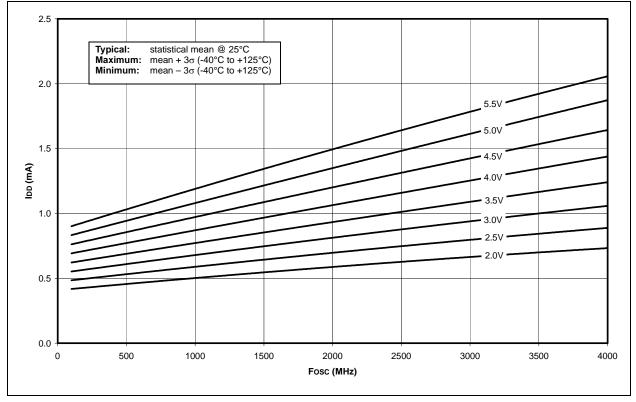

### 18.2 DC Characteristics: Power-Down and Supply Current PIC16F737/747/767/777 (Industrial, Extended) PIC16LF737/747/767/777 (Industrial) (Continued)

|              | 7 <b>37/747/767/777</b><br>strial)         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                      |       |            |            |                                |  |  |  |  |  |  |

|--------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------|------------|------------|--------------------------------|--|--|--|--|--|--|

|              | <b>37/747/767/777</b><br>strial, Extended) |                                                                                                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |            |            |                                |  |  |  |  |  |  |

| Param<br>No. | Device                                     | Тур                                                                                                                                | Max                                                  | Units | Conditions |            |                                |  |  |  |  |  |  |

|              | Supply Current (IDD) <sup>(2,3)</sup>      |                                                                                                                                    |                                                      |       |            |            |                                |  |  |  |  |  |  |

|              | PIC16LF7X7                                 | 9                                                                                                                                  | 20                                                   | μA    | -40°C      |            |                                |  |  |  |  |  |  |

|              |                                            | 7                                                                                                                                  | 15                                                   | μΑ    | +25°C      | VDD = 2.0V |                                |  |  |  |  |  |  |

|              |                                            | 7                                                                                                                                  | 15                                                   | μΑ    | +85°C      |            |                                |  |  |  |  |  |  |

|              | PIC16LF7X7                                 | 16                                                                                                                                 | 30                                                   | μΑ    | -40°C      |            |                                |  |  |  |  |  |  |

|              |                                            | 14                                                                                                                                 | 25                                                   | μΑ    | +25°C      | VDD = 3.0V | Fosc = 32 kHz                  |  |  |  |  |  |  |

|              |                                            | 14                                                                                                                                 | 25                                                   | μΑ    | +85°C      |            | (LP Oscillator)                |  |  |  |  |  |  |

|              | All devices                                | 32                                                                                                                                 | 40                                                   | μΑ    | -40°C      |            |                                |  |  |  |  |  |  |

|              |                                            | 26                                                                                                                                 | 35                                                   | μΑ    | +25°C      | VDD = 5.0V |                                |  |  |  |  |  |  |

|              |                                            | 26                                                                                                                                 | 35                                                   | μΑ    | +85°C      | VDD = 3.0V |                                |  |  |  |  |  |  |

|              | Extended devices                           | 35                                                                                                                                 | 53                                                   | μΑ    | +125°C     |            |                                |  |  |  |  |  |  |

|              | PIC16LF7X7                                 | 72                                                                                                                                 | 95                                                   | μA    | -40°C      |            |                                |  |  |  |  |  |  |

|              |                                            | 76                                                                                                                                 | 90                                                   | μA    | +25°C      | VDD = 2.0V |                                |  |  |  |  |  |  |

|              |                                            | 76                                                                                                                                 | 90                                                   | μA    | +85°C      |            |                                |  |  |  |  |  |  |

|              | PIC16LF7X7                                 | 138                                                                                                                                | 175                                                  | μΑ    | -40°C      | _          |                                |  |  |  |  |  |  |

|              |                                            | 136                                                                                                                                | 170                                                  | μΑ    | +25°C      | VDD = 3.0V | Fosc = 1 MHz                   |  |  |  |  |  |  |

|              |                                            | 136                                                                                                                                | 170                                                  | μΑ    | +85°C      |            | (RC Oscillator) <sup>(3)</sup> |  |  |  |  |  |  |

|              | All devices                                | 310                                                                                                                                | 380                                                  | μΑ    | -40°C      |            |                                |  |  |  |  |  |  |

|              |                                            | 290                                                                                                                                | 360                                                  | μΑ    | +25°C      | VDD = 5.0V |                                |  |  |  |  |  |  |

|              |                                            | 280                                                                                                                                | 360                                                  | μΑ    | +85°C      | 122 - 0.01 |                                |  |  |  |  |  |  |

|              | Extended devices                           | 330                                                                                                                                | 500                                                  | μΑ    | +125°C     |            |                                |  |  |  |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

### 18.2 DC Characteristics: Power-Down and Supply Current PIC16F737/747/767/777 (Industrial, Extended) PIC16LF737/747/767/777 (Industrial) (Continued)

|              | 7 <b>37/747/767/777</b><br>strial)         |      | Standard Operating Conditions (unless otherwise stated)   Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial   Standard Operating Conditions (unless otherwise stated)   Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |            |            |                         |  |  |  |  |  |  |

|--------------|--------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------------|-------------------------|--|--|--|--|--|--|

|              | <b>37/747/767/777</b><br>strial, Extended) |      |                                                                                                                                                                                                                                                                                                                                                                                          |       |            |            |                         |  |  |  |  |  |  |

| Param<br>No. | Device                                     | Тур  | Max                                                                                                                                                                                                                                                                                                                                                                                      | Units | Conditions |            |                         |  |  |  |  |  |  |

|              | Supply Current (IDD) <sup>(2,3)</sup>      |      |                                                                                                                                                                                                                                                                                                                                                                                          |       |            |            |                         |  |  |  |  |  |  |

|              | PIC16LF7X7                                 | .950 | 1.3                                                                                                                                                                                                                                                                                                                                                                                      | mA    | -40°C      |            |                         |  |  |  |  |  |  |

|              |                                            | .930 | 1.2                                                                                                                                                                                                                                                                                                                                                                                      | mA    | +25°C      | VDD = 3.0V |                         |  |  |  |  |  |  |

|              |                                            | .930 | 1.2                                                                                                                                                                                                                                                                                                                                                                                      | mA    | +85°C      |            | Fosc = 8 MHz            |  |  |  |  |  |  |

|              | All devices                                | 1.8  | 3.0                                                                                                                                                                                                                                                                                                                                                                                      | mA    | -40°C      |            | (RC_RUN mode,           |  |  |  |  |  |  |

|              |                                            | 1.7  | 2.8                                                                                                                                                                                                                                                                                                                                                                                      | mA    | +25°C      | VDD = 5.0V | Internal RC Oscillator) |  |  |  |  |  |  |

|              |                                            | 1.7  | 2.8                                                                                                                                                                                                                                                                                                                                                                                      | mA    | +85°C      | VDD = 3.0V |                         |  |  |  |  |  |  |

|              | Extended devices                           | 2.0  | 4.0                                                                                                                                                                                                                                                                                                                                                                                      | mA    | +125°C     |            |                         |  |  |  |  |  |  |

|              | PIC16LF7X7                                 | 9    | 13                                                                                                                                                                                                                                                                                                                                                                                       | μA    | -10°C      |            |                         |  |  |  |  |  |  |

|              |                                            | 9    | 14                                                                                                                                                                                                                                                                                                                                                                                       | μA    | +25°C      | VDD = 2.0V |                         |  |  |  |  |  |  |

|              |                                            | 11   | 16                                                                                                                                                                                                                                                                                                                                                                                       | μΑ    | +70°C      |            |                         |  |  |  |  |  |  |

|              | PIC16LF7X7                                 | 12   | 34                                                                                                                                                                                                                                                                                                                                                                                       | μΑ    | -10°C      |            | Fosc = 32 kHz           |  |  |  |  |  |  |

|              |                                            | 12   | 31                                                                                                                                                                                                                                                                                                                                                                                       | μA    | +25°C      | VDD = 3.0V | (SEC_RUN mode,          |  |  |  |  |  |  |

|              |                                            | 14   | 28                                                                                                                                                                                                                                                                                                                                                                                       | μA    | +70°C      |            | Timer1 as Clock)        |  |  |  |  |  |  |

|              | All devices                                | 20   | 72                                                                                                                                                                                                                                                                                                                                                                                       | μA    | -10°C      |            |                         |  |  |  |  |  |  |

|              |                                            | 20   | 65                                                                                                                                                                                                                                                                                                                                                                                       | μA    | +25°C      | VDD = 5.0V |                         |  |  |  |  |  |  |

|              |                                            | 25   | 59                                                                                                                                                                                                                                                                                                                                                                                       | μA    | +70°C      |            |                         |  |  |  |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

# 18.5 Timing Parameter Symbology

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2ppS           |                                      | 3. Tcc:st | (I <sup>2</sup> C specifications only) |  |  |

|-----------------------|--------------------------------------|-----------|----------------------------------------|--|--|

| 2. TppS               |                                      | 4. Ts     | (I <sup>2</sup> C specifications only) |  |  |

| Т                     |                                      |           |                                        |  |  |

| F                     | Frequency                            | Т         | Time                                   |  |  |

| Lowerca               | se letters (pp) and their meanings:  | •         |                                        |  |  |

| рр                    |                                      |           |                                        |  |  |

| сс                    | CCP1                                 | osc       | OSC1                                   |  |  |

| ck                    | CLKO                                 | rd        | RD                                     |  |  |

| CS                    | CS                                   | rw        | RD or WR                               |  |  |

| di                    | SDI                                  | SC        | SCK                                    |  |  |

| do                    | SDO                                  | SS        | SS                                     |  |  |

| dt                    | Data in                              | tO        | TOCKI                                  |  |  |

| io                    | I/O port                             | t1        | T1CKI                                  |  |  |

| mc                    | MCLR                                 | wr        | WR                                     |  |  |

|                       | se letters and their meanings:       |           |                                        |  |  |

| S                     |                                      |           |                                        |  |  |

| F                     | Fall                                 | Р         | Period                                 |  |  |

| Н                     | High                                 | R         | Rise                                   |  |  |

| I                     | Invalid (High-impedance)             | V         | Valid                                  |  |  |

| L                     | Low                                  | Z         | High-impedance                         |  |  |

| I <sup>2</sup> C only |                                      |           |                                        |  |  |

| AA                    | output access                        | High      | High                                   |  |  |

| BUF                   | Bus free                             | Low       | Low                                    |  |  |

| TCC:ST (              | <sup>12</sup> C specifications only) |           |                                        |  |  |

| CC                    |                                      |           |                                        |  |  |

| HD                    | Hold                                 | SU        | Setup                                  |  |  |

| ST                    |                                      |           |                                        |  |  |

| DAT                   | DATA input hold                      | STO       | Stop condition                         |  |  |

| STA                   | Start condition                      |           |                                        |  |  |

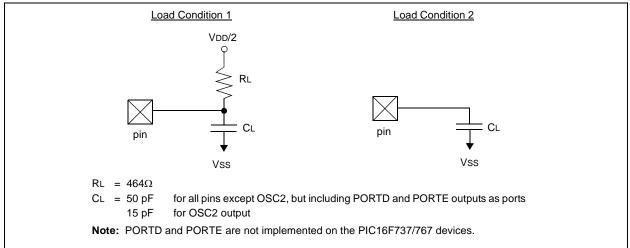

### FIGURE 18-4: LOAD CONDITIONS

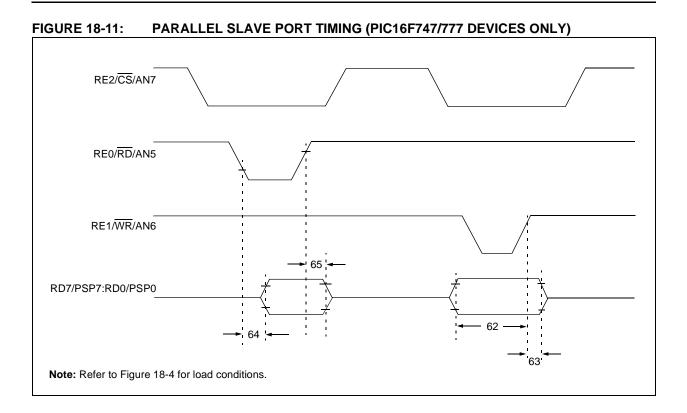

### TABLE 18-9: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F747/777 DEVICES ONLY)

| Param<br>No.                                        | Symbol                                                                               | Characteristic                                                                             |            | Min | Тур† | Max | Units               | Conditions          |

|-----------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|-----|------|-----|---------------------|---------------------|

| 62                                                  | TdtV2wrH                                                                             | Data In Valid before $\overline{WR}$ $\uparrow$ or $\overline{CS}$ $\uparrow$ (setup time) |            | 20  | —    | _   | ns                  |                     |

|                                                     |                                                                                      |                                                                                            | 25         | —   |      | ns  | Extended range only |                     |

| 63*                                                 | TwrH2dtI                                                                             |                                                                                            | PIC16F7X7  | 20  | —    | _   | ns                  |                     |

|                                                     |                                                                                      |                                                                                            | PIC16LF7X7 | 35  | —    | —   | ns                  |                     |

| 64                                                  | TRDL2DTV $\overline{RD} \downarrow$ and $\overline{CS} \downarrow$ to Data Out Valid |                                                                                            | _          | —   | 80   | ns  |                     |                     |

|                                                     |                                                                                      |                                                                                            |            | —   | -    | 90  | ns                  | Extended range only |

| 65                                                  | TrdH2dtI                                                                             | $\overline{RD}$ $\uparrow$ or $\overline{CS}$ $\downarrow$ to Data Out Invalid             |            | 10  | —    | 30  | ns                  |                     |