Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf767t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

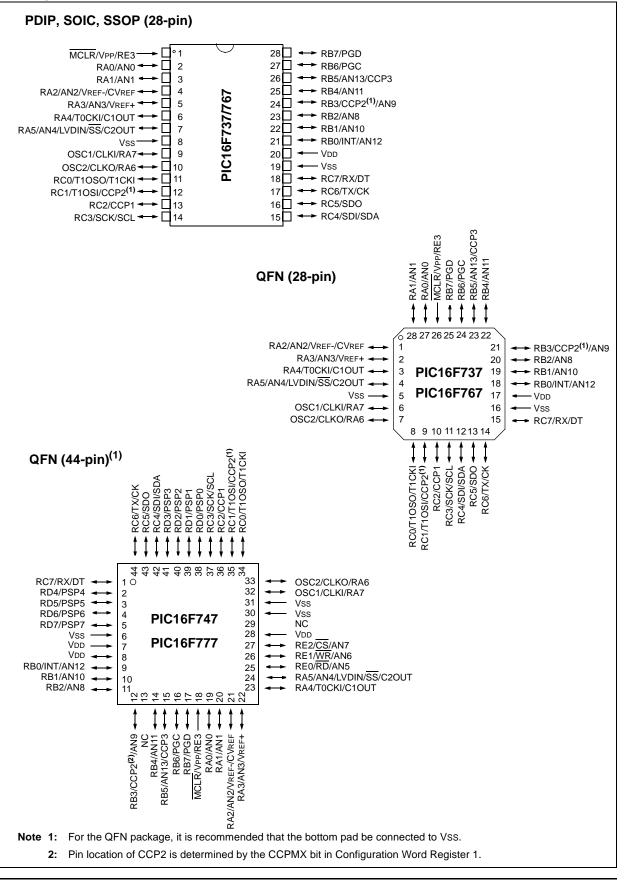

#### **Pin Diagrams**

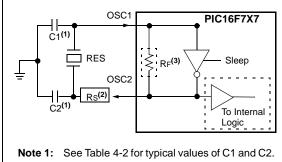

#### FIGURE 4-2: CERAMIC RESONATOR OPERATION (HS OR XT OSC CONFIGURATION)

- **2:** A series resistor (Rs) may be required.

- 3: RF varies with the resonator chosen (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

#### TABLE 4-2: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| Typical Capacitor Values Used: |          |       |       |  |  |  |  |  |  |  |

|--------------------------------|----------|-------|-------|--|--|--|--|--|--|--|

| Mode Freq OSC1 OSC2            |          |       |       |  |  |  |  |  |  |  |

| XT                             | 455 kHz  | 56 pF | 56 pF |  |  |  |  |  |  |  |

|                                | 2.0 MHz  | 47 pF | 47 pF |  |  |  |  |  |  |  |

|                                | 4.0 MHz  | 33 pF | 33 pF |  |  |  |  |  |  |  |

| HS                             | 8.0 MHz  | 27 pF | 27 pF |  |  |  |  |  |  |  |

|                                | 16.0 MHz | 22 pF | 22 pF |  |  |  |  |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode rather than XT mode is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is 330Ω.

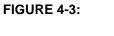

## 4.3 External Clock Input

The ECIO Oscillator mode requires an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the ECIO Oscillator mode, the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 4-3 shows the pin connections for the ECIO Oscillator mode.

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

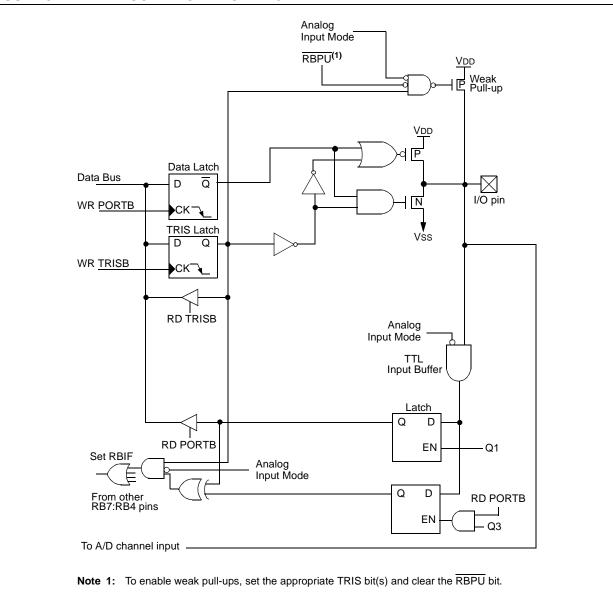

## 5.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

### 5.1 PORTA and the TRISA Register

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in Configuration Register 1H (see **Section 15.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA3:RA0 and RA5 as A/D converter inputs is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register 1). Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register.

| Note: | On a Power-on Reset, RA5 and RA3:RA0          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the RA pins even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 5-1: INITIALIZING PORTA

| BCF<br>BCF | STATUS, |       | ;<br>; Bank0            |

|------------|---------|-------|-------------------------|

| -          |         | ICI I | ,                       |

| CLRF       | PORTA   |       | ; Initialize PORTA by   |

|            |         |       | ; clearing output       |

|            |         |       | ; data latches          |

| BSF        | STATUS, | RP0   | ; Select Bank 1         |

| MOVLW      | 0x0F    |       | ; Configure all pins    |

| MOVWF      | ADCON1  |       | ; as digital inputs     |

| MOVLW      | 0xCF    |       | ; Value used to         |

|            |         |       | ; initialize data       |

|            |         |       | ; direction             |

| MOVWF      | TRISA   |       | ; Set RA<3:0> as inputs |

|            |         |       | ; RA<5:4> as outputs    |

|            |         |       | ; TRISA<7:6>are always  |

|            |         |       | ; read as '0'.          |

| REGISTER 5-1: | TRISE RE                                                                                                                            | GISTER (A      | DDRESS 8        | 39h)            |              |             |              |             |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----------------|--------------|-------------|--------------|-------------|--|--|--|--|

|               | R-0                                                                                                                                 | R-0            | R/W-0           | R/W-0           | U-0          | R/W-1       | R/W-1        | R/W-1       |  |  |  |  |

|               | IBF                                                                                                                                 | OBF            | IBOV            | PSPMODE         | _(1)         | TRISE2      | TRISE1       | TRISE0      |  |  |  |  |

|               | bit 7                                                                                                                               |                |                 |                 |              |             |              | bit 0       |  |  |  |  |

|               |                                                                                                                                     |                |                 |                 |              |             |              |             |  |  |  |  |

| bit 7         |                                                                                                                                     | ave Port Sta   |                 | bits:           |              |             |              |             |  |  |  |  |

|               | <b>IBF:</b> Input Buffer Full Status bit                                                                                            |                |                 |                 |              |             |              |             |  |  |  |  |

|               | <ul> <li>1 = A word has been received and is waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul>        |                |                 |                 |              |             |              |             |  |  |  |  |

| bit 6         |                                                                                                                                     |                |                 |                 |              |             |              |             |  |  |  |  |

|               | 1 = The output buffer still holds a previously written word                                                                         |                |                 |                 |              |             |              |             |  |  |  |  |

| bit E         | <ul><li>0 = The output buffer has been read</li><li>bit 5 IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode)</li></ul> |                |                 |                 |              |             |              |             |  |  |  |  |

| Dit 5         |                                                                                                                                     |                |                 | · ·             |              | ,           | ust be clea  | red in      |  |  |  |  |

|               | <ul> <li>1 = A write occurred when a previously input word has not been read (must be cleared in<br/>software)</li> </ul>           |                |                 |                 |              |             |              |             |  |  |  |  |

|               | 0 = No overflow occurred                                                                                                            |                |                 |                 |              |             |              |             |  |  |  |  |

| bit 4         |                                                                                                                                     | : Parallel Sla |                 | le Select bit   |              |             |              |             |  |  |  |  |

|               | 1 = Parallel Slave Port mode<br>0 = General Purpose I/O mode                                                                        |                |                 |                 |              |             |              |             |  |  |  |  |

| bit 3         |                                                                                                                                     | ented: Read    |                 |                 |              |             |              |             |  |  |  |  |

| bit 0         | •                                                                                                                                   |                |                 | state of the TR | ISE3 bit has | no effect a | nd will alwa | vs read '1' |  |  |  |  |

| bit 2         |                                                                                                                                     | -              | -               |                 |              |             |              |             |  |  |  |  |

|               | PORTE Data Direction bits:<br>TRISE2: Direction Control bit for pin RE2/CS/AN7                                                      |                |                 |                 |              |             |              |             |  |  |  |  |

|               | 1 = Input                                                                                                                           |                |                 |                 |              |             |              |             |  |  |  |  |

|               | 0 = Output                                                                                                                          |                |                 |                 |              |             |              |             |  |  |  |  |

| bit 1         |                                                                                                                                     | irection Cont  | rol bit for pin | RE1/WR/AN6      |              |             |              |             |  |  |  |  |

|               | 1 = Input                                                                                                                           |                |                 |                 |              |             |              |             |  |  |  |  |

| bit 0         |                                                                                                                                     |                | ol hit for nin  | RE0/RD/AN5      |              |             |              |             |  |  |  |  |

| DILU          | 1 = Input                                                                                                                           |                |                 | REU/RD/ANS      |              |             |              |             |  |  |  |  |

|               | 0 = Output                                                                                                                          |                |                 |                 |              |             |              |             |  |  |  |  |

|               |                                                                                                                                     |                |                 |                 |              |             |              |             |  |  |  |  |

|               | Legend:                                                                                                                             |                |                 |                 |              |             |              |             |  |  |  |  |

|               | R = Reada                                                                                                                           | ıble bit       | W = W           | ritable bit     | U = Unimpl   | emented bi  | t, read as ' | 0'          |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

#### EXAMPLE 6-1: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0

| CLRWDT  |             | ; | Cl |

|---------|-------------|---|----|

| BANKSEL | OPTION_REG  | ; | Se |

| MOVLW   | b'xxxx0xxx' | ; | Se |

| MOVWF   | OPTION_REG  | ; | va |

|         |             |   |    |

- Clear WDT and prescaler Select Bank of OPTION\_REG Select TMR0, new prescale value and clock source

- TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|-----------------------|------------|----------|-----------|--------|--------|-------|--------|--------|-------|----------------------|---------------------------------|--|

| 01h,101h              | TMR0       | Timer0 M | odule Reg | ister  |        |       |        |        |       | xxxx xxxx            | uuuu uuuu                       |  |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE      | PEIE      | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 0000 000x            | 0000 000u                       |  |

| 81h,181h              | OPTION_REG | RBPU     | INTEDG    | TOCS   | TOSE   | PSA   | PS2    | PS1    | PS0   | 1111 1111            | 1111 1111                       |  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

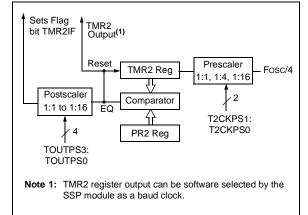

## 8.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable and is cleared on any device Reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt, latched in flag bit, TMR2IF (PIR1<1>).

Timer2 can be shut-off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

Register 8-1 shows the Timer2 Control register.

Additional information on timer modules is available in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (POR, MCLR Reset, WDT Reset or BOR)

TMR2 is not cleared when T2CON is written.

## 8.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module which optionally uses it to generate the shift clock.

#### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

#### 10.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register (SSPCON)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 10-1: SSPSTAT: MSSP STATUS (SPI MODE) REGISTER (ADDRESS 94h)

|       | R/W-0                                                                         | R/W-0           | R-0             | ,<br>R-0      | R-0         | 、<br>R-0      | ,<br>R-0     | R-0           |  |  |  |  |

|-------|-------------------------------------------------------------------------------|-----------------|-----------------|---------------|-------------|---------------|--------------|---------------|--|--|--|--|

|       | SMP                                                                           | CKE             | D/A             | к-0<br>Р      | R-0<br>S    | R-U<br>R/W    | UA           | BF            |  |  |  |  |

|       | bit 7                                                                         | ORL             | DIA             | I             | 5           | 11/00         | 07           | bit 0         |  |  |  |  |

|       |                                                                               |                 |                 |               |             |               |              | DILO          |  |  |  |  |

| bit 7 | SMP: Sam                                                                      | ple bit         |                 |               |             |               |              |               |  |  |  |  |

|       | SPI Master                                                                    | •               |                 |               |             |               |              |               |  |  |  |  |

|       | 1 = Input d                                                                   | ata sampled     | at end of da    | ata output ti | me          |               |              |               |  |  |  |  |

|       | 0 = Input d                                                                   | ata sampled     | at middle o     | f data outpu  | it time     |               |              |               |  |  |  |  |

|       | <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode. |                 |                 |               |             |               |              |               |  |  |  |  |

|       |                                                                               |                 |                 | used in Slav  | /e mode.    |               |              |               |  |  |  |  |

| bit 6 | CKE: SPI Clock Edge Select bit                                                |                 |                 |               |             |               |              |               |  |  |  |  |

|       |                                                                               | nit occurs on   |                 |               |             |               |              |               |  |  |  |  |

|       | 0 = Transmit occurs on transition from Idle to active clock state             |                 |                 |               |             |               |              |               |  |  |  |  |

|       | Note:                                                                         | Polarity of o   | clock state is  | s set by the  | CKP bit (SS | PCON1<4>      | ).           |               |  |  |  |  |

| bit 5 | D/A: Data/                                                                    | Address bit     |                 |               |             |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                      | c mode only.    |                 |               |             |               |              |               |  |  |  |  |

| bit 4 | P: Stop bit                                                                   |                 |                 |               |             |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                      | mode only.      | This bit is cle | ared when t   | he MSSP m   | odule is disa | bled, SSPEN  | l is cleared. |  |  |  |  |

| bit 3 | S: Start bit                                                                  |                 |                 |               |             |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                      | c mode only.    |                 |               |             |               |              |               |  |  |  |  |

| bit 2 | R/W: Read                                                                     | I/Write bit Inf | ormation        |               |             |               |              |               |  |  |  |  |

|       | Used in I <sup>2</sup> C                                                      | c mode only.    |                 |               |             |               |              |               |  |  |  |  |

| bit 1 | UA: Update                                                                    | e Address bi    | it              |               |             |               |              |               |  |  |  |  |

|       |                                                                               | c mode only.    |                 |               |             |               |              |               |  |  |  |  |

| bit 0 | BF: Buffer                                                                    | Full Status b   | oit (Receive    | mode only)    |             |               |              |               |  |  |  |  |

|       |                                                                               | e complete,     | -               |               |             |               |              |               |  |  |  |  |

|       |                                                                               | e not comple    |                 |               |             |               |              |               |  |  |  |  |

|       |                                                                               |                 |                 |               |             |               |              |               |  |  |  |  |

|       | Legend:                                                                       |                 |                 |               |             |               |              |               |  |  |  |  |

|       | R = Reada                                                                     | ble bit         | W = W           | ritable bit   | U = Unim    | plemented     | bit, read as | '0'           |  |  |  |  |

|       | -n = Value                                                                    | at POR          | '1' = Bi        | t is set      | '0' = Bit i | s cleared     | x = Bit is u | nknown        |  |  |  |  |

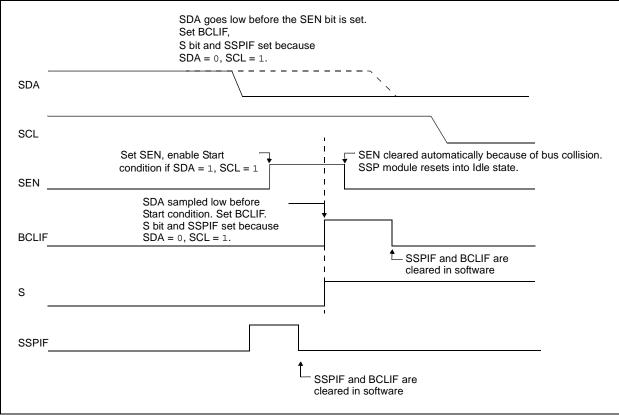

#### 10.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 10-26).

- b) SCL is sampled low before SDA is asserted low (Figure 10-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 10-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 10-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pin is sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

### FIGURE 10-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

## 13.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

### 13.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Off mode, CM<2:0> = 111. This ensures compatibility to the PIC16F87X devices.

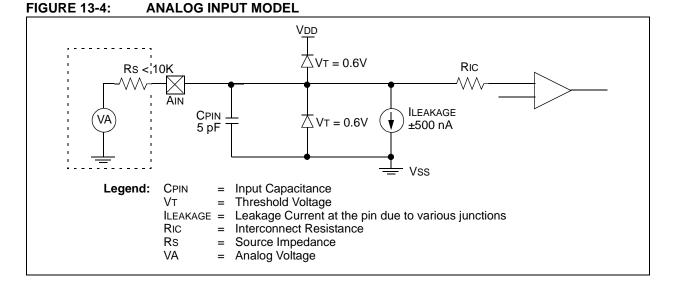

### 13.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 13-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| TABLE 13-1: | <b>REGISTERS ASSOCIATED WITH COMPARATOR MODULE</b> |

|-------------|----------------------------------------------------|

|-------------|----------------------------------------------------|

| Address                                 | Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|-----------------------------------------|--------|-------|-------|--------|--------|-------|--------|--------|--------|-----------------|---------------------------------|

| 9Ch                                     | CMCON  | C2OUT | C10UT | C2INV  | C1INV  | CIS   | CM2    | CM1    | CM0    | 0000 0111       | 0000 0111                       |

| 9Dh                                     | CVRCON | CVREN | CVROE | CVRR   | —      | CVR3  | CVR2   | CVR1   | CVR0   | 000- 0000       | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh,18Bh                  | INTCON | GIE   | PEIE  | TMR0IE | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x       | 0000 000u                       |

| 0Dh                                     | PIR2   | OSFIF | CMIF  | LVDIF  | —      | BCLIF | _      | CCP3IF | CCP2IF | 000- 0-00       | 000- 0-00                       |

| 8Dh                                     | PIE2   | OSFIE | CMIE  | LVDIE  | —      | BCLIE | _      | CCP3IE | CCP2IE | 000- 0-00       | 000- 0-00                       |

| 05h                                     | PORTA  | RA7   | RA6   | RA5    | RA4    | RA3   | RA2    | RA1    | RA0    | xx0x 0000       | uu0u 0000                       |

| 85h TRISA PORTA Data Direction Register |        |       |       |        |        |       |        |        |        |                 | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

## 14.0 COMPARATOR VOLTAGE **REFERENCE MODULE**

The comparator voltage reference generator is a 16-tap resistor ladder network that provides a fixed voltage reference when the comparators are in mode '110'. A programmable register controls the function of the reference generator. Register 14-1 lists the bit functions of the CVRCON register.

As shown in Figure 14-1, the resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The comparator reference supply voltage (also referred to as CVRSRC) comes directly from VDD. It should be noted, however, that the voltage at the top of the ladder is CVRSRC - VSAT, where VSAT is the saturation voltage of the power switch transistor. This reference will only be as accurate as the values of CVRSRC and VSAT.

The output of the reference generator may be connected to the RA2/AN2/VREF-/CVREF pin. This can be used as a simple D/A function by the user if a very high-impedance load is used. The primary purpose of this function is to provide a test path for testing the reference generator function.

#### **REGISTER 14-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER** (ADDRESS 9Dh)

|         | R/W-0                                                                                                       | R/W-0                        | R/W-0           | U-0          | R/W-0                                                                                                 | R/W-0     | R/W-0          | R/W-0  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------|------------------------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------|-----------|----------------|--------|--|--|--|

|         | CVREN                                                                                                       | CVROE                        | CVRR            |              | CVR3                                                                                                  | CVR2      | CVR1           | CVR0   |  |  |  |

|         | bit 7                                                                                                       |                              |                 |              |                                                                                                       |           | •              | bit 0  |  |  |  |

|         |                                                                                                             |                              |                 |              |                                                                                                       |           |                |        |  |  |  |

| bit 7   | CVREN: C                                                                                                    | omparator V                  | oltage Refe     | rence Enabl  | e bit                                                                                                 |           |                |        |  |  |  |

|         |                                                                                                             | circuit powe<br>circuit powe |                 |              |                                                                                                       |           |                |        |  |  |  |

| bit 6   | CVROE: C                                                                                                    | omparator V                  | REF Output      | Enable bit   |                                                                                                       |           |                |        |  |  |  |

|         |                                                                                                             | voltage leve<br>voltage leve | •               |              |                                                                                                       |           | oin            |        |  |  |  |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                                   |                              |                 |              |                                                                                                       |           |                |        |  |  |  |

|         | 1 = 0 to 0.625 CVRSRC, with CVRSRC/24 step size<br>0 = 0.25 CVRSRC to 0.72 CVRSRC, with CVRSRC/32 step size |                              |                 |              |                                                                                                       |           |                |        |  |  |  |

| bit 4   | Unimplem                                                                                                    | ented: Read                  | <b>l as</b> '0' |              |                                                                                                       |           |                |        |  |  |  |

| bit 3-0 | CVR3:CVF                                                                                                    | <b>0:</b> Compara            | tor VREF Va     | lue Selectio | n bits $0 \le C$                                                                                      | R3:CVR0   | ≤ 15           |        |  |  |  |

|         | When CVR                                                                                                    | R = 1:                       |                 |              |                                                                                                       |           |                |        |  |  |  |

|         |                                                                                                             | CVR<3:0>/24                  | l) • (CVRSR     | C)           |                                                                                                       |           |                |        |  |  |  |

|         | When CVR                                                                                                    |                              |                 |              | $\langle \mathbf{O} \rangle$ $\langle \mathbf{D} \mathbf{e} \mathbf{e} \mathbf{e} \mathbf{e} \rangle$ |           |                |        |  |  |  |

|         | $CVREF = 1/4 \bullet (CVRSRC) + (CVR3:CVR0/32) \bullet (CVRSRC)$                                            |                              |                 |              |                                                                                                       |           |                |        |  |  |  |

|         |                                                                                                             |                              |                 |              |                                                                                                       |           |                |        |  |  |  |

|         | Legend:                                                                                                     |                              |                 |              |                                                                                                       |           |                |        |  |  |  |

|         | R = Reada                                                                                                   |                              |                 | ritable bit  |                                                                                                       | •         | bit, read as ' |        |  |  |  |

|         | -n = Value                                                                                                  | at POR                       | '1' = Bi        | t is set     | '0' = Bit is                                                                                          | s cleared | x = Bit is u   | nknown |  |  |  |

| REGIST            | REGISTER 15-2: CONFIGURATION WORD REGISTER 2 (ADDRESS 2008h)                                                                              |                                                                                                                                 |                   |         |         |           |        |           |           |             |            |          |       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|---------|-----------|--------|-----------|-----------|-------------|------------|----------|-------|

| U-1               | U-1                                                                                                                                       | U-1                                                                                                                             | U-1               | U-1     | U-1     | U-1       | R/P-1  | U-1       | U-1       | U-1         | U-1        | R/P-1    | R/P-1 |

|                   | _                                                                                                                                         | _                                                                                                                               | —                 | —       | _       |           | BORSEN |           | —         | _           | —          | IESO     | FCMEN |

| bit 13            |                                                                                                                                           |                                                                                                                                 |                   |         |         |           |        |           |           |             |            |          | bit 0 |

| bit 13-7<br>bit 6 | BOR                                                                                                                                       | SEN: Br                                                                                                                         | i <b>ted:</b> Rea | Reset S | oftware |           |        | ion of th | nic hit   |             |            |          |       |

| bit 5-2           | Refer to Configuration Word Register 1, bit 6 for the function of this bit.<br><b>Unimplemented:</b> Read as '1'                          |                                                                                                                                 |                   |         |         |           |        |           |           |             |            |          |       |

| bit 1             | IESO: Internal External Switchover bit<br>1 = Internal External Switchover mode enabled<br>0 = Internal External Switchover mode disabled |                                                                                                                                 |                   |         |         |           |        |           |           |             |            |          |       |

| bit 0             | 1 = F                                                                                                                                     | <b>FCMEN:</b> Fail-Safe Clock Monitor Enable bit<br>1 = Fail-Safe Clock Monitor enabled<br>0 = Fail-Safe Clock Monitor disabled |                   |         |         |           |        |           |           |             |            |          |       |

|                   | Lege                                                                                                                                      | end:                                                                                                                            |                   |         |         |           |        |           |           |             |            |          |       |

|                   | R = I                                                                                                                                     | Readabl                                                                                                                         | e bit             |         | W = 1   | Writable  | e bit  | U = Uni   | mpleme    | nted bit, i | read as '  | 0'       |       |

|                   | -n =                                                                                                                                      | Value at                                                                                                                        | POR               |         | '1' =   | Bit is se | t      | 0' = Bit  | is cleare | ed          | x = Bit is | s unknov | vn    |

### 15.10.1 REFERENCE VOLTAGE SET POINT

The internal reference voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low-voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter #36. The low-voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 15-6.

#### 15.10.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

## 15.11 Operation During Sleep

When enabled, the LVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 15.12 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the LVD module to be turned off.

Note: If the LVD is enabled and the BOR module is not enabled, the band gap will require a start-up time of no more than 50 μs before the band gap reference is stable. Before enabling the LVD interrupt, the user should ensure that the band gap reference voltage is stable by monitoring the IRVST bit in the LVDCON register. The LVD could cause erroneous interrupts before the band gap is stable.

#### 15.13 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR occurs; then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS); when the OST ends, the device comes out of Reset.

If  $\overline{\text{MCLR}}$  is kept low long enough, all delays will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X7 device operating in parallel.

Table 15-3 shows the Reset conditions for the Status, PCON and PC registers, while Table 15-4 shows the Reset conditions for all the registers.

### 15.14 Power Control/Status Register (PCON)

The Power Control/Status register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if bit BOR cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable.

Bit 1 is Power-on Reset Status bit, POR. It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

## 17.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 17.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## TABLE 18-15: A/D CONVERTER CHARACTERISTICS: PIC16F7X7 (INDUSTRIAL, EXTENDED) PIC16LF7X7 (INDUSTRIAL)

| _            | İ                  | İ                                                 |            | 1           | 1                         |              |            |                                                                                                                                               |

|--------------|--------------------|---------------------------------------------------|------------|-------------|---------------------------|--------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym Characteristic |                                                   | Min        | Тур†        | Мах                       | Units        | Conditions |                                                                                                                                               |

| A01          | NR                 | Resolution                                        |            | —           | _                         | 10 bits      | bit        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |

| A03          | EIL                | Integral Linearity Error                          |            | _           |                           | <±1          | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |

| A04          | Edl                | Differential Linear                               | rity Error | _           | —                         | <±1          | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |

| A06          | EOFF               | Offset Error                                      |            | -           | —                         | <±2          | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |

| A07          | Egn                | Gain Error                                        |            | _           | —                         | <±1          | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |

| A10          | _                  | Monotonicity                                      |            | —           | guaranteed <sup>(3)</sup> | —            |            | $VSS \leq VAIN \leq VREF$                                                                                                                     |

| A20          | Vref               | Reference Voltage<br>(VREF+ – VREF-)              |            | 2.0         | —                         | VDD + 0.3    | V          |                                                                                                                                               |

| A21          | Vref+              | Reference Voltage High                            |            | AVDD – 2.5V | —                         | AVDD + 0.3V  | V          |                                                                                                                                               |

| A22          | VREF-              | Reference Voltage Low                             |            | AVss-0.3V   | —                         | VREF+ - 2.0V | V          |                                                                                                                                               |

| A25          | VAIN               | Analog Input Voltage                              |            | Vss - 0.3V  | —                         | VREF + 0.3V  | V          |                                                                                                                                               |

| A30          | Zain               | Recommended Impedance of<br>Analog Voltage Source |            | —           | —                         | 2.5          | kΩ         | (Note 4)                                                                                                                                      |

| A40          | lad                | A/D Conversion<br>Current (VDD)                   | PIC16F7X7  | —           | 220                       | —            | μΑ         | Average current<br>consumption when A/D is on<br>(Note 1)                                                                                     |

|              |                    |                                                   | PIC16LF7X7 | —           | 90                        | —            | μA         |                                                                                                                                               |

| A50          | IREF               | VREF Input Current (Note 2)                       |            | _           | _                         | 5            | μΑ         | During VAIN acquisition.<br>Based on differential of VHOLD<br>to VAIN to charge CHOLD,<br>see Section 12.1 "A/D<br>Acquisition Requirements". |

|              |                    |                                                   |            | —           | —                         | 150          | μA         | During A/D conversion cycle                                                                                                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current specification includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

4: Maximum allowed impedance for analog voltage source is 10 kΩ. This requires higher acquisition time.

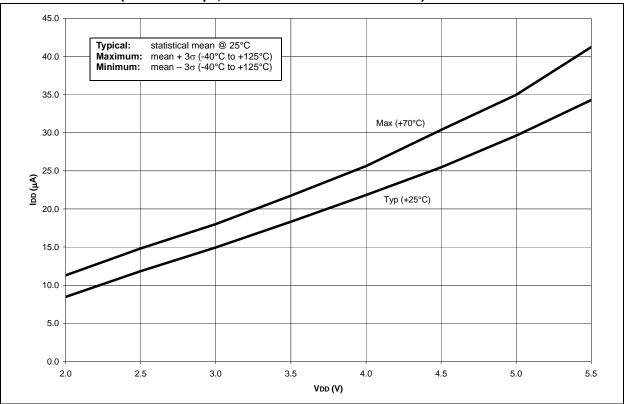

## FIGURE 19-9: IDD vs. VDD, SEC\_RUN MODE, -10°C TO +125°C, 32.768 kHz (XTAL 2 x 22 pF, ALL PERIPHERALS DISABLED)

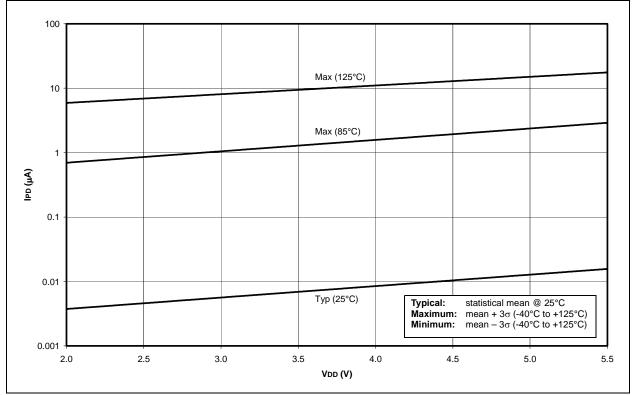

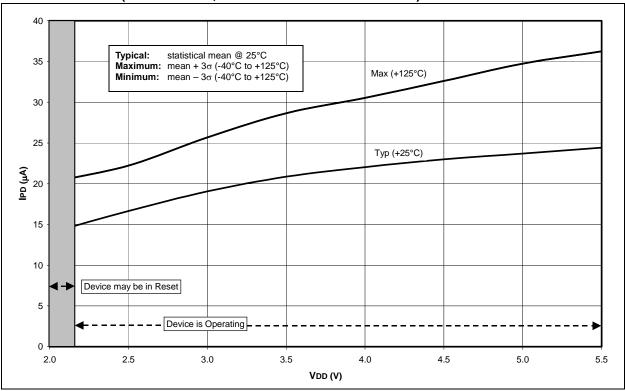

FIGURE 19-10: IPD vs. VDD, -40°C TO +125°C (SLEEP MODE, ALL PERIPHERALS DISABLED)

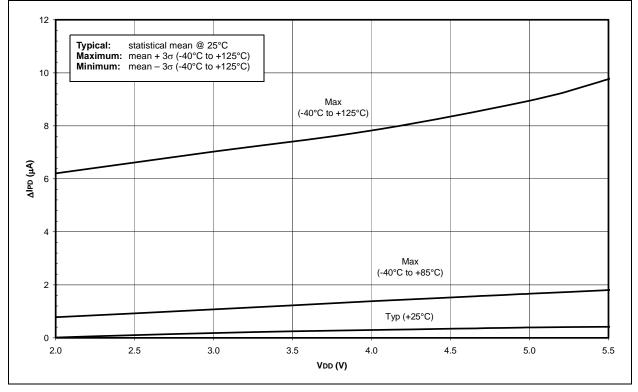

#### FIGURE 19-17: △IPD BOR vs. VDD, -40°C TO +125°C (SLEEP MODE, BOR ENABLED AT 2.00V-2.16V)

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support